**XPEXAR** ... the analog plus company<sup>TM</sup>

**APPLICATIONS**

CPI

DMI

T1 and CEPT Interfaces

Low Power PCM Line Interface

June 1997-3

XR-T56L85

## FEATURES10

- Low Power (Typical 14mA)

- Single +5V Supply

- Up to 2.048 Mbps Operation in Both TX and RX Directions

- Receiver Input can be:

- Balanced Transformer Coupled

- Capacitively (Twisted Pair)

- Single Coaxial Capacitive Coupling

#### **GENERAL DESCRIPTION**

The XR-T56L85 is a PCM line interface chip. It consists of both transmit and receive circuitry in a DIL 18 pin package. The maximum bit rate the chip can handle is 2.048 Mbps and the signal level to the received can be

attenuated by 10dB of cable loss at half the bit rate. Total current consumption is between 12-16mA at +5V.

#### **ORDERING INFORMATION**

| Part No.   | Package                    | Operating<br>Temperature Range |

|------------|----------------------------|--------------------------------|

| XR-T56L85N | 18 Lead 300 Mil CDIP       | -40°C to +85°C                 |

| XR-T56L85D | 18 Lead 300 Mil JEDEC SOIC | -40°C to +85°C                 |

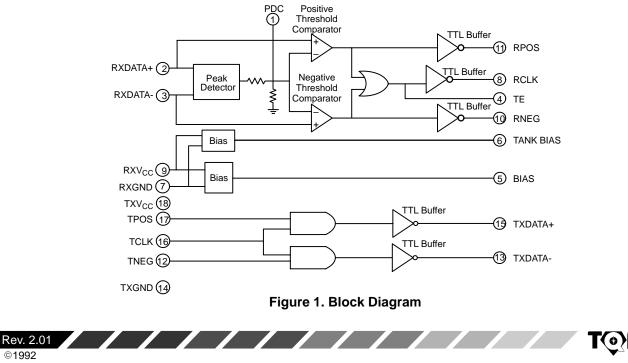

## **BLOCK DIAGRAM**

EXAR Corporation, 48720 Kato Road, Fremont, CA 94538 (510) 668-7000 FAX (510) 668-7017

# XR-T56L85

Т(•)М

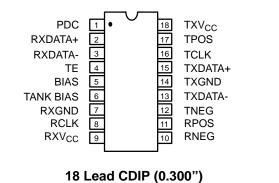

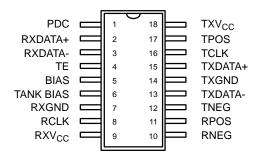

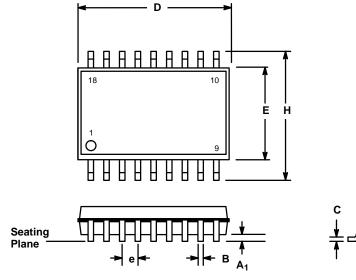

# **PIN CONFIGURATION**

18 Lead SOIC (Jedec, 0.300")

## **PIN DESCRIPTION**

| Pin # | Symbol            | Туре | Description                                                                                                                                                                                                                                          |  |  |

|-------|-------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1     | PDC               |      | Peak Detector Capacitor. This pin should be connected to a 0.1µF capacitor                                                                                                                                                                           |  |  |

| 2     | RXDATA+           | I    | <b>Receive Analog Input Positive.</b> The AMI signal received from the line is applied at this and the RX DATA(-) pin. Data and clock from the signal applied at these two pins recovered and output on the RPOS, RNEG, and RCLK pins, respectively. |  |  |

| 3     | RXDATA-           | I    | Receive Analog Input Negative. See the description for RX DATA(+).                                                                                                                                                                                   |  |  |

| 4     | TE                | 0    | LC Tank Excitation Output. This output connects to one side of the tank circuitry.                                                                                                                                                                   |  |  |

| 5     | BIAS              | 0    | <b>Bias.</b> This pin should be tied to ground through a $0.1\mu F$ capacitor.                                                                                                                                                                       |  |  |

| 6     | TANK BIAS         |      | Tank Reference. The tank circuitry is biased via this output.                                                                                                                                                                                        |  |  |

| 7     | RXGND             |      | <b>Receiver Ground.</b> To minimize ground interference a separate pin is used to ground the receiver section.                                                                                                                                       |  |  |

| 8     | RCLK              | 0    | <b>Recovered Receive Clock.</b> Recovered clock signal from the AMI signal received at the RX DATA(+) and RX DATA(-) pins. This signal is output to the terminal equipment.                                                                          |  |  |

| 9     | RXV <sub>CC</sub> |      | Receive Supply Voltage. 5V supply voltage for the Receive Section.                                                                                                                                                                                   |  |  |

| 10    | RNEG              | 0    | <b>Receive Negative Data Output.</b> A signal at this pin corresponds to the receipt of a negative pulse on the RX DATA(+)/RX DATA(-) pins. This TTL compatible signal is output to the terminal equipment.                                          |  |  |

| 11    | RPOS              | 0    | <b>Receive Positive Data Output.</b> A signal at this pin corresponds to the receipt of a positive pulse on the RX DATA(+)/RX DATA pins. This TTL compatible signal is outputed to the terminal equipment.                                           |  |  |

| 12    | TNEG              | I    | <b>Transmit Negative Data Input.</b> TTL input for a negative polarity pulse (the negative portion of the AMI pulse train) to be transmitted to the line via the TX DATA(+) and TX DATA pins.                                                        |  |  |

| 13    | TXDATA-           | 0    | <b>Transmit Negative Data Output.</b> This pin, along with the TX DATA(+) pin, forms a differential driver output, this is used to drive AMI data down the line via a transformer. Note: This is an open-collector output.                           |  |  |

| 14    | TXGND             |      | Transmit Ground.                                                                                                                                                                                                                                     |  |  |

| 15    | TXDATA+           | 0    | Transmit Positive Data Output. Please see description for TX DATA(-).                                                                                                                                                                                |  |  |

| 16    | TCLK              | I    | Transmit Clock. TPOS and TNEG are sampled on the rising edge of TCLK.                                                                                                                                                                                |  |  |

| 17    | TPOS              | Ι    | <b>Transmit Positive Data Input.</b> TTL input for a positive polarity pulse (the positive portion of the AMI pulse train) to be transmitted to the line via the TX DATA(+) and TX DATA(-) pins.                                                     |  |  |

| 18    | TXVcc             |      | Transmit Supply Voltage. 5V supply voltage to the transmit section.                                                                                                                                                                                  |  |  |

Rev. 2.01

# **ELECTRICAL CHARACTERISTICS**

Test Conditions:  $V_{CC} = 5V \pm 5\%$ ,  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ , Unless Otherwise Specified

| Parameters                     | Min. | Тур. | Max. | Unit                    | Conditions                                                                           |

|--------------------------------|------|------|------|-------------------------|--------------------------------------------------------------------------------------|

| DC Electrical Characteristics  |      |      |      |                         |                                                                                      |

| Supply Voltage                 | 4.75 | 5    | 5.25 | V                       |                                                                                      |

| Supply Current                 |      | 14   | 16   | mA                      | Total Current to Pin 9 & Pin 18 (Transmit-<br>ter Outputs Open and All Ones Pattern) |

| Receiver Section               |      |      | •    | •                       |                                                                                      |

| Tank Drive Current             | 300  | 500  | 700  | μΑ                      | Measured at Pin 4, $V_{CC}$ = 5V                                                     |

| Clock Output Low               |      | 0.3  | 0.6  | V                       | Measured at Pin 8, $I_{OL} = 1.6 \text{mA}$                                          |

| Clock Output High              | 3.0  | 3.6  |      | V                       | Measured at Pin 8, $I_{OH}$ =400 $\mu$ A                                             |

| Data Output Low                |      | 0.3  | 0.6  | V                       | Measured at Pin 10 & 11, I <sub>OL</sub> =1.6mA                                      |

| Data Output High               | 3.0  | 3.6  |      | V                       | Measured at Pin 10 & 11, $I_{OH}$ =400µA                                             |

| Transmitter Section            |      |      |      | •                       | •                                                                                    |

| Driver Output Low              | 0.6  | 0.9  | 1.2  | V                       | Measured at Pin 13 & 15, I <sub>OL</sub> =-40mA                                      |

| Output Leakage Current         |      |      | 100  | μA                      | Measured in Off State<br>Output Pull-up to +20V                                      |

| Input High Voltage             | 2.2  |      |      | V                       | Measured at Pin 12, 16 & 17 $I_{OL} = -40$ mA, $V_{OL} = 1.0V$                       |

| Input Low Voltage              |      |      | 0.8  | V                       | Measured at Pin 12, 16 & 17<br>Output Off                                            |

| Input Low Current              |      |      | -1.6 | mA                      | Measured at Pin 12, 16 & 17<br>Input Low Voltage = 0.4V                              |

| Input High Current             |      |      | 40   | μΑ                      | Measured at Pin 12, 16 & 17<br>Input Low Voltage = 0.4V                              |

| Output Low Current             |      |      | -30  | mA                      | Measured at Pin 13 & 15<br>V <sub>OL</sub> = 1.0V                                    |

| AC Electrical Characteristices | i    | •    | •    | •                       |                                                                                      |

| Receiver Section               |      |      |      |                         |                                                                                      |

| Input Level                    |      | 6    | 6.6  | Vpp                     | Measured Between Pin 2 & 3                                                           |

| Loss Input Signal Alarm Level  |      | 0.6  |      | Vpp                     | Measured Between Pin 2 & 3<br>Alarm on Pull Data/Clock Output High                   |

| Input Impedance at 2.048MHz    |      | 2.5  |      | kΩ                      | Measured Between Pin 2 & 3<br>With Sinewave Input                                    |

| Clock Duty Cycle               | 35   | 50   | 65   | %                       | Measured at Pin 8 at 2.0V DC Level                                                   |

| Clock Rise & Fall Time         |      | 20   | 40   | ns                      | Measured at Pin 8, CL = 15pF                                                         |

| Data Pulse Width               | 35   | 50   | 75   | % of<br>clock<br>period | Measured at Pin 10 & 11<br>At 1V DC Level, Cable Loss = $\emptyset dB$               |

| Transmitter Section            |      |      | •    | •                       | -                                                                                    |

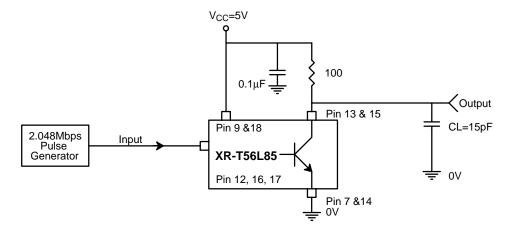

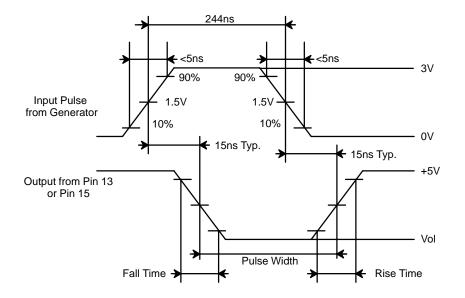

| Pulse Width at 2.048MHz        | 234  | 244  | 264  | ns                      | Measured at Pin 13 & 15 Figure 3                                                     |

| Output Rise Time               |      | 12   | 25   | ns                      | Figure 3                                                                             |

| Output Fall Time               |      | 12   | 25   | ns                      | Figure 3                                                                             |

| Output Fall Imbalance          |      | 2.5  |      | ns                      | At 50% Output Level                                                                  |

/ / / / /

Rev. 2.01

T�M™

#### **ABSOLUTE MAXIMUM RATINGS**

Supply Voltage ..... +20V

#### SYSTEM DESCRIPTION

#### The Receiver

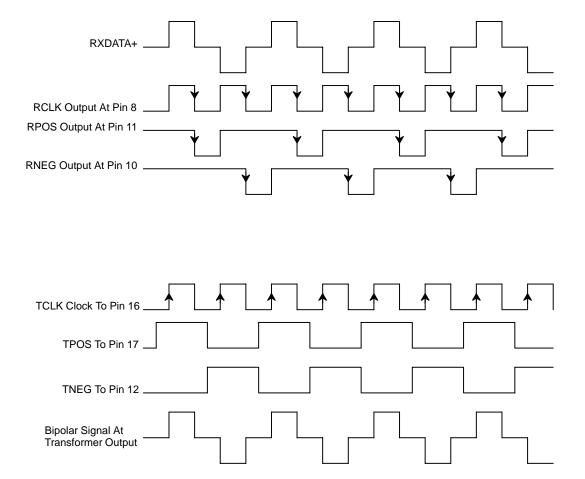

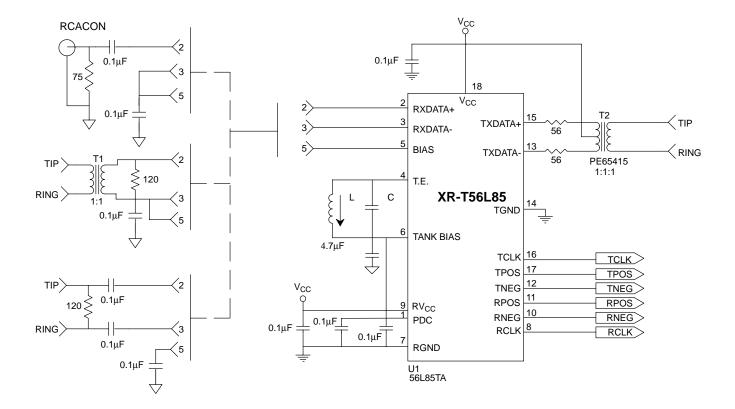

The incoming bipolar PCM signal, which is attenuated and distorted by the cable is applied to the receiver input, consisting of the RX DATA(+) and RX DATA(-) pins, either through a balanced transformer, a balanced capacitively coupled terminal or a single-ended coaxial cable (see Figure 5). A peak detector following the input generates a DC reference for the positive and negative threshold comparator (to extract the positive and negative data pulses). Information on the positive and negative data pulses is outputed as TTL compatible signals at pins RPOS and RNEG, respectively. More specifically, an output signal present at the RPOS pin indicates that a positive pulse was received at the RX DATA(+)/RX DATA(-) pins, from the incoming bipolar data stream. Likewise an output signal present at the RNEG pin indicates that a negative pulse was received at the RX DATA(+)/RX DATA(-) pins. This conversion from the bipolar signal to TTL compatible signals allows for digital processing of the clock and data signals by the terminal equipment. An example of the waveforms of the TTL compatible recovered clock and data as output by the receiver portion of the chip is presented in Figure 2, Figure 3 and Figure 5. A tank circuit tuned to the

Storage Temperature .....-65°C to 150°C

appropriate frequency is added externally to provide the appropriate frequency-selective filtering of the received clock signal.

#### The Transmitter

The transmitter portion of the chip receives TTL compatible signals and transmits a corresponding bipolar data stream down the line (See *Figure 5*). TPOS and TNEG are TTL compatible signals that dictate the polarity of the pulse to be generated and transmitted on the output bipolar data stream. Both TPOS and TNEG inputs are sampled by the rising edge of the transmit clock, TCLK. The TX DATA(+) and TX DATA(-) pins form a differential driver output, this is used to drive AMI data down the line via a transformer. The TX DATA(+) and TX DATA(-) pins are open-collector outputs.

When a logic "high" signal is applied to the TPOS pin, a positive pulse (the positive portion of the bipolar data stream) will be transmitted to the line via the TX DATA(+) O/P and TX DATA(-) O/P pins. Likewise, when a logic "high" signal is applied to the TNEG pin, a negative pulse will be transmitted to the line via the TX DATA(+) and TX DATA(-) pins. An illustration of the key waveforms involved in this TTL to AMI conversion process, in the Transmitter portion of the chip is presented in *Figure 4*.

Figure 2.

Figure 3.

Figure 4. Receiver Timing Diagram With 1-1-1-1-1 Pattern

L=Tank Coil AIE 415-0804 (1.544 and 2.048 Mbs)

| Device | 1.544Mbs | 2.048Mbs |

|--------|----------|----------|

| L      | 60µH     | 60µH     |

| С      | 175pF    | 100pF    |

Figure 5. Application Circuit for XR-T56L85

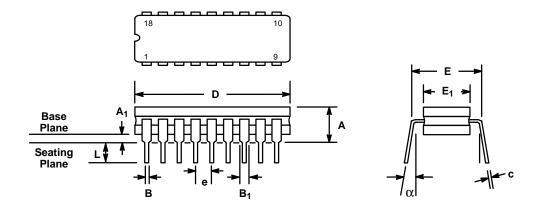

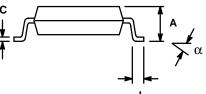

# 18 LEAD CERAMIC DUAL-IN-LINE (300 MIL CDIP)

Rev. 1.00

|                | INCHES    |              | MILLIMETERS |       |

|----------------|-----------|--------------|-------------|-------|

| SYMBOL         | MIN       | MAX          | MIN         | МАХ   |

| А              | 0.100     | 0.200        | 2.54        | 5.08  |

| A <sub>1</sub> | 0.015     | 0.070        | 0.38        | 1.78  |

| В              | 0.014     | 0.026        | 0.36        | 0.66  |

| B <sub>1</sub> | 0.045     | 0.065        | 1.14        | 1.65  |

| С              | 0.008     | 0.018        | 0.20        | 0.46  |

| D              | 0.860     | 0.960        | 21.84       | 24.38 |

| E <sub>1</sub> | 0.250     | 0.310        | 6.35        | 7.87  |

| E              | 0.300 BSC |              | 7.62 BSC    |       |

| е              | 0.100 BSC |              | 2.54 BSC    |       |

| L              | 0.125     | 0.200        | 3.18        | 5.08  |

| α              | 0°        | $15^{\circ}$ | 0°          | 15°   |

Note: The control dimension is the inch column

# 18 LEAD SMALL OUTLINE (300 MIL JEDEC SOIC)

Rev. 1.00

|                | INC   | HES    | MILLIMETERS |       |

|----------------|-------|--------|-------------|-------|

| SYMBOL         | MIN   | МАХ    | MIN         | MAX   |

| А              | 0.093 | 0.104  | 2.35        | 2.65  |

| A <sub>1</sub> | 0.004 | 0.012  | 0.10        | 0.30  |

| В              | 0.013 | 0.020  | 0.33        | 0.51  |

| С              | 0.009 | 0.013  | 0.23        | 0.32  |

| D              | 0.447 | 0.463  | 11.35       | 11.75 |

| E              | 0.291 | 0.299  | 7.40        | 7.60  |

| е              | 0.0   | 50 BSC | 1.2         | 7 BSC |

| н              | 0.394 | 0.419  | 10.00       | 10.65 |

| L              | 0.016 | 0.050  | 0.40        | 1.27  |

| α              | 0°    | 8°     | 0°          | 8°    |

Note: The control dimension is the millimeter column

Notes

Notes

# NOTICE

EXAR Corporation reserves the right to make changes to the products contained in this publication in order to improve design, performance or reliability. EXAR Corporation assumes no responsibility for the use of any circuits described herein, conveys no license under any patent or other right, and makes no representation that the circuits are free of patent infringement. Charts and schedules contained here in are only for illustration purposes and may vary depending upon a user's specific application. While the information in this publication has been carefully checked; no responsibility, however, is assumed for inaccuracies.

EXAR Corporation does not recommend the use of any of its products in life support applications where the failure or malfunction of the product can reasonably be expected to cause failure of the life support system or to significantly affect its safety or effectiveness. Products are not authorized for use in such applications unless EXAR Corporation receives, in writing, assurances to its satisfaction that: (a) the risk of injury or damage has been minimized; (b) the user assumes all such risks; (c) potential liability of EXAR Corporation is adequately protected under the circumstances.

Copyright 1992 EXAR Corporation Datasheet June 1997 Reproduction, in part or whole, without the prior written consent of EXAR Corporation is prohibited.