# F<sup>2</sup>MC-8L FAMILY MICROCONTROLLERS

MB89150/150A SERIES HARDWARE MANUAL

# 1. GENERAL

| I.1 Features                 | . 1-3  |

|------------------------------|--------|

| I.2 Product Series           | . 1-4  |

| I.3 Block Diagram            | . 1-5  |

| I.4 Pin Assignment           | . 1-6  |

| 1.5 Pin Function Description | . 1-10 |

| I.6 Handling Devices         | . 1-15 |

The MB89150 and MB89150A series microcontrollers contain various resources such as an LCD controller/driver, timers, serial interfaces, a remote-control carrier frequency generator, and external interrupts, including the compact instruction system.

### 1.1 Features

- CPU core common to MB89600 series

- Double-clock pulse control

- Maximum memory space: 64K bytes

- Minimum instruction execution time: 0.95 μs at 4.2 MHz

- I/O ports: Max. 43

- 21-bit time-base counter

- 8/16-bit PWM timer/counter: 1 channel

- 8-bit serial I/O: 1 channel

- External interrupt input: 4 pins (Edge selection enabled) + 8 pins (Level interrupt)

- Buzzer output

- 15-bit watch prescaler

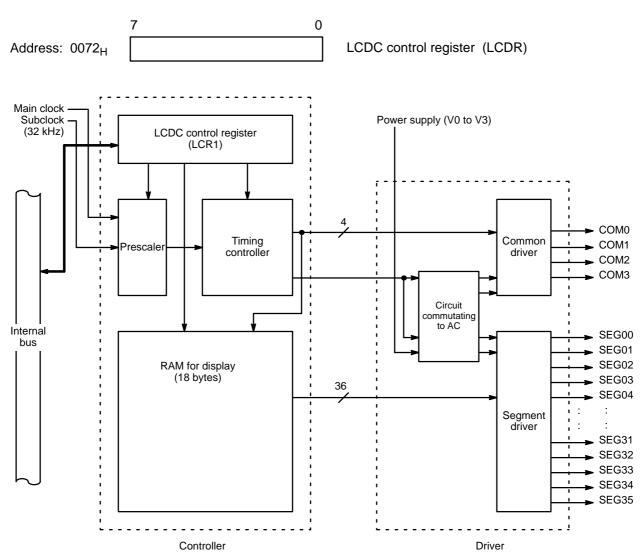

- LCD controller/driver with 36 segment outputs x 4 common outputs (max. 144 pixels)

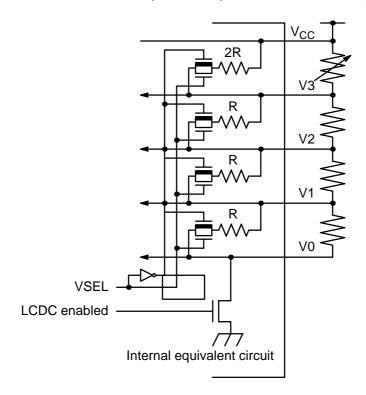

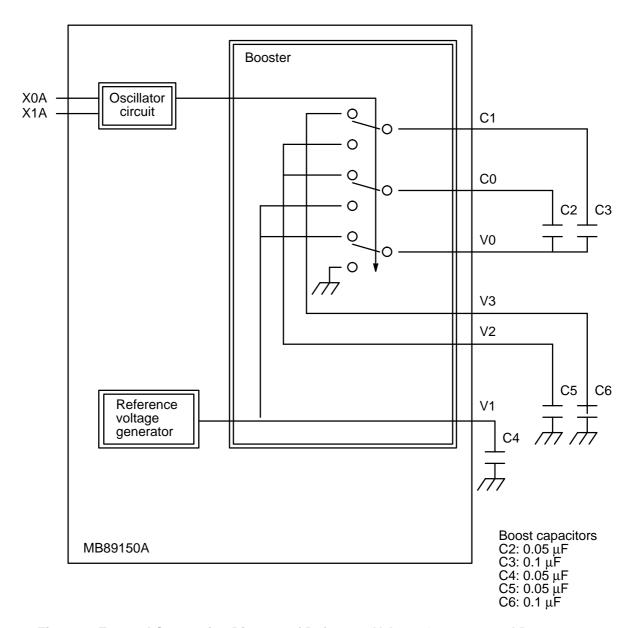

- Built-in reference voltage generator and booster for driving LCD

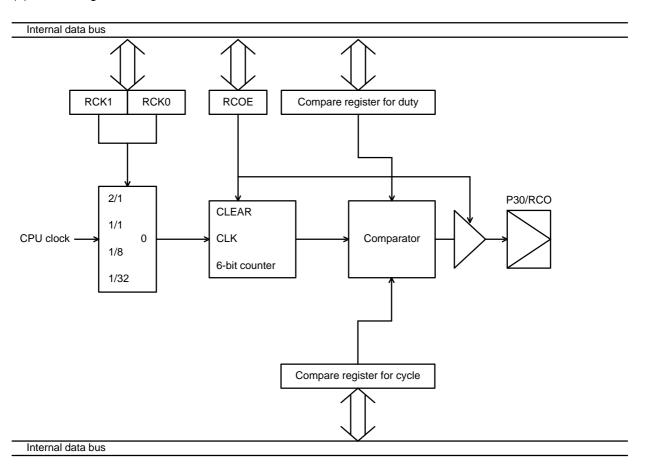

- Built-in remote-control carrier frequency generator

- Internal power-on reset

- Low-power consumption modes (stop mode, sleep mode and watch mode)

- Package: QFP-80, SQFP-80

- CMOS technology

### 1.2 Product Series

Table 1-1 lists the types and functions of the MB89150 series of microcontrollers.

Table 1-1 Types and Functions of MB89150 Series of Microcontrollers

| Model Name                       | MB89151/A                                                                         | MB89152/A                                                                                                                                                                                                                                    | MB89153/A        | MB89154/A        | MB89155/A         | MB89P155/A      | MB89PV150                          |  |  |  |

|----------------------------------|-----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------|-------------------|-----------------|------------------------------------|--|--|--|

| Classification                   | Mass-produced product (mask ROM product)  Temporary product (small scale product) |                                                                                                                                                                                                                                              |                  |                  |                   |                 |                                    |  |  |  |

| ROM capacity                     | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                            |                                                                                                                                                                                                                                              |                  |                  |                   |                 | 32 K × 8 bits<br>(External<br>ROM) |  |  |  |

| RAM capacity                     | 128 × 8 bits                                                                      |                                                                                                                                                                                                                                              |                  | 256 × 8 b        | its               |                 | 512 × 8 bits                       |  |  |  |

| CPU functions                    |                                                                                   | Number of basic instructions Instruction bit length Instruction length Data bit length Minimum instruction execution time Interrupt processing time  Number of basic instructions 8 bits 1 to 3 bytes 1 to 3 bytes 1 to 3 bytes 9 us/4.2 MHz |                  |                  |                   |                 |                                    |  |  |  |

| Port                             | I/O port (N<br>Output port<br>I/O port (O<br>Output por<br>Total                  | ırrent                                                                                                                                                                                                                                       |                  |                  |                   |                 |                                    |  |  |  |

| Timer counter                    |                                                                                   | 2 channels f                                                                                                                                                                                                                                 | or 8-bit timer c | ounter or 1 cha  | annel for 16-bi   | t event counter |                                    |  |  |  |

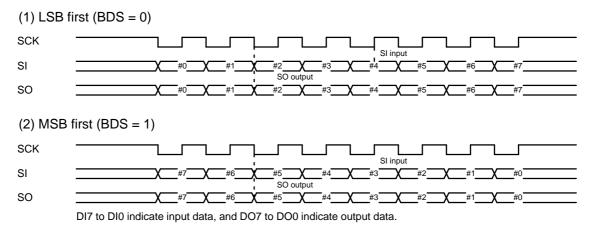

| Serial I/O                       | 8-bit lengtl<br>Selectable                                                        |                                                                                                                                                                                                                                              | nificant bit (LS | B) first or most | t significant bit | (MSB) first     |                                    |  |  |  |

| LCD controller<br>and driver     | Common of<br>Segment of<br>Biased po<br>RAM capa<br>Built-in ref<br>Built-in div  | Reference<br>voltage<br>generator<br>and booster<br>for driving<br>LCD not<br>built in                                                                                                                                                       |                  |                  |                   |                 |                                    |  |  |  |

| Number of external interrupts    | 4 (selectal<br>8 (interrup                                                        | ole from rising<br>t for level only                                                                                                                                                                                                          | edge, falling e  | dge, or both ed  | dges)             |                 |                                    |  |  |  |

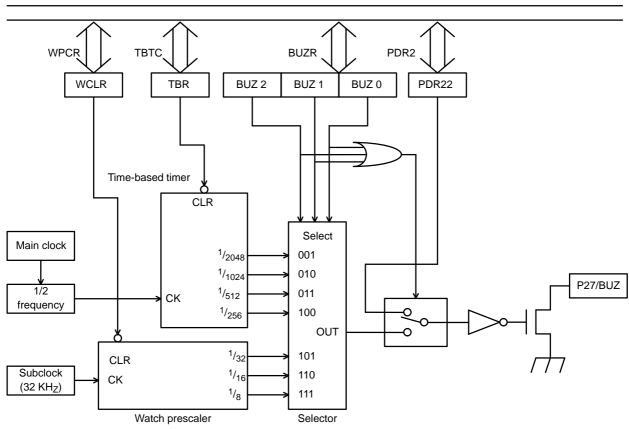

| Buzzer output                    | 1 (7-type f                                                                       | requencies ar                                                                                                                                                                                                                                | e programmab     | le)              |                   |                 |                                    |  |  |  |

| Remote-control carrier frequency | 1 (pulse width and cycle are programmable)                                        |                                                                                                                                                                                                                                              |                  |                  |                   |                 |                                    |  |  |  |

| Standby mode                     | Watch, sub, sleep, and stop modes                                                 |                                                                                                                                                                                                                                              |                  |                  |                   |                 |                                    |  |  |  |

| Process                          | CMOS                                                                              |                                                                                                                                                                                                                                              |                  |                  |                   |                 |                                    |  |  |  |

| Package*1                        | QFP-80, SQFP-80                                                                   |                                                                                                                                                                                                                                              |                  |                  |                   |                 |                                    |  |  |  |

| Operating voltage*2              | 2.2 to 6.0 V 2.7 to 6.0 V                                                         |                                                                                                                                                                                                                                              |                  |                  |                   |                 |                                    |  |  |  |

| EMROM used                       |                                                                                   |                                                                                                                                                                                                                                              | MBM              | 127C256A-25 (    | LCC package)      | )               |                                    |  |  |  |

<sup>\*1:</sup> Refer to the data sheet for the detail of each package

1-4

<sup>\*2:</sup> Operating voltage varies depending to the condition such as frequency or others. Operation under 2.2 volt will be provided individually.

<sup>\*3:</sup> Selected by the mask option.

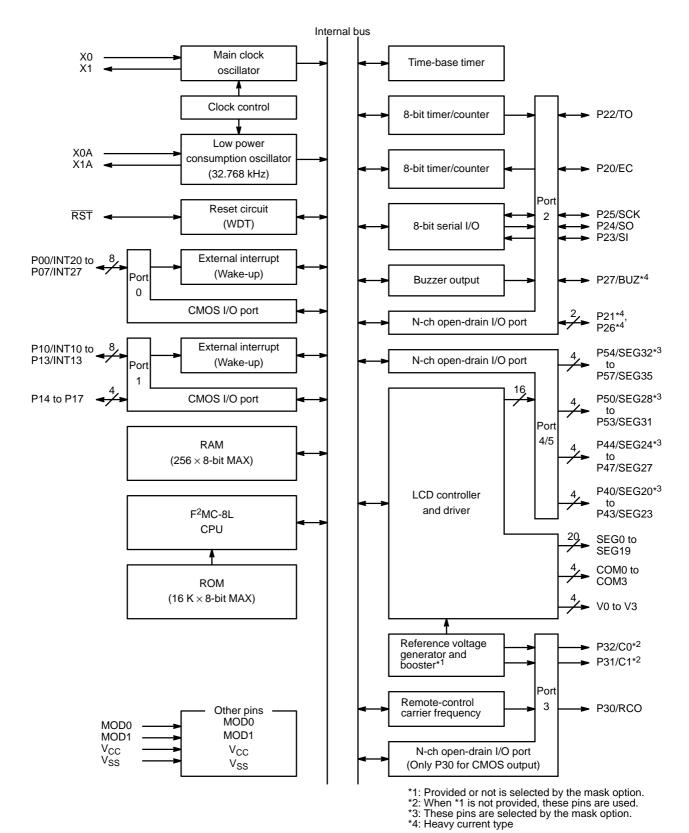

### 1.3 Block Diagram

Fig. 1.1 Block Diagram (Mass-produced product)

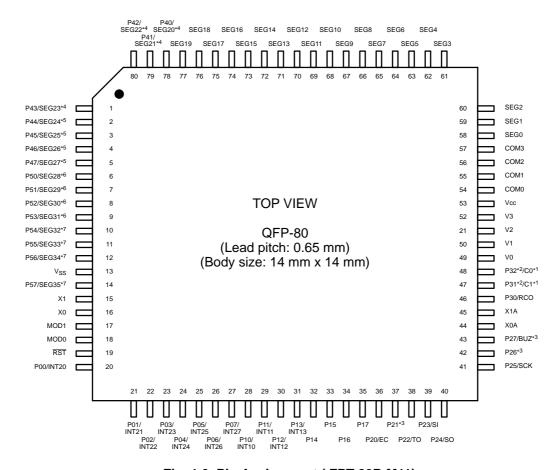

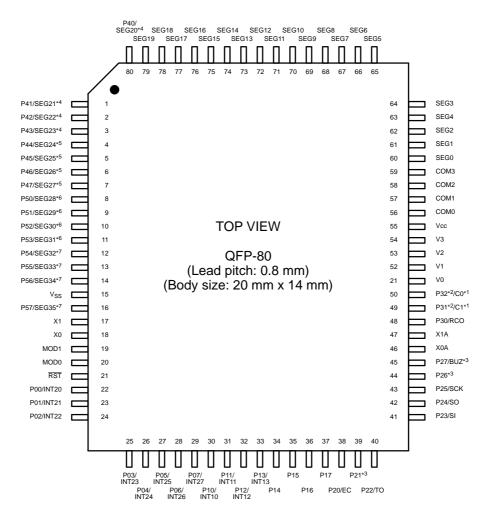

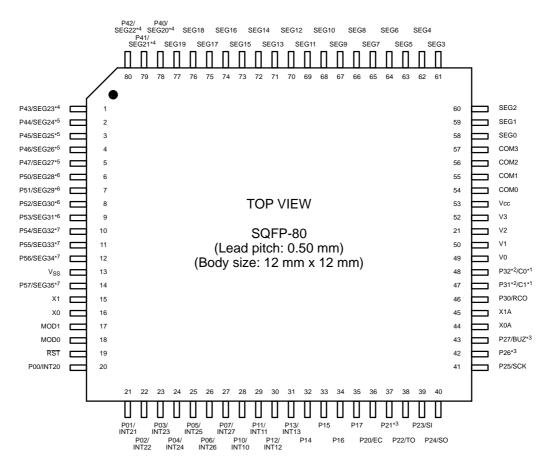

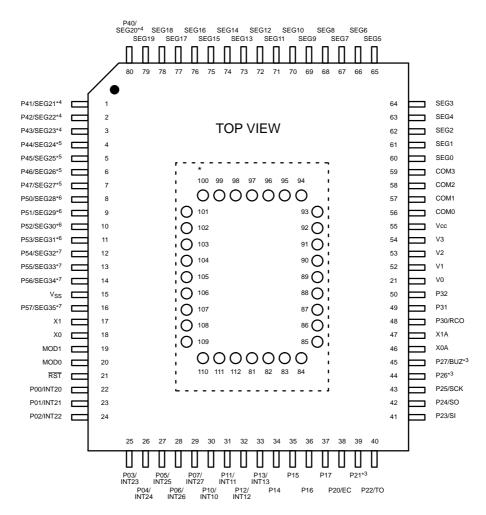

### 1.4 Pin Assignment

The production of this type is under consideration

Model with this pin assignment: MB8915X/P155

Fig. 1.2 Pin Assignment (FPT-80P-M11)

- \*1: Microcontrollers with built-in booster

- \*2: Microcontrollers without built-in booster

- \*3: N-ch open-drain heavy current type

- \*4 to \*7: These pins are selected by the mask option at four pins.

Model with this pin assignment: MB8915X/P155

Fig. 1.3 Pin Assignment (FPT-80P-M06)

- \*1: Microcontrollers with built-in booster

- \*2: Microcontrollers without built-in booster

- \*3: N-ch open-drain heavy current type

- \*4 to \*7: These pins are selected by the mask option at four pins.

Model with this pin assignment: MB8915X/P155

Fig. 1.4 Pin Assignment (FPT-80P-M05)

- \*1: Microcontrollers with built-in booster

- \*2: Microcontrollers without built-in booster

- \*3: N-ch open-drain heavy current type

- \*4 to \*7: These pins are selected by the mask option at four pins.

Model with this pin assignment: MB8915X/P155

Fig. 1.5 Pin Assignment (MQP-80C-P01)

\*3: N-ch open-drain heavy current type

\*4 to \*7: These pins are selected by the mask option at four pins.

## 1.5 Pin Function Description

Table 1-2 and Table 1-3 lists the pin function and Table 1-3 shows the input/output circuit configurations.

**Table 1-2 Pin Function Description**

| Pin No.  |          |                              | Cinavit         |                                                                                                                                                                                                              |  |

|----------|----------|------------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| QFP 0.65 | QFP 0.80 | Pin Name                     | Circuit<br>type | Function                                                                                                                                                                                                     |  |

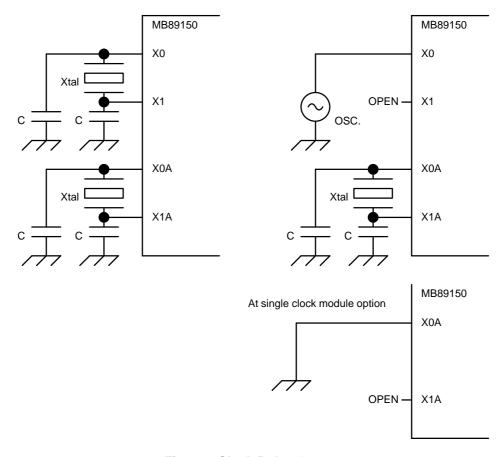

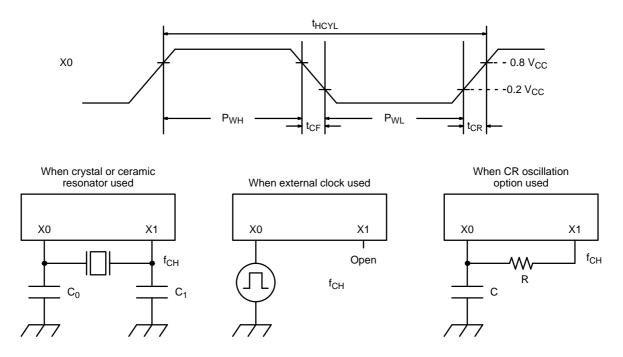

| 16       | 18       | X0                           | ^               | Crystal oscillator pins for main clock (Max. 10 MHz)                                                                                                                                                         |  |

| 15       | 17       | X1                           | A               | CR oscillation available (only for mask product)                                                                                                                                                             |  |

| 18       | 20       | MOD0                         | В               | Operation-mode select pins These pins are connected directly to V <sub>SS</sub> .                                                                                                                            |  |

| 17       | 19       | MOD1                         | В               | These pins are connected directly to V <sub>SS</sub> .                                                                                                                                                       |  |

| 19       | 21       | RSTX                         | С               | Reset I/O pin This pin consists of an N-ch open-drain output with a pull-up resistor and hysteresis input. A Low level is output from this pin. The internal circuit is initialized at input of a Low level. |  |

| 20 to 27 | 22 to 29 | P00/INT20<br>to<br>P07/INT27 | D               | General-purpose I/O ports These ports also serve as external interrupt 2 input (wake-up input) pins. Input is hysteresis type.                                                                               |  |

| 28 to 31 | 30 to 33 | P10/INT10<br>to<br>P13/INT13 | D               | General-purpose I/O ports  These ports also serve as pins for input of external interrupt 1. Input of external interrupt 1 is hysteresis type.                                                               |  |

| 32 to 35 | 34 to 37 | P14 to P17                   | Е               | General-purpose I/O port                                                                                                                                                                                     |  |

| 36       | 38       | P20/EC                       | G               | N-ch open-drain type general-purpose I/O port This port also serves as an external clock input pin for the timer. The resource is hysteresis input.                                                          |  |

| 37       | 39       | P21                          | Н               | N-ch open-drain type general-purpose I/O port                                                                                                                                                                |  |

| 38       | 40       | P22/TO                       | Н               | N-ch open-drain type general-purpose I/O port This port also serves as an timer output pin                                                                                                                   |  |

| 39       | 41       | P23/SI                       | G               | N-ch open-drain type general-purpose I/O port This port also serves as an serial I/O data input pin. The resource is hysteresis input                                                                        |  |

| 40       | 42       | P24/SO                       | Н               | N-ch open-drain type general-purpose I/O port This port also serves as an serial I/O data output pin.                                                                                                        |  |

| 41       | 43       | P25/SCK                      | G               | N-ch open-drain type general-purpose I/O port This port also serves as an serial I/O clock output pin. The resource is hysteresis input                                                                      |  |

| 42       | 44       | P26                          | Н               | N-ch open-drain type general-purpose I/O port                                                                                                                                                                |  |

| 43       | 45       | P27/BUZ                      | Н               | N-ch open-drain type general-purpose I/O port This port also serves as an buzzer output pin                                                                                                                  |  |

| 48       | 50       | P32                          | I               | This port serves as an N-ch open-drain type general-purpose output port only for microcontrollers without built-in booster.                                                                                  |  |

| 70       | 50       | C0                           | _               | This port serves as a capacitor connecting pin for microcontrollers with a built-in booster.                                                                                                                 |  |

| 47       | 49       | P31                          | I               | This port serves as an N-ch open-drain type general-purpose output port only for microcontrollers without a built-in booster.                                                                                |  |

| 71       | 70       | C1                           | _               | This port serves as a capacitor connecting pin for microcontrollers with a built-in booster.                                                                                                                 |  |

(Continued)

1-10

| Pin                  | No.                  |                              | Circuit |                                                                                                                                                   |

|----------------------|----------------------|------------------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| QFP 0.65             | QFP 0.80             | Pin Name                     | type    | Function                                                                                                                                          |

| 46                   | 48                   | P30/RCO                      | F       | General-purpose output-only port This port also serves as a remote-control carrier frequency output pin.                                          |

| 14 to 6              | 16 to 8              | P57/SEG35<br>to<br>P50/SEG28 | I/J     | N-ch open-drain type general-purpose output ports These ports also serve as LCDC segment output pins. They should be switched by the mask option. |

| 5 to 78              | 7 to 80              | P47/SEG27<br>to<br>P40/SEG20 | I/J     | N-ch open-drain type general-purpose output ports These ports also serve as LCDC segment output pins. They should be switched by the mask option. |

| 58 to 77             | 60 to 79             | SEG0 to<br>SEG19             | J       | LCDC segment output-only pins                                                                                                                     |

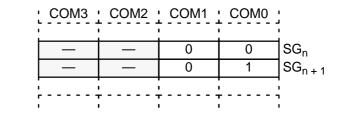

| 57<br>56<br>55<br>54 | 59<br>58<br>57<br>56 | COM3<br>COM2<br>COM1<br>COM0 | J       | LCDC common output-only pins                                                                                                                      |

| 52<br>51<br>50<br>49 | 54<br>53<br>52<br>51 | V3<br>V2<br>V1<br>V0         | _       | Power pins for driving LCD                                                                                                                        |

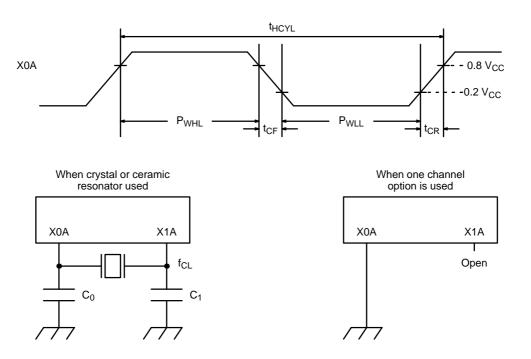

| 44                   | 46                   | X0A                          | A'      | Low-speed clock pulse oscillation pin (32 KHz)                                                                                                    |

| 45                   | 47                   | X1A                          |         | 2011 Speed Stook pulse oscillation pill (oz 1412)                                                                                                 |

| 53                   | 55                   | V <sub>CC</sub>              |         | Power pin                                                                                                                                         |

| 13                   | 15                   | V <sub>SS</sub>              | _       | Power (GND) pin                                                                                                                                   |

Table 1-3 Pins for External ROM

| Pin No.                                      |                                                     |              |                                                                     |

|----------------------------------------------|-----------------------------------------------------|--------------|---------------------------------------------------------------------|

| QFP 0.80                                     | Pin Name                                            | Circuit type | Function                                                            |

| 82                                           | $V_{PP}$                                            | Output       | High-level output pin                                               |

| 83<br>84<br>85<br>86<br>87<br>88<br>89<br>90 | A12<br>A7<br>A6<br>A5<br>A4<br>A3<br>A2<br>A1<br>A0 | Output       | Address-output pins                                                 |

| 93<br>94<br>95                               | 01<br>02<br>03                                      | Input        | Data-input pins                                                     |

| 96                                           | V <sub>SS</sub>                                     | Output       | Power (GND) pin                                                     |

| 98<br>99<br>100<br>101<br>102                | 04<br>05<br>06<br>07<br>08                          | Input        | Data-input pins                                                     |

| 103                                          | CEX                                                 | Output       | Chip-enable pin for ROM A High level is output in the standby mode. |

| 104                                          | A10                                                 | Output       | Address-output pin                                                  |

| 105                                          | OEX                                                 | Output       | Output-enable pin for ROM A Low level is always output.             |

| 107<br>108<br>109                            | A11<br>A9<br>A8                                     | Output       | Address-output pins                                                 |

| 110                                          | A13                                                 | Output       | Address-output pin                                                  |

| 111                                          | A14                                                 | Output       | Address-output pin                                                  |

| 112                                          | V <sub>CC</sub>                                     | Output       | Power pin for EPROM                                                 |

| 81<br>92<br>97<br>106                        | NC                                                  | _            | Internal-connection pins. These pins must always be kept open.      |

**Table 1-4 Input/Output Circuit Configurations**

| Classification | Circuit                                  | Remarks                                                                                                                       |

|----------------|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| А              | X1<br>X0<br>X0<br>Standby control signal | Used for high speed pulse • Feedback resistor: About 2 MΩ                                                                     |

| A'             | Standby control signal                   | Used for low speed pulse                                                                                                      |

| В              |                                          | Hysteresis input                                                                                                              |

| С              | R Pch                                    | <ul> <li>Output pull-up resistor (P-ch): About 50 kΩ (5 V)</li> <li>Hysteresis input</li> </ul>                               |

| D              | Pch Nch Port Resource                    | CMOS input/output     The resource is hysteresis input.      The pull-up resistor is available (not available for MB89PV150). |

| E              | Pch                                      | CMOS input/output      The pull-up resistor is available (not available for MB89PV150).                                       |

(Continued)

| Classification | Circuit     | Remarks                                                                                                                                                                                                                   |

|----------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| F              | Pch         | CMOS output     Pch is driven with heavy current                                                                                                                                                                          |

| G              | Nch         | N-ch open-drain input/output CMOS input The resource is hysteresis input.                                                                                                                                                 |

|                | Resource    | The pull-up resistor is available (not available for<br>MB89P155 and MB89PV150).                                                                                                                                          |

| Н              | Nch         | <ul> <li>N-ch open-drain input/output</li> <li>CMOS input</li> <li>P21, P26, and P27 are heavy-current drive type pins.</li> <li>The pull-up resistor is available (not available for MB89P155 and MB89PV150).</li> </ul> |

|                |             | N-ch open-drain output                                                                                                                                                                                                    |

| l              | Nch         | The pull-up resistor is available (not available for MB89P155 and MB89PV150). P31 and P32 are not provided with a resistor.                                                                                               |

| J              | Pch Nch Nch | LCDC segment output                                                                                                                                                                                                       |

### 1.6 Handling Devices

### (1) Preventing latch-up

Latch-up may occur if a voltage higher than  $V_{CC}$  or lower than Vss is applied to the input or output pins other than port 4, or if voltage exceeding the rated value is applied between  $V_{CC}$  and  $V_{SS}$ .

When latch-up occurs, the supply current increases rapidly, sometimes resulting in overheating and destruction. Therefore, no voltage exceeding the maximum ratings should be used.

### (2) Handling unused input pins

Leaving unused input pins open may cause a malfunction. Therefore, these pins should be set to pull-up or pull-down.

(3) Always set NC (internal connections) open.

### (4) Variations in supply voltage

Although the specified  $V_{CC}$  supply voltage operating range is assured, a sudden change in the supply voltage within the specified range may cause a malfunction. Therefore, the voltage supply to the IC should be kept as constant as possible. The  $V_{CC}$  ripple (P-P value) at the supply frequency (50 - 60 Hz) should be less than 10% of the typical  $V_{CC}$  value, or the coefficient of excessive variation should be 0.1 V/ms max. instantaneous change when the power supply is switched.

### (5) Precautions for external clocks

It takes some time for oscillation to stabilize after changing the mode to power-on reset (option selection) and stop. Consequently, an external clock must be input.

# 2. HARDWARE CONFIGURATION

2.1 CPU

2-3

2.2 Resource Functions

2-22

### 2.1 CPU

This section describes the CPU hardware composition. The CPU has the following six functions.

- Memory Space

- Arrangement of 16-bit Data in Memory

- Registers

- Operation Modes

- Clock Control Block

- Interrupt Controller

### 2.1.1 Memory space

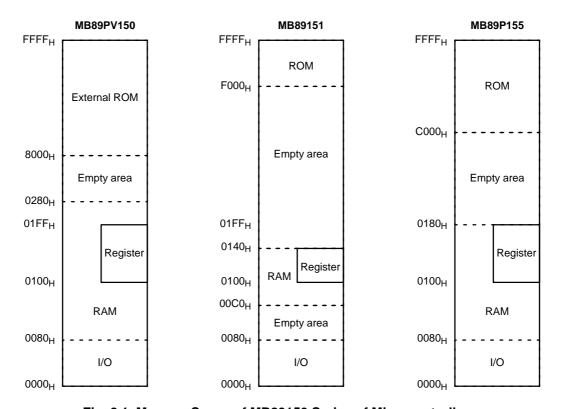

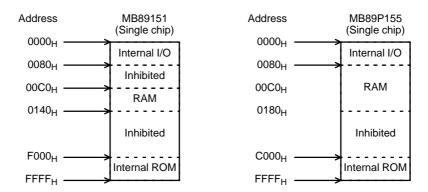

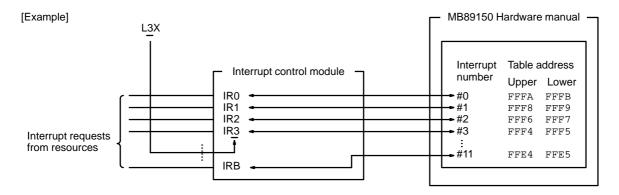

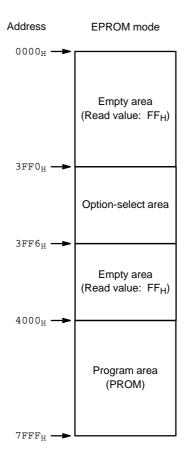

The MB89150 series of microcontrollers have a memory area of 64K bytes. All I/O, data, and program areas are located in this space. The I/O area is near the lowest address and the data area is immediately above it. The data area may be divided into register, stack, and direct-address areas according to the applications. The program area is located near the highest address and the tables of interrupt and reset vectors and vector-call instructions are at the highest address. Figure 2.1 shows the structure of the memory space for the MB89150 series of microcontrollers.

Fig. 2.1 Memory Space of MB89150 Series of Microcontrollers

### (1) I/O area

This area is where various resources such as control and data registers are located. The memory map for the I/O area is given in APPENDIX A.

### (2) RAM area

This area is where the static RAM is located. Addresses from  $0100_{\rm H}$  to  $017F_{\rm H}$  are also used as the general-purpose register area.

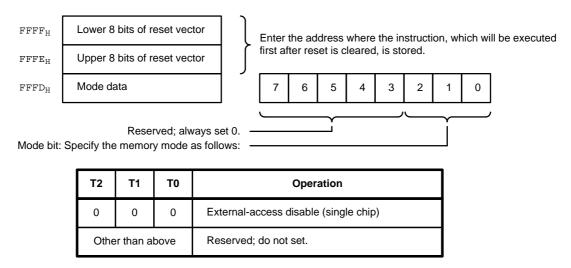

### (3) ROM area

This area is where the internal ROM is located. Addresses from  $\mathtt{FFD0}_\mathtt{H}$  to  $\mathtt{FFFF}_\mathtt{H}$  are also used for the table of interrupt and reset and vector-call instructions. Fig. 2.2 shows the correspondence between each interrupt number or reset and the table addresses to be referenced for the MB89150 series of microcontrollers.

|          | Table address     |                   |  |  |  |

|----------|-------------------|-------------------|--|--|--|

|          | Upper data        | Lower data        |  |  |  |

| CALLV #0 | FFC0 <sub>H</sub> | $FFC1_{H}$        |  |  |  |

| CALLV #1 | FFC2 <sub>H</sub> | FFC3 <sub>H</sub> |  |  |  |

| CALLV #2 | FFC4 <sub>H</sub> | FFC5 <sub>H</sub> |  |  |  |

| CALLV #3 | FFC6 <sub>H</sub> | FFC7 <sub>H</sub> |  |  |  |

| CALLV #4 | FFC8 <sub>H</sub> | FFC9 <sub>H</sub> |  |  |  |

| CALLV #5 | FFCA <sub>H</sub> | FFCB <sub>H</sub> |  |  |  |

| CALLV #6 | $FFCC_H$          | FFCD <sub>H</sub> |  |  |  |

| CALLV #7 | FFCE <sub>H</sub> | FFCF <sub>H</sub> |  |  |  |

|               |                              | -                            |  |  |  |  |

|---------------|------------------------------|------------------------------|--|--|--|--|

|               | Table address                |                              |  |  |  |  |

|               | Upper data                   | Lower data                   |  |  |  |  |

| Interrupt #11 | FFE4 <sub>H</sub>            | FFE5 <sub>H</sub>            |  |  |  |  |

| Interrupt #10 | FFE6 <sub>H</sub>            | FFE7 <sub>H</sub>            |  |  |  |  |

| Interrupt #9  | FFE8 <sub>H</sub>            | FFE9 <sub>H</sub>            |  |  |  |  |

| Interrupt #8  | FFEA <sub>H</sub>            | FFEB <sub>H</sub>            |  |  |  |  |

| Interrupt #7  | FFEC <sub>H</sub>            | FFED <sub>H</sub>            |  |  |  |  |

| Interrupt #6  | FFEE <sub>H</sub>            | FFEF <sub>H</sub>            |  |  |  |  |

| Interrupt #5  | FFF0 <sub>H</sub>            | FFF1 <sub>H</sub>            |  |  |  |  |

| Interrupt #4  | FFF2 <sub>H</sub>            | FFF3 <sub>H</sub>            |  |  |  |  |

| Interrupt #3  | FFF4 <sub>H</sub>            | FFF5 <sub>H</sub>            |  |  |  |  |

| Interrupt #2  | FFF6 <sub>H</sub>            | FFF7 <sub>H</sub>            |  |  |  |  |

| Interrupt #1  | FFF8 <sub>H</sub>            | FFF9 <sub>H</sub>            |  |  |  |  |

| Interrupt #0  | $FFFA_H$                     | FFFB <sub>H</sub>            |  |  |  |  |

| Reset mode    |                              | $FFFD_H$                     |  |  |  |  |

| Reset vector  | $\mathtt{FFFE}_{\mathtt{H}}$ | $\mathtt{FFFF}_{\mathtt{H}}$ |  |  |  |  |

Note:  $\mathtt{FFFC}_{\mathtt{H}}$  is already reserved.

Fig. 2.2 Table of Reset and Interrupt Vectors

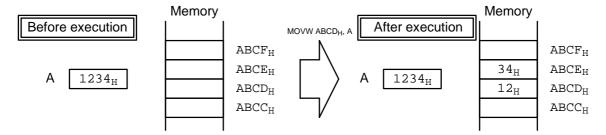

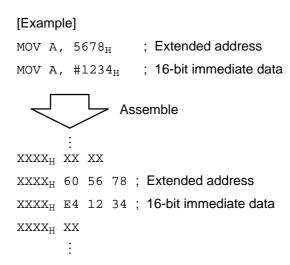

### 2.1.2 Arrangement of 16-bit data in memory

When the MB89150 series of microcontrollers handle 16-bit data, the data written at the lower address is treated as the upper data and that written at the next address is treated as the lower data as shown in Figure 2.3.

Fig. 2.3 Arrangement of 16-bit Data in Memory

This is the same as when 16 bits are specified by the operand during execution of an instruction. Bits closer to the OP code are treated as the upper byte and those next to it are treated as the lower byte. This is also the same when the memory address or 16-bit immediate data is specified by the operand.

Fig. 2.4 Arrangement of 16-bit Data during Execution of Instruction

Data saved in the stack by an interrupt is also treated in the same manner.

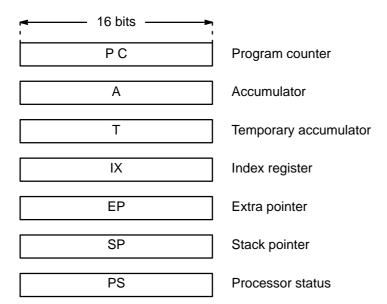

### 2.1.3 Internal registers in CPU

The MB89150 series of microcontrollers have dedicated registers in the CPU and general-purpose registers in memory.

<Dedicated registers>

Program counter (PC)

16-bit long register indicating location where instructions stored

• Accumulator (A) 16-bit long register where results of operations stored temporarily; the lower

byte is used to execute 8-bit data processing instructions.

• Temporary accumulator (T) 16-bit long register; the operations are performed between this register and

the accumulator. The lower one byte is used to execute 8-bit data processing

instructions

Stack pointer (SP)

16-bit long register indicating stack area

Processor status (PS)

16-bit long register where register pointers and condition codes stored

• Index register (IX)

16-bit long register for index modification

• Extra pointer (EP) 16-bit long register for memory addressing

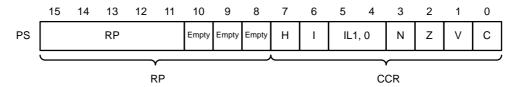

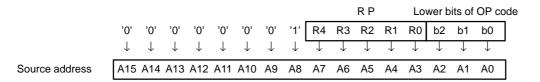

The 16 bits of the program status (PS) can be divided into 8 upper bits for a register bank pointer (RP) and 8 lower bits for a condition code register (CCR). (See Figure 2.5.)

Fig. 2.5 Structure of Processor Status

The RP indicates the address of the current register bank and the contents of the RP; the real addresses are translated as shown in Figure 2.6.

Fig. 2.6 Rule for Translating Real Addresses at General-purpose Register Area

The CCR has bits indicating the results of operations and transfer data contents, and bits controlling the CPU operation when an interrupt occurs.

- H-flag: H-flag is set when a carry or a borrow out of bit 3 into bit 4 is generated as a result of operations; it is cleared in other cases. This flag is used for decimal-correction instructions.

- I-flag: An interrupt is enabled when this flag is 1 and is disabled when it is 0. The I-flag is 0 at reset.

- IL1 and IL0: These bits indicate the level of the currently-enabled interrupt. The CPU executes interrupt

processing only when an interrupt with a value smaller than the value indicated by this bit is

requested.

| IL1 | IL0 | Interrupt level | High and low       |

|-----|-----|-----------------|--------------------|

| 0   | 0   | 1               | High               |

| 0   | 1   |                 | <b>1</b>           |

| 1   | 0   | 2               |                    |

| 1   | 1   | 3               | Low = No interrupt |

- N-flag: The N-flag is set when the most significant bit is 1 as a result of operations; it is cleared when the MSB is 0.

- Z-flag: Z-flag is set when the bit is 0 as a result of operations; it is cleared in other cases.

- V-flag: V-flag is set when a two's complement overflow occurs as a result of operations; it is reset when an overflow does not occur.

- C-flag: C-flag is set when a carry or a borrow out of bit 7 is generated as a result of operations; it is

cleared in other cases. When the shift instruction is executed, the value of the C-flag is shifted

out.

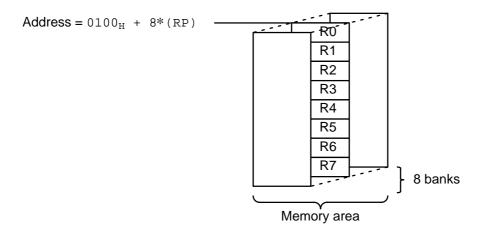

<General-purpose registers>

General-purpose registers are 8-bit long registers for storing data.

The 8-bit long general-purpose registers are in the register banks in memory. One bank has eight registers and up to 32 banks are available for the MB89151 series of microcontrollers. The register bank pointer (RP) indicates the currently-used bank.

Note: The number of register banks used depends on the RAM capacity.

Fig. 2.7 Register Bank Configuration

### 2.1.4 Operation modes and external bus operation

The MB89150 series of microcontrollers have only single-chip mode.

The memory map is as follows:

Fig. 2.8 Memory Maps in Various Modes

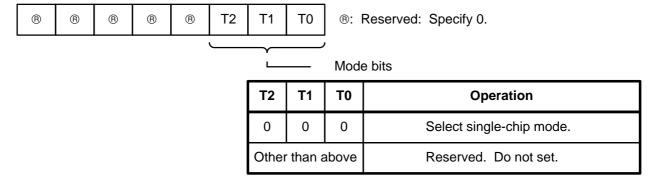

The relationship between the states and operations of the device-mode pins is shown below. (Only 00 can be set for MB89150.)

| MOD1 | MOD0 | Description                                                                          |  |  |  |  |  |  |

|------|------|--------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 0    | 0    | Reset vectors are read from the internal ROM. The external access does not function. |  |  |  |  |  |  |

| 1    | 1    | Write mode for products containing EPROM.                                            |  |  |  |  |  |  |

The following functions are selected according to the mode-data setting conditions.

Note: Do not select the single-chip mode with the externally-fetched mode data.

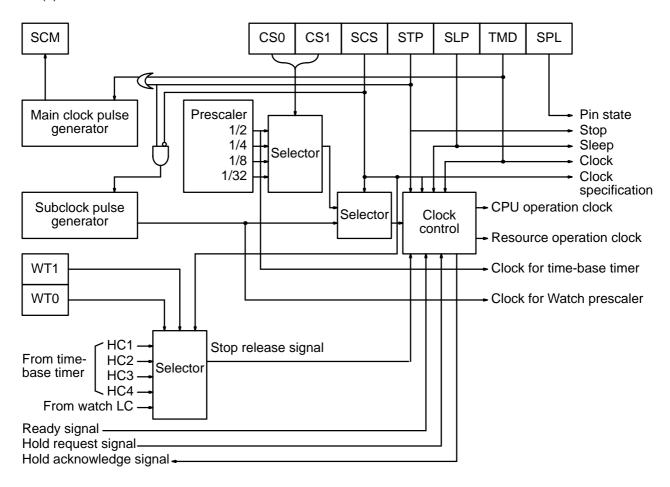

### 2.1.5 Clock control block

This block controls the standby operation, oscillation stabilization time, software reset, and clock switching.

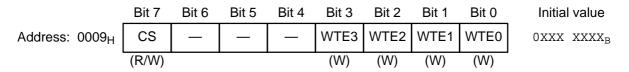

### (1) Register list

|                            | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | System clock                    |

|----------------------------|-------|-------|-------|-------|-------|-------|-------|-------|---------------------------------|

| Address: 0007 <sub>H</sub> | SCM   |       | 1     | WT1   | WT0   | SCS   | CS1   | CS0   | control register<br>(SYCC)      |

|                            |       |       |       |       |       |       |       |       | (0100)                          |

| Address: 0008 <sub>H</sub> | STP   | SLP   | SPL   | RST   | TMD   | 1     |       | _     | Standby control register (STBC) |

### (2) Block diagram

(a) Machine clock control section

### (b) Reset control section

### (3) Description of registers

### (a) STBC (Standby-conrol register)

|                            | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Initial value          |

|----------------------------|-------|-------|-------|-------|-------|-------|-------|-------|------------------------|

| Address: 0008 <sub>H</sub> | STP   | SLP   | SPL   | RST   | TMD   |       | 1     |       | 0001 0XXX <sub>B</sub> |

|                            | (W)   | (W)   | (R/W) | (W)   | (W)   |       |       |       | •                      |

[Bit 7] STP: Stop bit

Bit 7 specifies switching to the stop mode.

| 0 | No operation |

|---|--------------|

| 1 | Stop mode    |

This bit is cleared at reset or stop cancellation.

0 is always read when this bit is read.

[Bit 6] SLP: Sleep bit

Bit 6 specifies switching to the sleep mode.

| 0 | No operation |

|---|--------------|

| 1 | Sleep mode   |

This bit is cleared at reset or stop cancellation.

0 is always read when this bit is read.

[Bit 5] SPL: Pin state specifying bit

Bit 5 specifies the external pin state in the watch or stop mode.

| 0 | Holds state and level immediately before watch or stop mode |

|---|-------------------------------------------------------------|

| 1 | High impedance                                              |

This bit is cleared at resetting.

[Bit 4] RST: Software reset bit Bit 4 resets the software.

| 0 | Generates 4-cycle reset signal |

|---|--------------------------------|

| 1 | No operation                   |

1 is always read when this bit is read.

If a software reset is performed during operation in a submode, one oscillation stabilization period is required to switch to the main mode. Therefore, a reset signal is output during the oscillation stabilization period.

### HARDWARE CONFIGURATION

[Bit 3] TMD: Watch bit

Bit 3 specifies switching to the watch mode.

| 0 | No operation |

|---|--------------|

| 1 | Watch mode   |

Writing at this bit is possible only in the submode (SCS = 0). 0 is always read when this bit is read. This bit is cleared at an interrupt request or reset.

### (b) System clock control register (SYCC)

|                            | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Initial value        |

|----------------------------|-------|-------|-------|-------|-------|-------|-------|-------|----------------------|

| Address: 0007 <sub>H</sub> | SCM   | _     | _     | WT1   | WT0   | scs   | CS1   | CS0   | XM M100 <sub>B</sub> |

|                            | (R)   |       |       | (R/W) | (R/W) | (R/W) | (R/W) | (R/W) |                      |

[Bit 7] SCM: System clock monitor bit

Bit 7 checks whether the current system clock is the main clock or subclock.

| 0 | Subclock (Main clock is stopping or oscillation of main clock stable) |

|---|-----------------------------------------------------------------------|

| 1 | Main clock                                                            |

[Bits 4 and 3] WT1 and WT0: Oscillation stabilization time select bits

Bits 4 and 3 select the oscillation stabilization wait time of the main clock.

| WT1 | WT0 | Oscillation stabilization time   | Oscillation stabilization time at original oscillation of 10 MHz |

|-----|-----|----------------------------------|------------------------------------------------------------------|

| 1   | 1   | Approximate 2 <sup>18</sup> /fch | Approximate 87.4 (ms)                                            |

| 1   | 0   | Approximate 2 <sup>16</sup> /fch | Approximate 21.8 (ms)                                            |

| 0   | 1   | Approximate 2 <sup>12</sup> /fch | Approximate 1.4 (ms)                                             |

| 0   | 0   | Approximate 2 <sup>4</sup> /fch  | Approximate 0 (ms)                                               |

fch: Oscillation frequency of main clock

If the main mode is specified by the system clock select bit (SCS), the mode switches to main mode after the selected wait time has elapsed.

The initial value of this bit is determined by the mask option. Do not rewrite this bit during the oscillation stabilization period nor rewrite it concurrently with switching from low speed to high speed.

The oscillation stabilization time of the main clock is generated by dividing down the frequency of the main clock. Since the oscillation frequency is unstable immediately after oscillation starts, use the above table.

[Bit 2] SCS: System clock select bit Bit 2 selects the system clock mode.

| 0 | Selects subclock (32 kHz) mode |

|---|--------------------------------|

| 1 | Selects main clock mode        |

[Bits 1 and 0] CS1 and CS0: System clock select bits

If the main mode is specified by the system clock select bit (SCS), the system clock is as given in the table below.

| CS1 | Cs0 | Instruction cycle | Minimum instruction execu-<br>tion time at 10 MHz |

|-----|-----|-------------------|---------------------------------------------------|

| 0   | 0   | 64/fch            | 21.3 (μs)                                         |

| 0   | 1   | 16/fch            | 5.33 (μs)                                         |

| 1   | 0   | 8/fch             | 2.67 (μs)                                         |

| 1   | 1   | 4/fch             | 1.33 (µs)                                         |

fch: frequency of main clock

### (4) Description of operation

### (a) Low-power consumption mode

This chip has three operation modes. The sleep mode, and stop mode in the table below reduce the power consumption. In the main mode, four system clocks can be selected according to the system condition to minimize power consumption.

Table 2-1 Operating State of Low-power Consumption Modes

Clock pulse Fach operating clock pulse

| Main operation | (CS1,  | Operation            |                     | pulse<br>ration     | Ea                |                  | ng clock pul<br>nain clock) | se              | Wake-up source in                                   |

|----------------|--------|----------------------|---------------------|---------------------|-------------------|------------------|-----------------------------|-----------------|-----------------------------------------------------|

| mode           | CS0)   | mode                 | Main                | Sub                 | CPU               | Time-base timer  | Each resource               | Clock           | each mode                                           |

|                | (1, 1) | RUN<br>SLEEP<br>STOP | Oscillates<br>Stops | Oscillates          | 1.5 MHz<br>Stops  | 1.5 MHz<br>Stops | 1.5 MHz<br>Stops            | 32 kHz          | Various interrupt requests External interrupt       |

| Main           | (1,0)  | RUN<br>SLEEP<br>STOP | Oscillates<br>Stops | Oscillates          | 750 kHz<br>Stops  | 1.5 MHz<br>Stops | 750 kHz<br>Stops            | 32 kHz          | Various interrupt<br>requests<br>External interrupt |

| mode           | (0,1)  | RUN<br>SLEEP<br>STOP | Oscillates<br>Stops | Oscillates          | 375 kHz<br>Stops  | 1.5 MHz<br>Stops | 375 kHz<br>Stops            | 32 kHz          | Various interrupt requests External interrupt       |

|                | (0,0)  | RUN<br>SLEEP<br>STOP | Oscillates<br>Stops | Oscillates          | 98.4 kHz<br>Stops | 1.5 MHz<br>Stops | 98.4 kHz<br>Stops           | 32 kHz          | Various interrupt<br>requests<br>External interrupt |

| Submode        | _      | RUN<br>SLEEP<br>STOP | Stops               | Oscillates<br>Stops | 32 kHz<br>Stops   | Stops            | 32 kHz<br>Stops             | 32 kHz<br>Stops | Various interrupt<br>requests<br>External interrupt |

| CLOCK<br>mode  |        |                      | Stops               | Oscillates          | Stops             | Stops            | Stops                       | 32 kHz          | Watch external interrupt                            |

- The submode stops oscillation of the main clock.

- The SLEEP mode stops only the operating clock pulse of the CPU; other operations are continued.

- The WATCH mode stops the functions of all chips other than the special resources.

- The STOP mode stops the oscillation. Data can be held with the lowest power consumption in this mode.

- For microcontrollers with a built-in booster (MB89150A), the booster stops when the mode is switched from the subclock mode to the stop mode.

### [1] WATCH mode

### • Switching to WATCH mode

- Writing 1 at the TMD bit (bit 3) of the STBC register switches the mode to WATCH mode. Writing is invalid if 1 is set at the SCS bit (bit 2) of the SYCC register.

- The WATCH mode stops all chip functions except the watch prescaler, external interrupt, and wake-up functions. Therefore, data can be held with the lowest power consumption.

- The input/output pins and output pins during the WATCH mode can be controlled by the SPL bit of the STBC register so that they are held in the state immediately before entering the WATCH mode or so that they enter the high-impedance state.

- If an interrupt is requested when 1 is written at the TMD bit, instruction execution continues without switching to the WATCH mode.

- In the WATCH mode, the values of registers and RAM immediately before entering the WATCH mode are held.

### Canceling WATCH mode

- The WATCH mode is canceled by inputting the reset signal and requesting an interrupt.

- When the reset signal is input during the WATCH mode, the CPU is switched to the reset state and the WATCH mode is canceled.

- When an interrupt higher than level 11 is requested from a resource during the WATCH mode, the WATCH mode is canceled.

- When the I flag and IL bit are enabled like an ordinary interrupt after canceling, the CPU executes the interrupt processing. When they are disabled, the CPU executes the interrupt processing from the instruction next to the one before entering the WATCH mode.

- If the WATCH mode is canceled by inputting the reset signal, the CPU is switched to the oscillation stabilization wait state. Therefore, the reset sequence is not executed unless the oscillation stabilization time is elapsed. The oscillation stabilization time will be that of the main clock selected by the WT1 and WT0 bits. However, when Power-on Reset is not specified by the mask option, the CPU is not switched to the oscillation stabilization wait state, even if the WATCH mode is canceled by inputting the reset signal.

### [2] SLEEP mode

### Switching to SLEEP mode

- Writing 1 at the SLP bit (bit 6) of the STBC register switches the mode to SLEEP mode.

- The SLEEP mode stops the CPU operating clock pulse; only the CPU stops and the resources continue to operate.

- If an interrupt is requested when 1 is written at the SLP bit (bit 6), instruction execution continues without switching to the SLEEP mode. In the SLEEP mode, the values of registers and RAM immediately before entering the SLEEP mode are held.

### Canceling SLEEP mode

- The SLEEP mode is canceled by inputting the reset signal and requesting an interrupt.

- When the reset signal is input during the SLEEP mode, the CPU is switched to the reset state and the SLEEP mode is canceled.

- When an interrupt higher than level 11 is requested from a resource during the SLEEP mode, the SLEEP mode is canceled.

- When the I flag and IL bit are enabled like an ordinary interrupt after canceling, the CPU executes the interrupt processing. When they are disabled, the CPU executes the interrupt processing from the instruction next to the one before entering the SLEEP mode.

### [3] STOP mode

- Switching to STOP mode

- Writing 1 at the STP bit (bit 7) of the STBC register switches the mode to STOP mode.

- The STOP mode varies when the main clock is operating and when the subclock is operating. When the main clock is operating: The main clock stops but the subclock does not stop. All chip functions except the watch function stop.

- When subclock is operating: Both the main clock and subclock stop. All chip functions stop.

- The input/output pins and output pins during the STOP mode can be controlled by the SPL bit (bit

5) of the STBC register so that they are held in the state immediately before entering the STOP mode, or so that they enter in the high-impedance state.

- If an interrupt is requested when 1 is written at the STP bit (bit 7), instruction execution continues without switching to the STOP mode.

- In the STOP mode, the values of registers and RAM immediately before entering the STOP mode are held.

### Canceling STOP mode

- The STOP mode is canceled either by inputting the reset signal or by requesting an interrupt.

- When the reset signal is input during the STOP mode, the CPU is switched to the reset state and the STOP mode is canceled.

- When an interrupt higher than level 11 is requested from the external interrupt circuit during the STOP mode, the STOP mode is canceled.

- When the I flag and IL bit are enabled like an ordinary interrupt after canceling, the CPU executes the interrupt processing. When they are disabled, the CPU executes the interrupt processing from the instruction next to the one before entering the STOP mode.

- Four oscillation stabilization times of the main clock can be selected by the WT1 and WT0 bits.

The oscillation stabilization time of the subclock is fixed (at 2<sup>15</sup>/fcl -- fcl: frequency of subclock).

- If the STOP mode is canceled by inputting the reset signal, the CPU is switched to the oscillation stabilization wait state. Therefore, the reset sequence is not executed unless the oscillation stabilization time is elapsed. The oscillation stabilization time corresponds to the oscillation stabilization time of the main clock selected by the WT1 and WT0 bits. However, when Power-on Reset is not specified by the mask option, the CPU is not switched to the oscillation stabilization wait state even if the STOP mode is canceled by inputting the reset signal.

### [4] Setting low power consumption mode

| S           | Mode        |             |         |  |  |

|-------------|-------------|-------------|---------|--|--|

| STP (Bit 7) | SLP (Bit 6) | TMD (Bit 3) | ivioue  |  |  |

| 0           | 0           | 0           | Normal  |  |  |

| 0           | 0           | 1           | WATCH   |  |  |

| 0           | 1           | 0           | SLEEP   |  |  |

| 1           | 0           | 0           | STOP    |  |  |

| 1           | ×           | ×           | Disable |  |  |

Note: When the mode is switched from the subclock mode to the main clock mode, do not set the stop, sleep, and watch modes. If the SCS bit of the SYCC register is rewritten from 0 to 1, set the above modes after the SCM bit of the SYCC register has been set to 1.

For microcontrollers with a built-in booster (MB89150A), the booster stops when the mode is switched from the subclock mode to the stop mode.

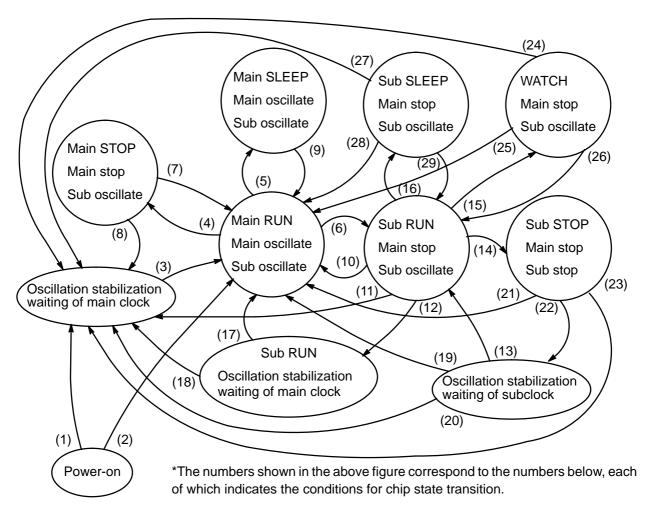

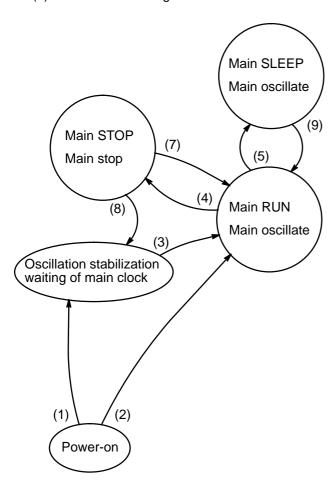

### (b) State transition diagram

- (1) When power-on reset option is selected

- (2) When power-on reset option is not selected

- (3) After oscillation stabilized

- (4) Set STP bit to 1.

- (5) Set SLP bit to 1.

- (6) Set SCS bit to 0.

- (7) External reset when power-on reset option not selected

- (8) External reset or interrupt when power-on reset option selected

- (9) External reset or interrupt

- (10)External reset when power-on reset option not selected

- (11) External reset or other reset when power-on reset option selected

- (12)Set SCS bit to 1.

- (13)After oscillation stabilized

- (14)Set STP bit to 1.

- (15)Set TMD bit to 1.

- (16)Set SLP bit to 1.

- (17)External reset after oscillation stabilized or when power-on reset option not selected

- (18)External reset or other reset when power-on reset option selected

- (19)External reset after oscillation is stabilized or when power-on reset option not selected

- (20)External reset when power-on reset option selected

- (21)External reset when power-on reset option not selected

- (22)Interrupt

- (23)External reset when power-on reset option selected

- (24)External reset when power-on reset option selected

- (25)External reset when power-on reset option not selected

- (26)Interrupt

- (27)External reset when power-on reset option selected

- (28)External reset when power-on reset option not selected

- (29)Interrupt

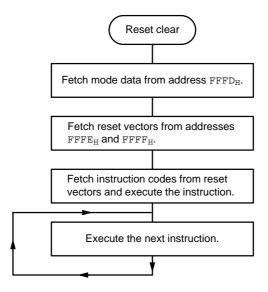

### (d) Reset

There are four types of resets as shown in Table 2-2.

Table 2-2 Sources of Reset

| Reset name         | Description                     |

|--------------------|---------------------------------|

| External-pin reset | Sets external-reset pin to Low  |

| Software reset     | Writes 0 at RST (bit 4) of STBC |

| Watchdog reset     | Overflows watchdog timer        |

| Power-on reset     | Turns power on                  |

When the power-on reset and reset during the stop mode are used, the oscillation stabilization time is needed after the oscillator operates. The time-base timer or watch prescaler controls this stabilization time. Consequently, the operation does not start immediately even after canceling the reset.

However, if Power-on Reset Disabled is selected by the mask option, no oscillation stabilization time is required in any state after external pins have been released from the reset.

Note: If Power-on Reset Disabled is selected, the RST pin must be kept Low until the oscillation stabilization time selected by the option has elapsed after power on.

### (5) Single clock

The single clock module can be selected by the mask option. In the single clock operation, the functions are the same as those of the double clock module except that the subclock mode cannot be set. Therefore, the input pin X0A of the subclock should be connected to GND. The X1A pin must be kept open.

Note: For microcontrollers with a built-in booster (MB89150A), do not select the single clock module. The double-clock module should be used.

### (a) State transition diagram

- (1) When power-on reset option selected

- (2) When power-on reset option not selected

- (3) After oscillation stabilized

- (4) Set STP bit to 1.

- (5) Set SLP bit to 1.

- (7) External reset when power-on reset option not selected

- (8) External reset or interrupt when power-on reset option selected

- (9) External reset or interrupt

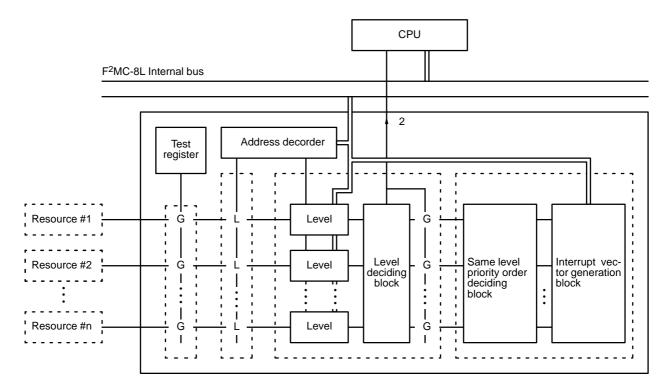

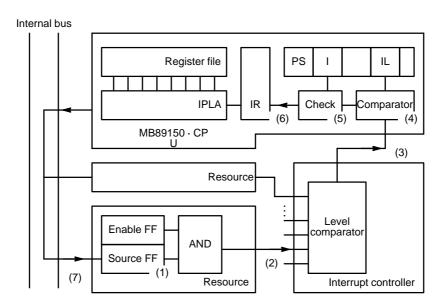

### 2.1.6 Interrupt controller

The interrupt controller for the  $F^2MC-8L$  is located between the CPU and each resource. This controller receives interrupt requests from the resources, assigns priority to them, and transfers the priority to the CPU; it also decides the priority of same-level interrupts.

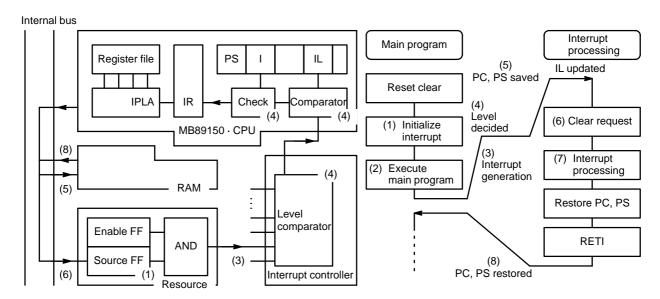

### (1) Block diagram

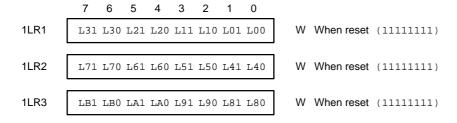

### (2) Register list

| Address             | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   | Name                        | [Abbreviation] | (Initial value) |

|---------------------|-----|-----|-----|-----|-----|-----|-----|-----|-----------------------------|----------------|-----------------|

| 007C <sub>H</sub>   | L31 | L30 | L21 | L20 | L11 | L10 | L01 | L00 | Interrupt-level register #1 | [ILR1]         | (1111 1111)     |

|                     | ,   |     | 1   |     |     |     |     |     |                             |                |                 |

| $007D_{\mathrm{H}}$ | L71 | ь70 | L61 | L60 | L51 | L50 | L41 | L40 | Interrupt-level register #2 | [ILR2]         | (1111 1111)     |

|                     |     |     |     |     |     |     |     |     |                             |                |                 |

| $007E_{\rm H}$      | LB1 | LB0 | LA1 | LA0 | L91 | L90 | L81 | L80 | Interrupt-level register #3 | [ILR3]         | (1111 1111)     |

|                     |     |     |     |     |     |     |     |     |                             |                |                 |

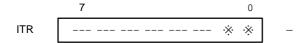

| $007F_{\rm H}$      | _   | _   | _   | _   | _   | _   | EV  | EN  | Interrupt-test register     | [ITR]          | (00)            |

|                     |     |     |     |     |     |     |     |     |                             |                |                 |

### (2) Description of registers

• Interrupt level register (ILRX: Interrupt Level Register X)

The ILRx sets the interrupt level of each resource. The digits in the center of each bit correspond to the interrupt numbers.

When an interrupt is requested from a resource, the interrupt controller transfers the interrupt level based on the value set at the 2 bits of the ILRX corresponding to the interrupt to the CPU. The relationship between the 2 bits of the ILRX and the required interrupt levels is as follows:

| Lx1 | Lx0 | Required interrupt level |

|-----|-----|--------------------------|

| 0   | Х   | 1                        |

| 1   | 0   | 2                        |

| 1   | 1   | 3 (None)                 |

• Interrupt test register (ITR)

The ITR is used for testing. Do not access it.

### (4) Description of operation

### Interrupt functions

The MB89150 series of microcontrollers have 12 inputs for interrupt requests from each resource. The interrupt level is set by 2-bit registers corresponding to each input. When an interrupt is requested from a resource, the interrupt controller receives it and transfers the contents of the corresponding register to the CPU. The interrupt to the device is processed as follows:

- (1) An interrupt source is generated inside each resource.

- (2) If an interrupt is enabled, an interrupt request is output from each resource to the interrupt controller by referring to the interrupt-enable bit inside each resource.

- (3) After receiving this interrupt request, the interrupt controller determines the priority of simultaneously-requested interrupts and then transfers the interrupt level for the applicable interrupt to the CPU.

- (4) The CPU compares the interrupt level requested from the interrupt controller with the IL bit in the processor status register.

- (5) As a result of the comparison, if the priority of the interrupt level is higher than that of the current interrupt processing level, the contents of the I-flag in the same processor status register are checked.

- (6) As a result of the check in step (5), if the I-flag is enabled for an interrupt, the contents of the IL bit are set to the required level. As soon as the currently-executing instruction is terminated, the CPU performs the interrupt processing and transfers control to the interrupt-processing routine.

- (7) When an interrupt source is cleared by software in the user's interrupt processing routine, the CPU terminates the interrupt processing.

Figure 2.9 outlines the interrupt operation for the MB89150 series of microcontrollers.

Fig. 2.9 Interrupt-processing Flowchart

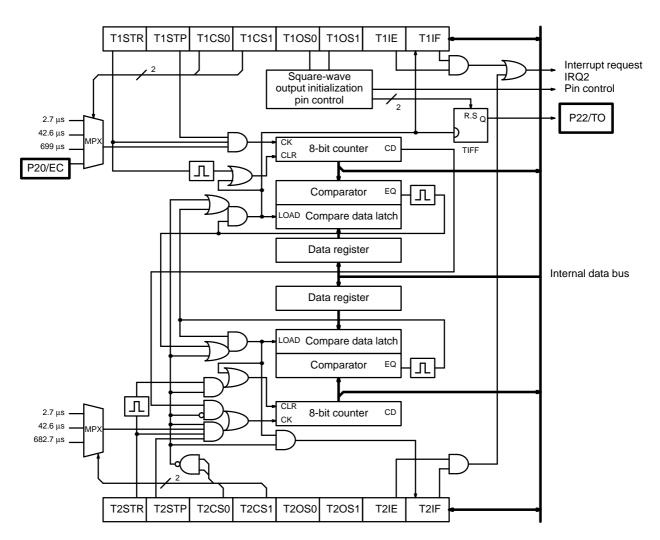

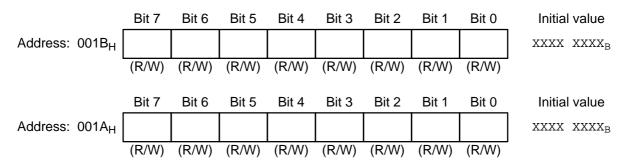

### 2.2 Resource Functions

### 2.2.1 I/O ports

- The MB89150 series of microcontrollers have six parallel ports (43 ports). Ports 0, 1, and 2 serve as 8-bit I/O ports; ports 4 and 5 serve as 8-bit output-only ports; and port 3 serves as a 3-bit output-only port.

- Each port is also used as the I/O pin for the resource.

- (1) List of port functions

**Table 2-3 List of Port Functions**

| Pin name            | Input type | Output type        | Function        | bit7  | bit6  | bit5  | bit4  | bit3  | bit2  | bit1  | bit0  |

|---------------------|------------|--------------------|-----------------|-------|-------|-------|-------|-------|-------|-------|-------|

| P00 to P07          | CMOS       | CMOS<br>push-pull  | Parallel port 0 | P07   | P06   | P05   | P04   | P03   | P02   | P01   | P00   |

| F 00 t0 F 07        | Hysteresis | pusii-puii         | Resource        | INT27 | INT26 | INT25 | INT24 | INT23 | INT22 | INT21 | INT20 |

| P10 to P17          | CMOS       | CMOS<br>push-pull  | Parallel port 1 | P17   | P16   | P15   | P14   | P13   | P12   | P11   | P10   |

| 1 10 10 1 17        | Hysteresis | pusii-puii         | Resource        |       |       |       |       | INT13 | INT12 | INT11 | INT10 |

| P20 to P27 CMOS<br> | CMOS       | N-ch<br>open drain | Parallel port 2 | P27   | P26   | P25   | P24   | P23   | P22   | P21   | P20   |

|                     | Hysteresis | open drain         | Resource        | BUZ   |       | sck   | so    | SI    | то    |       | EC    |

| P30 to P32 —        | _          | CMOS<br>push-pull  | Parallel port 3 |       |       |       |       |       | P32   | P31   | P30   |

|                     |            | pusir-puli         | Resource        |       |       |       |       |       | C0    | C1    | RCO   |

| P40 to P47          |            | N-ch<br>open drain | Parallel port 4 | P47   | P46   | P45   | P44   | P43   | P42   | P41   | P40   |

| 1 40 10 1 47        |            | open diam          | Resource        | SEG27 | SEG26 | SEG25 | SEG24 | SEG23 | SEG22 | SEG21 | SEG20 |

| P50 to P57          | _          | N-ch<br>open drain | Parallel port 5 | P57   | P56   | P55   | P54   | P53   | P52   | P51   | P50   |

| 1 30 10 1 37        |            | opon diam          | Resource        | SEG35 | SEG34 | SEG33 | SEG32 | SEG31 | SEG30 | SEG29 | SEG28 |

### Notes:

- 1. Ports 4 and 5 serve as output ports only when they are selected by the mask option for use as ports.

- 2. Ports 3 (excluding port 30) serves as an output ports only for microcontrollers without a built-in booster.

### (2) Port registers

**Table 2-4 Port Registers**

| Register name                         | Read/Write | Address           | Initial value         |

|---------------------------------------|------------|-------------------|-----------------------|

| Port-0 data register (PDR0)           | R/W        | 0000 <sub>H</sub> | XXXXXXXX <sub>B</sub> |

| Port-0 data direction register (DDR0) | W          | 0001 <sub>H</sub> | 00000000 <sub>B</sub> |

| Port-1 data register (PDR1)           | R/W        | 0002 <sub>H</sub> | XXXXXXXX <sub>B</sub> |

| Port-1 data direction register (DDR1) | W          | 0003 <sub>H</sub> | 00000000 <sub>B</sub> |

| Port-2 data register (PDR2)           | R/W        | 0004 <sub>H</sub> | XXXXXXXX <sub>B</sub> |

| Port-2 data direction register (DDR2) | W          | 0005 <sub>H</sub> | 00000000 <sub>B</sub> |

| Port-3 data register (PDR3)           | R/W        | 000C <sub>H</sub> | XXXXX111 <sub>B</sub> |

| Port-4 data register (PDR4)           | W          | 000E <sub>H</sub> | 11111111 <sub>B</sub> |

| Port-5 data register (PDR5)           | R/W        | 000F <sub>H</sub> | 11111111 <sub>B</sub> |

### (3) Description of functions

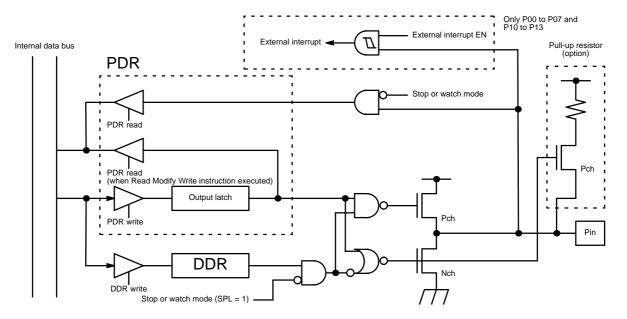

P00 to P07 CMOS-type I/O ports

P10 to P17 CMOS-type I/O ports

### · Switching input and output

These ports have a data-direction register (DDR) and port-data register (PDR) for each bit. Input and output can be set independently for each bit. The pin with the DDR set to 1 is set to output, and the pin with the DDR set to 0 is set to input.

#### Operation for output port (DDR = 1)

The value written at the PDR is output to the pin when the DDR is set to 1. When the PDR is read, usually, the value of the pin is read instead of the contents of the output latch. However, when the Read Modify Write instruction is executed, the contents of the output latch are read irrespective of the DDR setting conditions. Therefore, the bit-processing instruction can be used even if input and output are mixed with each other. When data is written to the PDR, the written data is held in the output latch irrespective of the DDR setting conditions.

### • Operation for input port (DDR = 0)

When settings the input, the output impedance goes High. Therefore, when the PDR is read, the value of the pin is read.

## • State when reset

The DDR is initialized to 0 by resetting and the output impedance goes High at all bits. The PDR is not initialized by resetting. Therefore, set the value of the PDR before setting the DDR to output.

# • State in watch and stop modes

With the SPL bit of the standby-control register set to 1, in the watch or stop mode, the output impedance goes High irrespective of the value of the DDR.

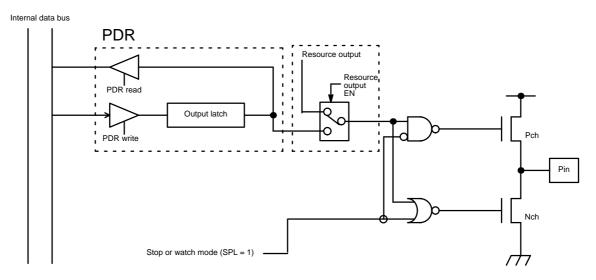

Fig. 2.10 Ports 0 and 1

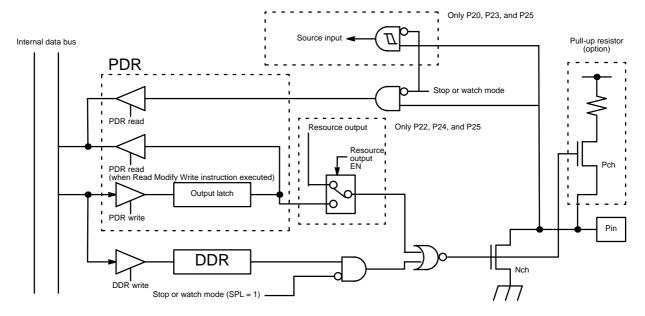

P20 to P27 N-ch open-drain type I/O ports (also used as resource input/output)

### · Switching input and output

This port has a data-direction register (DDR) and a port-data register (PDR) for each bit. Input and output can be set independently for each bit. The pin with the DDR set to 1 is set to output, and the pin with the DDR set to 0 is set to input.

### Operation for output port (DDR = 1)

The value written at the PDR is output to the pin when the DDR is set to 1. When the PDR is read, usually, the value of the pin is read instead of the contents of the output latch. However, when the Read Modify Write instruction is executed, the contents of the output latch are read irrespective of the DDR setting conditions. Therefore, the bit-processing instruction can be used even if input and output are mixed with each other. When data is written to the PDR, the written data is held in the output latch irrespective of the DDR setting conditions.

### Resource output operation (DDR = 1)

When using as the resource output, setting is performed by the resource output enable bit. (See the description of each resource.) Even if the output from each resource is enabled, the read value of the port is effective except when the Read Modify Write instruction is read, so the pin state can be checked.

### • Operation for input port (DDR = 0)

When used as the input port, the output impedance goes High. Therefore, when the PDR is read, the value of the pin is read.

When the DDR is initialized to 0 by reset, the output impedance of all bits goes High. Since the PDR is not initialized by reset, set the value before setting the DDR to output.

#### State when reset

When reset, the DDR is initialized to 0 and the output impedance goes High at all bits. When reset, the PDR is not initialized. Therefore, set the value of the PDR before setting the DDR to output.

#### State in watch and stop modes

With the SPL bit of the standby-control register set to 1, in the watch or stop mode, the output impedance goes High irrespective of the value of the DDR.

Fig. 2.11 Port 2

P30/RCO CMOS type output-only ports (also used as resource output)

### • Operation for output port

The value written at the PDR is output to the pin. When the PDR is read at this port, the contents of the output latch can always be read instead of the pin state.

#### • Operation for resource output

When using as the resource output, setting is performed by the resource output enable bit. (See the description of each resource.) Even if the output from each resource is enabled, the read value of the port is effective except when the Read Modify Write instruction is read, so the pin state can be checked.

### • State when reset

At reset, the PDR is initialized to 1 and the output transistors of all bits are turned off.

### • State in stop mode

When the SPL bit of the standby-control register is set to 1, in the stop mode, the output impedance goes High irrespective of the value of the PDR.

Fig. 2.12 P30

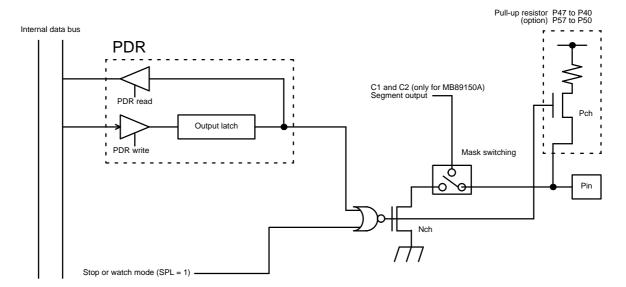

P31 and 32 N-ch open-drain type output ports (used as pins for connecting capacitors C0 and C1 when selected by mask option)

P40 to P47 N-ch open-drain-type output-only ports (also used as segment output)

P50 to P57 N-ch open-drain-type output-only ports (also used as segment output)

#### Operation for output port

The value written at the PDR is output to the pin. When the PDR is read in this port, usually, the contents of the output latch is read instead of the value of the pin.

### Segment output

When selected by the mask option for use as segment pins, ports 4 and 5 serve as segment outputs. In this case, they cannot be used as output ports.

P31 and P32 serve as capacitor connection pins for microcontrollers with a built-in booster (MB89150A). They cannot be used as output ports. P31 and P32 are not available for selection of a pull-up resistor.

#### State when reset

The PDR is initialized to 1 at reset, so the output register is turned off at all bits.

### • State in stop mode

When the SPL bit of the standby-control register is set to 1, in the stop mode, the output impedance goes High irrespective of the value of the PDR.

Fig. 2.13 P31, P32, Port 4, and Port 5

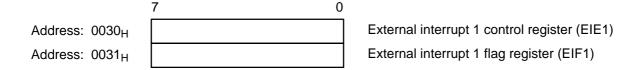

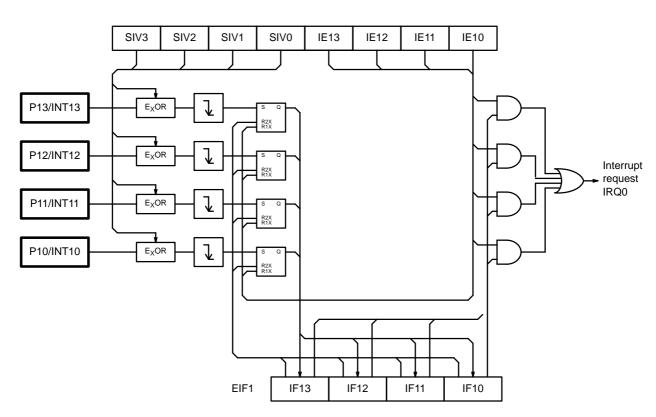

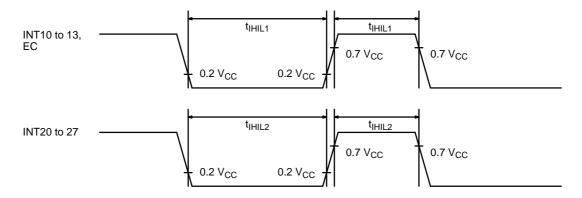

## 2.2.2 External interrupt 1

The external interrupt 1 is controlled by the external interrupt control and external interrupt flag registers.

- Four external interrupt inputs

- An interrupt request is output at the falling edge of the input signal.

- Inverting an input signal outputs an interrupt request at the rising edge.

- Usable as wake-up input

## (1) Registers

Fig. 2.14 External Interrupt 1 Block Diagram

# (2) Description of registers

(a) External-interrupt 1 control register (EIE1)

|                            | Bit7  | Bit6  | Bit5  | Bit4  | Bit3  | Bit2  | Bit1  | Bit0  | Initial value          |

|----------------------------|-------|-------|-------|-------|-------|-------|-------|-------|------------------------|

| Address: 0030 <sub>H</sub> | SIV3  | SIV2  | SIV1  | SIV0  | IE13  | IE12  | IE11  | IE10  | 0000 0000 <sub>B</sub> |

| '                          | (R/W) | •                      |

[Bit 7]: SIV3

[Bit 6]: SIV2

[Bit 5]: SIV1

[Bit 4]: SIV0

These bits are used to invert external interrupts EI13 to EI10.

| 0 | External interrupt signal not inverted |

|---|----------------------------------------|

| 1 | External interrupt signal inverted     |

[Bit 3]: IE13

[Bit 2]: IE12

[Bit 1]: IE11

[Bit 0]: IE10

These bits are used to enable external interrupts EI13 to EI10.

| 0 | External interrupt disabled (edge detect flag initialized) |

|---|------------------------------------------------------------|

| 1 | External interrupt enabled                                 |

Note: The interrupt flag may be turned on immediately after an interrupt is enabled or an interrupt input is inverted.

## (b) External interrupt 1 flag register (EIF1)

|                            | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Initial value     |

|----------------------------|-------|-------|-------|-------|-------|-------|-------|-------|-------------------|

| Address: 0031 <sub>H</sub> |       |       | -     | _     | IE13  | IE12  | IE11  | IE10  | 0000 <sub>B</sub> |

| ·                          |       |       |       |       | (R/W) | (R/W) | (R/W) | (R/W) | •                 |

[Bit 3]: IF13

[Bit 2]: IF12

[Bit 1]: IF11

[Bit 0]: IF10

These bits are used to detect the falling edges of EI13 to EI10.

# (When write)

| 0 | Falling edge detect flag cleared |

|---|----------------------------------|

| 1 | No operation                     |

## (When read)

| 0 | Falling edge not detected |

|---|---------------------------|

| 1 | Falling edge detected     |

If the interrupt enable bits (IE13 to IE10) of the external interrupt 1 control register (EIE1) are 1, an interrupt request is output to the CPU when the corresponding falling edge detect flag bits (IF13 to IF10) are set to 1.

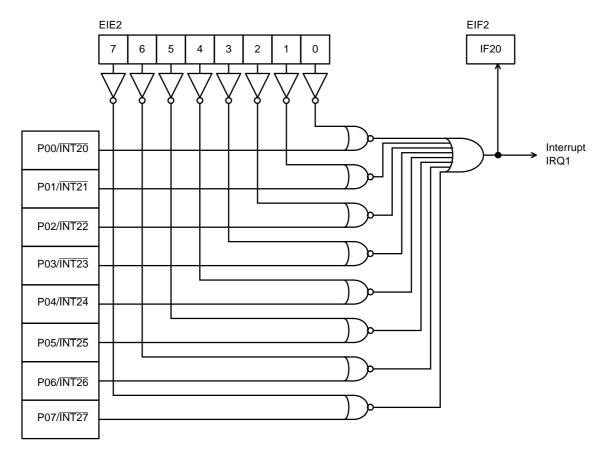

## 2.2.3 External interrupt 2

External interrupt 2 is controlled by the external interrupt control and external interrupt flag registers.

- Eight external interrupt input pins

- An interrupt request is output by Low-level input signals.

- Also usable as wake-up input

## (1) Registers

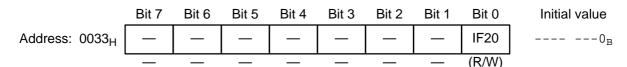

Address: 0032<sub>H</sub>

Address: 0033<sub>H</sub>

External interrupt 2 control register (EIE2)

External interrupt 2 flag register (EIF2)

# (2) Block diagram

Fig. 2.15 External Interrupt 2 Block Diagram

## (2) Description of registers

(a) External interrupt 2 control register (EIE2)

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 Initial value Address: **IE27** IE26 IE25 IE24 IE23 IE22 IE21 IE20 0000 0000<sub>B</sub> (R/W) (R/W) (R/W) (R/W) (R/W) (R/W) (R/W) (R/W)  $0032_{H}$ [Bit 7]: IE27

[Bit 6]: IE26 [Bit 5]: IE25 [Bit 4]: IE24 [Bit 3]: IE23 [Bit 2]: IE22 [Bit 1]: IE21 [Bit 0]: IE20

These bits are used to enable external interrupt of INT27 to INT20.

| 0 | External interrupt disabled |

|---|-----------------------------|

| 1 | External interrupt enabled  |

### (b) External interrupt 2 flag register (EIF2)

[Bit 0]: IF20

This bit is used to detect LOW level.

## (When write)

| 0 | Clears flag for detecting LOW level |

|---|-------------------------------------|

| 1 | No operation                        |

### (When read)

| 0 | No LOW level input       |

|---|--------------------------|

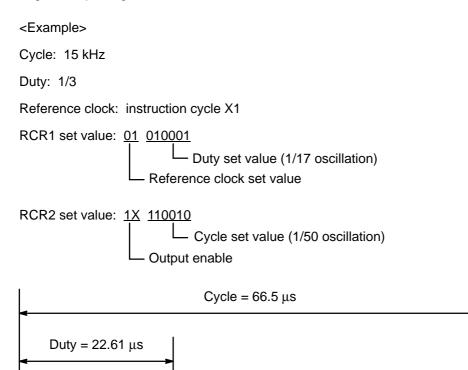

| 1 | LOW level input detected |