# F<sup>2</sup>MC-8L FAMILY MICROCONTROLLERS

MB89610 SERIES HARDWARE MANUAL

#### F<sup>2</sup>MC-8L FAMILY MICROCONTROLLERS

#### MB89610 SERIES HARDWARE MANUAL

Edition 1.0 January 1995

© 1995 FUJITSU LIMITED

All Rights Reserved.

Circuit diagrams utilizing Fujitsu products are included as a means of illustrating typical semiconductor applications. Complete information sufficient for construction purposes is not necessarily given.

The information contained in this document has been carefully checked and is believed to be reliable. However, Fujitsu assumes no responsibility for inaccuracies.

The information contained in this document does not convey any license under the copyrights, patent rights or trademarks claimed and owned by Fujitsu.

Fujitsu reserves the right to change products or specifications without notice.

No part of this publication may be copied or reproduced in any form or by any means, or transferred to any third party without prior written consent of Fujitsu.

## ■ PREFACE

The MB89610 series of microcontrollers are application-specific integrated circuits. They are general-purpose and high-speed products in the  $F^2MC-8L$  Family series of 8-bit single-chip microcontrollers operating at low voltages.

This manual covers the functions and operations of the MB89610 series of microcontrollers. Refer to the  $F^2MC-8L$  Family Software Manual for instructions.

## **Table of Contents**

| 1. INTRODUCTION       1-1         1.1. FEATURES       1-3         1.2. PRODUCT SERIES       1-4         1.3. BLOCK DIAGRAM       1-5         1.4. PIN ASSIGNMENT       1-6         1.5. PIN DESCRIPTION       1-9                                                                                                                                                                                                                                                                                                                                                              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.6. HANDLING DEVICES       1-13         2. PINS AND PACKAGE       2-1         2.1. CPU       2-3         2.2. CLOCK CONTROL BLOCK       2-13         2.3. INTERRUPT CONTROLLER       2-21         2.4. I/O PORTS       2-24         2.5. 8-BIT PWM TIMER (TIMER 1)       2-31         2.6. PULSE-WIDTH COUNT TIMER (TIMER 2)       2-36         2.7. 16-BIT TIMER/COUNTER (TIMER 3)       2-42         2.8. 8-BIT SERIAL I/O 1 AND 2       2-47         2.9. EXTERNAL INTERRUPT CIRCUIT       2-53         2.10 BUZZER OUTPUT CIRCUIT       2-58                              |

| 3. DATA FORMAT       3-1         3.1       CLOCK PULSE GENERATOR       3-3         3.2       RESET       3-4         3.2.1       Reset Operation       3-4         3.2.2       Reset Sources       3-5         3.3       INTERRUPT       3-6         3.4       MEMORY ACCESS MODE       3-8         3.5       READY AND HOLD FUNCTIONS       3-10         3.5.1       Ready Function       3-10         3.5.2       Hold Function       3-11         3.6       LOW-POWER CONSUMPTION MODES       3-12         3.7       PIN STATES FOR SLEEP, STOP, HOLD, AND RESET       3-14 |

| APPENDIX         App1           APPENDIX 1. MASK OPTIONS         App3           APPENDIX 2. I/O MAP         App4           APPENDIX 3. EPROM SETTING FOR MB89P625         App6                                                                                                                                                                                                                                                                                                                                                                                                 |

# Figures

| Fig. 1.1 Block Diagram                                                        | 1-5  |

|-------------------------------------------------------------------------------|------|

| Fig. 1.2 Pin Assignment (DIP-64P-M01 and MDP-64C-P02)                         | 1-6  |

| Fig. 1.3 Pin Assignment (FPT-64P-M03 and FPT-64P-M09)                         | 1-7  |

| Fig. 1.4 Pin Assignment (FPT-64P-M06 and MQP-64C-P01)                         | 1-8  |

| Fig. 1.5 I/O Circuits                                                         | 1-11 |

| Fig. 1.5 I/O Circuits (Continued)                                             |      |

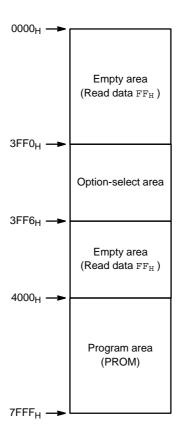

| Fig. 2.1 Memory Space of MB89610 Series of Microcontrollers                   | 2-3  |

| Fig. 2.2 Arrangement of 16 bit Data in Memory Space                           | 2-5  |

| Fig. 2.3 Arrangement of 16 bit Data during Execution of Instruction           | 2-5  |

| Fig. 2.4 Structure of Processor Status                                        | 2-6  |

| Fig. 2.5 Rule for Translating Real Addresses at General-purpose Register Area | 2-7  |

| Fig. 2.6 Register Bank Configuration                                          |      |

| Fig. 2.7 Memory Maps in Various Modes                                         | 2-9  |

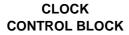

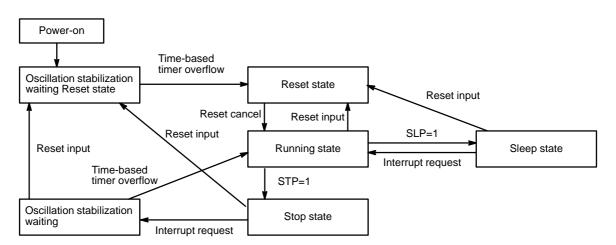

| Fig. 2.8 State Transition Diagram in Low-power Consumption Modes              | 2-18 |

| Fig. 2.9 Interrupt-processing Flowchart                                       |      |

| Fig. 2.10 Ports 0 and 1 (in Single-chip Mode)                                 | 2-26 |

| Fig. 2.11 Port 2 (in Single-chip Mode)                                        | 2-27 |

| Fig. 2.12 Port 3                                                              |      |

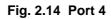

| Fig. 2.13 Port 4                                                              |      |

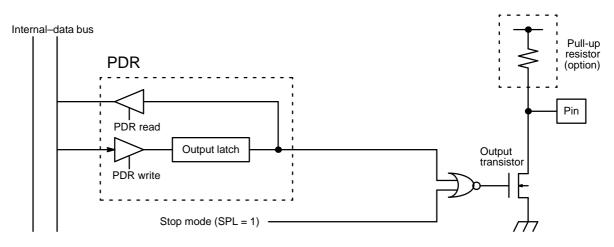

| Fig. 2.14 Port 5                                                              |      |

| Fig. 2.15 Port 6                                                              |      |

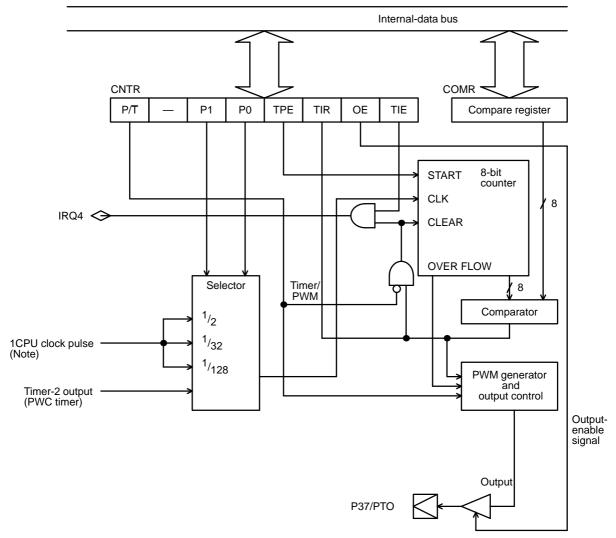

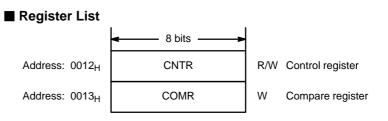

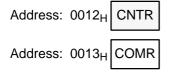

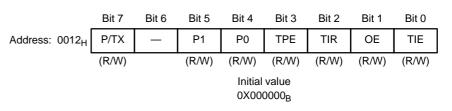

| Fig. 2.16 8-bit PWM Timer Block Diagram                                       | 2-31 |

| Fig. 2.17 Timer Operation                                                     |      |

| Fig. 2.18 PWM Pulse Output                                                    | 2-35 |

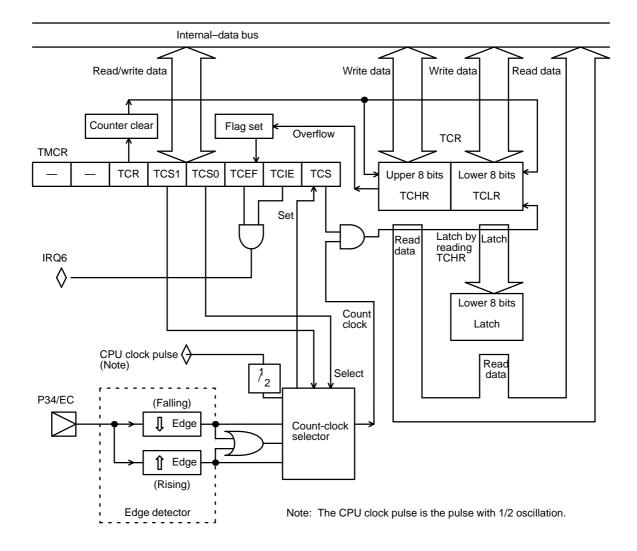

| Fig. 2.19 Pulse-width Timer Block Diagram                                     |      |

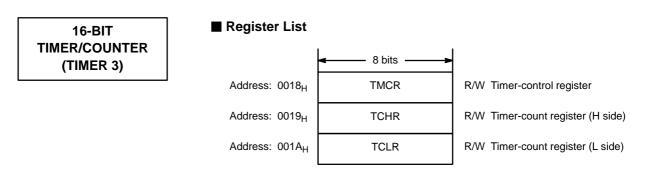

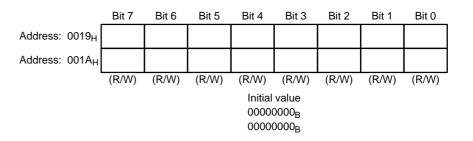

| Fig. 2.20 16-bit Timer/Counter Block Diagram                                  | 2-42 |

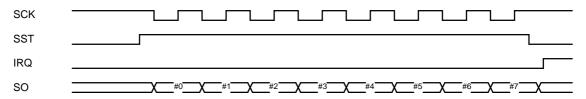

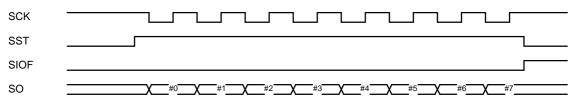

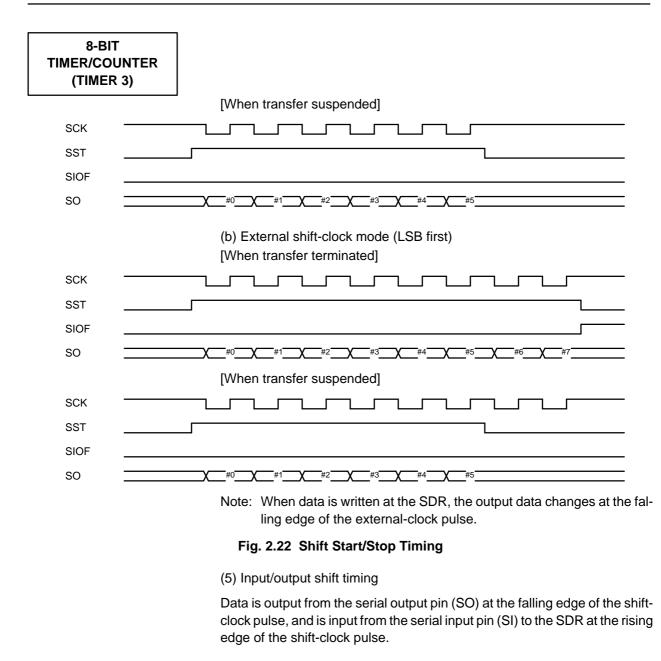

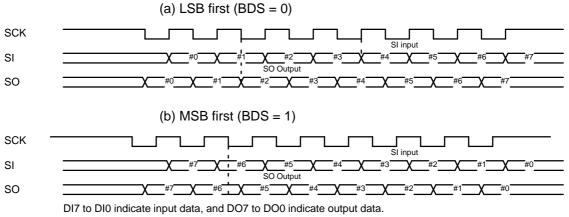

| Fig. 2.21 Shift Start/Stop Timing                                             |      |

| Fig. 2.22 Input/Output Shift Timing                                           |      |

| Fig. 3.1 Clock Pulse Generator                                                |      |

| Fig. 3.2 Outline of Reset Operation                                           |      |

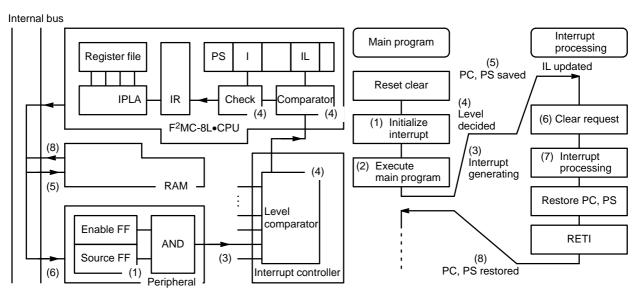

| Fig. 3.3 Interrupt-processing Flowchart                                       |      |

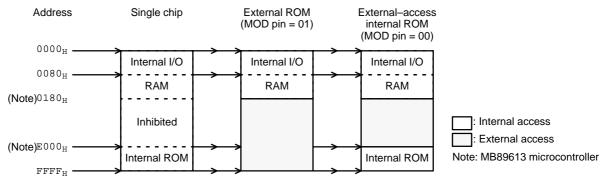

| Fig. 3.4 Memory Map in Various Modes                                          |      |

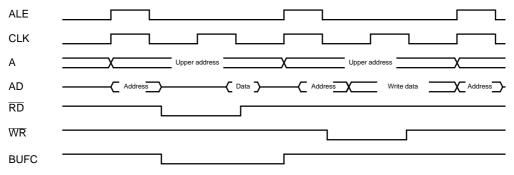

| Fig. 3.5 External-access Timing Chart                                         |      |

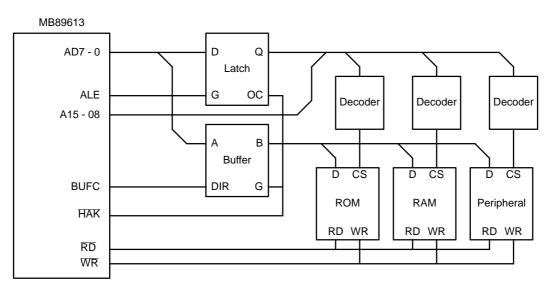

| Fig. 3.6 External Peripheral/Memory Connection                                |      |

| Fig. 3.7 Ready Input Timing Chart (Write Cycle)                               |      |

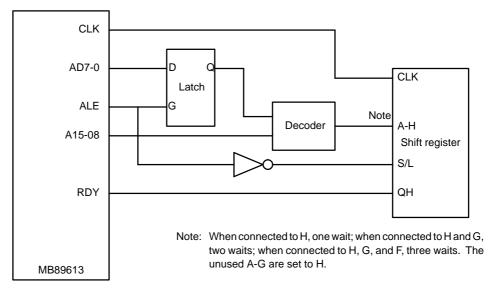

| Fig. 3.8 Ready Generation Circuit                                             | 3-10 |

| Fig. 3.9 Hold Timing                                                          |      |

| Fig. 3.10 State Transition Diagram at Low-power Consumption                   | 3-13 |

## Tables

| Table 1-1 . Types and Functions of MB89610 Series of Microcontrollers | 1-4  |

|-----------------------------------------------------------------------|------|

| Table 1-2 . Pin Description                                           | 1-9  |

| Table 2-1 . Table of Reset and Interrupt Vectors                      | 2-4  |

| Table 2-2 . Operating State in Low-Power Consumption Modes            | 2-17 |

| Table 2-3 . Selection of Oscillation Stabilization Time               | 2-18 |

| Table 2-4 . Watchdog Timer Interval Time (at 10 MHz Oscillation)      | 2-19 |

| Table 2-5 . Sources of Reset                                          |      |

| Table 2-6 . List of Port Functions                                    | 2-24 |

| Table 2-7 . Selection of Timer/Counter Operation Mode                 |      |

| Table 2-8 . Buzzer Output Frequencies (at 10 MHz Oscillation)         |      |

| Table 3-1 . Reset Vector Structure                                    |      |

| Table 3-2 . Interrupt Sources and Interrupt Vectors                   |      |

| Table 3-3 . Oscillation Stabilization Time                            | 3-12 |

# 1. INTRODUCTION

The MB89610 series of single-chip microcontrollers use the F<sup>2</sup>MC-8L CPU core for high-speed processing even at low voltages.

They contain resources such as timers, serial interfaces, and an external-interrupt input; they can be used widely in civil and industrial equipment, including portable equipment.

## **1.1 FEATURES**

- Various package options

- Four types of QFP package (0.5-mm, 0.65-mm, and 1-mm pitch)

- SDIP package

- High-speed processing even at low voltages Minimum instruction execution time: 0.4  $\mu s$  at 3.5 V, 0.8  $\mu s$  at 2.7 V

- F<sup>2</sup>MC-8L CPU core

- Instruction system most suited to controller

- Multiplication and division instructions

- 16-bit arithmetic operation

- Instruction test and branch instruction

- Bit manipulation instruction, etc.

- Four types of timers

- 8-bit PWM timer (usable as both reload timer and PWM timer)

- 8-bit pulse-width count timer (applicable to remote control)

- 16-bit timer/counter

- 20-bit time-based timer

- Two serial interfaces

The transfer direction can be selected to communicate with various equipment.

- External-interrupt input

- Four channels

- Four channels can be used independently to cancel the low-power consumption modes.

- An edge-detection function is provided.

- Low-power consumption modes

- Stop mode (Oscillation stops to minimize the current consumption.)

- Sleep mode (The CPU stops to reduce current consumption to about 30% of normal.)

- Bus interface

Supports hold and ready functions

## **1.2 PRODUCT SERIES**

Table 1-1 lists the types and functions of the MB89610 series of microcontrollers.

| Model Name                   | MB89613                                                                                                                                                                                                                                                                                                               | MB89615                        | MB89P625/W625* <sup>1</sup>                                                | MB89PV620* <sup>1</sup>                  |  |  |  |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|----------------------------------------------------------------------------|------------------------------------------|--|--|--|

| Classification               | Mass-produ<br>(Mask ROI                                                                                                                                                                                                                                                                                               |                                | One-time programmable products/EPROMs                                      | Piggy back/Evaluation<br>and development |  |  |  |

| ROM capacity                 | 8K × 8 bits<br>(Internal ROM)                                                                                                                                                                                                                                                                                         | 16K × 8 bits<br>(Internal ROM) | 16K × 8 bits<br>(Internal PROM, writable<br>by general-purpose<br>writers) | 32K × 8 bits<br>(External ROM)           |  |  |  |

| RAM capacity                 | $256 \times 8$ bits                                                                                                                                                                                                                                                                                                   | $512 \times 8$ bits            | $512 \times 8$ bits                                                        | $1K \times 8$ bits                       |  |  |  |

| CPU function                 | Numbe<br>Instruc<br>Instruc<br>Data bi<br>Minimu<br>Interru                                                                                                                                                                                                                                                           |                                |                                                                            |                                          |  |  |  |

| Port                         | Input port5 (4 used as resources)Output port (N-ch open drain)8I/O port (N-ch open drain)8 (4 used as resources)Output port (CMOS)8 (8 used as bus-control pins)I/O port (CMOS)24 (24 used as both bus pins and resourceTotal53                                                                                       |                                |                                                                            |                                          |  |  |  |

| PWM timer                    | 8-bit reload timer operation (toggle output possible, count clock cycle: 0.4 $\mu$ s to 3.3 ms)<br>8-bit resolution PWM operation (conversion cycle: 10 $\mu$ s to 839 ms)                                                                                                                                            |                                |                                                                            |                                          |  |  |  |

| Pulse-width count timer      | 8-bit timer operation (overflow output possible, count clock cycle: 0.4 μs to 12.8 μs)<br>8-bit reload timer operation (toggle output possible, operating clock cycle: 0.4 μs to 12.8 μs)<br>8-bit pulse-width measurement<br>(continuous measurement possible: High and Low widths, and from ↑ to ↑ and from ↓ to ↓) |                                |                                                                            |                                          |  |  |  |

| Timer/counter                | 16-bit timer operation (count clock cycle: 0.4 $\mu s)$ 16-bit event counter operation (selectable from rising edge, falling edge, or both edges)                                                                                                                                                                     |                                |                                                                            |                                          |  |  |  |

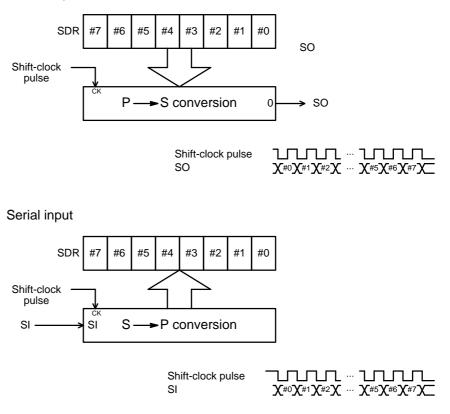

| Serial I/O 1<br>Serial I/O 2 | 8-bit length<br>Selectable from least significant bit (LSB) first or most significant bit (MSB) first<br>Transfer clock (external, 0.8 μs, 3.2 μs, 12.8 μs)                                                                                                                                                           |                                |                                                                            |                                          |  |  |  |

| External-interrupt input     | Four independent channels (edge selection, interrupt vector, interrupt source flag)<br>Selectable from rising or falling edge<br>Used for clearing stop or sleep mode (The edge can be detected even in the stop mode.)                                                                                               |                                |                                                                            |                                          |  |  |  |

| Standby mode                 |                                                                                                                                                                                                                                                                                                                       | Sleep mode                     | e and stop mode                                                            |                                          |  |  |  |

| Process                      |                                                                                                                                                                                                                                                                                                                       | C                              | CMOS                                                                       |                                          |  |  |  |

| Operating voltage*2          | 2.2 V to                                                                                                                                                                                                                                                                                                              | o 6.0 V                        | 2.7 V to 6.0 V                                                             | 2.7 V to 6.0 V                           |  |  |  |

| EPROM used                   |                                                                                                                                                                                                                                                                                                                       |                                |                                                                            | MBM27C256A-20                            |  |  |  |

\*1: One-time programmable products, EPROM products, and piggy-back/evaluation chip are common with the MB89620 series.

\*2: Varies according to conditions such as frequency (see Electrical Characteristics). The operating voltage of the MB89PV620 differs depending on connected ICE or EPROM.

## **1.3 BLOCK DIAGRAM**

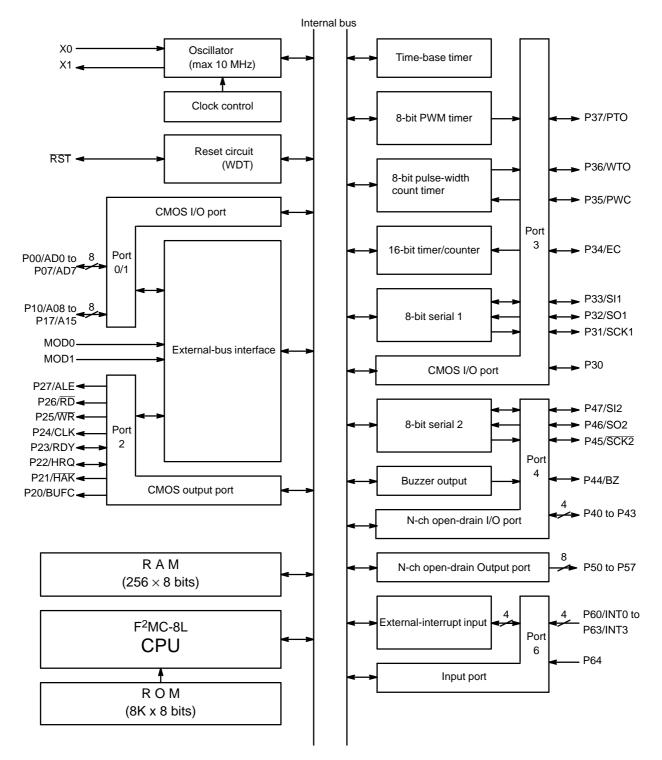

Fig. 1.1 Block Diagram

## **1.4 PIN ASSIGNMENT**

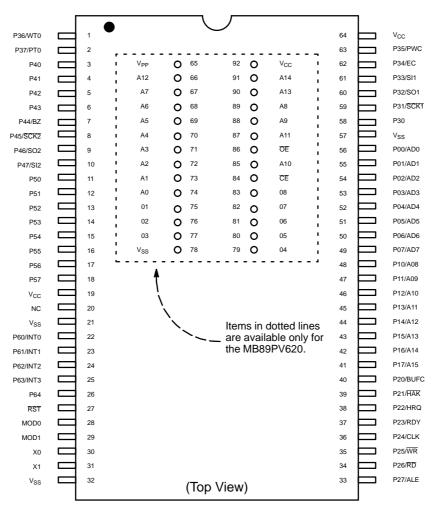

Fig. 1.2 Pin Assignment (DIP-64P-M01 and MDP-64C-P02)

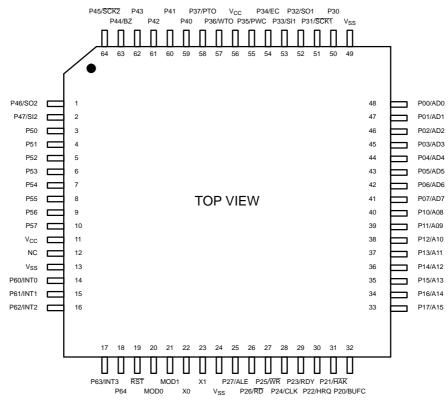

Fig. 1.3 Pin Assignment (FPT-64P-M03 and FPT-64P-M09)

| Note: | Pin assignmen | t on top | of pac | kage ( | only | for pigg | yback/eva | luation | type) |

|-------|---------------|----------|--------|--------|------|----------|-----------|---------|-------|

|-------|---------------|----------|--------|--------|------|----------|-----------|---------|-------|

| Pin No. | Pin Name        | Pin No. | Pin Name        | Pin No. | Pin Name | Pin No. | Pin Name        |

|---------|-----------------|---------|-----------------|---------|----------|---------|-----------------|

| 65      | NC              | 73      | A2              | 81      | N.C.     | 89      | 0E              |

| 66      | V <sub>PP</sub> | 74      | A1              | 82      | 04       | 90      | NC              |

| 67      | A12             | 75      | A0              | 83      | 05       | 91      | A11             |

| 68      | A7              | 76      | N.C.            | 84      | 06       | 92      | A9              |

| 69      | A6              | 77      | 01              | 85      | 07       | 93      | A8              |

| 70      | A5              | 78      | 02              | 86      | 08       | 94      | A13             |

| 71      | A4              | 79      | 03              | 87      | CE       | 95      | A14             |

| 72      | A3              | 80      | V <sub>SS</sub> | 88      | A10      | 96      | V <sub>CC</sub> |

Note: NC (No connection): Always open because internal connection is made

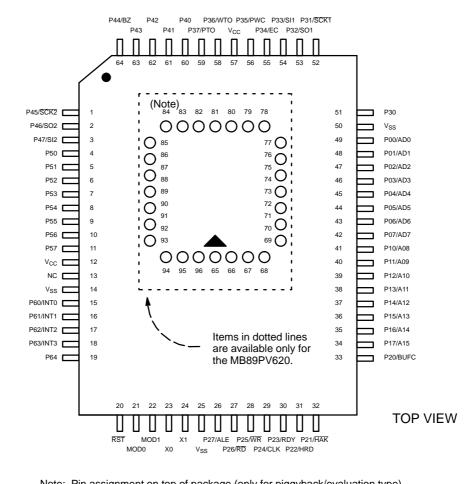

Fig. 1.4 Pin Assignment (FPT-64P-M06 and MQP-64C-P01)

## 1.5 PIN DESCRIPTION

Table 1-2 lists the pin functions and Figure 1.5 shows the input/output circuits.

| Table ' | 1-2 | Pin | Descri | ption |

|---------|-----|-----|--------|-------|

|---------|-----|-----|--------|-------|

|                     | Pin No.             |                             | Pin No.                  |                 | Pin No.                                                                                                                                                                                                               |  | Pin No. |  |  |  |  |

|---------------------|---------------------|-----------------------------|--------------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|---------|--|--|--|--|

| DIP-<br>64P-<br>M01 | FPT-<br>64P-<br>M06 | FPT-<br>64P-<br>M03/<br>M09 | Pin Name                 | Circuit<br>type | Function                                                                                                                                                                                                              |  |         |  |  |  |  |

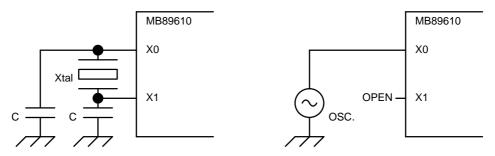

| 30                  | 23                  | 22                          | X0                       | А               | Crystal oscillator pins                                                                                                                                                                                               |  |         |  |  |  |  |

| 31                  | 24                  | 23                          | X1                       |                 |                                                                                                                                                                                                                       |  |         |  |  |  |  |

| 28                  | 21                  | 20                          | MOD0                     | в               | <b>Operation-mode select pins</b><br>These pins are connected directly to $V_{CC}$ or $V_{SS}$ .                                                                                                                      |  |         |  |  |  |  |

| 29                  | 22                  | 21                          | MOD1                     | В               | These pins are connected directly to VCC or VSS.                                                                                                                                                                      |  |         |  |  |  |  |

| 27                  | 20                  | 19                          | RST                      | С               | Reset I/O pin<br>This pin consists of an N-ch open-drain output with a pull-up resistor and hysteresis<br>input. A Low level is output from this pin. The internal circuit is initialized at input of a<br>Low level. |  |         |  |  |  |  |

| 56<br>to<br>49      | 49<br>to<br>42      | 48<br>to<br>41              | P00/AD0<br>to<br>P07/AD7 | D               | General-purpose I/O ports<br>When the external bus is used, these ports also serve as multiplex pins for output of<br>lower addresses or input and output of data.                                                    |  |         |  |  |  |  |

| 48<br>to<br>41      | 41<br>to<br>34      | 40<br>to<br>33              | P10/A08<br>to<br>P17/A15 | D               | General-purpose I/O ports<br>When the external bus is used, these ports also serve as pins for output of upper<br>addresses.                                                                                          |  |         |  |  |  |  |

| 40                  | 33                  | 32                          | P20/BUFC                 | F               | General-purpose output-only port<br>When the external bus is used, this port also serves as a buffer-control output pin by<br>setting BCTR.                                                                           |  |         |  |  |  |  |

| 39                  | 32                  | 31                          | P21/HAK                  | F               | General-purpose output-only port<br>When the external bus is used, this port also serves as a hold-acknowledge pin by<br>setting BCTR.                                                                                |  |         |  |  |  |  |

| 38                  | 31                  | 30                          | P22/HRQ                  | D               | General-purpose output-only port<br>When the external bus is used, this port also serves as a hold-request input pin by<br>setting BCTR.                                                                              |  |         |  |  |  |  |

| 37                  | 30                  | 29                          | P23/RDY                  | D               | General-purpose output-only port<br>When the external bus is used, this port also serves as a ready-input                                                                                                             |  |         |  |  |  |  |

| 36                  | 29                  | 28                          | P24/CLK                  | F               | <b>General-purpose output-only port</b><br>When the external bus is used, this port also serves as a clock-output pin.                                                                                                |  |         |  |  |  |  |

| 35                  | 28                  | 27                          | P25/WR                   | F               | General-purpose output-only port<br>When the external bus is used, this port also serves as a write-signal output pin.                                                                                                |  |         |  |  |  |  |

| 34                  | 27                  | 26                          | P26/RD                   | F               | <b>General-purpose output-only port</b><br>When the external bus is used, this port also serves as a read-signal output pin.                                                                                          |  |         |  |  |  |  |

| 33                  | 26                  | 25                          | P27/ALE                  | F               | General-purpose output-only port<br>When the external bus is used, this port also serves as an address-latch signal-ou<br>put pin.                                                                                    |  |         |  |  |  |  |

| 58                  | 51                  | 50                          | P30                      | E               | General-purpose I/O port<br>Input is hysteresis type.                                                                                                                                                                 |  |         |  |  |  |  |

| 59                  | 52                  | 51                          | P31/SCK1                 | E               | General-purpose I/O port<br>This port also serves as a clock I/O pin for serial I/O 1.<br>Input is hysteresis type.                                                                                                   |  |         |  |  |  |  |

|                     | Pin No.             |                             |                           |                 |                                                                                                                                                      |  |

|---------------------|---------------------|-----------------------------|---------------------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| DIP-<br>64P-<br>M01 | FPT-<br>64P-<br>M06 | FPT-<br>64P-<br>M03/<br>M09 | Pin Name                  | Circuit<br>type | Function                                                                                                                                             |  |

| 60                  | 53                  | 52                          | P32/SO1                   | E               | <b>General-purpose I/O port</b><br>This port also serves as a data-output pin for serial I/O 1.<br>Input is hysteresis type.                         |  |

| 61                  | 54                  | 53                          | P33/SI1                   | E               | <b>General-purpose I/O port</b><br>This port also serves as a data-input pin for serial I/O 1.<br>Input is hysteresis type.                          |  |

| 62                  | 55                  | 54                          | P34/EC                    | E               | General-purpose I/O port<br>This port also serves as an external-clock input pin for the 16-bit timer/counter.<br>Input is hysteresis type.          |  |

| 63                  | 56                  | 55                          | P35/PWC                   | E               | General-purpose I/O port<br>This port also serves as a measured-pulse input pin for the 8-bit pulse-width count-<br>er.<br>Input is hysteresis type. |  |

| 1                   | 58                  | 57                          | P36/WTO                   | E               | General-purpose I/O port<br>This port also serves as a toggle output pin for the 8-bit pulse-width counter.<br>Input is hysteresis type.             |  |

| 2                   | 59                  | 58                          | P37/PTO                   | E               | General-purpose I/O port<br>This port also serves as a toggle output pin for the 8–bit PWM timer.<br>Input is hysteresis type.                       |  |

| 3<br>to<br>6        | 60<br>to<br>63      | 59<br>to<br>62              | P40<br>to<br>P43          | G               | N-ch open-drain I/O ports<br>Input is hysteresis type.                                                                                               |  |

| 7                   | 64                  | 63                          | P44/BZ                    | G               | <b>N-ch open-drain I/O port</b><br>This port also serves as the buzzer output pin.<br>Input is hysteresis type.                                      |  |

| 8                   | 1                   | 64                          | P45/SCK2                  | G               | <b>N-ch open-drain I/O port</b><br>This port also serves as a clock I/O pin for serial I/O 2.<br>Input is hysteresis type.                           |  |

| 9                   | 2                   | 1                           | P46/SO2                   | G               | <b>N-ch open-drain I/O port</b><br>This port also serves as a data-output pin for serial I/O 2.<br>Input is hysteresis type.                         |  |

| 10                  | 3                   | 2                           | P47/SI2                   | G               | <b>N-ch open-drain I/O port</b><br>This port also serves as a data-output pin for serial I/O 2.<br>Input is hysteresis type.                         |  |

| 11<br>to<br>18      | 4<br>to<br>11       | 3<br>to<br>10               | P50<br>to<br>P57          | Н               | N-ch open-drain output-only ports                                                                                                                    |  |

| 22<br>to<br>25      | 15<br>to<br>18      | 14<br>to<br>17              | P60INT0<br>to<br>P63/INT3 | I               | General-purpose input-only ports<br>These ports also serve as external-interrupt input pins.<br>Input is hysteresis type.                            |  |

| 26                  | 19                  | 18                          | P64                       | I               | General-purpose input-only ports.<br>Input is hysteresis type.                                                                                       |  |

| 19<br>64            | 12<br>57            | 11<br>56                    | V <sub>CC</sub>           | —               | Power pin                                                                                                                                            |  |

| 21<br>32<br>57      | 14<br>25<br>50      | 13<br>24<br>49              | V <sub>SS</sub>           | —               | Power (GND) pins                                                                                                                                     |  |

| 20                  | 13                  | 12                          | N.C.                      | _               | It should be used at the same potential at $V_{SS}$ .                                                                                                |  |

## Table 1-2 Pin Description (Continued)

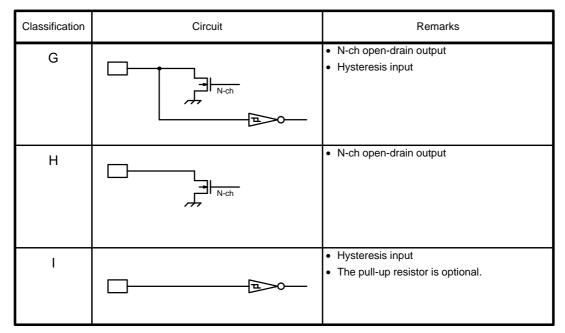

| Classification | Circuit                                                                                                            | Remarks                                                                                                                        |

|----------------|--------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| A              | X1<br>X0<br>X0<br>X0<br>X0<br>X0<br>X0<br>X0<br>X0<br>X0<br>X0<br>X0<br>X0<br>X0                                   | <ul> <li>Feedback resistor: About 2 MΩ</li> </ul>                                                                              |

| В              |                                                                                                                    | CMOS input                                                                                                                     |

| С              | R<br>R<br>R<br>N-ch<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R | <ul> <li>Output pull-up resistor (P-ch): About 50 kΩ (5 V)</li> <li>Hysteresis input</li> </ul>                                |

| D              | P-ch<br>N-ch                                                                                                       | <ul> <li>CMOS output</li> <li>CMOS input</li> <li>The pull-up resistor is optional.<br/>(P22 and P23 are excluded.)</li> </ul> |

| E              | P-ch<br>P-ch<br>N-ch<br>T                                                                                          | <ul> <li>CMOS output</li> <li>Hysteresis input</li> <li>The pull-up resistor is optional.</li> </ul>                           |

| F              | P-ch<br>P-ch<br>N-ch<br>F                                                                                          | CMOS output                                                                                                                    |

Fig. 1.5 I/O Circuits

Fig. 1.5 I/O Circuits (Continued)

## **1.6 HANDLING DEVICES**

#### (1) Preventing latch-up

Latch-up may occur if a voltage higher than Vcc or lower than Vss is applied to the input or output pins other than port 4, or if voltage exceeding the rated value is applied between Vcc and Vss.

When latch-up occurs, the supply current increases rapidly, sometimes resulting in overheating and destruction.

Therefore, no voltage exceeding the maximum ratings should be used.

#### (2) Handling unused input pins

Leaving unused input pins open may cause a malfunction. Therefore, these pins should be set to pull-up or pull-down.

#### (3) Variations in supply voltage

Although the specified Vcc supply voltage operating range is assured, a sudden change in the supply voltage within the specified range may cause a malfunction. Therefore, the voltage supply to the IC should be kept as constant as possible. The  $V_{CC}$  ripple (P-P value) at the supply frequency (50 - 60 Hz) should be less than 10% of the typical Vcc value, or the coefficient of excessive variation should be 0.1 V/ms max. instantaneous change when the power supply is switched.

(4) Precautions for external clocks

It takes some time for oscillation to stabilize after changing the mode to power-on reset (option selection) and stop.

Consequently, an external clock must be input.

# 2. PINS AND PACKAGE

| 2.1 CPU                                    |

|--------------------------------------------|

| 2.2 CLOCK CONTROL BLOCK                    |

| 2.3 INTERRUPT CONTROLLER 2-21              |

| 2.4 I/O PORTS 2-24                         |

| 2.5 8-BIT PWM TIMER (TIMER 1) 2-31         |

| 2.6 PULSE-WIDTH COUNT TIMER (TIMER 2) 2-36 |

| 2.7 16-BIT TIMER/COUNTER (TIMER 3) 2-42    |

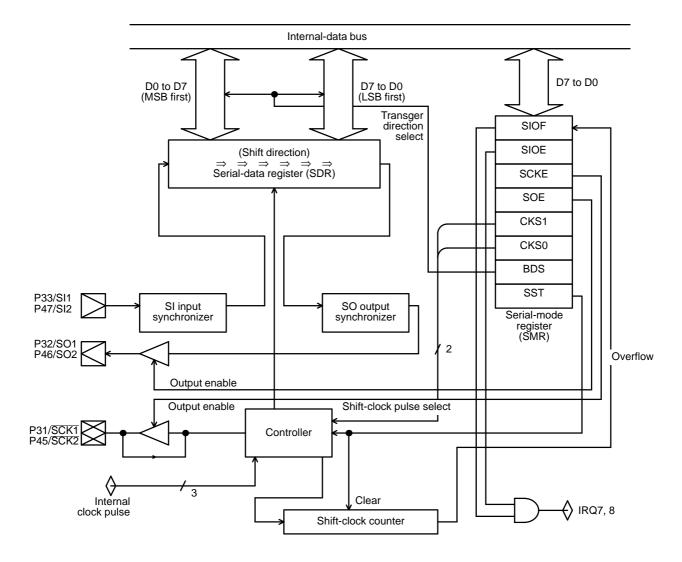

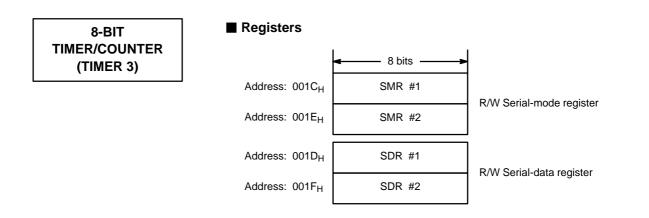

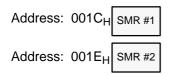

| 2.8 8-BIT SERIAL I/O 1 AND 2 2-47          |

| 2.9 EXTERNAL INTERRUPT CIRCUIT 2-53        |

| 2.10 BUZZER OUTPUT CIRCUIT 2-58            |

|                                            |

CPU

## 2.1 CPU

- This section describes the CPU hardware composition. The CPU has the following six functions.

- Memory Space

- Arrangement of 16-bit Data in Memory

- Registers

- Operation Modes and External Bus Operation

- Clock Control Block

- Interrupt Controller

#### Memory Space

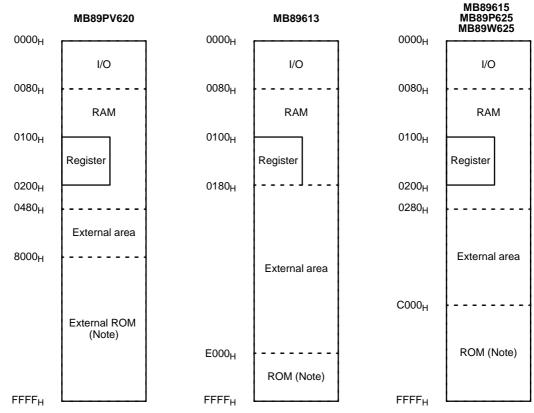

The MB89610 series of microcontrollers have a memory area of 64 Kbytes. All I/O, data, and program areas are located in this space. The I/O area is near the lowest address and the data area is immediately above it. The data area may be divided into register, stack, and direct-address areas according to the applications. The program area is located near the highest address and the tables of interrupt and reset vectors and vector-call instructions are at the highest address. Figure 2.1 shows the structure of the memory space for the MB89610 series of microcontrollers.

Note: These areas serve as external areas according to the mode.

Fig. 2.1 Memory Space of MB89610 Series of Microcontrollers

Table 2-1 Table of Reset and Interrupt Vectors

CPU

#### (1) I/O area

This area is where various resources such as control and data registers are located. The memory map for the I/O area is given in Appendix 1.

#### (2) RAM area

This area is where the static RAM is located. Addresses from  $0100_{\rm H}$  to  $017F_{\rm H}$  are also used as the general-purpose register area.

#### (3) External area

When data is read and written from and to this area with the external-bus function specified, the external device is accessed via ports 0, 1, and 2. Examples of expanding the external memory and peripheral resources by using the external- bus pins are described in 3.4 Memory Access Modes.

#### (4) ROM area

This area is where the internal ROM is located. Addresses from  $FFC0_{H}$  to  $FFFF_{H}$  are also used for the tables of interrupt and reset vectors and vectorcall instructions. Table 2-1 shows the correspondence between each interrupt number or reset and the table addresses to be referenced for the MB89610 series of microcontrollers.

|          | Table address     |                   |  |  |  |  |  |

|----------|-------------------|-------------------|--|--|--|--|--|

|          | Upper data        | Lower data        |  |  |  |  |  |

| CALLV #0 | FFC0 <sub>H</sub> | FFC1 <sub>H</sub> |  |  |  |  |  |

| CALLV #1 | FFC2 <sub>H</sub> | FFC3 <sub>H</sub> |  |  |  |  |  |

| CALLV #2 | $FFC4_{H}$        | FFC5 <sub>H</sub> |  |  |  |  |  |

| CALLV #3 | FFC6 <sub>H</sub> | FFC7 <sub>H</sub> |  |  |  |  |  |

| CALLV #4 | FFC8 <sub>H</sub> | FFC9 <sub>H</sub> |  |  |  |  |  |

| CALLV #5 | FFCA <sub>H</sub> | FFCB <sub>H</sub> |  |  |  |  |  |

| CALLV #6 | FFCC <sub>H</sub> | FFCD <sub>H</sub> |  |  |  |  |  |

| CALLV #7 | FFCE <sub>H</sub> | FFCF <sub>H</sub> |  |  |  |  |  |

| ] |               | Table a           | ddress            |

|---|---------------|-------------------|-------------------|

|   |               | Upper data        | Lower data        |

|   | Interrupt #11 | FFE4 <sub>H</sub> | FFE5 <sub>H</sub> |

|   | Interrupt #10 | FFE6 <sub>H</sub> | FFE7 <sub>H</sub> |

|   | Interrupt #9  | FFE8 <sub>H</sub> | FFE9 <sub>H</sub> |

|   | Interrupt #8  | FFEA <sub>H</sub> | FFEB <sub>H</sub> |

|   | Interrupt #7  | FFEC <sub>H</sub> | FFED <sub>H</sub> |

|   | Interrupt #6  | FFEE <sub>H</sub> | FFEF <sub>H</sub> |

|   | Interrupt #5  | FFF0 <sub>H</sub> | FFF1 <sub>H</sub> |

|   | Interrupt #4  | FFF2 <sub>H</sub> | FFF3 <sub>H</sub> |

| _ | Interrupt #3  | FFF4 <sub>H</sub> | FFF5 <sub>H</sub> |

|   | Interrupt #2  | FFF6 <sub>H</sub> | FFF7 <sub>H</sub> |

|   | Interrupt #1  | FFF8 <sub>H</sub> | FFF9 <sub>H</sub> |

|   | Interrupt #0  | FFFA <sub>H</sub> | FFFB <sub>H</sub> |

|   | Reset mode    |                   | FFFD <sub>H</sub> |

|   | Reset vector  | FFFE <sub>H</sub> | FFFF <sub>H</sub> |

Note:  $FFFC_H$  is already reserved.

CPU

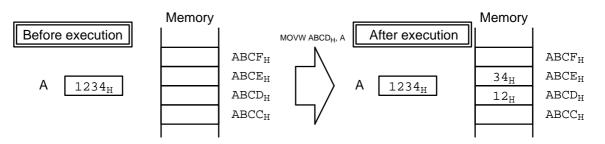

#### Arrangement of 16-bit Data in Memory Space

When the MB89610 series of microcontrollers handle 16-bit data, the data written at the lower address is treated as the upper data and that written at the next address is treated as the lower data as shown in Figure 2.2.

#### Fig. 2.2 Arrangement of 16 bit Data in Memory Space

This is the same as when 16 bits are specified by the operand during execution of an instruction. Bits closer to the OP code are treated as the upper byte and those next to it are treated as the lower byte. This is also the same when the memory address or 16-bit immediate data is specified by the operand.

#### [Example]

| MOV A                                                   | , 50 | 578 <sub>F</sub> | ł           |   | ; Extended address      |  |  |  |  |

|---------------------------------------------------------|------|------------------|-------------|---|-------------------------|--|--|--|--|

| MOV A                                                   | , #2 | 1234             | $4_{\rm H}$ |   | ; 16-bit immediate data |  |  |  |  |

| Assemble                                                |      |                  |             |   |                         |  |  |  |  |

| $\mathbf{X}\mathbf{X}\mathbf{X}\mathbf{X}_{\mathrm{H}}$ | хх   | XX               |             |   |                         |  |  |  |  |

| $XXXX_{\rm H}$                                          | 60   | 56               | 78          | ; | Extended address        |  |  |  |  |

| $XXXX_{\rm H}$                                          | E4   | 12               | 34          | ; | 16-bit immediate data   |  |  |  |  |

| $XXXX_{\rm H}$                                          | XX   |                  |             |   |                         |  |  |  |  |

|                                                         | ÷    |                  |             |   |                         |  |  |  |  |

#### Fig. 2.3 Arrangement of 16 bit Data during Execution of Instruction

Data saved in the stack by an interrupt is also treated in the same manner.

|    | 0  |     |   |

|----|----|-----|---|

| Fl | Jſ | TSI | J |

| С | Р | u |

|---|---|---|

| C |   | υ |

#### Internal Registers in CPU

The MB89610 series of microcontrollers have dedicated registers in the CPU and general-purpose registers in memory.

| Program counter (PC)                          | 16-bit long register indicating location where instructions stored                                                                                                                   |  |  |  |  |  |  |  |

|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| <ul> <li>Accumulator (A)</li> </ul>           | 16-bit long register where results of opera-<br>tions stored temporarily. The lower byte is<br>used to execute 8-bit data processing<br>instructions.                                |  |  |  |  |  |  |  |

| <ul> <li>Temporary accumulator (T)</li> </ul> | 16-bit long register where the operations<br>are performed between this register and the<br>accumulator. The lower one byte is used to<br>execute 8-bit data processing instructions |  |  |  |  |  |  |  |

| <ul> <li>Stack pointer (SP)</li> </ul>        | 16-bit long register indicating stack area                                                                                                                                           |  |  |  |  |  |  |  |

| <ul> <li>Processor status (PS)</li> </ul>     | 16-bit long register where register pointers and condition codes are stored                                                                                                          |  |  |  |  |  |  |  |

| <ul> <li>Index register (IX)</li> </ul>       | 16-bit long register for index modification                                                                                                                                          |  |  |  |  |  |  |  |

| <ul> <li>Extra pointer (EP)</li> </ul>        | 16-bit long register for memory addressing                                                                                                                                           |  |  |  |  |  |  |  |

| ▲ 16 bits                                     | - <b>&gt;</b>                                                                                                                                                                        |  |  |  |  |  |  |  |

| P C                                           | Program counter                                                                                                                                                                      |  |  |  |  |  |  |  |

| A                                             | Accumulator                                                                                                                                                                          |  |  |  |  |  |  |  |

| Т                                             | Temporary accumulator                                                                                                                                                                |  |  |  |  |  |  |  |

| IX                                            | Index register                                                                                                                                                                       |  |  |  |  |  |  |  |

| EP                                            | Extra pointer                                                                                                                                                                        |  |  |  |  |  |  |  |

| SP                                            | Stack pointer                                                                                                                                                                        |  |  |  |  |  |  |  |

| PS                                            | Processor status                                                                                                                                                                     |  |  |  |  |  |  |  |

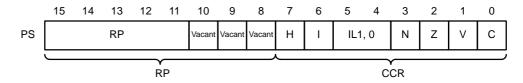

The 16 bits of the processor status (PS) can be divided into 8 upper bits for a register bank pointer (RP) and 8 lower bits for a condition code register (CCR). (See Figure 2.4.)

Fig. 2.4 Structure of Processor Status

The RP indicates the address of the current register bank. The rule for translating for the data the contents of the RP and the real addresses are as shown in Figure 2.5.

|                |              |              |              |              |              |              |              |     |              |              | RΡ           |              | Lov          | ower bits of OP o |              |              | ode |

|----------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|-----|--------------|--------------|--------------|--------------|--------------|-------------------|--------------|--------------|-----|

|                | '0'          | '0'          | '0'          | '0'          | '0'          | '0'          | '0'          | '1' | R4           | R3           | R2           | R1           | R0           | b2                | b1           | b0           |     |

|                | $\downarrow$ | ↓   | $\downarrow$ | $\downarrow$ | $\downarrow$ | $\downarrow$ | $\downarrow$ | $\downarrow$      | $\downarrow$ | $\downarrow$ |     |

| Source address | A15          | A14          | A13          | A12          | A11          | A10          | A9           | A8  | A7           | A6           | A5           | A4           | A3           | A2                | A1           | A0           | ]   |

Fig. 2.5 Rule for Translating Real Addresses at General-purpose Register Area

The CCR has bits indicating the results of operations and transfer data contents, and bits controlling the CPU operation when an interrupt occurs.

- H-flag is set when a carry or a borrow out of bit 3 into bit 4 is generated as a result of operations; it is cleared in other cases. This flag is used for decimal-correction instructions.

- I-flag

An interrupt is enabled when this flag is 1 and is disabled when it is 0. The I-flag is 0 at reset.

- IL1 and IL0 These bits indicate the level of the currently-enabled interrupt. The CPU executes interrupt processing only when an interrupt with a value smaller than the value indicated by this bit is requested.

| IL1 | IL0 | Interrupt level | High and low       |

|-----|-----|-----------------|--------------------|

| 0   | 0   | 1               | High               |

| 0   | 1   |                 | Î                  |

| 1   | 0   | 2               |                    |

| 1   | 1   | 3               | Low = No interrupt |

- N-flag The N-flag is set when the most significant bit is 1 as a result of operations; it is cleared when the MSB is 0.

- Z-flag is set when the bit is 0 as a result of operations; it is cleared in other cases.

- V-flag is set when a two's complement overflow occurs as a result of operations; it is reset when an overflow does not occur.

- C-flag is set when a carry or a borrow out of bit 7 is generated as a result of operations; it is cleared in other cases.

When the shift instruction is executed, the value of the C-flag is shifted out.

CPU

CPU

• General-purpose registers

General-purpose registers are 8-bit long registers for storing data.

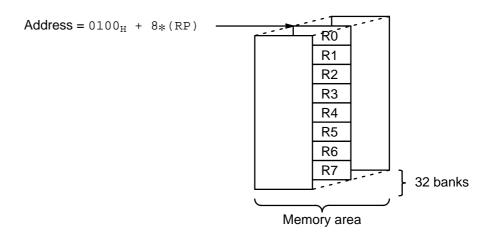

The 8-bit long general-purpose registers are in the register banks in memory. One bank has eight registers and up to 32 banks are available for the MB89610 series of microcontrollers. In the MB89613 microcontroller, when the external RAM is allocated to  $0180_{\rm H}$  to  $01FF_{\rm H}$  by the external circuit, 16 remaining banks can be extended externally. The register bank pointer (RP) indicates the currently-used bank.

Fig. 2.6 Register Bank Configuration

#### Operation Modes

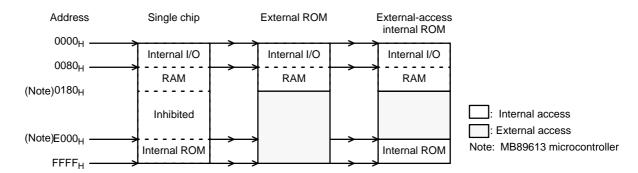

The MB89610 series of microcontrollers have the following three operation modes.

(1)Single-chip mode

(2) External-ROM mode

(3)External-access internal-ROM mode

The memory map for each mode is as follows:

#### Fig. 2.7 Memory Maps in Various Modes

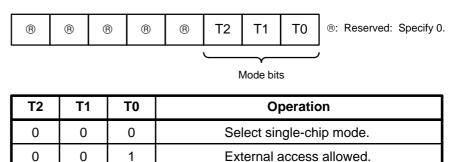

The mode that the device enters depends on the states of the device-mode pins and the contents of the mode data fetched during the reset sequence. The relationship between the states and operations of the device-mode pins is shown below.

| MOD1 | MOD0 | Description                                                                          |  |  |  |  |  |  |  |  |

|------|------|--------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| 0    | 0    | Reset vectors are read from the internal ROM. The external access does not function. |  |  |  |  |  |  |  |  |

| 0    | 1    | Reset vectors are read from the external ROM. The external access functions.         |  |  |  |  |  |  |  |  |

| 1    | 0    | Reserved for future expansion and testing.                                           |  |  |  |  |  |  |  |  |

| 1    | 1    | Write mode for products containing EPROM.                                            |  |  |  |  |  |  |  |  |

The following functions are selected according to the mode-data setting conditions.

Note: Do not select the single-chip mode with the externally-fetched mode data.

Reserved. Do not set.

Other than above

CPU

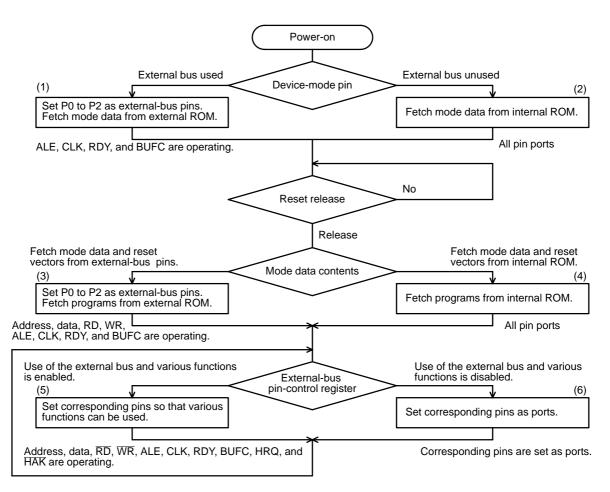

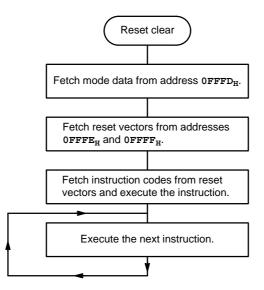

As shown in the flowchart below, each mode is set according to the status of the device-mode pins and the contents of the mode data fetched during the reset sequence.

| Setting procedure                                   | Mode selected                     | Mode pin | Mode data |

|-----------------------------------------------------|-----------------------------------|----------|-----------|

| (2)→(4)→(6)                                         | Single-chip mode                  | 00       | XXXXX000  |

| $(1)\rightarrow(3)\rightarrow$ *(5)or(6)            | External-ROM mode                 | 01       | XXXXX001  |

| $(2) \rightarrow (3) \rightarrow *(5) \text{or}(6)$ | External-access internal-ROM mode | 00       | XXXXX001  |

\* Depends on whether ready or hold function used

When the external-bus function is used, the following pins become active at default.

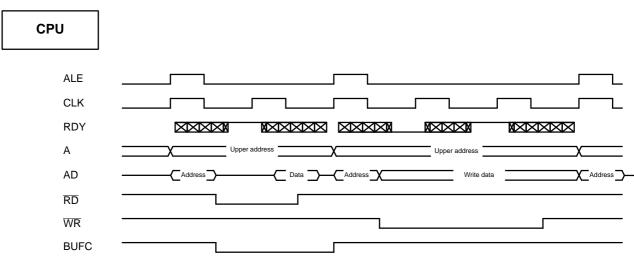

A08 to A15, AD0 to AD7, RD, WR, ALE, CLK, RDY, BUFC

The external-bus pin-control register (BCTR) is used to switch the function of the pin controlling the external bus for port 2 in the external-bus mode. When either of the bits is set to 0, the pin corresponding to the bit serves as the port. In the single-chip mode, the contents of both bits are ignored and all 8 bits of port 2 serve as parallel ports. Access to this register is not allowed in modes other than the external-bus mode. The structure of the BCTR is as follows:

#### HARDWARE CONFIGURATION

| CDU |                            | Bit 7 | Bit 6                                 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-----|----------------------------|-------|---------------------------------------|-------|-------|-------|-------|-------|-------|

| CPU | Address: 0005 <sub>H</sub> | _     | —                                     | —     | —     | —     | —     | HLD   | BUF   |

|     |                            |       |                                       |       |       |       |       | (W)   | (W)   |

|     |                            |       | Initial value<br>XXXXX01 <sub>B</sub> |       |       |       |       |       |       |

[Bit 1] HLD: Hold-enable bit.

Bit 1 is used to enable the holding operation.

| 0 | In external-bus mode, P21 and P22 serve as ports.                                             |

|---|-----------------------------------------------------------------------------------------------|

| 1 | In external-bus mode, P21 used for $\overline{\text{HAK}}$ output and P22 used for HRQ input. |

[Bit 0] BUF: BUFC-operation enable bit.

Bit 0 is used to enable the operation of the BUFC pin.

| 0 | In external-bus mode, P20 serves as port.       |

|---|-------------------------------------------------|

| 1 | In external-bus mode, P20 used for BUFC output. |

The states of the bus pins in each mode are follows:

| Pin name   | Single chip | External Access |  |  |

|------------|-------------|-----------------|--|--|

| P00 to P07 | P00 to P07  | AD7 to AD0      |  |  |

| P17        | P17         | A15             |  |  |

| P16        | P16         | A14             |  |  |

| P15        | P15         | A13             |  |  |

| P14        | P14         | A12             |  |  |

| P13        | P13         | A11             |  |  |

| P12        | P12         | A10             |  |  |

| P11        | P11         | A09             |  |  |

| P10        | P10         | A08             |  |  |

| P27        | P27         | ALE             |  |  |

| P26        | P26         | RD              |  |  |

| P25        | P25         | WR              |  |  |

| P24        | P24         | CLK             |  |  |

| P23        | P23         | RDY             |  |  |

| P22        | P22         | HRQ             |  |  |

| P21        | P21         | HAK             |  |  |

| P20        | P20         | BUFC            |  |  |

Meaning of each signal

| AD0 to AD7 | : | Address/data multiplex bus            |

|------------|---|---------------------------------------|

| A08 to A15 | : | Address bus                           |

| ALE        | : | Address-latch enable                  |

| RD         | : | Read strobe (Active at L)             |

| WR         | : | Write strobe (Active at L)            |

| CLK        | : | Clock output                          |

| RDY        | : | Bus-ready input (Wait at L)           |

| HRQ        | : | Hold request                          |

| HAK        | : | Hold-acknowledge output (Active at L) |

| BUFC       | : | Buffer control                        |

Note: RD, WR, and BUFC are not output when the address indicates the internal area.

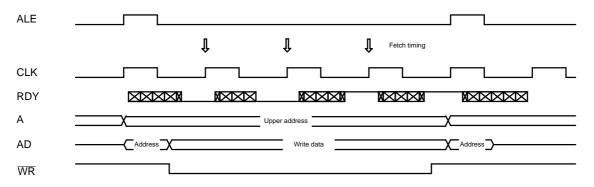

The timing concept for external access is shown below. Refer to the data sheet for details about the ERECTRICAL CHARACTERISTICS.

# FUĴĨTSU

Note: The read cycle of the RDY signal is prolonged in the same manner as the write cycle.

The RDY signal is used for the ready function. When a Low level is input, the bus cycle is prolonged in CLK cycles. Fetching is carried out near the rising edge of the CLK signal. To prolong the bus cycle, set the RDY signal to Low before the rising edge of the CLK signal.

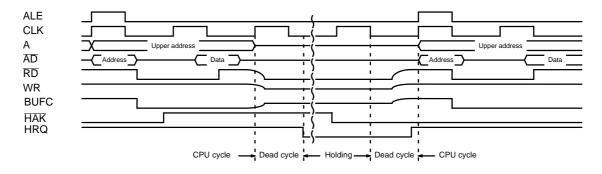

The HRQ and HAK signals are used for the hold function. To obtain the external bus, set the HRQ signal to High. After that, the CPU recognizes the bus request between instructions to stop operation and sets the HAK signal to Low after waiting one half cycle. It signals the outside that the bus is open in this way. When another device terminates use of the bus, set the HRQ signal to Low to notify the CPU. When the CPU detects the Low level of the HRQ signal, it sets the HAK signal to High and starts using the external bus after waiting one half cycle. The hold function timing concept is as follows:

CLOCK CONTROL BLOCK

## 2.2 CLOCK CONTROL BLOCK

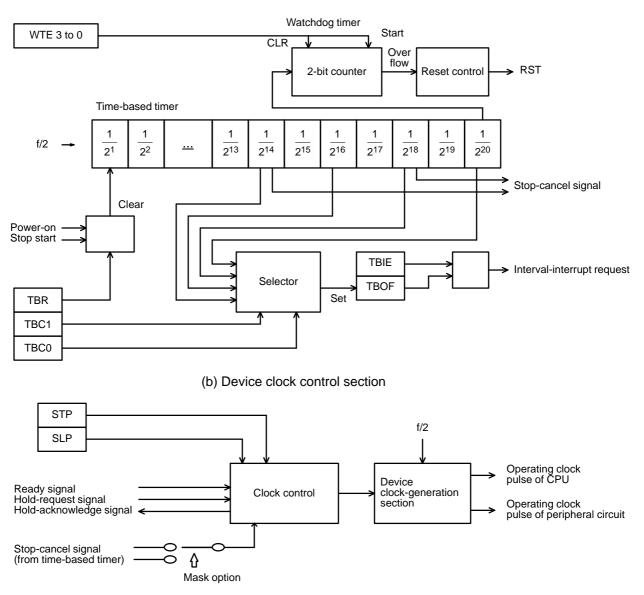

This block controls the standby operation, software reset, time-based timer, and watchdog timer.

#### Clock Control Block Diagram

(a) Time-based timer and watchdog timer

(c) Reset-control section

FUJITSU

### CLOCK CONTROL BLOCK

#### Register List

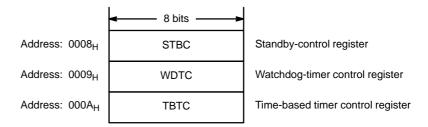

Main/sub clock control block consists of standby control register (STBC) and system clock control register (SYCC).

#### n Description of Registers

The detail of each register is described below.

TBTC

0009<sub>H</sub>

Address: 000A<sub>H</sub>

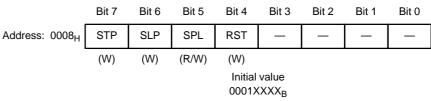

|  | (1) | Standby-conrol | register | (STBC) |

|--|-----|----------------|----------|--------|

|--|-----|----------------|----------|--------|

#### [Bit 7] STP: Stop bit

Bit 7 is used to specify switching to the stop mode.

| 0 | No operation |

|---|--------------|

| 1 | Stop mode    |

This bit is cleared at reset or stop cancellation. 0 is read whenever this bit is read.

#### [Bit 6] SLP: Sleep bit

Bit 6 is used to specify switching to the sleep mode.

| ſ | 0 | No operation |

|---|---|--------------|

|   | 1 | Sleep mode   |

2-14

This bit is cleared at reset or sleep and stop cancellation. The stop mode is selected when 1 is written simultaneously to the STP and SLP bits. 0 is read whenever this bit is read.

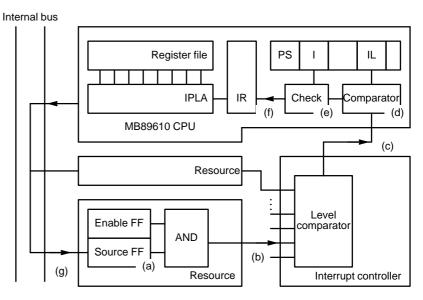

[Bit 5] SPL: Pin state specifying bit

Bit 5 is used to specify the state of the external pin in the stop mode.

| 0 | Holds state and level immediately before stop mode |

|---|----------------------------------------------------|

| 1 | High impedance                                     |

This bit is cleared at reset.

| CLOCK<br>CONTROL BLOCK                               | [Bit 4] RST: Software reset bit<br>Bit 4 is used to specify the software reset. |

|------------------------------------------------------|---------------------------------------------------------------------------------|

|                                                      | 0     Generates 4-cycle reset signal       1     No operation                   |

|                                                      | 1 is read when this bit is read.                                                |

| Address: STBC                                        | (2) Watchdog-timer control register (WDTC)                                      |

| 0008 <sub>H</sub>                                    | Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0                                 |

| Address: WDTC                                        | Address: 0009 <sub>H</sub> WTE3 WTE2 WTE1 WTE0                                  |

| 0009 <sub>H</sub><br>Address: 000A <sub>H</sub> TBTC | (W) (W) (W) (W)<br>Initial value<br>XXXXXXX <sub>B</sub>                        |

The WDTC register controls the watchdog timer.

[Bits 3 to 0] WTE3 to WTE0: Watchdog timer control bits These bits are used to control the watchdog timer.

1) First write after reset

| 0101             | Start watchdog timer |

|------------------|----------------------|

| Other than above | No operation         |

2) Second write after reset

| 0101             | Clear watchdog-timer counter |  |  |  |

|------------------|------------------------------|--|--|--|

| Other than above | No operation                 |  |  |  |

The watchdog timer can be stopped only by reset. 1111 is read when these bits are read.

(3) Time-based timer control register (TBTC)

|                            | Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 |   |   |       |       |     |       | Bit 0 |

|----------------------------|-------------------------------------------------|---|---|-------|-------|-----|-------|-------|

| Address: 000A <sub>H</sub> |                                                 | - | _ | TBIE  | TBOF  | TBR | TBC1  | TBC0  |

|                            |                                                 |   |   | (R/W) | (R/W) | (W) | (R/W) | (R/W) |

|                            | Initial value<br>XXX00000 <sub>B</sub>          |   |   |       |       |     |       |       |

The TBTC register controls the time-based timer and interval timer.

[Bit 4] TBIE: Interval-interrupt enable bit

Bit 4 is used to enable an interrupt by the interval timer.

| 0 | Interval-interrupt disabled |  |  |

|---|-----------------------------|--|--|

| 1 | Interval-interrupt enabled  |  |  |

This bit is cleared at reset.

[Bit 3] TBOF: Interval-timer overflow bit

(1) This bit is used to clear the interval-timer overflow flag when writing.

| 0 | Clear interval-timer overflow flag. |

|---|-------------------------------------|

| 1 | No operation                        |

(2) This bit indicates that the interval timer overflows at reading.

| 0 | Interval timer does not overflow |  |  |

|---|----------------------------------|--|--|

| 1 | Interval timer overflows         |  |  |

1 is read when the Read Modify Write instructions are read. If the TBOF bit is set to 1 when the TBIE bit is 1, an interrupt request is output. This bit is cleared at reset.

[Bit 2] TBR: Time-based timer initialize bit

Bit 2 is used to clear the time-based timer counter.

| 0 | Time-based timer counter cleared |  |

|---|----------------------------------|--|

| 1 | No operation                     |  |

1 is read when this bit is read.

[Bits 1 and 0] TBC1 and TBC0: Interval-time setting bits These bits are used to set the cycle of the interval timer.

| TBC1 | TBC0 | Interval time at 10 MHz oscillation |  |  |

|------|------|-------------------------------------|--|--|

| 0    | 0    | 3.3 ms                              |  |  |

| 0    | 1    | 13.1 ms                             |  |  |

| 1    | 0    | 52.4 ms                             |  |  |

| 1    | 1    | 209.7 ms                            |  |  |

These bits are cleared at reset.

CLOCK CONTROL BLOCK

#### Description of Operation

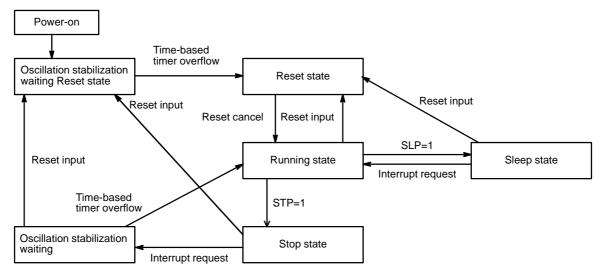

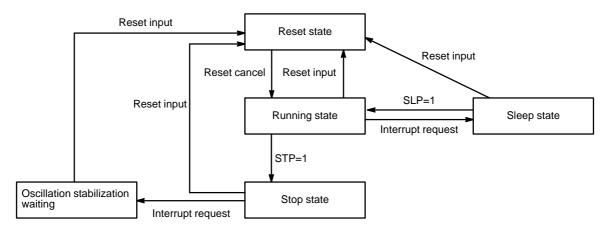

(1) Low-power consumption mode

There are two low-power consumption modes: sleep and stop. Table 2-2 lists the state in each operation mode.

| Table 2-2 C | Operating S | State in Low-Po | ower Consumptic | n Modes |

|-------------|-------------|-----------------|-----------------|---------|

|-------------|-------------|-----------------|-----------------|---------|

| Operation mode | Switching conditions | Oscillation | Clock    | CPU   | Peripheral<br>circuit | Pin      | Canceling       |

|----------------|----------------------|-------------|----------|-------|-----------------------|----------|-----------------|

| Sleep          | SLP=1                | Operates    | Operates | Stops | Operates              | Operates | Reset/interrupt |

| Stop (SPL = 0) | STP=1                | Stops       | Stops    | Stops | Stops                 | Stops    | Reset/interrupt |

| Stop (SPL = 1) | STP=1                | Stops       | Stops    | Stops | Stops                 | Hi-Z     | Reset/interrupt |

- The sleep mode stops only the operating clock pulse of the CPU; other operations are continued.

- The stop mode stops oscillation. Therefore, data can be held with the lowest power consumption.

- (a) Sleep mode

- Switching to sleep mode

- Writing 1 at the SLP bit (bit 6) of the STBC switches the mode to sleep.

- The sleep mode stops the operating clock pulses of the CPU; only the CPU stops and the peripheral circuits continue to operate.

- If an interrupt is requested when 1 is written at the SLP bit (bit 6), execution of the instruction continues without switching to the sleep mode.

- The contents of registers and RAM are held in the sleep mode.

- · Canceling sleep mode

- The sleep mode is canceled by inputting the reset signal and requesting an interrupt.

- When the reset signal is input during the sleep mode, the CPU is switched to the reset state and the sleep mode is canceled.

- When an interrupt higher than level 11 is requested from the peripheral circuit during the sleep mode, the sleep mode is canceled.

- When the I-flag and IL bits are set to accept an interrupt after canceling, the CPU executes the interrupt processing. When they are set to ignore, the CPU executes the interrupt processing from the next instruction.

- (b) Stop mode

- Switching to stop mode

- Writing 1 at the STP bit (bit 7) of the STBC switches the mode to stop.

- The stop mode stops oscillation and all chip functions stop. Therefore, data can be held with the lowest power consumption.

| CLOCK<br>CONTROL BLOCK | <ul> <li>During the stop mode, whether the I/O and output pins are set to the<br/>previous or high-impedance state can be controlled by the SPL bit (bit<br/>5) of the STBC.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                      |

|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                        | <ul> <li>If an interrupt is requested when 1 is written at the STP bit (bit 7), execution of the instruction continues without switching to the stop mode.</li> <li>The contents of registers and RAM are held in the stop mode.</li> </ul>                                                                                                                                                                                                                                                                                                                                                  |

|                        | <ul> <li>Canceling stop mode</li> <li>The stop mode is canceled by inputting the reset signal and requesting<br/>an interrupt.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                        | <ul> <li>When a reset signal is input during the sleep mode, the CPU is switched to the reset state, but the stop mode is canceled.</li> <li>When an interrupt higher than level 11 is requested from the external-interrupt circuit during the stop mode, the stop mode is canceled.</li> <li>After the oscillation stabilization time since the stop mode was canceled has elapsed, when the I-flag and IL bits are set to accept an interrupt, the CPU executes the interrupt processing. When they are set to ignore, the CPU executes the interrupt processing from the next</li> </ul> |

|                        | <ul> <li>instruction.</li> <li>The oscillation stabilization time can be selected from the two types in Table 3 by the mask option.</li> <li>With Power-on Reset Available selected, when the stop mode is can-</li> </ul>                                                                                                                                                                                                                                                                                                                                                                   |

With Power-on Reset Available selected, when the stop mode is canceled by inputting the reset signal, the CPU is switched to the oscillation stabilization wait state. Thus, the reset sequence is executed after the oscillation stabilization time has elapsed.

Table 2-3

Selection of Oscillation Stabilization Time

| Number of counts for minimum instruction time | Time at 10 MHz oscillation | Remarks                |

|-----------------------------------------------|----------------------------|------------------------|

| About 2 <sup>16</sup> counts                  | About 26.2 ms              | For crystal oscillator |

| About 2 <sup>12</sup> counts                  | About 1.64 ms              | For ceramic oscillator |

Fig. 2.8 State Transition Diagram at Low-power Consumption(with power-on reset)

#### Fig. 2.9 State Transition Diagram in Low-power Consumption Modes(without power-on reset)

#### (2) Watchdog timer

Program runaway is detected by the watchdog timer.

- (a) Starting watchdog timer

- Write 0101 first at the WTE3 to WTE0 bits (bits 3 0) of the WDTC after reset.

(b) Operation watchdog timer

- Write the second or later 0101 at the WTE3 to WTE0 bits (bits 3 0) to clear the watchdog-timer counter.

- If the watchdog-timer counter is not cleared within the time specified in Table 4, a reset occurs in the watchdog timer after about two instruction cycles to initialize the chip.

- The watchdog-timer counter is cleared by switching to the standby and hold states.

- The clock source for the watchdog timer is supplied from the timebased timer. Therefore, the watchdog timer is cleared as soon as the time-based timer is cleared.

- Once started, the watchdog timer cannot be stopped until a reset occurs.

#### Table 2-4 Watchdog Timer Interval Time (at 10 MHz Oscillation)

| Minimum time   | Maximum time   |

|----------------|----------------|

| About 209.7 ms | About 419.4 ms |

# CLOCK CONTROL BLOCK

#### (3) Time-based timer

The time-based timer consists of 20 counters which use a 1/2 oscillation as a clock source. This timer has functions for the watchdog timer, the timer for waiting for stable oscillation, and the interval timer for causing an interrupt in a fixed cycle.

(a) Control of time-based timer

- The time-based timer counter is cleared by writing 0 at the TBR bit (bit 2) of the TBTC, or by switching to the stop mode.

- In other cases, the counter is incremented for as long as the clock pulse oscillates.

(b) Functions of interval timer

- The TBOF bit (bit 3) is set at every interval time specified by the TBC1 and TBC0 bits (bits 1 and 0) of the TBTC.

- This interval time is based on the time when the time-based timer counter is finally cleared.

- The TBOF bit (bit 3) is cleared by switching to the stop mode since the time-based timer is used as the counter for waiting for oscillation stabilization in returning.

- If 1 is already set at the TBIE bit (bit 4) when the TBOF bit (bit 3) is set, an interval interrupt occurs.

- The interrupt source is cleared by writing 0 at the TBOF bit (bit 3).

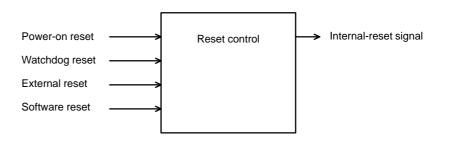

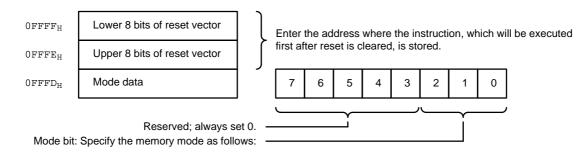

# (4) Reset

There are four types of resets as shown in Table 2-5.

# Reset name Description External-pin reset Sets external-reset pin to Low Software reset Writes 0 at RST (bit 4) of STBC Watchdog reset Overflows watchdog timer

#### Table 2-5 Sources of Reset

When the power-on reset and reset during the stop mode are used, the oscillation stabilization time is needed after the oscillator operates. The timebased timer controls this stabilization time. Consequently, the operation does not start immediately even after canceling the reset.

Turns power on

Power-on reset

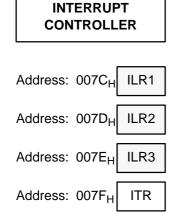

INTERRUPT CONTROLLER

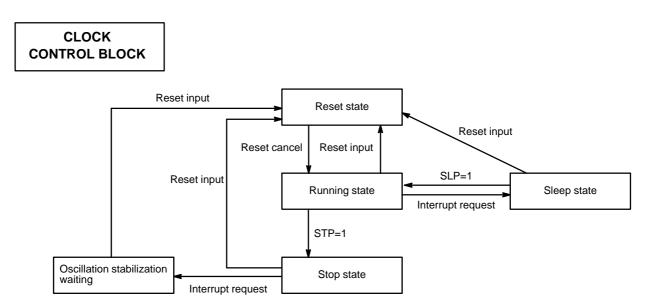

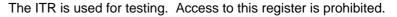

# 2.3 INTERRUPT CONTROLLER

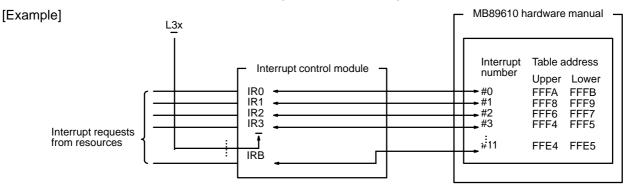

The interrupt controller for the  $F^2MC-8L$  is located between the CPU and each resource. This controller receives interrupt requests from the resources, assigns priority to them, and transfers the priority to the CPU; it also decides the priority of same-level interrupts.

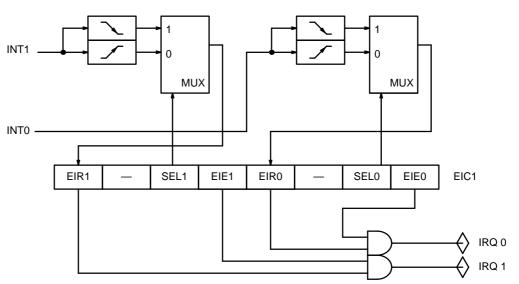

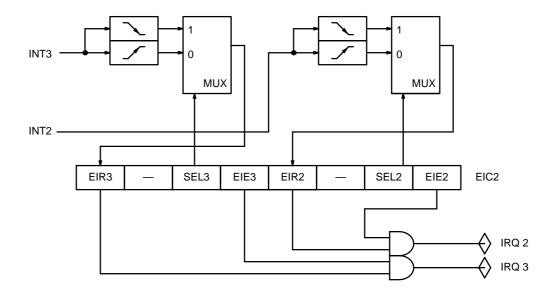

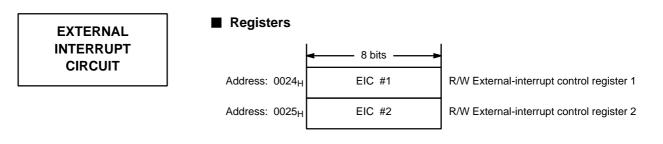

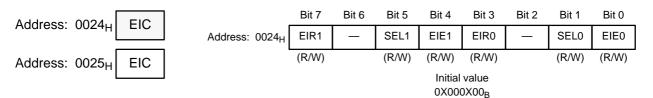

# Block Diagram

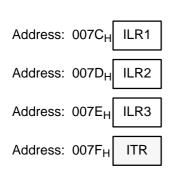

# Register List

|                            | ◄ 8 bits → |   |                             |

|----------------------------|------------|---|-----------------------------|

| Address: 007C <sub>H</sub> | ILR1       | W | Interrupt level register #1 |

| Address: 007D <sub>H</sub> | ILR2       | W | Interrupt level register #2 |

| Address: 007E <sub>H</sub> | ILR3       | W | Interrupt level register #3 |

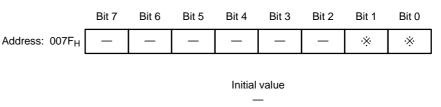

| Address: 007F <sub>H</sub> | ITR        | — | Interrupt test register     |

# Description of Registers

(1) Interrupt level register (ILRx: Interrupt Level Register x)

|                            | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3                      | Bit 2 | Bit 1 | Bit 0 |

|----------------------------|-------|-------|-------|-------|----------------------------|-------|-------|-------|

| Address: 007C <sub>H</sub> | L31   | L30   | L21   | L20   | L11                        | L10   | L01   | L00   |

| Address: 007D <sub>H</sub> | L71   | L70   | L61   | L60   | L51                        | L50   | L41   | L40   |

| Address: 007E <sub>H</sub> | LB1   | LB0   | LA1   | LA0   | L91                        | L90   | L81   | L80   |

|                            | (W)   | (W)   | (W)   | (W)   | (W)                        | (W)   | (W)   | (W)   |

|                            |       |       |       |       | value<br>I111 <sub>B</sub> |       |       |       |

The ILRx sets the interrupt level of each resource. The figure at the center of each bit corresponds to the interrupt number.

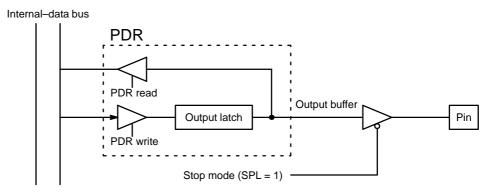

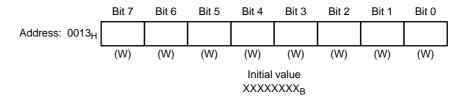

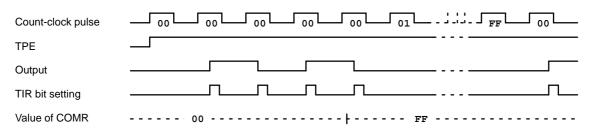

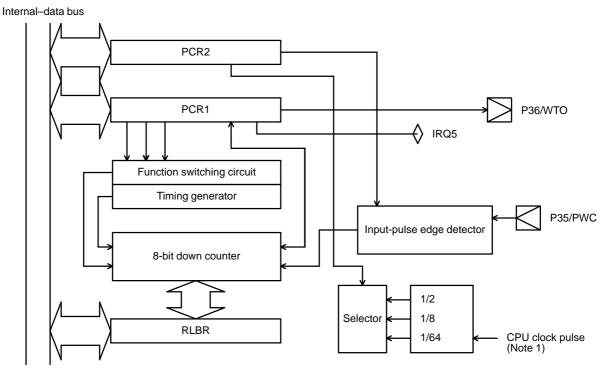

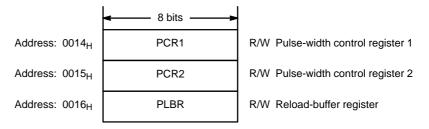

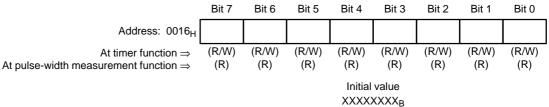

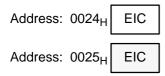

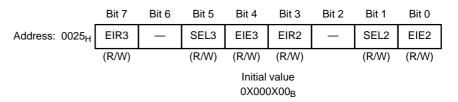

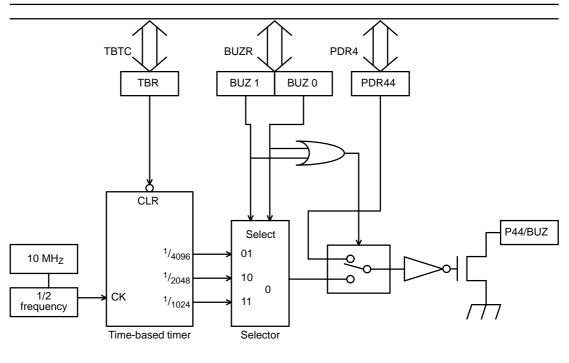

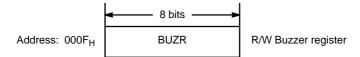

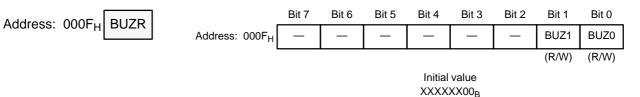

[Bit 7 and 6][Bit 5 and 4][Bit 3 and 2][Bit 1 and 0]Lx1, Lx0: Interrupt level setting bit