FUJITSU SEMICONDUCTOR

CONTROLLER MANUAL

CM25-10126-1E

# F<sup>2</sup>MC-8L 8-BIT MICROCONTROLLERS MB89863 Series HARDWARE MANUAL

# PREFACE

Thank you for choosing FUJITSU semiconductor products.

The MB89863 is a proprietary 8-bit single-chip microcontroller developed as a specific-application (inverter control) version of the F<sup>2</sup>MC\*-8L (MB89600 series) Family of microcontrollers, and is intended for use with ASIC (application-specific IC) and other low-voltage applications.

This manual describes the functions and operations of the MB89863 microcontroller. Please be sure to read it through carefully.

The following terms and definitions are used throughout this manual.

O One instruction cycle is equivalent to four oscillator clock cycles.

Oscillation at 4.2 MHz: 1 instruction cycle =  $0.95 \,\mu s$

Oscillation at 8 MHz: 1 instruction cycle =  $0.50 \ \mu s$

\*: F<sup>2</sup>MC is an abbreviation for FUJITSU Flexible Microcontroller

This manual is organized as follows.

Chapter 1 General

This chapter describes the model lineup of the MB89863 microcontrollers, with an overview of each model.

Chapter 2 Hardware Configuration

This chapter describes the internal configuration and operating modes of the F<sup>2</sup>MC\*-8L CPU and specifications for the hardware built into the MB89863 microcontroller.

Chapter 3 Operation

This chapter describes the use of the MB89863, including reset sequence, interrupts, external bus operation, and low-power consumption modes.

Chapter 4 Instruction Overview

This chapter describes instructions used with the F<sup>2</sup>MC\*-8L Family microcontrollers.

**Chapter 5 Electrical Characteristics**

This chapter describes absolute maximum ratings, recommended operating conditions, DC and AC standards, and electrical characteristics for the A/D converter unit.

#### Appendix I/O Map

The I/O map lists registers in the I/O area.

- The products described in this manual and the specifications thereof may be changed without prior notice. To obtain up-to-date information and/or specifications, contact your Fujitsu sales representative or Fujitsu authorized dealer.

- 2. Fujitsu will not be liable for infringement of copyright, industrial property right, or other rights of a third party caused by the use of information or drawings described in this manual.

- 3. The contents of this manual may not be transferred or copied without the express permission of Fujitsu.

- 4. The products contained in this document are not intended for use with equipments which require extremely high reliability such as aerospace equipments, undersea repeaters, nuclear control systems or medical equipments for life support.

- 5. Some of the products described in this manual may be strategic materials (or special technology) as defined by the Foreign Exchange and Foreign Trade Control Law. In such cases, the products or portions thereof must not be exported without permission as defined under the Law.

# CONTENTS

| Chapter   | 1:   | OVERVIEW 1                                  |         |

|-----------|------|---------------------------------------------|---------|

| 1.1       | Feat | ures                                        | ····· 1 |

| 1.2       | Proc | luct Lineup                                 | 2       |

| 1.3       | Bloo | ck Diagram                                  | 3       |

| 1.4       | Pin  | Assignment                                  | 4       |

| 1.5       | Exte | ernal Dimensions                            | 5       |

| 1.6       | Pin  | Descriptions                                | 6       |

| 1.7       |      | dling Devices                               |         |

| 1.8       | Dev  | elopment Environment                        | 9       |

| Chapter 2 | 2:   | HARDWARE CONFIGURATION                      | 10      |

| 2.1       | CPU  | J                                           | 10      |

| 2.1       | 1.1  | Memory Space                                | 10      |

| 2.1       | 1.2  | Locating Memory Space in 16-bit Data        | 12      |

| 2.1       | 1.3  | Registers                                   | 13      |

| 2.1       | 1.4  | Operating Modes                             | 16      |

| 2.1       | 1.5  | Clock Controller                            |         |

| 2.1       | 1.6  | Interrupt Controller                        |         |

| 2.2       | Peri | pheral Functions                            |         |

| 2.2       | 2.1  | I/O Ports ·····                             |         |

| 2.2       | 2.2  | Timer Unit                                  | 38      |

| 2.2       | 2.3  | 8-Bit PWM Timers 1 and 2                    | 69      |

| 2.2       | 2.4  | UART ·····                                  |         |

| 2.2       | 2.5  | A/D Converter ·····                         |         |

| 2.2       | 2.6  | External Interrupt Circuit                  |         |

| Chapter 3 | 3:   | OPERATION                                   | 95      |

| 3.1       |      | ck Pulse Generator                          |         |

| 3.2       | Res  | et                                          |         |

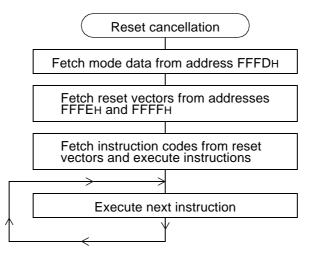

| 3.2       | 2.1  | Reset Operation                             |         |

| 3.2       | 2.2  | Reset Conditions                            |         |

| 3.3       |      | rrupts                                      |         |

| 3.4       |      | Power Consumption Modes                     |         |

| 3.5       | Pin  | States in Sleep, Stop, Hold and Reset Modes | ·· 101  |

| Chapter | 4: INSTRUCTION TABLES103                 |

|---------|------------------------------------------|

| 4.1     | Transfer-Related Instructions103         |

| 4.2     | Operation-Related Instructions           |

| 4.3     | Branch-Related Instructions105           |

| 4.4     | Other Instructions                       |

| 4.5     | Instruction Map106                       |

| Chapter | 5: ELECTRICAL CHARACTERISTICS107         |

| 5.1     | Absolute Maximum Ratings107              |

| 5.2     | Recommended Operating Conditions         |

| 5.3     | DC Standards                             |

| 5.4     | AC Standards110                          |

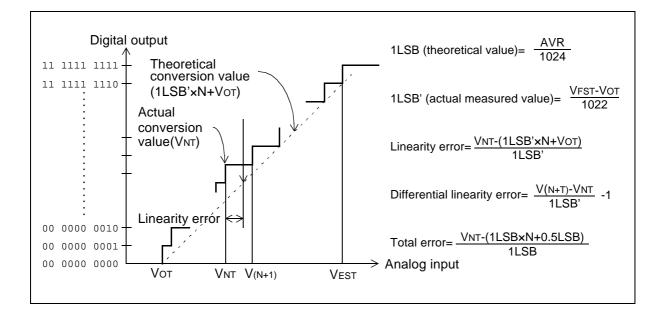

| 5.5     | A/D Converter Electrical Characteristics |

| Appendi | x 1: I/O MAP117                          |

# Chapter 1: OVERVIEW

The MB89863 is a single-chip microcontroller using the  $F^2MC-8L$  core for low-voltage, high-speed operation, with built-in peripherals including a timer unit, a timer, UART, A/D converter, and external interrupt. This product is optimized for pulse output for the control of AC inverter motors.

### 1.1 Features

• F<sup>2</sup>MC-8L CPU Core

|                                                    | Multiplication and division instructions |

|----------------------------------------------------|------------------------------------------|

| Instruction set optimized for controller operation | 16-bit arithmetic operations             |

|                                                    | Instruction test and branch instructions |

|                                                    | Bit manipulation instructions, etc.      |

• Timer Unit

Outputs a non-overlapping 3-phase waveform for AC inverter motor control. Can also be used as PWM (4 channels).

• 8-bit PWM timer (2 channels)

Can be used as a reload timer or a PWM.

• UART

Full-duplex double buffer Transfers synchronous or asynchronous data.

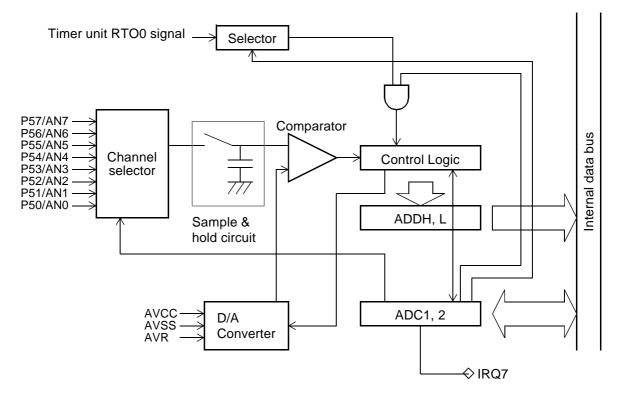

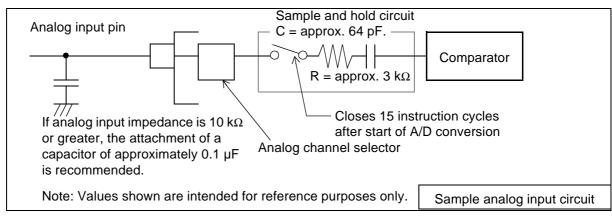

• A/D Converter

10-bit resolution, conversion time of 33 instruction cycles. Can be started by timer unit.

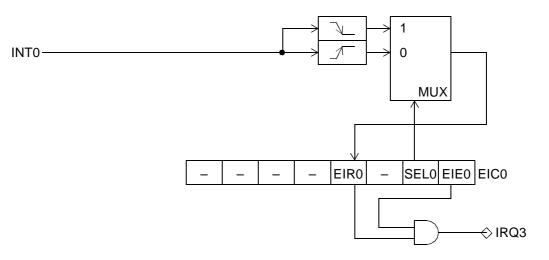

• External Interrupt Input (1 channel)

Can also be used to wake from low-power consumption modes (includes edge detection function).

• Low-Power Consumption Modes

Stop mode (oscillator stops, virtually no current consumed) Sleep mode (CPU stops, current consumption reduced to approximately one-third of normal)

# **1.2 Product Lineup**

Table 1.2.1 lists the product lineup for the MB89863 and MB89P/W857 series of microcontrollers.

| Part No.                  | MB89863                                                                                                                                                                                                                                         | MB89P857                                                                                                             | MB89W857                    |  |  |

|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|-----------------------------|--|--|

| Туре                      | Mass-producted (mask ROM) product                                                                                                                                                                                                               | One-time/EPROM/evaluation products                                                                                   |                             |  |  |

| ROM size                  | $8K \times 8$ bits, built-in                                                                                                                                                                                                                    | 32K × 8 bits (internal PRO<br>general-purpose EPROM                                                                  |                             |  |  |

| RAM size                  | $256 \times 8$ bits, built-in                                                                                                                                                                                                                   | 1K × 8 b                                                                                                             | its, built-in               |  |  |

| CPU functions             | Number of basic i<br>Instruction bit len<br>Instruction length<br>Data bit length:                                                                                                                                                              | 6                                                                                                                    | S                           |  |  |

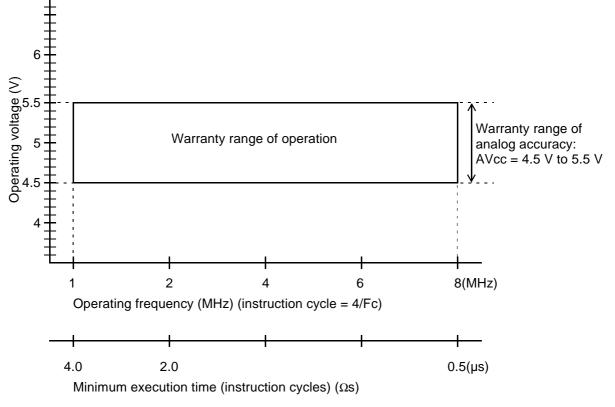

| Minimum execution time    | 0.95 μs/4.2 MHz<br>0.5 μs/8 MHz                                                                                                                                                                                                                 | 0.4 µs/                                                                                                              | /10 MHz                     |  |  |

| Interrupt processing time | 8.57 μs/4.2 MHz<br>4.5 μs/8 MHz                                                                                                                                                                                                                 | 3.6 μs/                                                                                                              | /10 MHz                     |  |  |

| I/O ports                 | Maximum 38 ports                                                                                                                                                                                                                                | Maximu                                                                                                               | m 53 ports                  |  |  |

| Timer unit                | 10-bit up/down counter timer × 1<br>Compare register with buffer × 4<br>Compare-clear register with buffer, zero detection pin control, 4 output channels,<br>non-overlapping 3-phase waveform output, 3-phase independent dead-time timer      |                                                                                                                      |                             |  |  |

| PWM timer                 | <ul> <li>8-bit reload timer operation (toggle output available, operating clock cycle: 1 to 64 instruction cycles)</li> <li>8-bit resolution PWM operation (conversion cycle: 255 to 16,320 instruction cycles), 2 built-in channels</li> </ul> |                                                                                                                      |                             |  |  |

| UART                      | 8-bit length, clock-synd                                                                                                                                                                                                                        | chronous/clock-asynchronou                                                                                           | is data transfer capability |  |  |

| Serial I/O                |                                                                                                                                                                                                                                                 | 8-bit length, LSB first/MSB first selection<br>Transfer clock (selection of external signa<br>32 instruction cycles) |                             |  |  |

| A/D converter             | 10-bit resolution × 8 channels<br>A/D conversion time: 33 instruction cycles<br>External startup or continuous startup by timer unit compare channel 0 (no exter-<br>nal startup on MB89863)                                                    |                                                                                                                      |                             |  |  |

|                           | 1 channel                                                                                                                                                                                                                                       | 4 ch                                                                                                                 | annels                      |  |  |

| External interrupts       | Selection of rising or falling edge<br>Can be used for wake-up from stop/sleep mode (edge detection also available in<br>stop mode)                                                                                                             |                                                                                                                      |                             |  |  |

| Standby mode              |                                                                                                                                                                                                                                                 | Sleep mode, stop mode                                                                                                |                             |  |  |

| Process                   |                                                                                                                                                                                                                                                 | CMOS                                                                                                                 |                             |  |  |

| Package                   | QFP-48                                                                                                                                                                                                                                          | SHE                                                                                                                  | DIP-64                      |  |  |

| Operating voltage         | 5V±10%                                                                                                                                                                                                                                          | 0.7.4                                                                                                                | o 5.5 V                     |  |  |

Table 1.2.1 MB89863 and MB89P/W857 Series Product Lineup

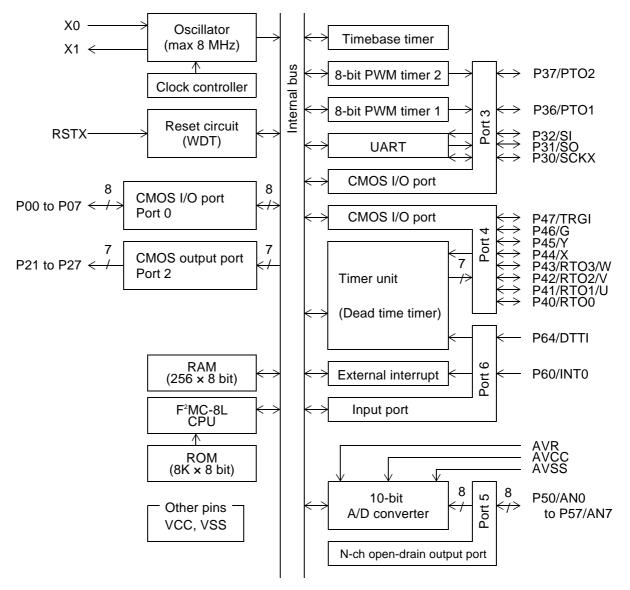

## 1.3 Block Diagram

Fig. 1.3.1 Block Diagram (MB89863)

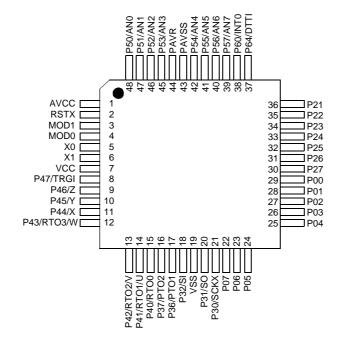

# 1.4 Pin Assignment

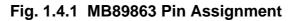

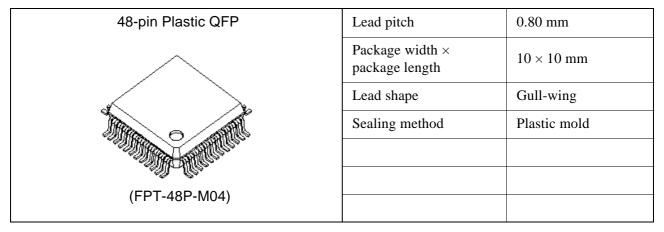

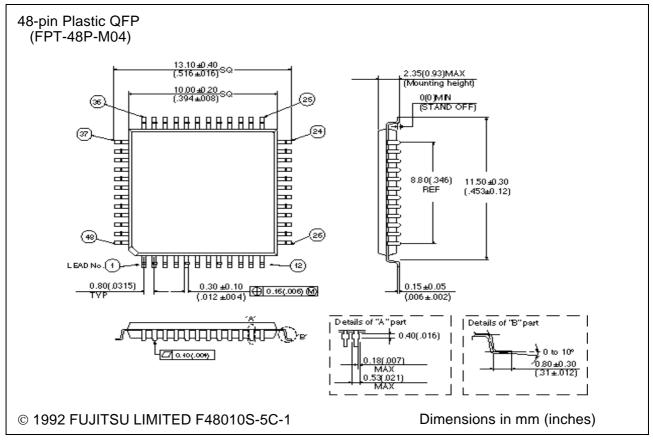

# **1.5 External Dimensions**

# FPT-48P-M04

#### EIAJ code: \*QFP048-P-1010-1

**Note:** External dimensions on specification diagrams are for reference purposes only. Users should consult directly for final information.

#### Fig. 1.5.1 External Dimensions (QFP48)

# **1.6 Pin Descriptions**

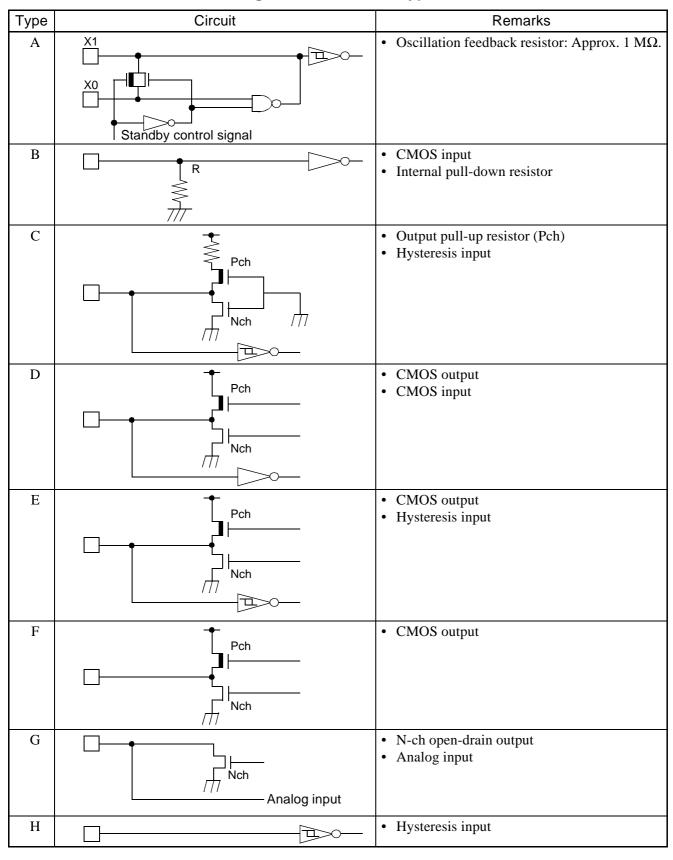

Table 1.6.1 lists the pin functions, and I/O circuit diagrams are shown in Figure 1-6-1.

| Table 1.0.1 Fill Description |            |                 |                                                                                                                                    |  |  |  |

|------------------------------|------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Pin No.<br>QFP48             | Pin name   | Circuit<br>type | Function                                                                                                                           |  |  |  |

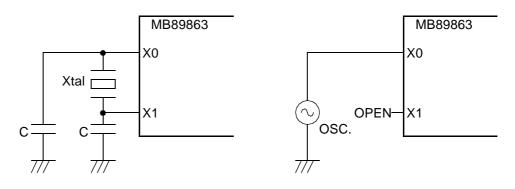

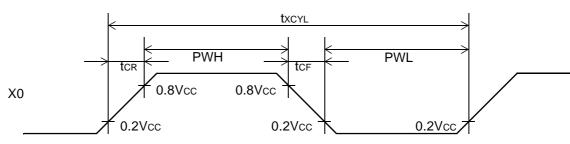

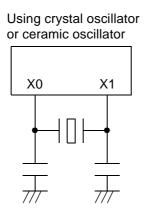

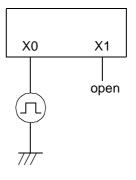

| 5                            | X0         |                 | Crystal oscillator pins (max 8 MHz)                                                                                                |  |  |  |

| 6                            | X1         | A               | Crystal oscillator pins (max 8 MHz)                                                                                                |  |  |  |

| 3                            | MOD0       |                 | Operating mode selection input pins.                                                                                               |  |  |  |

| 4                            | MOD1       | В               | Connect directly to VSS.<br>Internal pull-down resistor                                                                            |  |  |  |

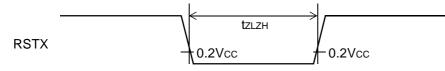

| 2                            | RSTX       | С               | Reset input pin<br>Low-level input signal initializes internal circuits.<br>Hysteresis input, internal pull-up resistor            |  |  |  |

| 22 to 29                     | P07 to P00 | D               | General-purpose I/O ports                                                                                                          |  |  |  |

| 30 to 36                     | P27 to P21 | F               | General-purpose output ports                                                                                                       |  |  |  |

| 21                           | P30/SCKX   | Е               | General-purpose I/O port.<br>Also functions as UART clock I/O pin. Hysteresis input.                                               |  |  |  |

| 20                           | P31/SO     | Е               | General-purpose I/O port.<br>Also functions as UART data output pin. Hysteresis input.                                             |  |  |  |

| 18                           | P32/SI     | Е               | General-purpose I/O port.<br>Also functions as UART data input pin. Hysteresis input.                                              |  |  |  |

| 17                           | P36/PT-1   | Е               | General-purpose I/O port.<br>Also functions as 8-bit PWM ch1 pulse output pin. Hysteresis input.                                   |  |  |  |

| 16                           | P37/PT-2   | Е               | General-purpose I/O port.<br>Also functions as 8-bit PWM ch2 pulse output pin. Hysteresis input.                                   |  |  |  |

| 15                           | P40/RTO0   | Е               | General-purpose I/O port.<br>Also functions as timer unit pulse output pin. Hysteresis input.                                      |  |  |  |

| 14                           | P41/RTO1/U | Е               | General-purpose I/O port.<br>Also functions as timer unit pulse output or non-overlapping 3-phase<br>output pin. Hysteresis input. |  |  |  |

| 13                           | P42/RTO2/V | Е               | General-purpose I/O port.<br>Also functions as timer unit pulse output or non-overlapping 3-phase<br>output pin. Hysteresis input. |  |  |  |

| 12                           | P43/RTO3/W | Е               | General-purpose I/O port.<br>Also functions as timer unit pulse output or non-overlapping 3-phase<br>output pin. Hysteresis input. |  |  |  |

| 11                           | P44/X      | Е               | General-purpose I/O port.<br>Also functions as non-overlapping 3-phase output pin. Hysteresis<br>input.                            |  |  |  |

#### Table 1.6.1 Pin Description

| Pin No.              | Pin name                                       | Circuit | Function                                                                                                                                                                 |  |

|----------------------|------------------------------------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| QFP48                | Tinname                                        | type    |                                                                                                                                                                          |  |

| 10                   | P45/Y                                          | Е       | General-purpose I/O port.<br>Also functions as non-overlapping 3-phase output pin. Hysteresis<br>input.                                                                  |  |

| 9                    | P46/Z                                          | Е       | General-purpose I/O port.<br>Also functions as non-overlapping 3-phase output pin. Hysteresis<br>input.                                                                  |  |

| 8                    | P47/TRGI                                       | Е       | General-purpose I/O port.<br>Also functions as timer unit trigger input pin. Hysteresis input.                                                                           |  |

| 39 to 42<br>45 to 48 | P57/AN7 to<br>P54/AN4<br>P53/AN3 to<br>P50/AN0 | G       | N-ch open-drain output ports.<br>Also function as A/D converter analog input pins.                                                                                       |  |

| 38                   | P60/INTO                                       | Н       | General-purpose input port.<br>Also functions as external interrupt input pins. Hysteresis input.                                                                        |  |

| 37                   | P64/DTTI                                       | Н       | General-purpose input port.<br>Also functions as dead time timer disable signal input pin. Hysteresis<br>input. DTTI input function includes noise cancellation circuit. |  |

| 7                    | VCC                                            | _       | Power supply pin.                                                                                                                                                        |  |

| 19                   | VSS                                            | _       | Power supply (GND) pin.                                                                                                                                                  |  |

| 1                    | AVCC                                           | _       | Power supply pin for A/D converter                                                                                                                                       |  |

| 44                   | AVR                                            | _       | Reference voltage input pin for A/D converter.                                                                                                                           |  |

| 43                   | AVSS                                           | _       | Power supply pin for A/D converter. Use at same potential as VSS.                                                                                                        |  |

Table 1.6.1 Pin Description (Continued)

Fig. 1.6.1 I/O Circuit Type

# 1.7 Handling Devices

(1) Preventing Latch-up

A phenomenon called latch-up may occur on CMOS IC devices if voltage higher than Vcc or lower than Vss is applied to input and output pins, or if voltage higher than the rated value is applied between Vcc and Vss.

When latch-up occurs, supply current levels increase rapidly and might result in thermal damage to elements.

Sufficient care must be taken to avoid exceeding maximum rated values at any time during operation.

(2) Handling Unused Input Pins

Unused input pins can cause devices to malfunction if left open, and should therefore be connected to a pull-up or pull-down resistor.

(3) Fluctuations in Power Supply Voltage

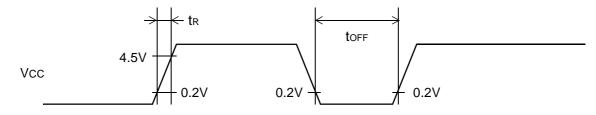

The operating range of Vcc power supply voltage is warranted according to specifications, however even within this range, sudden fluctuations in supply voltage may cause malfunctions, and therefore the supply voltage to the IC should be as stable as possible. As an indicator of stability, it is recommended that at commercial frequencies (50-60 Hz) the Vcc ripple effect in (P-P value) be within 10% of the typical VCC value, and that instantaneous changes at power turn on or off be limited so that the transient fluctuation rate be no more than 0.1 V/ms.

(4) Precautions for Use of External Clock

Even when an external clock is used, an oscillation stabilization time is required for a power-on reset or wake-up from stop mode.

(5) Power Supply and Analog Signal Input for A/C Converter

When turning on or off the power supply to the analog system, care must be taken that the analog power supply (AVCC, AVR) and analog input signal do not exceed the level of the digital power supply (VCC).

(6) Handling Power Supply Pins on Microcontrollers with A/D Converter

When the A/D converter is not in use, connect to be AVCC=VCC, and AVSS=AVR=VSS.

### **1.8 Development Environment**

The MB89863 is a mask ROM product.

In software development, the use of evaluation tools or OTPROM version chips requires the use of the MB89P/W857 chip and a pin array conversion adapter (Sun Hayato model: 64SD-48QF-8L) dedicated for the MB89863.

For programming to the MB89P/W857, refer to the 'F2MC-8L Family MB89860 Series Data Sheet.'

# Chapter 2: HARDWARE CONFIGURATION

# 2.1 CPU

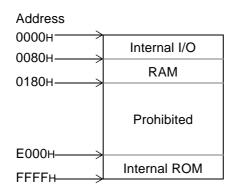

#### 2.1.1 Memory Space

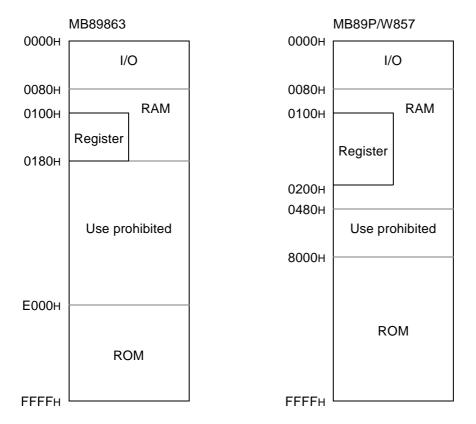

The MB89863 series of microcontrollers has 64 Kbytes of memory space. All I/O, data, and program areas are located in this space. The I/O area is located near the lowest address and the data area is immediately above it. The data area may be divided into register, stack and direct addressing areas according to the individual applications. The program area is located at the opposite end of the memory space, near the highest address, and the interrupt reset vectors and vector call instruction tables are at the top of the highest address. Figure 2.1.1 shows the structure of the memory space for the MB89863.

Fig. 2.1.1 Memory Space for MB89836 and MB89P/W857

O I/O Area

This area contains control registers for various peripheral devices, as well as data registers. The I/O area memory map is presented in Appendix 1.

O RAM Area

This area contains static RAM. The area from addresses 0100H to 0180H can also be used as the general-purpose register area.

O ROM Area

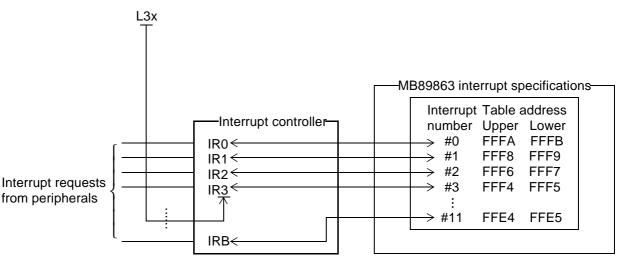

This area contains the internal ROM. The area from addresses FFC0H to FFFFH is also used for tables of interrupt and reset vectors and vector call instructions. Figure 2.1.2 shows the relation between each interrupt number or reset and the table addresses to be referenced for the MB89863 series microcontrollers.

|          | Table a    | address    |               | Table a    | address    |

|----------|------------|------------|---------------|------------|------------|

|          | Upper data | Lower data |               | Upper data | Lower data |

| CALLV #0 | FFC0H      | FFC1H      | Interrupt #11 | FFE4H      | FFE5H      |

| CALLV #1 | FFC2H      | FFC3н      | Interrupt #10 | FFE6H      | FFE7H      |

| CALLV #2 | FFC4H      | FFC5н      | Interrupt #9  | FFE8H      | FFE9н      |

| CALLV #3 | FFC6H      | FFC7н      | Interrupt #8  | FFEAH      | FFEBH      |

| CALLV #4 | FFC8H      | FFC9н      | Interrupt #7  | FFECH      | FFEDH      |

| CALLV #5 | FFCAH      | FFCBн      | Interrupt #6  | FFEEH      | FFEFH      |

| CALLV #6 | FFCCH      | FFCDH      | Interrupt #5  | FFF0H      | FFF1H      |

| CALLV #7 | FFCEH      | FFCFH      | Interrupt #4  | FFF2H      | FFF3н      |

|          | ·          |            | Interrupt #3  | FFF4H      | FFF5н      |

|          |            |            | Interrupt #2  | FFF6H      | FFF7н      |

|          |            |            | Interrupt #1  | FFF8H      | FFF9h      |

|          |            |            | Interrupt #0  | FFFAH      | FFFBH      |

|          |            |            | Reset mode    |            | FFFDH      |

|          |            |            |               |            |            |

**Note1:** Address FFFCH is reserved.

Note2: The MB89863 has no interrupt source corresponding to interrupt numbers 6, 8, and 10.

Reset vector

FFFEH

FFFFH

Fig. 2.1.2 Reset and Interrupt Vector Tables

#### 2.1 CPU

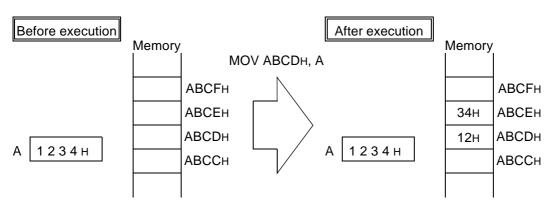

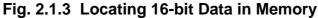

#### 2.1.2 Locating Memory Space in 16-bit Data

The MB89863 handles 16-bit data in memory by assigning the data written in the lower address to the high byte and the data written in the next address to the low byte as shown in Figure 2.1.3.

The same is true with an instruction operand designating 16-bit data, in which the values closest to the OP code are assigned to the high byte and the next adjacent values to the lower byte. The same treatment is used when the operand designates a memory address or 16-bit immediate data.

#### Fig. 2.1.4 Byte Order of 16-bit Data in Instructions

The same treatment is applied to data saved to stack following an interrupt.

### 2.1.3 Registers

The MB89863 registers are broadly divided into dedicated registers in the CPU and general-purpose registers in memory. The dedicated registers are as follows.

- Program counter (PC)......16-bit length, indicates locations where instructions are stored.

- Accumulator (A) ......16-bit length, used as a temporary storage register for calculations; lower byte used for 8-bit data processing instructions.

- Temporary accumulator (T) ... 16-bit length, used for calculation in combination with the accumulator; lower byte used for 8-bit data processing instructions.

- Stack pointer (SP).....16-bit length, indicates a stack area.

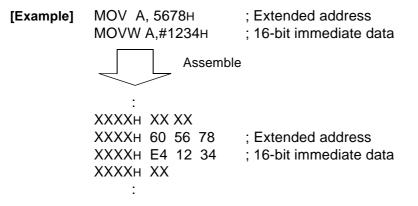

- Program status (PS)......16-bit register used to store register pointers and condition codes.

- Index register (IX)......16-bit register used for index modification.

- Extra pointer (EP).....16-bit pointer used for memory addressing.

| ←16-bit ───> |                         | Initial value                    |

|--------------|-------------------------|----------------------------------|

| PC           | : Program counter       | FFFDH                            |

| A            | : Accumulator           | Indeterminate                    |

| Т            | : Temporary accumulator | Indeterminate                    |

| IX           | : Index register        | Indeterminate                    |

| EP           | : Extra pointer         | Indeterminate                    |

| SP           | : Stack pointer         | Indeterminate                    |

| PS           | : Program status        | l flag=0, IL0,1=11               |

|              |                         | Indeterminate at all other times |

The 16 bits of the PS register can also be divided in to the upper 8 bits used for a register stack pointer and the lower 8 bits for a condition code register (CCR) (Figure 2.1.5).

Fig. 2.1.5 Structure of Program Status Register

2.1 CPU

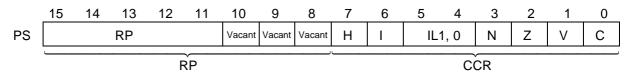

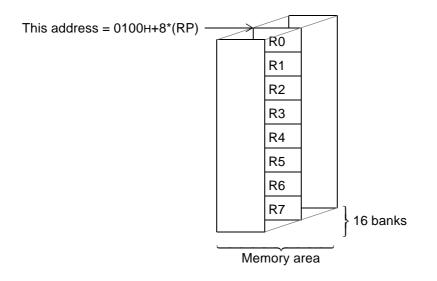

The RP register shows the address of the current register bank, so that the RP value and the actual address are related according to the conversion rule shown in Figure 2.1.6.

|                   |              |              |              |              |              |              |              | -            |              |              | RP           |              |              | op cod       | le lowe      | ər bits      |

|-------------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|

|                   | '0'          | '0'          | '0'          | '0'          | '0'          | '0'          | '0'          | '1'          | R4           | R3           | R2           | R1           | R0           | b2           | b1           | b0           |

|                   | $\downarrow$ |

| Generated address | A15          | A14          | A13          | A12          | A11          | A10          | A9           | A8           | A7           | A6           | A5           | A4           | A3           | A2           | A1           | A0           |

#### Fig. 2.1.6 Rule for Conversion of Actual Addresses the General-purpose Register Area

The CCR register consists of bits showing the results of arithmetic operations or the contents of transfer data, a bit controlling CPU operation during an interrupt.

- O H flag...... Set when calculations cause a carry or borrow from bit 3 to bit 4 to occur; otherwise, cleared. This flag is used for decimal-correction instructions.

- O I flag ...... Set to '1' to enable interrupts, and '0' to disable. Reset value is 0.

- O IL1, IL0 ...... Indicate the level of the currently enabled interrupt. The CPU executes interrupt processing only for requests for interrupts with a level lower than the value of this bit.

| IL1 | IL0 | Interrupt level | Priority level     |

|-----|-----|-----------------|--------------------|

| 0   | 0   | 1               | High               |

| 0   | 1   |                 |                    |

| 1   | 0   | 2               |                    |

| 1   | 1   | 3               | Low = no interrupt |

- O N flag ......Set when calculations cause the most significant bit (MSB) to be 1, and cleared when MSB is 0.

- O Z flag ...... Set when calculations result in all bits set to 0, and otherwise cleared.

- O V flag ......Set when calculations result in a 2's complement overflow, and reset when no overflow occurs.

- O C flag ...... Set when calculations result in a carry or borrow out of bit 7, and otherwise cleared. The value of the C flag is shifted out following a shift instruction.

The following general-purpose registers are provided.

• General-purpose registers ......8-bit length, used to store data.

The 8-bit general-purpose registers are located in the register banks in memory. One bank contains eight registers, and up to 16 banks are available for the MB89863 series of microcontrollers. The bank currently in use is indicated by the register bank pointer (RP).

2.1 CPU

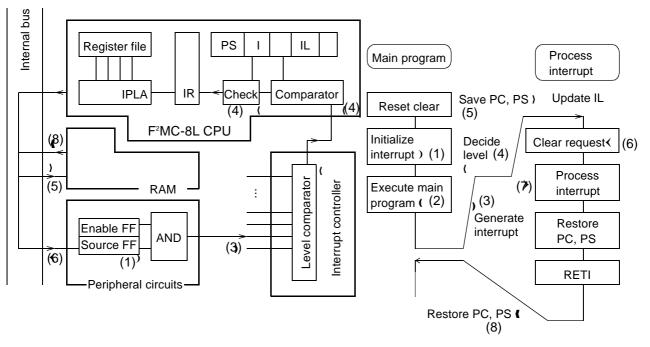

#### 2.1.4 Operating Modes

The MB89863 series of microcontrollers operates in single-chip mode.

The memory map is shown below.

#### Fig. 2.1.8 Memory Map

The mode in which the device operates is ultimately determined by the setting of the mode pins and the contents of the mode data read during the last reset sequence. The relationship between mode pin settings and operating status is shown below. The MB89863 microcontroller accepts only the setting '00.'

| MOD1      | MOD0 | Description                                                                        |

|-----------|------|------------------------------------------------------------------------------------|

| 0         | 0    | Reset vectors are read from internal ROM. External access functions not available. |

| All other |      | Reserved; do not set.                                                              |

The following functions are determined by mode data setting values.

®

®

®

®

T2

T1

T0

® Reserved; set to '0.'

— Mode bits

| T2 | T1        | Т0                    | Operation                 |

|----|-----------|-----------------------|---------------------------|

| 0  | 0         | 0                     | Selects single-chip mode. |

|    | All other | Reserved; do not set. |                           |

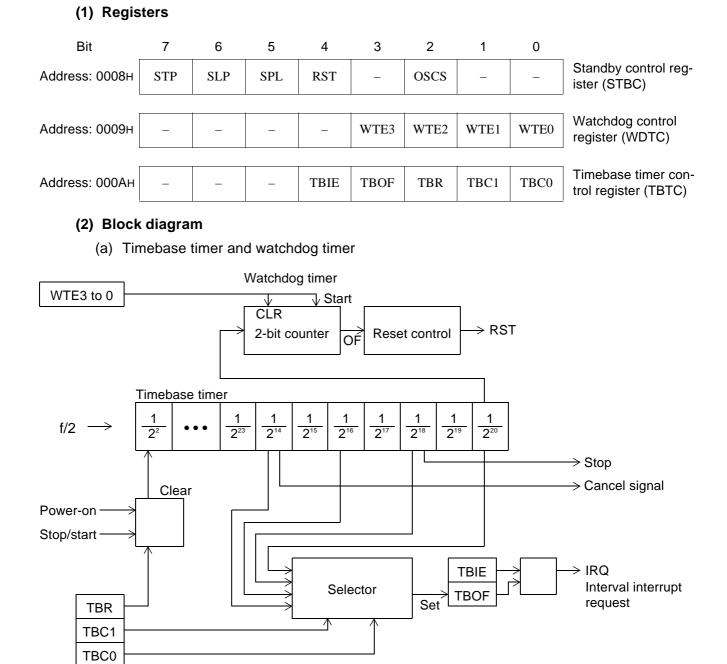

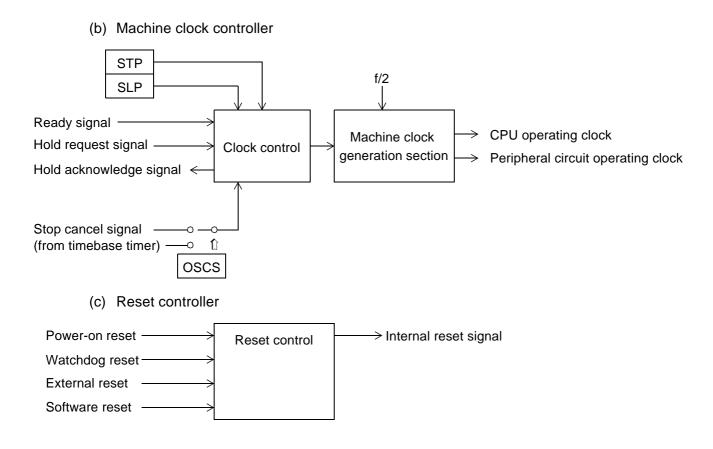

### 2.1.5 Clock Controller

This block controls standby operations, and generation of software resets, in addition to the timebase timer and watchdog timer functions.

#### 2.1 CPU

#### (3) Register Descriptions

#### (3.1) STBC (Standby Control) Register

|   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Initial value |

|---|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| Ī | STP   | SLP   | SPL   | RST   | -     | OSCS  | -     | -     | 0001Х0ХХв     |

|   | (W)   | (W)   | (R/W) | (W)   |       | (R/W) |       |       | _             |

The STBC register controls low-power consumption modes.

#### [Bit 7] STP: Stop bit

Bit 7 is used to specify switching to stop mode.

| 0 | No operation |

|---|--------------|

| 1 | Stop mode    |

The bit is cleared at reset or wake-up from stop mode.

Writing '1s' simultaneously into STP and SLP bits enters the stop mode.

The read value of this bit is always '0.'

#### [Bit 6] SLP: Sleep bit

Bit 6 is used to specify switching to sleep mode.

| 0 | No operation |

|---|--------------|

| 1 | Sleep mode   |

This bit is cleared at reset or wake-up from sleep mode or stop mode.

Writing '1s' simultaneously into STP and SLP bits enters the stop mode.

The read value of this bit is always '0.'

#### [Bit 5] SPL: Pin state select bit

Bit 5 is used to set the state of external pins when the MB89863 is in stop mode.

| 0 | Holds the state and level immediately before stop mode. |

|---|---------------------------------------------------------|

| 1 | High impedance state                                    |

This bit is cleared at reset.

2.1 CPU

[Bit 4]: Software reset bit

Bit 4 is used to specify a software reset.

| 0 | Generates reset signal of 4 instruction cycles |

|---|------------------------------------------------|

| 1 | No operation                                   |

The read value of this bit is always '1.'

[Bit 2] OSCS: Oscillation stabilization time select bit

This bit is used to select the length of the oscillation stabilization period.

| OSCS | Counts for minimum execution time | Time at 4.2 MHz oscillation | Time at 8 MHz<br>oscillation |

|------|-----------------------------------|-----------------------------|------------------------------|

| 0    | approx. 2 <sup>16</sup> counts    | approx. 62.3 ms             | approx. 32.7 ms              |

| 1    | approx. 2 <sup>12</sup> counts    | approx. 3.90 ms             | approx. 2.05 ms              |

This bit is initialized at zero at a power-on reset, but is not initialized by any other resets.

#### (3.2) WDTC (Watchdog Timer Control) Register

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Initial value |

|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| -     | -     | -     | -     | WTE3  | WTE2  | WTE1  | WTE0  | XXXXXXXXB     |

|       |       |       |       | (W)   | (W)   | (W)   | (W)   |               |

This register controls the watchdog timer function.

[Bits 3 to 0] WTE3 to WTE0: Watchdog timer control bits

These bits control the watchdog timer functions.

O First write after reset

| 0101      | Starts watchdog timer. |

|-----------|------------------------|

| All other | No operation           |

#### **O** Second write after reset

| 0101      | Clears watchdog timer counter. |

|-----------|--------------------------------|

| All other | No operation                   |

The watchdog timer can only be stopped by a reset.

The read value of bits 0-3 is '1111.'

#### (3.3) TBTC (Timebase Timer Control) Register

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Initial value |

|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| -     | -     | -     | TBIE  | TBOF  | TBR   | TBC1  | TBC0  | ХХХ00000в     |

|       |       |       | (R/W) | (R/W) | (W)   | (R/W) | (R/W) |               |

The TBTC register controls the timebase timer and interval timer.

[Bit 4] TBIE: interval interrupt enable bit

Bit 4 is used to enable an interrupt from the interval timer.

| 0 | Enables interval interrupt.  |

|---|------------------------------|

| 1 | Disables interval interrupt. |

This bit is cleared at reset.

#### [Bit 3] TBOF: Interval timer overflow bit

This bit is used to clear the interval timer overflow flag when writing.

| 0 | Clear internal timer overflow flag. |

|---|-------------------------------------|

| 1 | No operation                        |

O This bit indicates that an internal timer overflow occurred during reading.

| 0 | No interval timer overflow occurred |

|---|-------------------------------------|

| 1 | Interval timer overflow occurred    |

The read value is '1' for all read-modify-write instructions.

An interrupt request is generated if this TBOF bit is set to '1' while the TBIE bit is '1.'

This bit is cleared at reset.

#### [Bit 2] TBR: Timebase timer initialize bit

This bit clears the timebase timer counter.

| 0 | Clears timebase timer counter. |

|---|--------------------------------|

| 1 | No operation                   |

The read value of this bit is always '1.'

[Bits 1,0] TBC1,TBC0: Interval time setting bits

These bits are used to set the cycle of the interval timer.

| TBC1 | TBC0 | Interval time at 4.2 MHz oscillation | Interval time at 8 MHz oscillation |

|------|------|--------------------------------------|------------------------------------|

| 0    | 0    | 7.8 ms                               | 4.1 ms                             |

| 0    | 1    | 31.2 ms                              | 16.4 ms                            |

| 1    | 0    | 124.6 ms                             | 65.5 ms                            |

| 1    | 1    | 498.1 ms                             | 262.1 ms                           |

These bits are cleared at reset.

#### (4) Description of operation

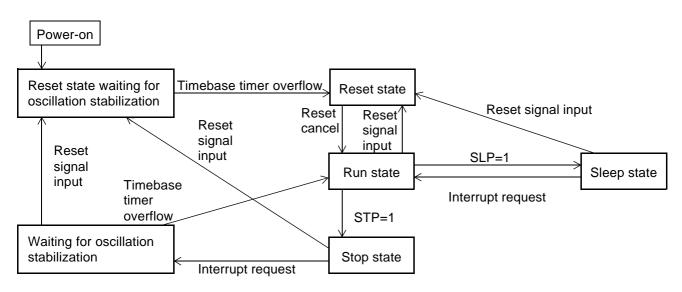

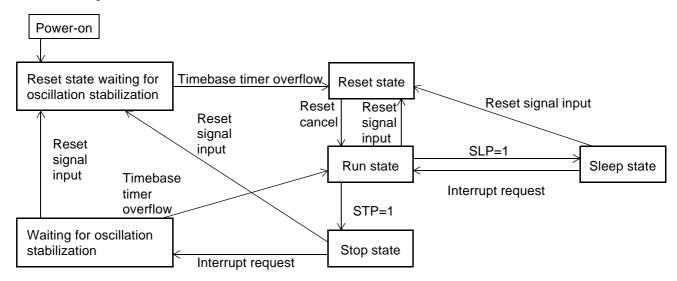

#### (4.1) Low-power consumption

There are two low-power consumption modes: sleep and stop. Table 2.1.1 lists the status of MB89863 components in each mode.

| Operating<br>mode | Switching condition | Oscillation | Clock    | CPU   | Peripheral circuits | Pins     | Exit<br>method      |

|-------------------|---------------------|-------------|----------|-------|---------------------|----------|---------------------|

| Sleep             | SLP=1               | Operates    | Operates | Stops | Operates            | Operates | Reset/<br>interrupt |

| Stop (SPL=0)      | STP=1               | Stops       | Stops    | Stops | Stops               | Holds    | Reset/<br>interrupt |

| Stop (SPL=1)      | STP=1               | Stops       | Stops    | Stops | Stops               | Hi-Z     | Reset/<br>interrupt |

Table 2.1.1 Operating State in Low-Power Consumption Modes

- In sleep mode, only the CPU operating clock stops; other operations are continued.

- In stop mode, the oscillation stops, and data can be retained with the lowest power consumption.

- (a) Sleep mode

- O Switching into sleep mode

- Write '1' to the SLP bit (bit 6) of the STBC register to enter sleep mode.

- Sleep mode shuts down the clock signal on which the CPU operates. Only the CPU stops, and the peripheral circuits of the MB89863 continue to operate.

- If an interrupt has been requested when '1' is written to the SLP bit (bit 6), the CPU will continue to execute instructions without switching into sleep mode.

- The contents of registers and RAM are retained while the chip is in sleep mode.

- O Wake-up from sleep mode

- The MB89863 exits sleep mode when a reset signal is input, or an interrupt is requested.

- A reset signal input while in sleep mode causes the MB89863 to switch to reset state, and to exit sleep mode.

- Any interrupt request lower than level 11 will cause the MB89863 to exit sleep mode.

- If the I flag and IL bits are set to accept interrupt requests after sleep mode, the CPU will start the interrupt processing. If they are set to ignore interrupt requests, the CPU will begin by processing the next instruction awaiting execution before transition to sleep mode.

22

- (b) Stop mode

- **O** Switching into stop mode

- Write '1' to the STP bit (bit 7) of the STBC register to enter sleep mode.

- Stop mode shuts down the oscillation and all MB89863 chip functions. In this mode, data can be retained at the lowest power consumption.

- While the chip is in stop mode, the SPL bit (bit 5) of the STBC register can be used to control whether the I/O pins and output pins retain their immediately previous settings or are set to high impedance.

- If an interrupt has been requested when '1' is written to the STP bit (bit 7), the CPU will continue to execute instructions without switching into stop mode.

- The contents of registers and RAM are retained while the chip is in stop mode.

- O Wake-up from stop mode

- The MB89863 exits stop mode when a reset signal is input, or an interrupt is requested.

- A reset signal input while in sleep mode causes the MB89863 to switch to reset state, and to exit stop mode.

- Any interrupt request lower than level 11 will cause the MB89863 to exit stop mode.

- After wake-up from stop mode if the I flag and IL bits are set to enable interrupt processing after sleep mode, the CPU will begin by processing the interrupt as soon as the oscillation stabilization time has passed. If the I flag and IL bits are set to ignore interrupt requests, the CPU will begin by processing the next instruction awaiting execution before transition to stop mode.

- The OSCS bit in the STBC register can be used to select either of two stabilization time settings, as shown in Table 2.1.2.

- When a reset signal is used to exit stop mode, the MB89863 enters oscillation stabilization wait status, and the oscillator stabilization wait period must elapse before the reset is executed.

| Counts for minimum execution time | Time at 4.2 MHz oscillation | Time at 8 MHz<br>oscillation | Remarks                 |

|-----------------------------------|-----------------------------|------------------------------|-------------------------|

| approx. 2 <sup>16</sup> counts    | approx. 62.3 ms             | approx. 32.7 ms              | For crystal oscillators |

| approx. 2 <sup>12</sup> counts    | approx. 3.90 ms             | approx. 2.05 ms              | For ceramic oscillators |

#### Table 2.1.2 Selection of Oscillator Stabilization Time

#### Fig. 2.1.9 State Transition in Lower-Power Consumption

#### (4.2) Watchdog timer

The watchdog timer function is used to detect program runaway (loop) conditions.

- O Starting the watchdog timer

- The first writing of '0101' to the WTE3 to WTE0 bits (bits 3 to 0) immediately after a reset will activate the watchdog timer.

- O Watchdog timer operations

- Once the timer has started, any second or later writing of '0101' to the WTE3 to WTE0 bits (bits 3 to 0) will clear the watchdog timer counter.

- If the watchdog timer counter is not cleared within the time specified in Table 2.1.3, a watchdog reset signal is generated and the chip is reset.

- Any transition to standby or hold status will clear the watchdog timer counter.

- Because the clock signal source for the watchdog timer is supplied from the timebase timer, the watchdog timer counter is simultaneously cleared whenever the timebase timer is cleared.

- Once started, the watchdog timer cannot be stopped until a reset signal is generated.

#### Table 2.1.3 Watchdog Timer Interval Time

| Minimum time     | Maximum time     | Remarks                |

|------------------|------------------|------------------------|

| approx. 498.1 ms | approx. 996.2 ms | Oscillation at 4.2 MHz |

| approx. 262.1 ms | approx. 524.3 ms | Oscillation at 8 MHz   |

24

#### (4.3) Timebase timer

The timebase timer consists of 20-stage counters which use a 1/2 oscillation cycle as a clock source signal (see Figure 1). The timebase timer provides the signal for the watchdog timer, the oscillation stabilization timer, and the interval timer used to generate interrupt request at fixed intervals.

- **O** Timebase timer control

- The timebase timer counter is cleared by writing '0' to the TBR bit (bit 2) of the TBTC register, or when the MB89863 enters stop mode.

- In all other cases the counter continues to count up for as long as the clock pulse continues.

- O Interval timer functions

- The interval timer operates by setting the TBOF bit (bit 3) in the TBTC register at regular intervals set by the TBC1,0 bits (bit 1, 0).

- The interval time is initiated by a flag set based on the time the timebase timer counter is last cleared.

- The TBOF bit (bit 3) is also cleared when the MB89863 goes into stop mode, because the timebase timer is used as the counter for the oscillation stabilization time on exiting.

- An interval interrupt is generated if the TBIE bit (bit 4) is set to '1' while TBOF bit (bit 3) is set.

- The interrupt source is cleared by writing '0' to the TBOF bit (bit 3).

#### (4.4) Resets

The MB89863 provides four types of resets, as shown in Table 2.1.4.

| Reset              | Description                                   |

|--------------------|-----------------------------------------------|

| External pin reset | Sets external reset pins to 'L' level         |

| Software reset     | Write '0' to RST bit (bit 4) of STBC register |

| Watchdog reset     | Triggered by watchdog timer overflow          |

| Power-on reset     | Triggered by power-on                         |

Table 2.1.4 MB89863 Reset Sources

A power-on reset or any reset in stop mode require an oscillation startup, which must be followed by an oscillation stabilization time because the oscillator has been deactivated. This stabilization time is controlled by the timebase timer. In such cases, therefore the MB89863 will not start operation immediately even if the reset is canceled.

#### 2.1 CPU

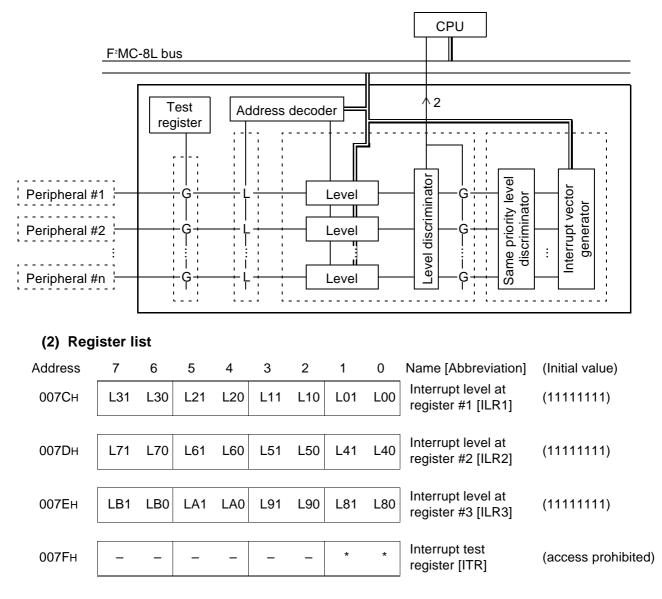

#### 2.1.6 Interrupt Controller

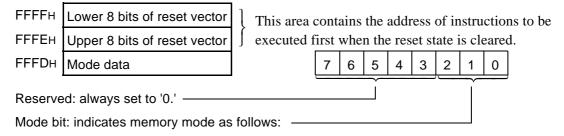

The interrupt controller for the F<sup>2</sup>MC-8L CPU core is located between the CPU and the peripheral circuits. This controller receives interrupt requests from the peripherals, assigns priorities to them, and then transfers the requests to the CPU. During that process, the controller also determines the priority of interrupts of the same level.

#### (1) Block diagram

#### (3) Detailed description of register

#### (3.1) Interrupt level setting registers (ILRx: Interrupt Level Setting Register x)

|      | 7   |     |     |     |     |     |     | 0   |   |             |            |

|------|-----|-----|-----|-----|-----|-----|-----|-----|---|-------------|------------|

| ILR1 | L31 | L30 | L21 | L20 | L11 | L10 | L01 | L00 | W | Reset value | (11111111) |

|      |     |     |     |     |     |     |     |     |   |             |            |

| ILR2 | L71 | L70 | L61 | L60 | L51 | L50 | L41 | L40 | W | Reset value | (11111111) |

|      |     |     |     |     |     |     |     |     |   |             |            |

| ILR3 | LB1 | LB0 | LA1 | LA0 | L91 | L90 | L81 | L80 | W | Reset value | (11111111) |

The ILRx registers determine the interrupt levels assigned to each of the peripheral resources. The figure at the center of each bit corresponds to the interrupt number.

#### [Example]

Interrupt requests from peripherals are passed to the interrupt controller, which assigns an interrupt level based on the 2-bit setting in the corresponding IRLx register, and then transfers the request to the CPU. The relation between the 2-bit settings in the IRLx register and the interrupt request level is as follows:

| Lx1 | Lx0 | Interrupt request level |

|-----|-----|-------------------------|

| 0   | Х   | 1                       |

| 1   | 0   | 2                       |

| 1   | 1   | 3 (no interrupt)        |

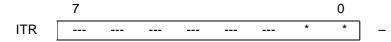

#### (3.2) Interrupt test register (ITR)

ITR is a register for testing; it is unaccessible.

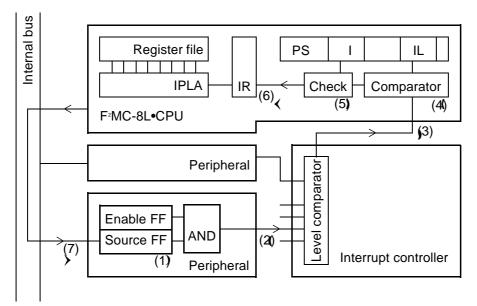

#### (4) Description of operation

#### (4.1) Interrupt functions

The MB89863 series of microcontrollers has 9 inputs for interrupt requests from peripherals. Each interrupt level is set by a 2-bit interrupt level register corresponding to an input signal. Interrupts requested by a peripheral are received by the interrupt controller and transferred to the CPU according to the level of the corresponding register. The overall procedure of interrupt processing by the MB89863 device is as follows.

- (1) An interrupt source is generated inside a resource.

- (2) If the interrupt enable bit for that peripheral is set to enable the interrupt, an interrupt request is output from that peripheral to the interrupt controller.

- (3) After receiving the interrupt request, the interrupt controller determines the relative priority of any simultaneously requested interrupts, and then transfers the assigned interrupt levels for the applicable interrupts to the CPU.

- (4) The CPU compares the level of the interrupt request to the IL bit in the program status register.

- (5) If the comparison shows that the incoming interrupt level is higher than that of the current interrupt processing level, the value of the I flag in the program status register is checked.

- (6) If the check in step (5) shows that the I flag is enabled for an interrupt, the value of the IL bit is set to the required level. As soon as execution of the current instruction is ended, the CPU processes the interrupt and transfers control to the appropriate interrupt processing routine.

- (7) After the interrupt source in step (1) is cleared by software in the user's interrupt processing routine, interrupt processing ends.

Figure 2.1.10 shows an overview of interrupt processing on the MB89863.

Fig. 2.1.10 Outline of MB89863 Interrupt Processing

# 2.2 Peripheral Functions

### 2.2.1 I/O Ports

#### (1) Overview

• The MB89863 series of microcontrollers has 6 parallel ports (38 pins).

Ports 0 and 4 are 8-bit I/O ports, port 5 is an 8-bit output port, port 2 is a 7-bit output port, port 3 is a 5-bit I/O port, and port 6 is a 2-bit input port.

• Ports 3, 4 and 5 also function as peripherals. Ports 0 and 2 are dedicated ports.

| Pin no.       | Input<br>type     | Output type       | Function        | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------------|-------------------|-------------------|-----------------|-------|-------|-------|-------|-------|-------|-------|-------|

| P00 to        | CMOS              | CMOS              | Parallel port 0 | P07   | P06   | P05   | P04   | P03   | P02   | P01   | P00   |

| P07           | CMOS              | push-pull         | Peripheral      | -     | -     | -     | -     | -     | -     | v     | -     |

| P21 to        |                   | CMOS              | Parallel port 2 | P27   | P26   | P25   | P24   | P23   | P22   | P21   | -     |

| P27           | —                 | push-pull         | Peripheral      | -     | _     | -     | -     | -     | -     | -     | _     |

| P30 to<br>P32 | CMOS              | CMOS<br>push-pull | Parallel port 3 | P37   | P36   | Ι     | Ι     | Ι     | P32   | P31   | P30   |

| P36 to<br>P37 | (Hyster-<br>esis) |                   | Peripheral      | PTO2  | PTO1  | -     | -     | -     | SI    | SO    | SCKX  |

| P40 to        | CMOS              | CMOS              | Parallel port 4 | P47   | P46   | P45   | P44   | P43   | P42   | P41   | P40   |

| P47           | (Hyster-          | push-pull         | Peripheral      | TRGI  | Ζ     | Y     | Х     | RTO3  | RTO2  | RTO1  | RTO0  |

| P50 to        | Analog            | N-ch open-        | Parallel port 5 | P57   | P56   | P55   | P54   | P53   | P52   | P51   | P50   |

| P57           | compa-            | drain             | Peripheral      | AN7   | AN6   | AN5   | AN4   | AN3   | AN2   | AN1   | AN0   |

| P60,          | CMOS              |                   | Parallel port 6 | -     | _     | -     | P64   | -     | -     | -     | P60   |

| P64           | (Hyster-<br>esis) | _                 | Peripheral      | _     | _     | -     | DTTI  | -     | _     | -     | INT0  |

Table 2.2.1 List of Ports and Functions

#### (2) Register list

#### Table 2.2.2 Port Registers

| Register                              | Read/Write | Address | Initial value |

|---------------------------------------|------------|---------|---------------|

| Port 0 data register (PDR0)           | R/W        | 0000н   | XXXXXXX       |

| Port 0 data direction register (DDR0) | W          | 0001н   | 0000000F      |

| Port 2 data register (PDR2)           | R/W        | 0004н   | 000000X1      |

| Port 3 data register (PDR3)           | R/W        | 000Сн   | XXXXXXXX      |

| Port 3 data direction register (DDR3) | W          | 000Dh   | 00XXX000      |

| Port 4 data register (PDR4)           | R/W        | 000Ен   | XXXXXXXX      |

| Port 4 data direction register (DDR4) | W          | 000Fh   | 00000001      |

| Port 5 data register (PDR5)           | R/W        | 0010н   | 11111111      |

| Port 6 data register (PDR6)           | R          | 0012н   | XXXXXXX       |

#### (3) Description of functions

P00 to P07: CMOS-type I/O ports

• Input/output switching

Each port bit has a DDR (data direction register) and a PDR (port data register), enabling input or output to be selected independently for each bit. A pin with DDR set to '1' is set for output, and a pin with DDR set to '0' is set for input.

• Output port operation (DDR=1)

When the DDR is set to '1,' the value written in the corresponding PDR is output to the pin with the DDR set to 1. Normally the PDR read value is the value of the pin, but not the contents of the output latch. However, in executing read-modify-write instructions, the contents of the output latch are read regardless of the DDR setting. Therefore bit processing instructions can be used even when input and output functions are both performed on the same pin. Data written to the PDR is held in the output latch irrespective of the DDR settings.

• Input port operation (DDR=0)

When used as an input port, the output state is high impedance. Therefore the PDR read value is the value of the pin.

• Status at reset

All pins are initialized to DDR=0 (with all bits for output at a high impedance) after a reset. The PDR is not initialized by reset, and retains the value it had before the DDR was reset for output.

• Status in stop mode

In stop mode, when the SPL bit of the standby control register is set to '1,' the output is set to high impedance regardless of the value of the DDR.

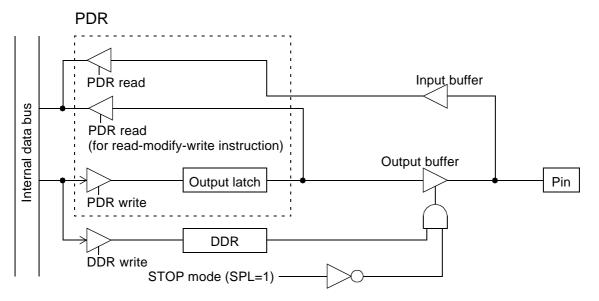

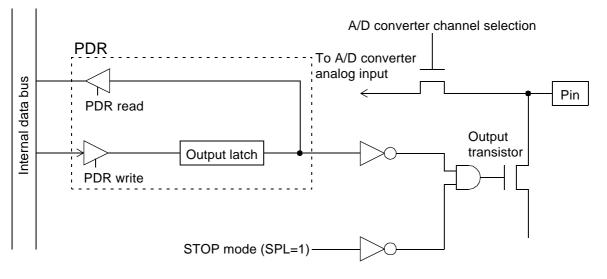

Fig. 2.2.1 Port 0

# P21 to P27: CMOS-type output ports

• Operation at output port

The value written to the PDR is output to the pin. Whenever the PDR is read the contents of the output latch are always read, so that bit processing instructions can be used even if the output level fluctuates due to load.

• Status at reset

At a reset, pins are in high impedance status, so that port output is enabled as soon as a vector fetch is performed, and the port begins operation as an output port. Because the PDR is initialized to '0' at a reset, the signal output to the pin is at 'L' level.

• Status in stop mode

In stop mode, when the SPL bit of the standby control register is set to '1,' the output is set to high impedance regardless of the value of the PDR.

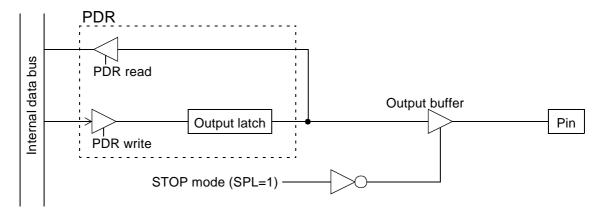

Fig. 2.2.2 Port 2

# P30 to P32, P36 to P37: CMOS-type I/O ports (used as resource input/output pins)

• Input/output switching

Each port bit has a DDR (data direction register) and a PDR (port data register), enabling input or output to be selected independently for each bit. A pin with DDR set to '1' is set for output, and a pin with DDR set to '0' is set for input. If the resource output enable bit is selected, the pin is set for output regardless of the DDR register value.

• Output port operation (DDR=1)

When the DDR is set to '1,' the value written in the corresponding PDR is output to the pin with the DDR set to '1.' Normally the PDR read value is the value of the pin, but not the contents of the output latch. However, in executing read-modify-write instructions, the contents of the output latch are read regardless of the DDR setting. Therefore bit processing instructions can be used even when input and output functions are both performed on the same pin. Data written to the PDR is held in the output latch regardless of the DDR setting.

• Input port operation (DDR=0)

When used as an input port, the output state is high impedance. Therefore reading the PDR value gives the value of the pin.

• Resource output operation

Pins are used for resource output by setting the resource output enable bit (see individual resource descriptions). For input/output switching, the resource output enable bit has priority, so that resource output is selected as long as this bit is set, even when the DDR value is set to '0.' Parallel port reading is effective even when a pin is enabled to allow resource output to be read.

• Resource input operation

Ports that double as resource inputs provide pin input values at all times regardless of the DDR or resource settings. If an external signal is used by a resource, the DDR should be set to input.

• Status at reset

The DDR and resource output enable bits are initialized to 0 at a reset and all bits are set to high impedance output. The PDR is indeterminate at reset, and retains the value it had before the DDR was reset to output.

• Status in stop mode

In stop mode, when the SPL bit of the standby control register is set to '1,' the output is set to high impedance regardless of the value of the DDR.

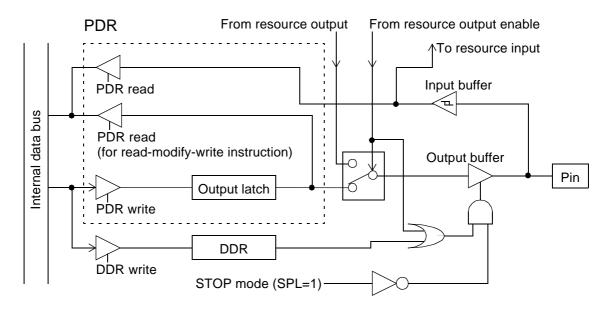

Fig. 2.2.3 Port 3

# P40 to P47: CMOS-type output ports (also used as timer unit output)

• Output specification

Each port bit has a DDR (data direction register) and a PDR (port data register), enabling input or output to be selected independently for each bit. A pin with DDR set to '1' is set for output, and a pin with DDR set to '0' is set for input. For port 4, the I/O setting is determined by the DDR regardless of the resource setting.

• Output port operation (DDR=1)

When the DDR is set to '1,' the value written in the corresponding PDR is output to the pin with DDR set to '1.' Normally the PDR read value is the value of the pin, but not the contents of the output latch. However, in executing read-modify-write instructions, the contents of the output latch are read regardless of the DDR setting. Therefore bit processing instructions can be used even when input and output functions are both performed on the same pin. Regardless of the DDR setting, data written to the PDR is held in the output latch.

• Input port operation (DDR=0)

When used as an input port, the output state is high impedance. Therefore the PDR read value is the value of the pin.

Resource output operation

When used as the output pin for the timer unit, control of the PDR is switched to the timer unit, even if the COER register of the timer unit is set. Therefore, output operation is designated by setting the DDR value of the corresponding pin for output.

When used for non-overlapping three-phase waveform output, the X, Y, and Z signal is output as an inverted U, V, W signal rather than through the PDR. Output operation is designated by setting the DDR value of the corresponding pin for output.

The RTO0 signal for starting the A/D converter uses the signal selected by the COER register, to be connected to the A/D converter. Therefore, the A/D converter can be started regardless of the setting of the DDR.

• Resource input operation

Ports that double as resource inputs provide pin input values at all times regardless of the DDR or resource settings. If an external signal is used by a resource, the DDR should be set to input.

• Status at reset

The DDR and resource output enable bits are initialized to 0 and all bits are set to output with high impedance after a reset. The PDR is indeterminate at reset, and retains the value it had before the DDR was reset to output.

• Status in stop mode

In stop mode, when the SPL bit of the standby control register is set to '1,' the output is set to high impedance regardless of the value of the DDR.

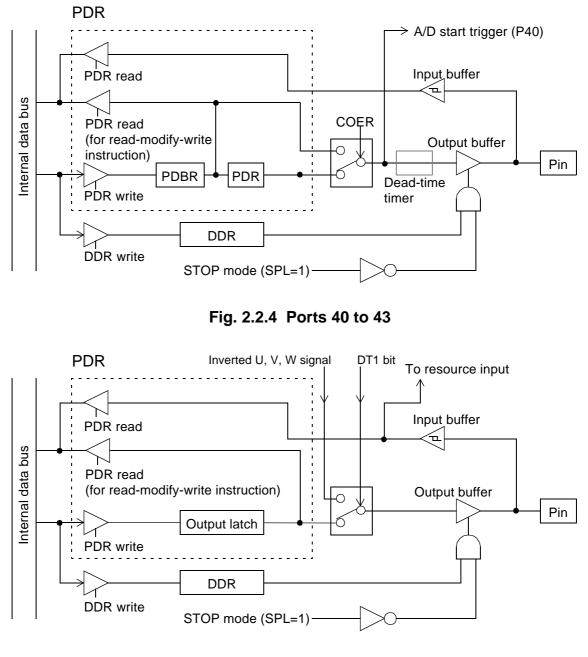

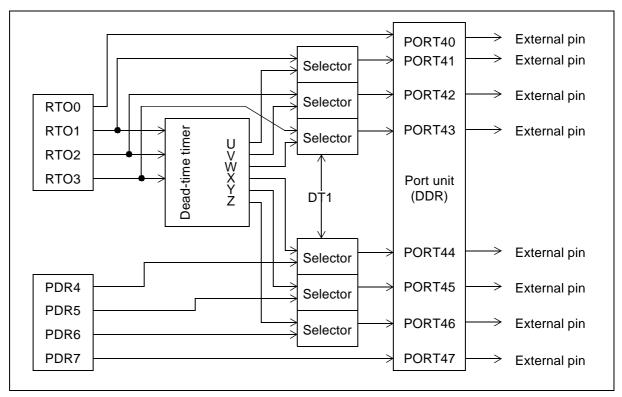

Fig. 2.2.5 Ports 44 to 47

P50 to P57: N-ch open drain-type output ports (also used as analog input)

• Output port operation

The value written to the PDR is output to the pin. At these ports, the read value of the PDR is the contents of the output latch, so that the state of the pin itself cannot be read.

• Analog input operation

When using these pins for analog input, The PDR is set to '1' to turn off the output transistor.

• Status at reset

At a reset, the PDR is initialized to '1' and then output transistors for all bits are turned off.

• Status in stop mode

In stop mode, when the SPL bit of the standby control register is set to '1,' the output is set to high impedance regardless of the value of the PDR.

Fig. 2.2.6 Port 5

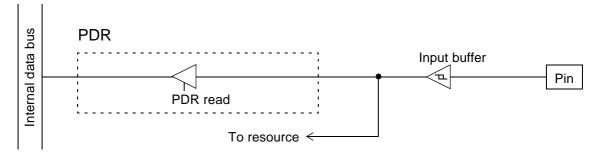

P60, P64: Input-only ports (also used as resource input)

• Input port operation

The PDR for these ports can only be read, so that the read value is always the value of the pin. When used as a resource input, the read value is the value of the pin.

Fig. 2.2.7 Port 6

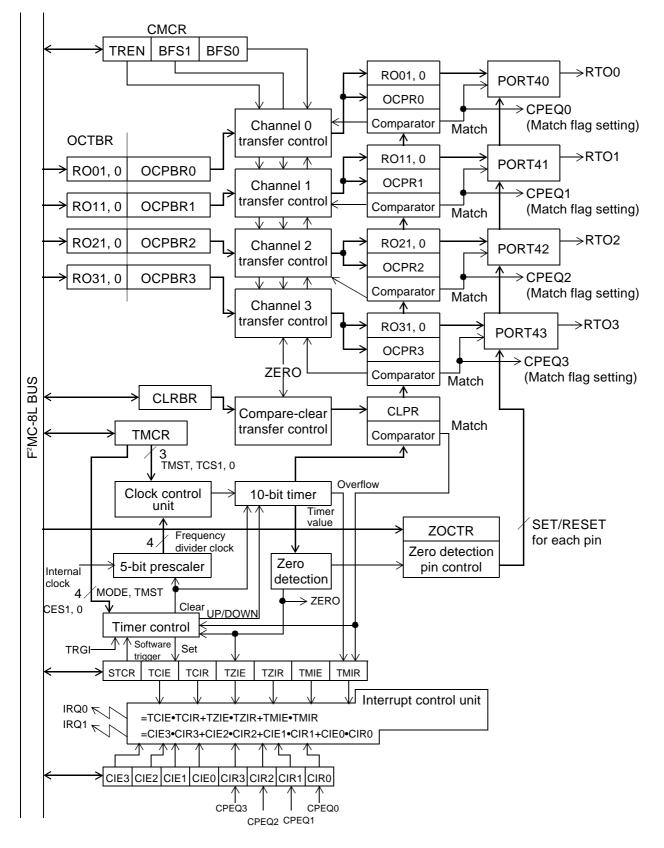

# 2.2.2 Timer Unit

Overview

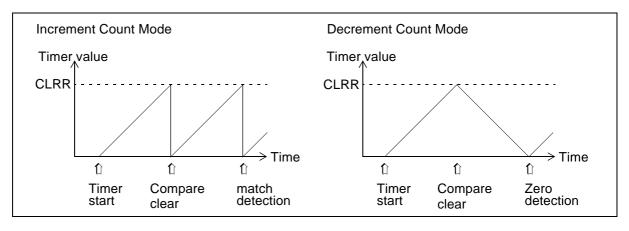

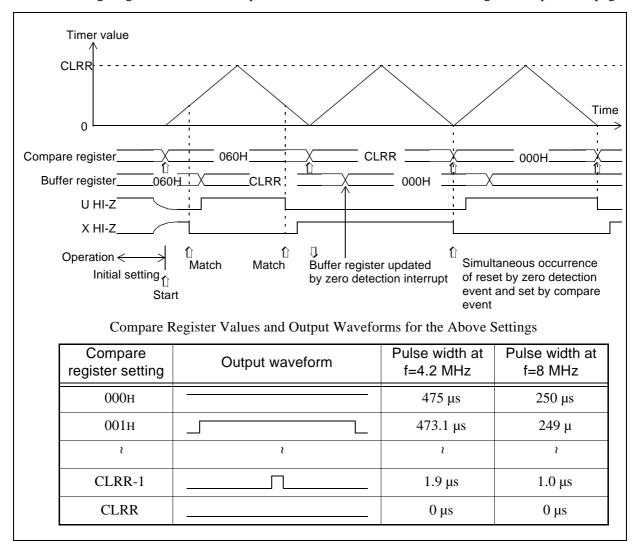

- This unit consists of one 10-bit up/down timer, one compare-clear register for cycle setting, four compare registers for output pin control, and one zero detection control register. It controls four realtime waveform output pins.

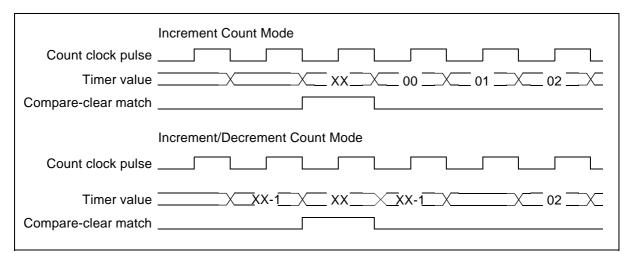

- There are two timer count modes: one for clearing the timer at detection of coincidence with the compare-clear register, and one for switching from increment to decrement counting. (In this mode, when the timer value goes to zero, decrementing is switched to incrementing.)

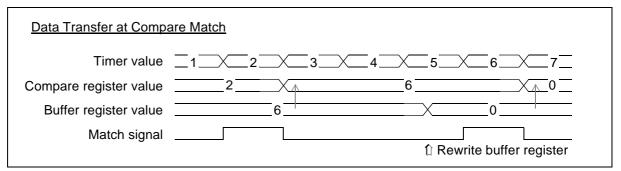

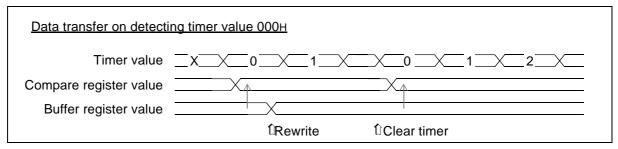

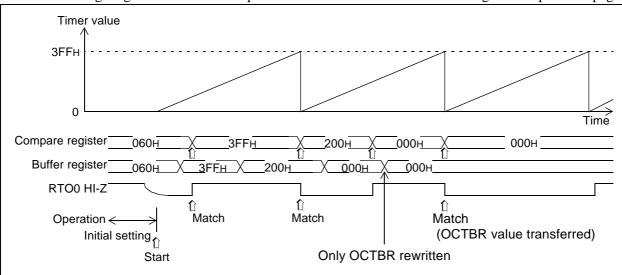

- The compare register and compare-clear register have buffer registers in which the next timer compare value is stored.

- The value in the buffer register is transferred to the compare register when the compare values match, or when timer value 000H is detected.

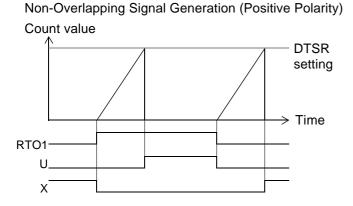

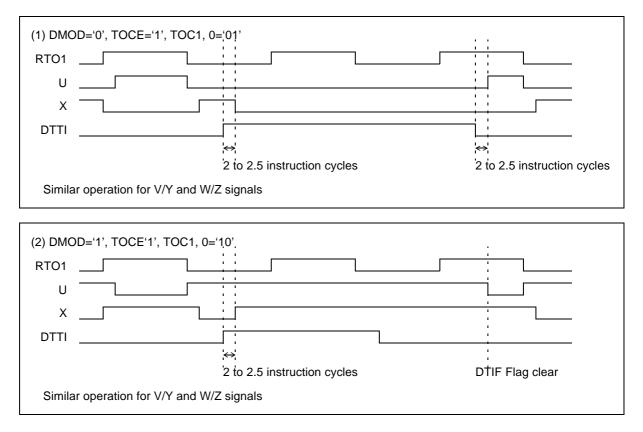

- Easy output of non-overlapping three-phase waveforms (U, V, W, X, Y, Z) for inverter motor control is available using the dead-time timers for each phase.

- External pins or software can be used for forced shutoff of the three-phase waveform output.

- The A/D converter can be started according to timing set up in the compare register.

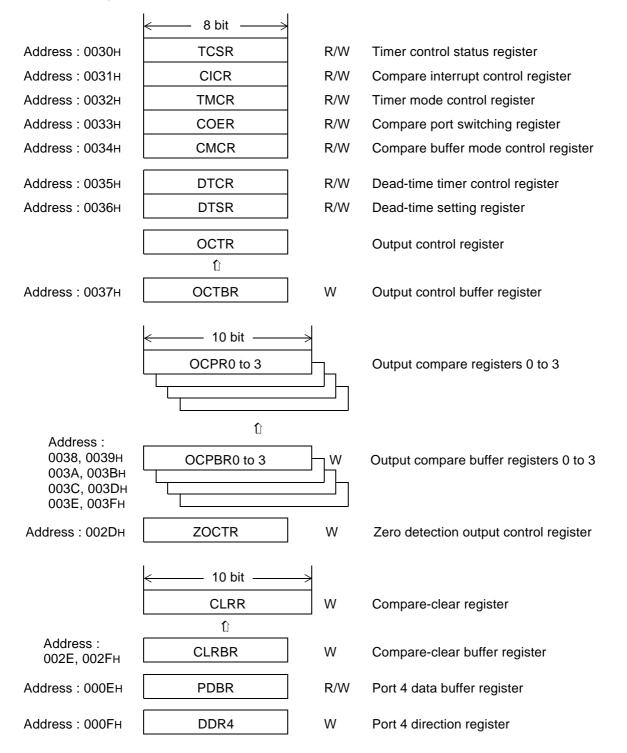

#### (1) Register list

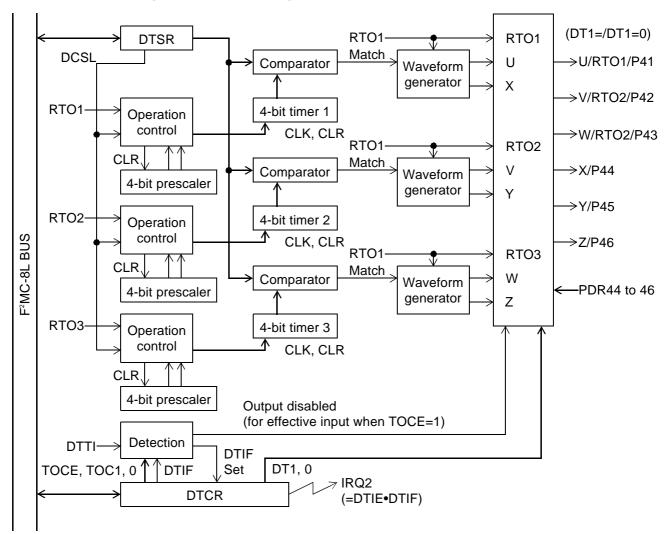

# (2) Block diagrams

# (2.1) Timer waveform generator block diagram

Chapter 2: HARDWARE CONFIGURATION

## (2.2) Dead-time generator block diagram

# (3) Description of registers

# (3.1) TCSR (Timer Control Status) Register

This register is used to clear the timer by software instructions, to enable transfers to the compare buffer register, and to control the clear interrupt, zero detection interrupt, and overflow interrupt functions from trigger input.

|                | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Initial value |

|----------------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| Address: 0030H | STCR  | -     | TCIE  | TCIR  | TZIE  | TZIR  | TMIE  | TMIR  | 1-000000в     |

|                | (W)   |       | (R/W) | (R/W) | (R/W) | (R/W) | (R/W) | (R/W) |               |

### [Bit 7] STCR: Software timer clear bit

Bit 7 is used to clear the timer count value. Write '0' to this bit to clear the timer and the prescaler.

Writing '1' to this bit is ignored and no operation is performed.

The read value of this bit is always '1.'

| 0 | Clears timer and prescaler. |

|---|-----------------------------|

| 1 | No operation                |

### [Bit 5] TCIE: Timer clear interrupt enable bit

Bit 5 is used to enable an interrupt request when the timer is cleared by external trigger input (TRGI).

| 0 | Disables timer clear interrupt by external trigger input |

|---|----------------------------------------------------------|

| 1 | Enables timer clear interrupt by external trigger input  |

# [Bit 4] TCIR: Timer clear interrupt request flag

This bit is an interrupt request flag used to clear the timer by external trigger input (TRGI). Set this bit to '1' to clear the timer from external trigger input.

Write '0' to clear this bit.

Writing '1' to this bit is ignored and the value of this bit is unchanged.

For read-modify-write instructions, the read value of this bit is always '1.'

| 0 | No request for timer clear interrupt from external trigger input |

|---|------------------------------------------------------------------|

| 1 | Request for timer clear interrupt from external trigger input    |

42

[Bit 3] TZIE: Zero detection interrupt enable bit

This bit is used to enable zero detection interrupt requests, which originate when a timer value of zero is detected.

| 0 | Disables zero detection interrupt request |

|---|-------------------------------------------|

| 1 | Enables zero detection interrupt request  |

[Bit 2] TZIR: Zero detection interrupt request flag

This bit is an interrupt request flag for the timer zero detection interrupt. It is set to '1' when a timer value of zero is detected.

Write '0' to clear this bit.

Writing '1' to this bit is ignored and the value of this bit is unchanged.

For read-modify-write instructions, the read value of this bit is always '1.'

| 0 | No request for zero detection interrupt |

|---|-----------------------------------------|

| 1 | Request for zero detection interrupt    |

[Bit 1] TMIE: Timer interrupt request enable bit

This bit is used to enable timer overflow interrupts/compare-clear match detection interrupts.

| 0 | Disables overflow/compare-clear match detection interrupts |

|---|------------------------------------------------------------|

| 1 | Enables overflow/compare-clear match detection interrupts  |

[Bit 0] TMIR: Timer overflow/compare-clear match interrupt request flag

This bit is an interrupt request flag for timer overflow or compare-clear match interrupts.

Bit 0 is set to '1' when the timer overflows or when a match is detected between the values of the compare-clear register and timer.

Write '0' to clear this bit.

Writing '1' to this bit is ignored and the value of this bit is unchanged.

For read-modify-write instructions, the read value of this bit is always '1.'

| 0 | No request for overflow/compare-clear match detection interrupts |

|---|------------------------------------------------------------------|

| 1 | Request for overflow/compare-clear match detection interrupts    |

### (3.2) CICR (Compare Interrupt Control) Register

This register is used for control of compare match interrupts, which are separate interrupts originating from each channel in the compare register. The interrupt request sent to the CPU is the OR-product of the interrupts for the four channels.

|                | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Initial value |

|----------------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| Address: 0031H | CIE3  | CIE2  | CIE1  | CIE0  | CIR3  | CIR2  | CIR1  | CIR0  | 00000008      |

|                | (R/W) |               |

[Bits 7 to 4] CIE3 to CIE0: Compare match interrupt request enable bits

CIE3: Enables interrupt request to CIR3

CIE2: Enables interrupt request to CIR2

CIE1: Enables interrupt request to CIR1

CIE0: Enables interrupt request to CIR0

| 0 | Disables interrupt request at compare match |

|---|---------------------------------------------|

| 1 | Enables interrupt request at compare match  |

[Bits 3 to 0] CIR3 to CIR0: Compare match interrupt request flags

These bits are flags, set to '1' when a match is detected between the values of the corresponding compare register and timer.

Write '0' to clear the bit

Writing '1' is ignored and the values of the bits are unchanged.

For read-modify-write instructions, the read value of these bits is always '1.'

CIR3: Set to '1' when values of compare register 3 (OCPR3) and timer agree.

CIR2: Set to '1' when values of compare register 2 (OCPR2) and timer agree.

CIR1: Set to '1' when values of compare register 1 (OCPR1) and timer agree.

CIR0: Set to '1' when values of compare register 0 (OCPR0) and timer agree.

| 0 | No request for interrupt at compare match |

|---|-------------------------------------------|

| 1 | Request for interrupt at compare match    |

# (3.3) COER (Compare/Port Switching) Register

This register is used to switch between the general-purpose port and timer unit-dedicated port functions.

|                | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Initial value |

|----------------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| Address: 0033H | -     | -     | -     | -     | RTO3  | RTO2  | RTO1  | RTO0  | 0000в         |

|                |       |       |       |       | (R/W) | (R/W) | (R/W) | (R/W) |               |

[Bits 3 to 0] RTO3 to RTO0: Realtime output set bits

Bits 3 to 0 are used to switch the functions of external pins.

| 0 | Operates as general-purpose port                 |

|---|--------------------------------------------------|

| 1 | Operates as dedicated output port for timer unit |

# (3.4) TMCR (Timer Mode Control) Register

This register is used to set the operating mode of the timer, the transfer mode of the buffer register, the signal edge at which the timer is cleared, the timer start and stop signals, and the count clock pulse.

Rewriting of values in this register must be performed with the timer in the stop state.

|                | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Initial value |

|----------------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| Address: 0032H | TMST  | MODE  | TSTX  | _     | CES1  | CES0  | TCS1  | TCS0  | 001-0000в     |

|                | (R/W) | (R/W) | (W)   |       | (R/W) | (R/W) | (R/W) | (R/W) | _             |

[Bit 7] TMST: Timer start/stop bit

This bit is used to start and stop the timer.

When the timer is started, the prescaler is cleared to start counting.

| ( | 0 | Timer stops (default value) |

|---|---|-----------------------------|

|   | 1 | Timer starts                |

### [Bit 6] MODE: Timer count mode select bit

This bit is used to select the operating mode of the timer when a match is detected between values of the compare-clear register and the timer.

| 0 | Sets timer to increment mode.<br>When a match occurs, the timer is cleared to start counting up from 0000H.                                                                                    |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 | Sets timer to increment/decrement mode<br>When a match occurs, the timer is switched from increment to decrement.<br>When zero is detected, the timer is switched from decrement to increment. |

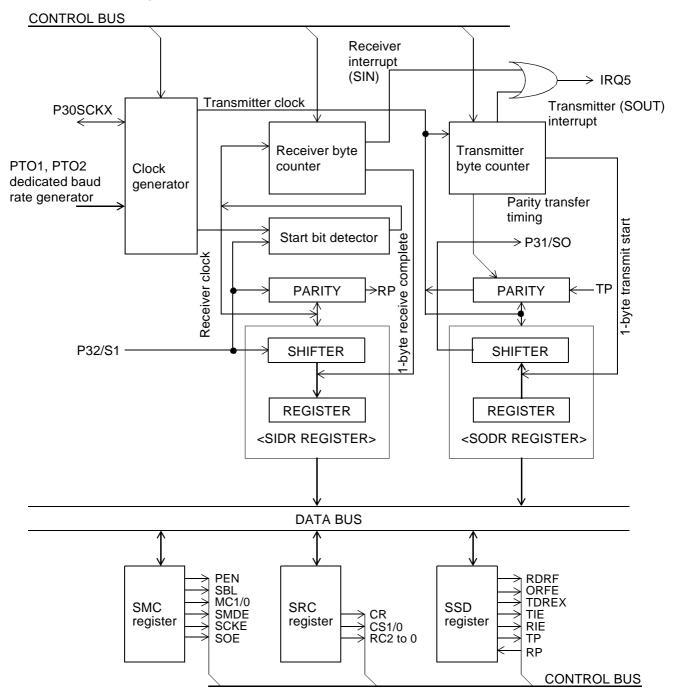

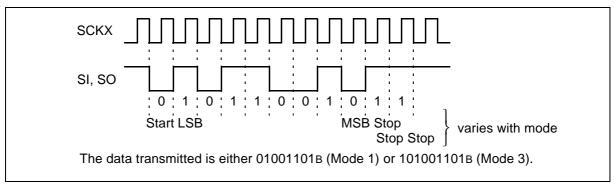

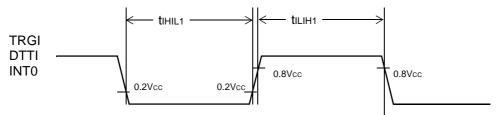

### [Bit 5] TSTX: Test mode select bit