# F<sup>2</sup>MC-8L FAMILY MICROCONTROLLERS MB89950 SERIES

HARDWARE MANUAL

### PREFACE

The MB89950 series of microcontrollers are mid-range of microcontroller. They are general-purpose and high-speed products in the F<sup>2</sup>MC-8L Family series of 8-bit single-chip microcontrollers operating at low voltages. It has UART, PWM, LCD controller and etc.

This manual covers the functions and operations of the MB89950 series of microcontrollers. Refer to the *F*<sup>2</sup>*MC-8L Family Software Manual* for instructions.

| 1. GENERAL                                       |       |

|--------------------------------------------------|-------|

| 1.1 Features                                     |       |

| 1.2 Product Series                               |       |

| 1.3 Block Diagram                                |       |

| 1.4 Pin Assignment                               |       |

| 1.5 Pin Description                              |       |

| 1.6 Handling Devices                             |       |

| -                                                |       |

| 2. HARDWARE CONFIGURATION                        |       |

| 2.1 CPU                                          | 2-3   |

| 2.1.1 Memory Space                               |       |

| 2.1.2 Arrangement of 16-bit Data in Memory Space | 2-5   |

| 2.1.3 Internal Registers in CPU                  |       |

| 2.1.4 Clock Control Block                        | 2-9   |

| 2.1.5 Interrupt Controller                       | 2-15  |

| 2.2 Peripherals                                  | 2-18  |

| 2.2.1 I/O Ports                                  | 2-18  |

| 2.2.2 8-bit PWM Timer (Timer 1)                  |       |

| 2.2.3 Pulse-width Count Timer (Timer 2)          |       |

| 2.2.4 UART                                       |       |

| 2.2.5 8-bit Serial I/O                           |       |

| 2.2.6 External Interrupt                         | 2-56  |

| 2.2.7 LCD Controller/driver                      | 2-59  |

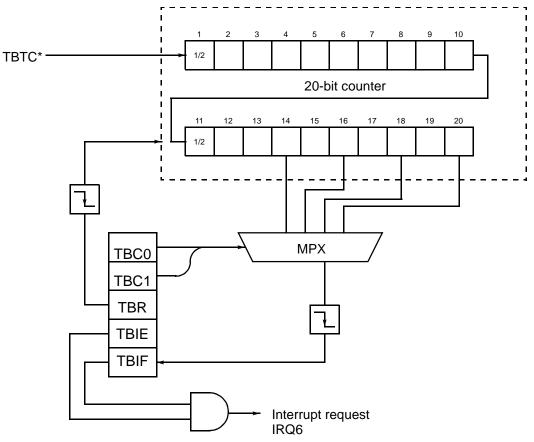

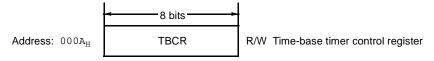

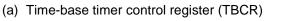

| 2.2.8 Time-base Timer                            | 2-69  |

| 2.2.9 Watchdog Timer Reset                       | 2-71  |

|                                                  |       |

| 3. OPERATION                                     |       |

| 3.1 Clock Pulse Generator                        |       |

| 3.2 Reset                                        |       |

| 3.2.1 Reset Operation                            |       |

| 3.2.2 Reset Sources                              |       |

| 3.3 Interrupt                                    |       |

| 3.4 Low-power Consumption Modes                  |       |

| 3.5 Pin States for Sleep, Stop and Reset         |       |

| 4. INSTRUCTIONS                                  | 4-1   |

| 4.1 Legend                                       |       |

| 4.2 Transfer Instructions                        |       |

| 4.3 Operation Instructions                       |       |

| 4.4 Branch Instructions                          |       |

| 4.5 Other Instructions                           |       |

| 4.6 F <sup>2</sup> MC-8L Family Instruction Map  |       |

| 5. MASK OPTIONS                                  | 5-1   |

|                                                  | A     |

|                                                  |       |

| Appendix A I/O Map                               |       |

| Appendix B Writing EPROM                         | Арр-5 |

# **Table of Contents**

# Tables

| Table 1-1 | Types and Functions of MB89950 Series of Microcontrollers       | 1-4  |

|-----------|-----------------------------------------------------------------|------|

| Table 1-2 | Pin Description                                                 | 1-8  |

| Table 1-3 | Pin Description for External ROM                                | 1-9  |

| Table 2–1 | Table of Reset and Interrupt Vectors                            | 2-4  |

| Table 2–2 | Operating Mode of Low-power Consumption Modes                   | 2-11 |

| Table 2–3 | Selection of Oscillation Stabilization Time                     | 2-12 |

|           | Sources of Reset                                                |      |

| Table 2–5 | List of Port Functions                                          | 2-18 |

| Table 2–6 | Operation Modes of UART                                         | 2-46 |

| Table 2–7 | Clock Division Ratio                                            | 2-48 |

| Table 2–8 | Input Clock of Baud Rate Generator                              | 2-48 |

| Table 2–9 | Selection of Baud Rate (When Dedicated Baud Rate Generate Used) | 2-49 |

| Table 3–1 | Interrupt Sources and Interrupt Vectors                         | 3-7  |

| Table 3–2 | Low-power Consumption Mode at Each Clock Mode                   | 3-8  |

| Table 3–3 | Pin State of MB89950                                            | 3-9  |

| Table 5–1 | Mask Options                                                    | 5-3  |

| Table 5–2 | Recommended Port/Segment Mask Option Combinations               | 5-3  |

# Figures

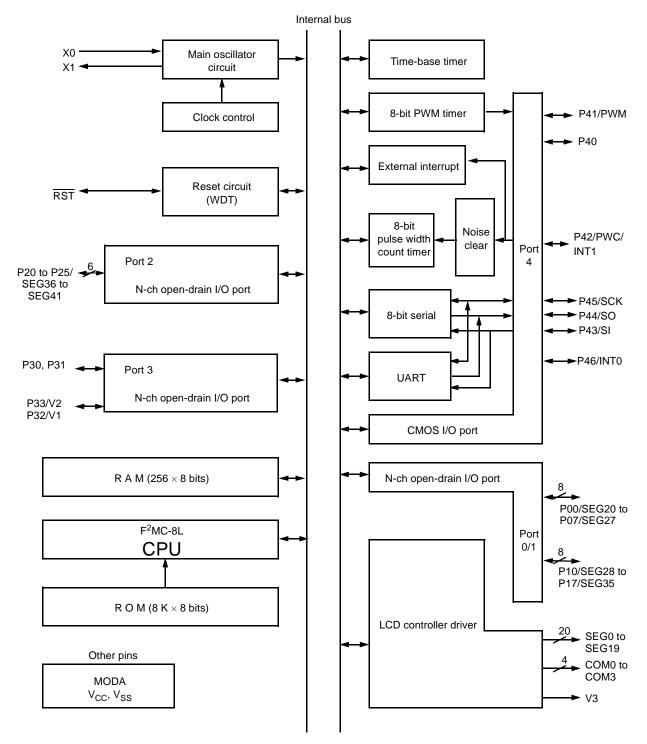

| Fig. 1.1  | Block Diagram (MB89953)                                              | 1-5  |

|-----------|----------------------------------------------------------------------|------|

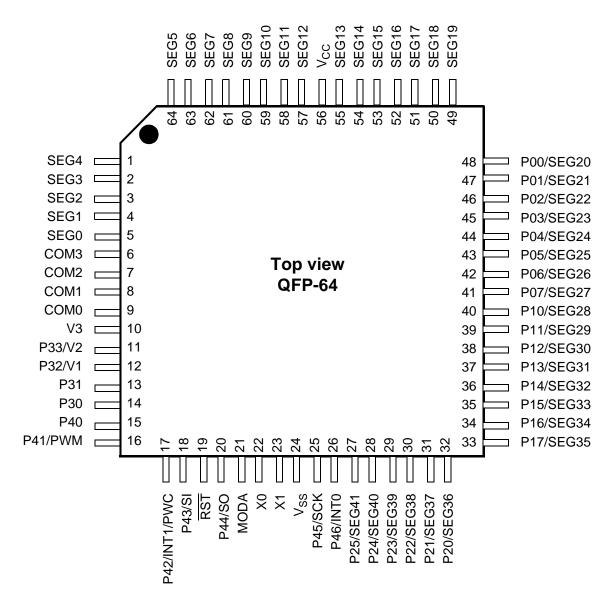

| Fig. 1.2  | Pin Assignment of MB89953 and MB89P955 (QFP-64, pitch: 0.65 mm)      | 1-6  |

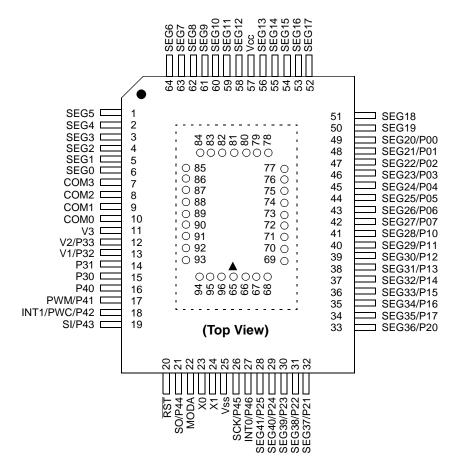

| Fig. 1.3  | Pin Assignment of MB89PV950 (MQFP-64, pitch: 0.8 mm)                 | 1-7  |

| Fig. 1.4  | I/O Circuits                                                         | 1-10 |

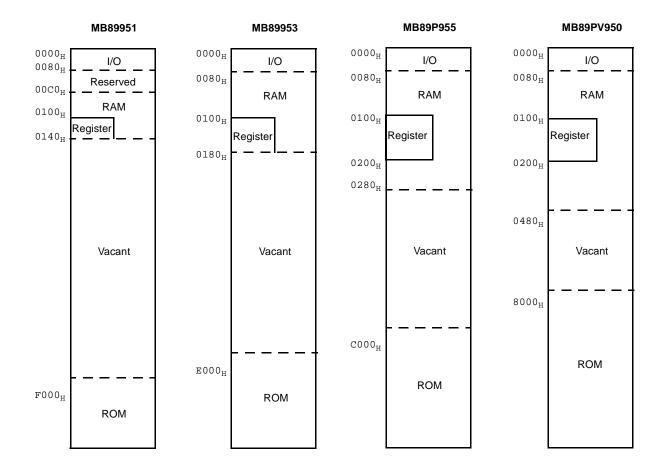

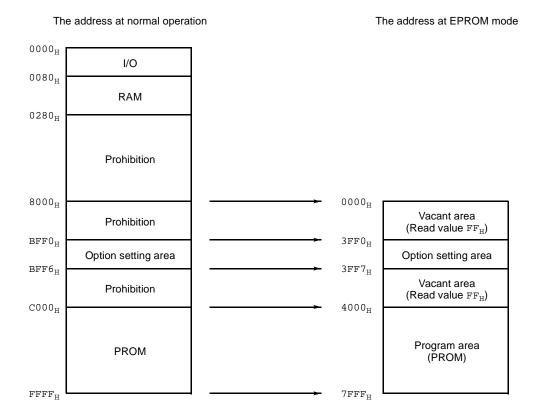

| Fig. 2.1  | Memory Space of MB89950 Series Microcontrollers                      | 2-3  |

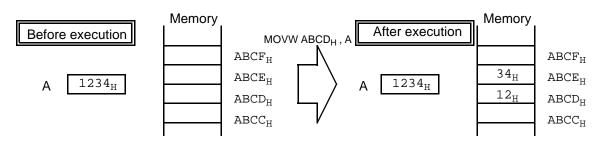

| Fig. 2.2  | Arrangement of 16 bit Data in Memory Space                           | 2-5  |

| Fig. 2.3  | Arrangement of 16 bit Data during Execution of Instruction           | 2-5  |

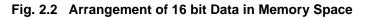

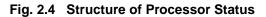

| Fig. 2.4  | Structure of Processor Status                                        | 2-7  |

| Fig. 2.5  | Rule for Translating Real Addresses at General-purpose Register Area | 2-7  |

| Fig. 2.6  | Register Bank Configuration                                          | 2-8  |

| Fig. 2.7  | Interrupt-processing Flowchart                                       | 2-17 |

| Fig. 2.8  | Ports 0, 1 and 2                                                     |      |

| Fig. 2.9  | Port 3                                                               | 2-22 |

| Fig. 2.10 | Port 4                                                               | 2-24 |

| Fig. 2.11 | Timer Operation                                                      | 2-28 |

| Fig. 2.12 |                                                                      |      |

| Fig. 2.13 | •                                                                    |      |

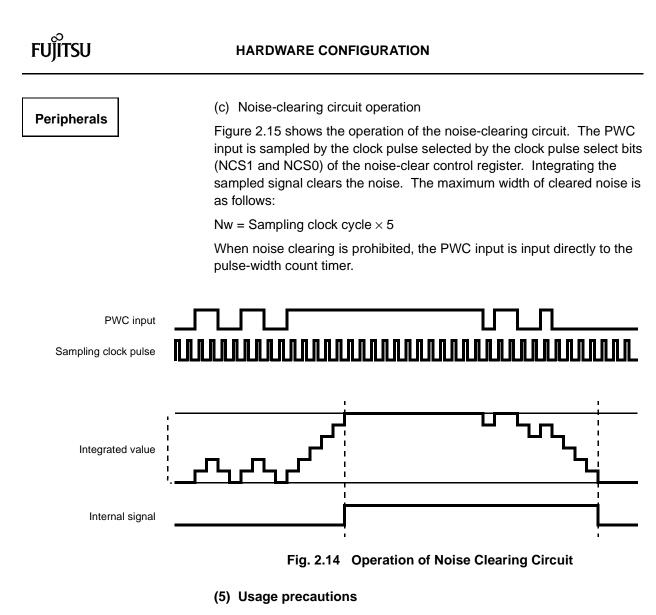

| Fig. 2.14 | Operation of Noise Clearing Circuit                                  | 2-36 |

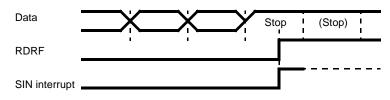

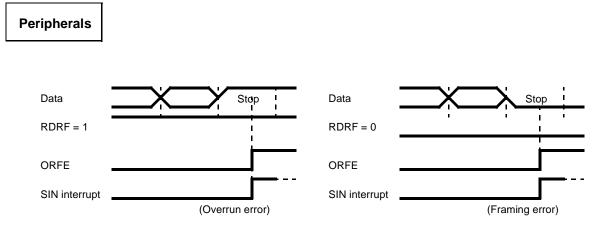

| Fig. 2.15 | RDRF Flag Set Timing                                                 | 2-46 |

| Fig. 2.16 |                                                                      |      |

| Fig. 2.17 | 0 0                                                                  |      |

| Fig. 2.18 |                                                                      |      |

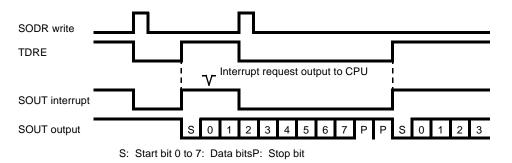

| Fig. 2.19 | Shift Start/Stop Timing                                              | 2-55 |

| Fig. 2.20 |                                                                      |      |

| Fig. 2.21 |                                                                      |      |

| Fig. 2.22 |                                                                      |      |

| Fig. 2.23 |                                                                      |      |

| Fig. 2.24 |                                                                      |      |

| Fig. 2.25 |                                                                      |      |

| Fig. 2.26 | 5 S                                                                  |      |

| Fig. 3.1  |                                                                      |      |

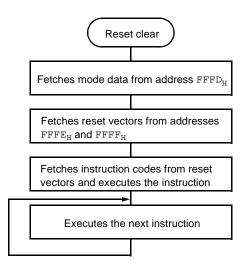

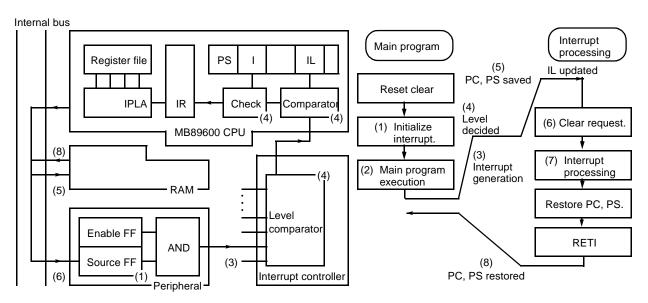

|           | Outline of Reset Operation                                           |      |

|           | Reset Vector Structure                                               |      |

| Fig. 3.4  | Interrupt-processing Flowchart                                       | 3-6  |

# 1.1 Features 1-3 1.2 Product Series 1-4 1.3 Block Diagram 1-5 1.4 Pin Assignment 1-6 1.5 Pin Description 1-8 1.6 Handling Devices 1-12

The MB89950 series of single-chip compact microcontroller using the F<sup>2</sup>MC-8L core for which can operate at high-speeds and low voltages. They contain peripheral such as timers, UART, serial interfaces, and external interrupts, including a 168-pixel LCD controller/driver; they are best suited for use in LCD panels.

#### 1.1 Features

- High-speed processing even at low voltages

Minimum instruction execution time: 0.8 µs/5 MHz (V<sub>CC</sub> = 5 V)

- F<sup>2</sup>MC-8L family CPU core Instruction system most suited to controller

- Multiplication and division instructions

- 16-bit arithmetic operation

- Instruction test and branch instruction

- Bit manipulation instruction, etc.

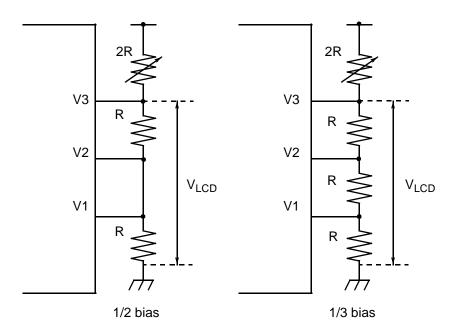

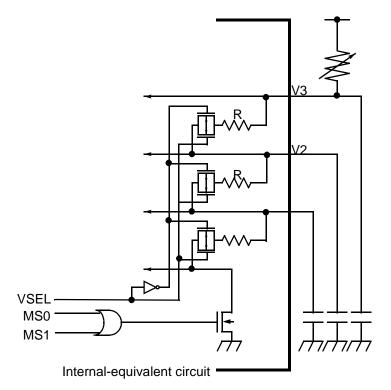

- LCD controller/driver

- Maximum 42 segment outputs x 4 common outputs

- Built-in LCD driver split resistor

- Three-channel timer unit

- 8-bit PWM timer: (usable as both reload timer and PWM timer)

- 8-bit pulse width count timer: (usable as both reload timer)

- 20-bit time-based counter

- Two serial interfaces

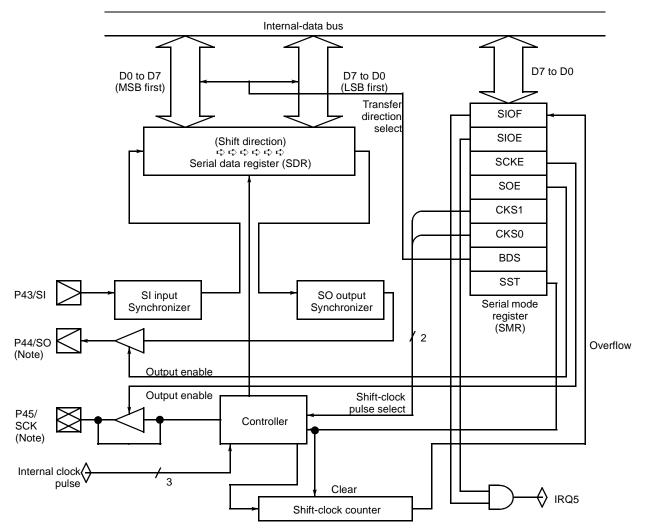

- 8-bit synchronous serial interface (The transfer direction can be selected to communicate with various equipment.)

- UART (5, 7, and 8-bit transfers possible)

- External-interrupt input: 2 channels

- 2 channels can be used to clear the low-power consumption modes. (An edge-detection function is provided)

- Low-power consumption modes

- Stop mode (Oscillation stops to minimize the current consumption.)

- Sleep mode (The CPU stops to reduce current consumption to about 30% of normal.)

#### 1.2 Product Series

Table 1–1 lists the types and functions of the MB89950 series of microcontrollers.

| Model name                   | MB89951                                                                                                                                                                                                                                                                                            | MB89953                       | MB89P955                                                                   | MB89PV950                                          |  |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|----------------------------------------------------------------------------|----------------------------------------------------|--|

| Classification               | Mass-produ<br>(Mask ROI                                                                                                                                                                                                                                                                            |                               | One-time programmable                                                      | Piggyback/Evaluation<br>and development<br>product |  |

| ROM capacity                 | 4K x 8 bits<br>(internal ROM)                                                                                                                                                                                                                                                                      | 8K x 8 bits<br>(internal ROM) | 16K × 8 bits<br>(Internal PROM; writable<br>by general-purpose<br>writers) | 32K × 8 bits<br>(External ROM)                     |  |

| RAM capacity                 | 128 × 8 bits                                                                                                                                                                                                                                                                                       | 256 × 8 bits                  | 512 × 8 bits                                                               | 1024 × 8 bits                                      |  |

| CPU function                 | Number of basic instructions:136<br>Instruction bit length:8 bits<br>Instruction length:1 to 3 bytes<br>Data bit length:1, 8, 16 bits<br>Minimum instruction execution time:0.8 $\mu$ s at 5 MHz (V <sub>CC</sub> = 5 V)<br>Interrupt processing time:7.2 $\mu$ s at 5 MHz (V <sub>CC</sub> = 5 V) |                               |                                                                            |                                                    |  |

| Port                         | <ul> <li>I/O port (N-ch open drain): 22 (also used as segment pin)<sup>*1</sup></li> <li>I/O port (N-ch open drain): 4 (two of them are also used as LCD bias pins)</li> <li>I/O port (CMOS): 7 (6 used as peripheral)</li> <li>Total: 33 (Maximum)</li> </ul>                                     |                               |                                                                            |                                                    |  |

| PWM Timer                    | 8-bit reload timer operation (toggle output possible)<br>8-bit resolution PWM operation<br>Operation clock (pulse-width count timer output: 0.8 μs, 12.8 μs, 51.2 μs/5 MHz)                                                                                                                        |                               |                                                                            |                                                    |  |

| Pulse-width Counter<br>Timer | 8-bit reload timer operation<br>8-bit pulse width measurement (continuous measurement, High- and Low-width measurement, and<br>one-cycle measurement)<br>Operation clock (0.8 μs, 3.2 μs, 25.6 μs/5 MHz)                                                                                           |                               |                                                                            |                                                    |  |

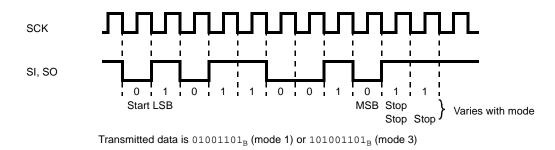

| Serial I/O                   | 8-bit length, selectable from least significant bit (LSB) first or most significant bit (MSB) first, transfer<br>clock (external, 1.6 μs, 6.4 μs, 25.6 μs/5 MHz)                                                                                                                                   |                               |                                                                            |                                                    |  |

| UART                         | 5-, 7-, 8-bit transfers pos                                                                                                                                                                                                                                                                        | ssible, internal baud-rate    | generator (Max. 78125 bp                                                   | os/5 MHz)                                          |  |

| LCD controller/driver        | Common output: 4<br>Segment output: 42 (max.)<br>Operation mode: 1/2 bias and 1/2 duty, 1/3 bias and 1/3 duty, 1/3 bias and 1/4 duty<br>LCD controller display RAM capacity: $42 \times 4$ bits<br>LCD driver split resistor: built-in (external resistor selectable)                              |                               |                                                                            |                                                    |  |

| External Interrupt           | 2 (edge selectable: one serving as pulse-width count timer input)                                                                                                                                                                                                                                  |                               |                                                                            |                                                    |  |

| Standby Mode                 | Sleep mode, stop mode                                                                                                                                                                                                                                                                              |                               |                                                                            |                                                    |  |

| Package                      | FPT-64-M09 MQP-64C-P0                                                                                                                                                                                                                                                                              |                               |                                                                            | MQP-64C-P01                                        |  |

| Operation Voltage *2         | 2.2 V to 6.0 V 2.7 V to 6.0 V                                                                                                                                                                                                                                                                      |                               |                                                                            | o 6.0 V                                            |  |

| EPROM                        | not applicable                                                                                                                                                                                                                                                                                     |                               |                                                                            | MBM27C256A-25<br>(LCC package)                     |  |

| Table 1–1 | Types and Functions of MB89950 Series of Microcontrollers |

|-----------|-----------------------------------------------------------|

|           |                                                           |

\*1 Mask Option.

\*2 Varies according to conditions such as frequency.

#### 1.3 Block Diagram

Fig. 1.1 Block Diagram (MB89953)

FUĴĨTSU

GENERAL

#### 1.4 Pin Assignment

Fig. 1.2 Pin Assignment of MB89953 and MB89P955 (QFP-64, pitch: 0.65 mm)

Fig. 1.3 Pin Assignment of MB89PV950 (MQFP-64, pitch: 0.8 mm)

| Pin No. | Pin Name |

|---------|----------|---------|----------|---------|----------|---------|----------|

| 65      | N.C.     | 73      | A2       | 81      | N.C.     | 89      | OE       |

| 66      | Vpp      | 74      | A1       | 82      | O4       | 90      | N.C.     |

| 67      | A12      | 75      | A0       | 83      | O5       | 91      | A11      |

| 68      | A7       | 76      | N.C.     | 84      | O6       | 92      | A9       |

| 69      | A6       | 77      | O1       | 85      | 07       | 93      | A8       |

| 70      | A5       | 78      | O2       | 86      | O8       | 94      | A13      |

| 71      | A4       | 79      | O3       | 87      | CE       | 95      | A14      |

| 72      | A3       | 80      | Vss      | 88      | A10      | 96      | Vcc      |

Pin assignment on package top (MB89PV950 only)

N.C.: Non connection pin. Keep open.

#### 1.5 Pin Description

Table 1–2 lists the pin functions and shows the Fig. 1.4 input/output circuits.

| Pin      | No          | <b>D</b> . 11                | 0       |                                                                                                                                                                                                                     |

|----------|-------------|------------------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0.65     | 0.8         | Pin Name                     | Circuit | Function                                                                                                                                                                                                            |

| 22       | 23          | X0                           | А       | Clock oscillator pins                                                                                                                                                                                               |

| 23       | 24          | X1                           |         |                                                                                                                                                                                                                     |

| 21       | 22          | MODA                         | В       | Operation-mode select pins<br>This pin is connected directly to Vss with pull down resistor.                                                                                                                        |

| 19       | 20          | RST                          | С       | Reset I/O pin<br>This pin consists of an N-ch open-drain output with a pull-up resistor and<br>hysteresis input. A Low level is put out from this pin. A "LOW" voltage on<br>this port generates a RESET condition. |

| 48 to 41 | 49 to<br>42 | P00/SEG20<br>to<br>P07/SEG27 | D       | N-channel open-drain type general-purpose I/O ports<br>Also serve as LCDC controller segment outputs.<br>Switching between port output and segment output is performed by the<br>mask option every 8 bits.          |

| 40 to 33 | 41 to<br>34 | P10/SEG28<br>to<br>P17/SEG35 | D       | N-channel open-drain type general-purpose I/O ports<br>Also serve as LCDC controller segment outputs.<br>Switching between port output and segment output is performed by the<br>mask option.                       |

| 32 to 27 | 33 to<br>28 | P20/SEG36<br>to<br>P25/SEG41 | D       | N-channel open-drain type general-purpose I/O ports<br>Also serve as LCDC controller segment outputs.<br>Switching between port output and segment output is performed by the<br>mask option.                       |

| 14 to 11 | 15 to<br>12 | P30 to P31                   | F       | N-channel open-drain type general-purpose I/O ports                                                                                                                                                                 |

| 12 to 11 | 13 to<br>12 | P32/V1 to<br>P33/V2          | D       | N-channel open-drain type general-purpose I/O ports<br>Also serve as LCDC controller power supply.                                                                                                                  |

| 15       | 16          | P40                          | E       | General-purpose I/O ports<br>A pull-up resistor option is provided.                                                                                                                                                 |

| 16       | 17          | P41/PWM                      | E       | General-purpose I/O port<br>Serves as PWM timer toggle output (PWM).<br>A pull-up resistor option is provided.                                                                                                      |

| 17       | 18          | P42/PWC/<br>INT1             | E       | General-purpose I/O port<br>Also serves as pulse-width count timer input (PWC) and external interrupt<br>input (INT1). The PWC and INT1 inputs are hysteresis type. A pull-up<br>resistor option is provided.       |

| 18       | 19          | P43/SI                       | E       | General-purpose I/O port<br>Also serves as serial I/O and UART data input (SI). The SI input is<br>hysteresis type.<br>A pull-up resistor option is provided.                                                       |

| 20       | 21          | P44/SO                       | E       | General-purpose I/O port<br>Also serves as serial I/O and UART data output (SO).<br>A pull-up resistor option is provided.                                                                                          |

| 25       | 26          | P45/SCK                      | E       | General-purpose I/O port<br>Also serves as serial I/O and UART clock input/output (SCK). The SCK<br>input is hysteresis type.<br>A pull-up resistor option is provided.                                             |

| Table 1–2 | Pin Description |

|-----------|-----------------|

|-----------|-----------------|

| Pin                            | No      | Pin Name         | Circuit | Function                                                                                                                                                 |

|--------------------------------|---------|------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0.65                           | 0.8     |                  | Circuit | Function                                                                                                                                                 |

| 26                             | 27      | P46/INT0         | E       | General-purpose input port<br>Also serves as external-interrupt input (INT0).<br>The input is hysteresis type.<br>A pull-up resistor option is provided. |

| 5 to 1<br>64 to 57<br>55 to 49 |         | SEG0 to<br>SEG19 | G       | For LCDC controller segment ouput                                                                                                                        |

| 9 to 6                         | 7 to 10 | COM0 TO<br>COM3  | G       | For LCDC controller common output                                                                                                                        |

| 10                             | 11      | V3               | -       | For LCD driver power supply                                                                                                                              |

| 56                             | 57      | Vcc              | -       | Power Pin                                                                                                                                                |

| 24                             | 25      | Vss              | -       | Power (GND) Pin                                                                                                                                          |

Table 1–2

Pin Description (Continued)

#### Table 1–3 Pin Description for External ROM

• External EPROM pins (for MB89PV950)

| Pins No. | Pin Name | I/O | Function                                  |

|----------|----------|-----|-------------------------------------------|

| 66       | Vpp      | 0   | For High-level output                     |

| 67       | A12      |     |                                           |

| 68       | A7       |     |                                           |

| 69       | A6       |     |                                           |

| 70       | A5       |     |                                           |

| 71       | A4       | 0   | For address output                        |

| 72       | A3       |     |                                           |

| 73       | A2       |     |                                           |

| 74       | A1       |     |                                           |

| 75       | A0       |     |                                           |

| 77       | 01       |     |                                           |

| 78       | O2       | I   | For data input                            |

| 79       | O3       |     |                                           |

| 80       | Vss      | 0   | For power supply (GND)                    |

| 82       | 04       |     |                                           |

| 83       | O5       |     |                                           |

| 84       | O6       | I   | For data input                            |

| 85       | 07       |     |                                           |

| 86       | O8       |     |                                           |

| 87       | CE       | 0   | For ROM output enable                     |

| _        |          |     | The High level is output in standby mode. |

| 88       | A10      | 0   | For address output                        |

| 89       | OE       | 0   | For ROM output enable.                    |

|          | _        |     | The Low level is always output.           |

| 91       | A11      |     |                                           |

| 92       | A9       | 0   | For address output                        |

| 93       | A8       |     |                                           |

| 94       | A13      | 0   | For address output                        |

| 95       | A14      |     |                                           |

| 96       | Vcc      | 0   | For EPROM power supply                    |

#### Table 1–3 Pin Description for External ROM (Continued)

• External EPROM pins (for MB89PV950)

| Pins No. | Pin Name | I/O | Function                |

|----------|----------|-----|-------------------------|

| 65<br>76 |          |     | For internal connection |

| 81<br>90 | N.C.     |     | Keep open.              |

Fig. 1.4 I/O Circuits

| Classification | Circuit                                                             | Remarks                                                                                                  |

|----------------|---------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

| A              | X1<br>T<br>T<br>T<br>T<br>T<br>T<br>T<br>T<br>T<br>T<br>T<br>T<br>T | <ul> <li>Crystal oscillator</li> <li>Feedback resistor: About 1 MΩ/<br/>5 V (1 to 5 MHz)</li> </ul>      |

| В              | R<br>777                                                            | <ul> <li>CMOS input</li> <li>Pull down resistor (N-ch)</li> </ul>                                        |

| С              | R<br>R<br>R<br>N-ch<br>R<br>N-ch                                    | <ul> <li>Output pull-up resistor (P-ch):</li> <li>About 50 MΩ (5 V)</li> <li>Hysteresis input</li> </ul> |

| D              |                                                                     | <ul> <li>N-ch open-drain output</li> <li>CMOS input</li> <li>The segment output is optional.</li> </ul>  |

| Classification | Circuit                                                                                                                       | Remarks                                                                                                                                         |

|----------------|-------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| E              | R<br>R<br>P-ch<br>P-ch<br>P-ch<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R | <ul> <li>CMOS output</li> <li>CMOS input</li> <li>Hysteresis input<br/>(peripheral input)</li> <li>The pull-up resistor is optional.</li> </ul> |

| F              |                                                                                                                               | <ul> <li>• N-ch open-drain output</li> <li>• CMOS input</li> </ul>                                                                              |

| G              |                                                                                                                               | LCDC output                                                                                                                                     |

Fig. 1.4 I/O Circuits (Continued)

#### 1.6 Handling Devices

#### (1) Preventing latch-up

Latchup may occur on CMOS ICs if voltage higher than  $V_{CC}$  or lower than  $V_{SS}$  is applied to input and output pins other than medium to high-voltage pins or if higher than the voltage which shows on Absolute Maximum Ratings is applied between  $V_{CC}$  and  $V_{SS}$ .

When latch-up occurs, supply current increases rapidly and might thermally damage elements. When using, take great care not to exceed the absolute maximum ratings.

#### (2) Treatment of Unused Input Pins

Leaving unused input pins open could cause malfunctions. They should be connected to pull-up or pulldown resistor.

#### (3) Power Supply Voltage Fluctuations

Although  $V_{CC}$  power supply voltage is assured to operate within the rated, a rapid change to the IC is therefore cause malfunctions, even if it occurs within the rated range. Stabilizing voltage supplied of the IC is therefore important. As stabilization guidelines, it is recommended to control power so that  $V_{CC}$  ripple fluctuations (P-P. value) will be less that 10% of the standard  $V_{CC}$  value at the commercial frequency (50 to 60 Hz) and the transient fluctuation rate will be less than 0.1 V/ms at the time of a momentary fluctuation such as when power is switched.

#### (4) Precaution When Using an External Clock

Even when an external clock is used, oscillation stabilization time is required for power-on reset (option selection) and release from stop mode.

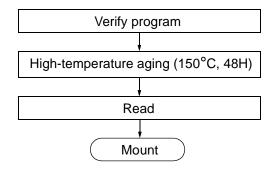

#### (5) Recommended Screening Conditions

The OTPROM product should be screened by high-temperature aging before mounting.

The programming test cannot be performed for all bits of the preprogrammed OTPROM product due to its characteristics. Consequently, 100% programming yielding cannot be ensured.

# 2. HARDWARE CONFIGURATION

| 2.1 | CPU             |  |

|-----|-----------------|--|

|     | Peripherals2-18 |  |

This chapter describes each block of the CPU hardware.

CPU

#### 2.1 CPU

This section describes the memory space and register composing CPU hardware.

#### 2.1.1 Memory Space

F<sup>2</sup>MC-8L CPU has a memory space of 64 Kilobytes. All I/O, data, and program areas are located in this space. The I/O area is near the lowest address and the data area is immediately above it. The data area can be divided into register, stack, and direct-address areas according to the applications. The program area is located near the highest address, and the tables of interrupt and reset vectors and vector-call instructions are at the highest address in this area. Fig.2.1 shows the structure of the memory space for the MB89950 series of microcontrollers.

Fig. 2.1 Memory Space of MB89950 Series Microcontrollers

#### (1) I/O area

This area is where various peripherals such as control and data registers are located. The memory map for the I/O area is given in APPENDIX A.

#### (2) RAM area

This area is where the static RAM is located. Addresses from  $0100_{\rm H}$  to  $017F_{\rm H}$  ( $0100_{\rm H}$  to  $013F_{\rm H}$  in MB89951,  $0100_{\rm H}$  to  $01FF0_{\rm H}$  in MB89P955 and MB89PV950) are also used as the general-purpose register area. One can access these registers through register-related instructions or just treat them as ordinary RAM.

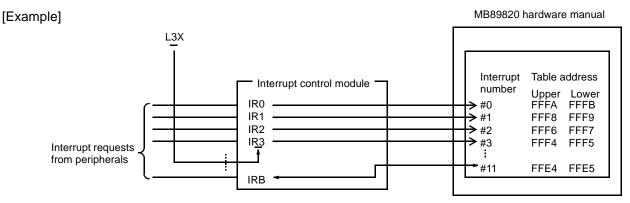

#### (3) ROM area

This area is where the internal ROM is located. Addresses from  $FFC0_H$  to  $FFFF_H$  are also used for the table of interrupt, reset and vector-call instructions. Table 2–1 shows the correspondence between each interrupt number or reset and the table addresses to be referenced for the MB89950 series of microcontrollers.

|          | Table a           | address           |              | Table a           | ddress                       |

|----------|-------------------|-------------------|--------------|-------------------|------------------------------|

|          | Upper data        | Lower data        |              | Upper data        | Lower data                   |

| CALLV #0 | FFC0 <sub>H</sub> | $FFC1_{H}$        | Interrupt #B | FFE4 <sub>H</sub> | FFE5 <sub>H</sub>            |

| CALLV #1 | FFC2 <sub>H</sub> | FFC3 <sub>H</sub> | Interrupt #A | FFE6 <sub>H</sub> | ffe7 <sub>h</sub>            |

| CALLV #2 | FFC4 <sub>H</sub> | FFC5 <sub>H</sub> | Interrupt #9 | FFE8 <sub>H</sub> | ffe9 <sub>h</sub>            |

| CALLV #3 | FFC6 <sub>H</sub> | FFC7 <sub>H</sub> | Interrupt #8 | ffea <sub>h</sub> | FFEB <sub>H</sub>            |

| CALLV #4 | FFC8 <sub>H</sub> | FFC9 <sub>H</sub> | Interrupt #7 | FFEC <sub>H</sub> | $\mathtt{FFED}_{\mathtt{H}}$ |

| CALLV #5 | FFCA <sub>H</sub> | FFCB <sub>H</sub> | Interrupt #6 | FFEE <sub>H</sub> | FFEF <sub>H</sub>            |

| CALLV #6 | FFCC <sub>H</sub> | FFCD <sub>H</sub> | Interrupt #5 | FFF0 <sub>H</sub> | FFF1 <sub>H</sub>            |

| CALLV #7 | FFCE <sub>H</sub> | FFCF <sub>H</sub> | Interrupt #4 | FFF2 <sub>H</sub> | FFF3 <sub>H</sub>            |

|          |                   |                   | Interrupt #3 | FFF4 <sub>H</sub> | FFF5 <sub>H</sub>            |

|          |                   |                   | Interrupt #2 | FFF6 <sub>H</sub> | $FFF7_{H}$                   |

|          |                   |                   | Interrupt #1 | FFF8 <sub>H</sub> | FFF9 <sub>H</sub>            |

|          |                   |                   | Interrupt #0 | FFFA <sub>H</sub> | FFFB <sub>H</sub>            |

|          |                   |                   | Reset mode   |                   | $\mathtt{FFFD}_{\mathtt{H}}$ |

|          |                   |                   | Reset vector | FFFE <sub>H</sub> | FFFF <sub>H</sub>            |

#### Table 2–1 Table of Reset and Interrupt Vectors

Note:  ${\tt FFFC}_{\rm H}$  is already reserved. When using  ${\tt FFFD}_{\rm H}$  in the reset mode, write  ${\tt 00}_{\rm H}.$

#### 2.1.2 Arrangement of 16-bit Data in Memory Space

When the MB89950 series of microcontrollers handle 16-bit data, the data written at the lower address is treated as the upper 8-bit data and that written at the next address is treated as the lower 8-bit data as shown in Fig. 2.2.

This is the same when 16 bits are specified by the operand during execution of an instruction. Bits closer to the OP code are treated as the upper byte and those next to it are treated as the lower byte. This is also the same when the memory address or 16-bit immediate data is specified by the operand.

| [Example]                   |                         |

|-----------------------------|-------------------------|

| MOV A, $5678_{\rm H}$       | ; Extended address      |

| MOV A, $#1234_{H}$          | ; 16-bit immediate data |

| As                          | semble                  |

| XXXX <sub>H</sub> XX XX     |                         |

| XXXX <sub>H</sub> 60 56 78  | ; Extended address      |

| $\rm XXXX_{\rm H}$ E4 12 34 | ; 16-bit immediate data |

| XXXX <sub>H</sub> XX        |                         |

#### Fig. 2.3 Arrangement of 16 bit Data during Execution of Instruction

Data saved in the stack by an interrupt is also treated in the same manner.

| CD |   |

|----|---|

| υг | υ |

#### 2.1.3 Internal Registers in CPU

The MB89950 series of microcontrollers have dedicated registers in the CPU and general-purpose registers in memory. The types of dedicated registers are as follows.

- Program counter (PC) 16-bit length register indicating the location where instructions are stored.

- Accumulator (A) 16-bit length register storing results of operations temporarily. The lower one byte is used to execute 8-bit data processing instructions.

- Temporary accumulator (T) 16-bit length register where the operations are performed between this register and the accumulator. The lower one byte is used to execute 8-bit data processing instructions.

- Index register (IX) 16-bit length register for index modification.

- Extra pointer (EP) 16-bit length register for indicating memory address.

- Stack pointer (SP) 16-bit length register indicating stack area.

- Processor status (PS) 16-bit length register where register pointers and condition codes are stored.

| 16 bits |                       |

|---------|-----------------------|

| P C     | Program counter       |

| A       | Accumulator           |

| Т       | Temporary accumulator |

| IX      | Index register        |

| EP      | Extra pointer         |

| SP      | Stack pointer         |

| PS      | Processor status      |

The 16 bits of the processor status (PS) can be divided into 8 upper bits for a register bank pointer (RP) and 8 lower bits for a condition code register (CCR). (See Fig. 2.4.)

The RP indicates the address of the current register bank. The relationship between the contents of the RP and the real addresses is as shown in Figure 2.5.

|                |              |              |              |              |              |              |              | _            |              |              | R P Lo       |              | Lower bits of OP co |              | ode          |              |  |

|----------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|---------------------|--------------|--------------|--------------|--|

|                | '0'          | '0'          | '0'          | '0'          | '0'          | '0'          | '0'          | '1'          | R4           | R3           | R2           | R1           | R0                  | b2           | b1           | b0           |  |

|                | $\downarrow$        | $\downarrow$ | $\downarrow$ | $\downarrow$ |  |

| Source address | A15          | A14          | A13          | A12          | A11          | A10          | A9           | A8           | A7           | A6           | A5           | A4           | A3                  | A2           | A1           | A0           |  |

#### Fig. 2.5 Rule for Translating Real Addresses at General-purpose Register Area

The CCR has bits indicating the results of operations and transfer data contents, and bits controlling the CPU operation when an interrupt occurs.

- H-flag is set when a carry or a borrow out of bit 3 into bit 4 is generated as a result of operations; it is cleared in other cases. This flag is used for decimal-correction instructions.

- I-flag An interrupt is enabled when this flag is 1 and is disabled when it is 0. The I-flag is 0 at reset.

- IL1 and IL0 These bits indicate the level of the currently-enabled interrupt. The CPU executes interrupt processing only when an interrupt with a value smaller than the value indicated by this bit is requested.

| IL1 | IL0 | Interrupt level | High and low       |

|-----|-----|-----------------|--------------------|

| 0   | 0   | 1               | High               |

| 0   | 1   | I               | ≜.                 |

| 1   | 0   | 2               |                    |

| 1   | 1   | 3               | low = No interrupt |

- N-flag The N-flag is set when the most significant bit is 1 as a result of operations; it is cleared when the MSB is 0.

CPU

- Z-flag Z-flag is set when zero is the result of operations; it is cleared in other cases.

- V-flag V-flag is set when a two's complement overflow occurs as a result of operations; it is reset when an overflow does not occur.

- C-flag C-flag is set when a carry or a borrow out of bit 7 is generated as a result of operations; it is cleared in other cases. When the shift instruction is executed, the value of the C-flag is shifted out.

• General-purpose register..... 8-bit length register where data are stored. 8-bit general-purpose registers are provided in the register banks in the memory for storing data. Eight registers are provided per bank for and up to 16 banks can be used for MB89953 (8 banks are provided in MB89951, 32 banks are provided in MB89P955 and MB89PV950). The register bank pointer (RP) indicates the currently-used bank.

Note: The register banks are as follows depend on RAM area.

| MB89951   | $\texttt{OlOO}_{H} \ \textbf{to} \ \texttt{OlSF}_{H}$ | 8 banks  |

|-----------|-------------------------------------------------------|----------|

| MB89953   | $\texttt{0100}_{H}$ to $\texttt{017F}_{H}$            | 16 banks |

| MB89P955  | $\texttt{Oloo}_{H} \text{ to } \texttt{Olff}_{H}$     | 32 banks |

| MB89PV950 | $\texttt{OlOO}_{H} \text{ to } \texttt{OlFF}_{H}$     | 32 banks |

Fig. 2.6 Register Bank Configuration

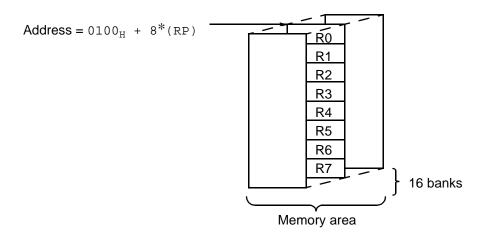

#### 2.1.4 Clock Control Block

CPU

This block controls the standby operation and software reset.

#### (1) Machine clock control block diagram

(a) Machine clock control section

# FUĴÎTSU

(Initial value) 0001XXXX<sub>B</sub>

#### [Bit 7] STP: Stop bit

This bit is used to specify switching CPU to the stop mode.

| ĺ | 0 | No operation |

|---|---|--------------|

| ĺ | 1 | Stop mode    |

This bit is cleared at reset or stop cancellation.

0 is always read when this bit is read.

#### [Bit 6] SLP: Sleep bit

This bit is used to specify switching the CPU to the sleep mode.

| 0 | No operation |

|---|--------------|

| 1 | Sleep mode   |

This bit is cleared at reset, sleep cancellation or stop cancellation.

0 is always read when this bit is read.

[Bit 5] SPL: Pin state specifying bit

This bit is used to specify the external pin state in the stop mode.

| 0 | Holds pin state and level immediately before stop mode |

|---|--------------------------------------------------------|

| 1 | High impedance                                         |

This bit is cleared at reset.

[Bit 4] RST: Software reset bit

This bit is used to specify the software reset.

| 0 | Generates 4-cycle reset signal |

|---|--------------------------------|

| 1 | No operation                   |

1 is always read when this bit is read.

#### (4) Description of operation

(a) Low-power consumption mode

This chip has three operation modes shown in the table below. The sleep mode and stop mode reduce the power consumption. The system clock can be selected out of three according to the system condition to minimize power consumption.

| Oscillation | Clock      | Each o  | operating cloc<br>(5 MHz clock) | Wake-up source     |                    |

|-------------|------------|---------|---------------------------------|--------------------|--------------------|

| mode        | pulse      | CPU     | Time-base<br>timer              | Each<br>peripheral | in each mode       |

| RUN         | Oscillates | 2.5 MHz | 2.5 MHz                         | 2.5 MHz            | Various interrupt  |

| SLEEP       | Oscillates | Stopp   |                                 |                    | requests           |

| STOP        | Stop       | Stops   | Stops                           | Stops              | External interrupt |

Table 2–2 Operating Mode of Low-power Consumption Modes

- The SLEEP mode stops only the operating clock pulse of the CPU; other operations are continued.

- The STOP mode stops the oscillation. Data can be held with the lowest power consumption in this mode.

#### a. SLEEP mode

- Switching to Sleep mode

- Writing 1 at the SLP (bit 6) of the STBC register switches the mode to SLEEP mode.

- The SLEEP mode is the mode to stop clock pulse operating the CPU; only the CPU stops and the peripherals continue to operate.

- If an interrupt is requested when 1 is written at the SLP (bit 6), instruction execution continues without switching to the SLEEP mode.

- In the SLEEP mode, the contents of registers and RAM immediately before entering the SLEEP mode are held.

- Canceling SLEEP mode

- The SLEEP mode is canceled by inputting the reset signal or requesting an interrupt.

- When the reset signal is input during the SLEEP mode, the CPU is switched to the reset state and the SLEEP mode is canceled.

- When an interrupt level higher than 11 is requested from a peripheral during the SLEEP mode, the SLEEP mode is canceled.

- When the I flag and IL bit are enable after canceling, the CPU executes the interrupt processing like an ordinary interrupt. When they are disabled, the CPU starts processing the next instruction given before entering the SLEEP mode.

CPU

#### b. STOP mode

- Switching to STOP mode

- Writing 1 at the STP (bit 7) of the STBC register switches the mode to STOP mode.

- The STOP mode stops clock oscillation and the CPU and all peripherals stop.

- The input/output pins and output pins in the STOP mode can be controlled by the SPL (bit 5) of the STBC register so that they are held in the state immediately before entering the STOP mode, or so that they enter in the high-impedance state.

- If an interrupt is requested when 1 is written at the STP (bit 7), instruction execution continues without switching to the STOP mode.

- In the STOP mode, the contents of registers and RAM immediately before entering the STOP mode are held.

- Canceling STOP mode

- The STOP mode is canceled either by inputting the reset signal or by requesting an interrupt.

- When the reset signal is input during the STOP mode, the CPU is switched to the reset state and the STOP mode is canceled.

- When an interrupt higher than level 11 is requested from the external interrupt circuit during the STOP mode, the STOP mode is canceled.

- When the I flag and IL bit are enabled after canceling, the CPU executes the interrupt processing like an ordinary interrupt. When they are disabled, the CPU starts processing the next instruction given before entering the STOP mode.

- The oscillation stabilization time can be selected from the two types in Table 2–3 as options.

- If the STOP mode is canceled by inputting the reset signal, the CPU is switched to the oscillation stabilization state. Therefore, the reset sequence is not executed unless the oscillation stabilization time is elapsed. The oscillation stabilization time corresponds to the optionally selected oscillation stabilization time of the main clock. However, when Power-on reset unavailable is selected by the mask option, the CPU is not switched to the oscillation stabilization state even if the STOP mode is canceled by inputting the reset signal.

| Oscillation<br>stabilization time      | Oscillation stabilization<br>time at 5 MHz | Remarks                |

|----------------------------------------|--------------------------------------------|------------------------|

| About 2 <sup>18</sup> /f <sub>CH</sub> | About 52.4 ms                              | For crystal oscillator |

| About 2 <sup>14</sup> /f <sub>CH</sub> | About 3.28 ms                              | For crystal oscillator |

| Table 2–3 | Selection | of | Oscillation | Stabilization | Time |

|-----------|-----------|----|-------------|---------------|------|

|           |           |    |             |               |      |

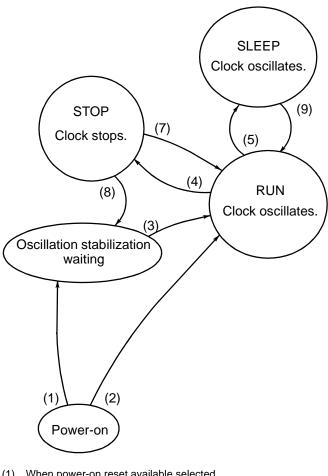

#### (b) State transition diagram

- When power-on reset available selected (1)

- (2) (3) When power-on reset unavailable selected After oscillation stabilizing

- Set STP bit to 1. Set SLP bit to 1. (4) (5)

- (7) (8)

- External reset when power-on reset unavailable selected External reset or interrupt when power-on reset available selected

- (9) External reset or interrupt

CPU

#### (c) Reset

There are four types of reset depending on the source shown in Table 2–4.

| Table 2–4 | Sources | of Reset |

|-----------|---------|----------|

|-----------|---------|----------|

| Reset name         | Description                            |

|--------------------|----------------------------------------|

| External-pin reset | When setting external-reset pin to Low |

| Software reset     | When writing 0 at RST (bit 4) of STBC  |

| Watchdog reset     | When watchdog timer overflows          |

| Power-on reset     | When turning power on                  |

When the power-on reset or reset during the stop state is used, the oscillation stabilization time is needed after the oscillator starts operating. The time-base timer controls this stabilization time. Consequently, the operation does not start immediately even after canceling the reset.

However, if Power-on reset is not selected by the mask option, no oscillation stabilization time is required in any state after external pins have been released from the reset.

Note: A longer time than the optionally-specified oscillation stabilization time should be allowed for reset at power-on of Power-on reset unavailable products. In other cases, the time is based on theorist timing given in the *MB89950 SERIES DATA SHEET* "AC characteristics."

#### 2.1.5 Interrupt Controller

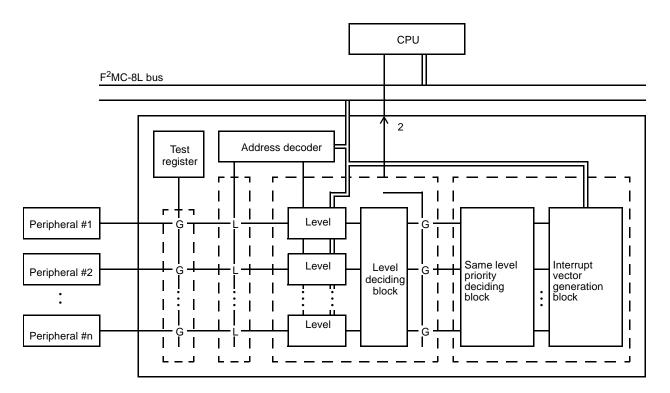

The interrupt controller for the  $F^2MC-8L$  family is located between the CPU and each peripheral. This controller receives interrupt requests from the peripherals, assigns priority to them. When the interrupt controller transfers the priority to the CPU, it also decides the priority of same-level interrupts.

#### (1) Block diagram

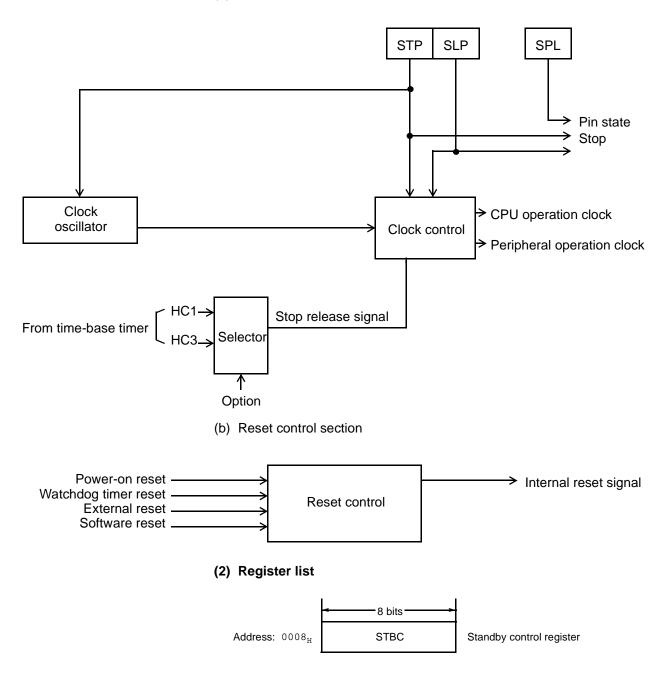

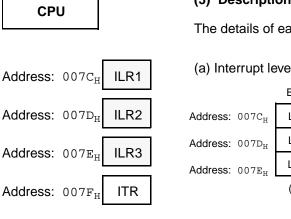

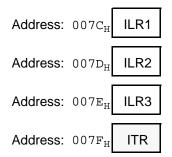

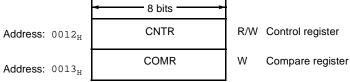

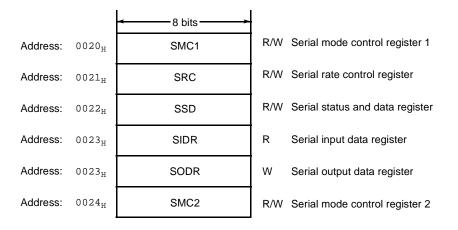

#### (2) Register list

Interrupt controller consists of interrupt-level registers (ILR1, 2, and 3) and interrupt-test register (ITR).

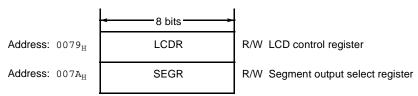

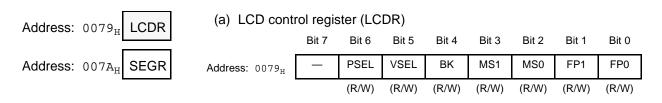

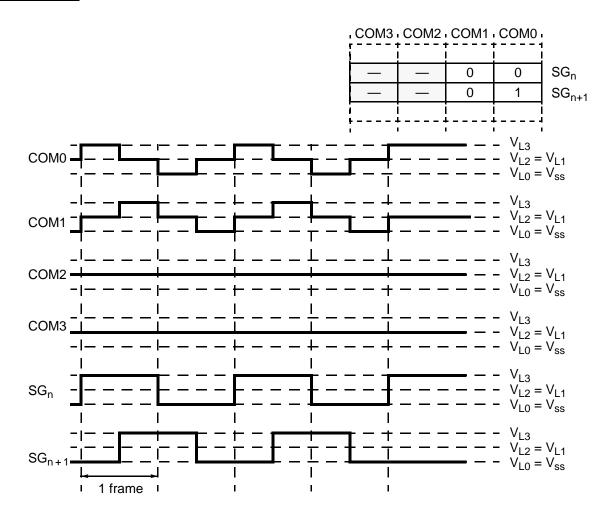

|                     | ≺ 8 bits → |   |                             |

|---------------------|------------|---|-----------------------------|

| Address: $007C_{H}$ | ILR1       | W | Interrupt level register #1 |

| Address: $007D_{H}$ | ILR2       | w | Interrupt level register #2 |

| Address: $007E_{H}$ | ILR3       | w | Interrupt level register #3 |

| Address: $007F_{H}$ | ITR        | _ | Interrupt test register     |

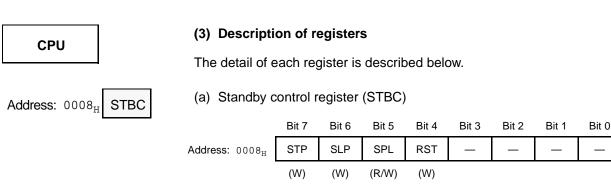

#### (3) Description of registers

The details of each register is described below.

(a) Interrupt level register 1 to 3 (ILRx: Interrupt Level Register x)

|                            | Bit 7                                    | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|----------------------------|------------------------------------------|-------|-------|-------|-------|-------|-------|-------|

| Address: $007C_{H}$        | L31                                      | L30   | L21   | L20   | L11   | L10   | L01   | L00   |

| Address: $007D_{H}$        | L71                                      | L70   | L61   | L60   | L51   | L50   | L41   | L40   |

| Address: 007E <sub>H</sub> | LB1                                      | LB0   | LA1   | LA0   | L91   | L90   | L81   | L80   |

| _                          | (W)                                      | (W)   | (W)   | (W)   | (W)   | (W)   | (W)   | (W)   |

|                            | (Initial value)<br>11111111 <sub>B</sub> |       |       |       |       |       |       |       |

The ILRx sets the interrupt level of each peripheral. The digits in the center of each bit correspond to the interrupt numbers.

[Bits 7 and 6][Bits 5 and 4][Bits 3 and 2][Bits 1 and 0]Lx1, Lx0: Interrupt level setting bit

| Lx1 | Lx0 | Required interrupt level |

|-----|-----|--------------------------|

| 0   | Х   | 1                        |

| 1   | 0   | 2                        |

| 1   | 1   | 3 (None)                 |

When an interrupt is requested from a peripheral, the interrupt controller transfers the interrupt level based on the value set at the 2 bits of the ILRx corresponding to the interrupt to the CPU.

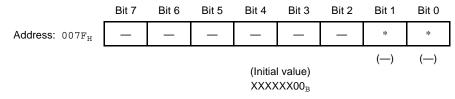

(b) Interrupt test register (ITR)

The ITR is used for testing. Do not access it.

#### (4) Description of operation

The functions of interrupt controllers are described below.

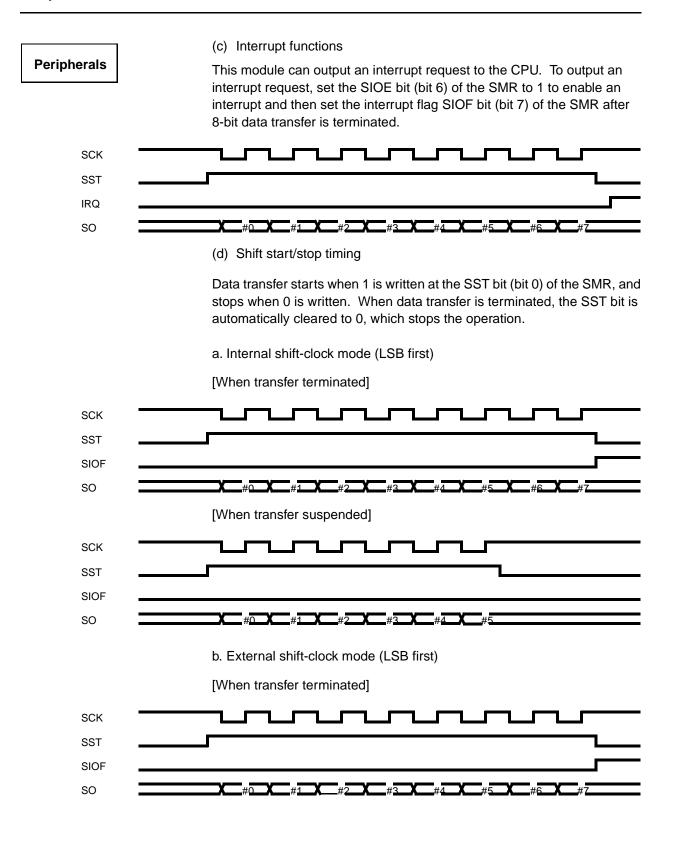

(a) Interrupt functions

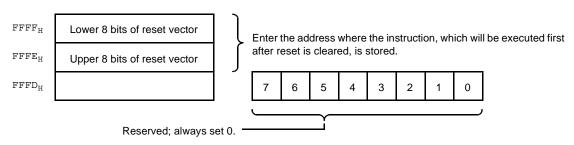

The MB89950 series of microcontrollers have 7 inputs for interrupt requests from the peripherals. The interrupt level is set by 2-bit registers corresponding to each input. When an interrupt is requested from a peripheral, the interrupt controller receives it and transfers the contents of the corresponding level register to the CPU. The interrupt to the device is processed as follows:

- (1) An interrupt source is generated inside a peripheral.

- (2) If an interrupt is enabled after referring to the interrupt-enable bit inside the peripheral, an interrupt request is output from the peripheral to the interrupt controller.

- (3) After receiving this interrupt request, the interrupt controller determines the priority of simultaneously-requested interrupts and then transfers the interrupt level for the applicable interrupt to the CPU.

- (4) The CPU compares the interrupt level requested from the interrupt controller with the IL bit in the processor status register.

- (5) As a result of the comparison, if the interrupt level has priority over the current interrupt processing level, the contents of the I-flag in the same processor status register are checked.

- (6) As a result of the check in step (5), if the I-flag is enabled for an interrupt, the contents of the IL bit are set to the required level. As soon as the currently-executing instruction is terminated, the CPU performs the interrupt processing and transfers control to the interrupt-processing routine.

- (7) When an interrupt source is cleared by software in the user's interrupt processing routine, the CPU terminates the interrupt processing.

Fig. 2.7 outlines the interrupt operation for the MB89950 series of microcontrollers.

Internal bus

Fig. 2.7 Interrupt-processing Flowchart

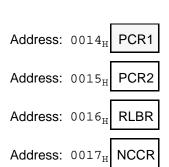

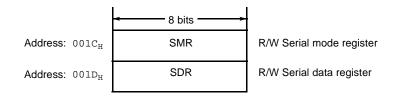

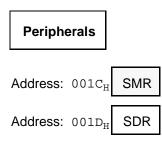

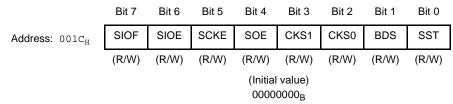

Peripherals

#### 2.2 Peripherals

#### 2.2.1 I/O Ports

- The MB89950 series of microcontrollers have five parallel ports (33 pins). Ports 0 and 1 serve as 8-bit I/O ports; port 2 serves 6-bit I/O port; port 3 serves as 4-bit I/O ports; port 4 serves as 7-bit I/O port.

- Ports 0, 1, 2, 3 and 4 are also used as peripherals.

- (1) List of port functions

| Pin    | Input Type | Output<br>Type | Function                        | bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2        | bit 1 | bit 0 |

|--------|------------|----------------|---------------------------------|-------|-------|-------|-------|-------|--------------|-------|-------|

| P00 to | CMOS       | N-ch           | Parallel port 0                 | P07   | P06   | P05   | P04   | P03   | P02          | P01   | P00   |

| P07    |            | open drain     | Segment output                  | SEG 2 | 27 —— |       |       |       |              | —— S  | SEG20 |

| P10 to | CMOS       | N-ch           | Parallel port 1                 | P17   | P16   | P15   | P14   | P13   | P12          | P11   | P10   |

| P17    |            | open drain     | Segment port 1                  | SEG 3 | 35 —— |       |       |       |              | s     | SEG28 |

| P20 to | CMOS       | N-ch           | Parallel port 2                 | _     |       | P25   | P24   | P23   | P22          | P21   | P20   |

| P25    |            | open drain     |                                 | —     |       | SEG4  | 1 ——  |       |              | —— S  | EG36  |

| P30 to | CMOS       | N-ch           | Parallel port 3                 | —     |       | _     |       | P33   | P32          | P31   | P30   |

| P33    |            | open drain     | LCD voltage                     | —     |       | _     | _     | V2    | V1           |       |       |

| P40 to | CMOS       | CMOS           | Parallel port 4                 | —     | P46   | P45   | P44   | P43   | P42          | P41   | P40   |

| P45    | Hysteresis | push-pull      | Timer serial/external interrupt | —     | INT0  | SCK   | SO    | SI    | PWC<br>/INT1 | PWM   |       |

Table 2–5 List of Port Functions

#### (2) Register list

I/O port consists of the following registers.

|                     | ≺8 bits ─> |                                  |                                       |

|---------------------|------------|----------------------------------|---------------------------------------|

| Address: $0000_{H}$ | PDR0       | R/W Port 0 data register         | Initial value = 11111111 <sub>B</sub> |

| Address: $0002_{H}$ | PDR1       | R/W Port 1 data register         | Initial value = 11111111 <sub>B</sub> |

| Address: $0004_{H}$ | PDR2       | R/W Port 2 data register         | Initial value = 11111111 <sub>B</sub> |

| Address: $000C_{H}$ | PDR3       | R/W Port 3 data register         | Initial value = 11111111 <sub>B</sub> |

| Address: $000E_{H}$ | PDR4       | R/W Port 4 data register         | Initial value = XXXXXXXX <sub>B</sub> |

| Address: $000F_{H}$ | DDR4       | W Port 4 data direction register | Initial value = X0000000 <sub>B</sub> |

Peripherals

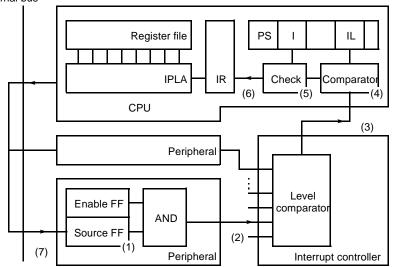

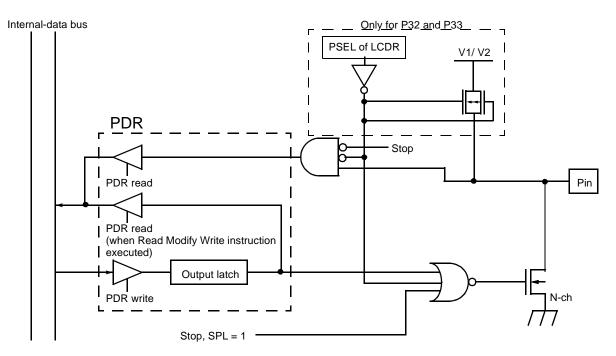

#### (3) Description of functions

The function of each port is described below.

- P00 to P07: N-ch open-drain type input/output ports (also used as segment output) P10 to P17: N-ch open-drain type input/output ports

- (also used as segment output)

- P20 to P25: N-ch open-drain type input/output ports (also used as segment output)

- Operation for output port The value written at the PDR is output to the pin. When the PDR is read, usually, the value of the pin is read instead of the contents of the output.

usually, the value of the pin is read instead of the contents of the output latch. However, when the Read Modify Write instruction is executed, the contents of the output latch are read. Therefore, the bit-processing instruction can be used even if input and output are mixed with each other.

• Operation for input port

When using these ports as input ports, set 1 at the PDR and turn the output transistor off. The value of the pin can always be read when the PDR is read. When the segment output is selected by the LCD controller port/segment select bit, the input data is always read as 0.

- Operation for segment output When using these ports as segment outputs, the segment output must be selected by the mask option. When segment output is selected using the LCD controller port/segment select bit, these ports can be used as segment outputs.

- State at reset

At reset, these ports serve as port inputs. The PDR is initialized to 1 and the output transistor is turned off at all bits.

• State in stop mode

For segment output, the output state when the CPU enters the stop mode is held. For port output, the pins states in stop mode are controlled by SPL bit in standby control register (STBC).

When SPL=0, pin states before entering stop mode are held. When SPL=1, port pins go high impedance in stop mode. FUJITSU

Peripherals

Fig. 2.8 Ports 0, 1 and 2

Note: Selection of segment output using the mask option is available only for mass-produced products. The mask option must be consistent with LCD segment output select register (SEGR).

Peripherals

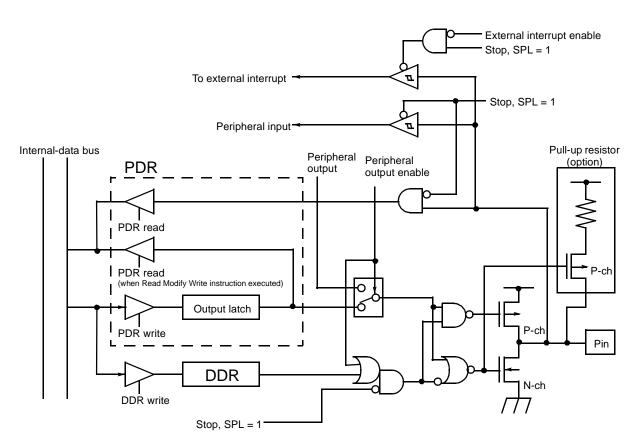

P30, P31: N-ch open-drain output, CMOS input

P32, P33: N-ch open-drain type input/output ports (also used as LCD controller power supply V1,V2)

• Operation for output port

The value written at the PDR is output to the pin. When the PDR is read, usually, the value of the pin is read instead of the contents of the output latch. However, when the Read Modify Write instruction is executed, the contents of the output latch are read. Therefore, the bit-processing instruction can be used even if input and output are mixed with each other.

- Operation for input port

When using these ports as input ports, set 1 at the PDR and turn the output transistor off. The value of the pin can always be read when the PDR is read. When V1/V2 is selected by PSEL bit of LCDR, the input data is always read as 0.

- Operation for V1 and V2 The PSEL bit in LCDR (see page 2-60) must be cleared in order to choose P32/P33 as LCD controller power supply.

- State at reset

At reset, these ports serve as LCD controller power supply. The PDR is initialized to 1 and the output transistor is turned off at all bits. Since PSEL bit of LCDR will be reset to zero (see page 2-60), therefore P32/P33 will be configured to V1/V2 right after reset.

• State in stop mode

If P32/P33 is chosen as V1/V2 and stop mode is triggered, the voltage at those pins before stop mode will be held. For port output, the pins states in stop mode are controlled by SPL bit in standby control register (STBC).

When SPL=0, pin states before entering stop mode are held. When SPL=1, port pins go high impedance in stop mode. FUĴĨTSU

Fig. 2.9 Port 3

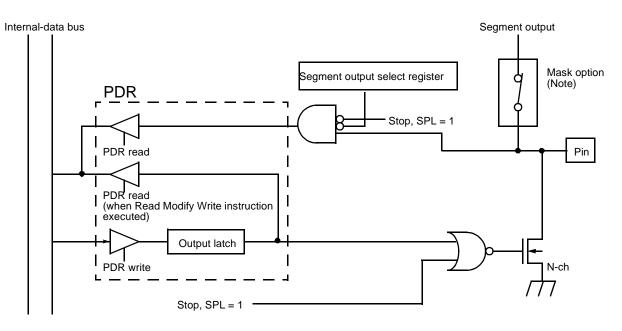

- P40 to P46: CMOS type I/O ports (also used as peripheral input and output)

- Switching input and output

This port has a data-direction register (DDR) and a port-data register

(PDR) for each bit. Input and output can be set independently for each

bit. The pin with the DDR set to 1 is set to output, and the pin with the

DDR set to 0 is set to input. When the peripheral output bit is enabled,

these ports are set to output irrespective of the DDR setting conditions.

- Operation for output port (DDR = 1)

The value written at the PDR is output to the pin where the DDR is set to 1. When the PDR is read, usually, the value of the pin is read instead of the contents of the output latch. However, when the Read Modify Write instruction is executed, the contents of the output latch are read irrespective of the DDR setting conditions. Therefore, the bit-processing instruction can be used even if input and output are mixed with each other. When data is written to the PDR, the written data is held in the output latch irrespective of the DDR setting conditions.

- Operation for input port (DDR = 0)

When used as the input port, the output impedance goes High.

Therefore, when the PDR is read, the value of the pin is read.

- Peripheral output operation

When using as the peripheral output, setting is performed by the peripheral output enable bit (See the description of each peripheral). The peripheral output enable bit has priority in switching input and output. Even if the output from each peripheral is enabled, the read value of the port is effective, so the peripheral output value can be checked.

• Peripheral input operation

The pin value at a port with the peripheral input function is always input for the peripheral input irrespective of the setting of the DDR and peripheral. Set the DDR to input when using an external signal for the peripheral input.

• State when reset

When reset, the DDR is initialized to 0 and the output impedance goes High at all bits. When reset, the PDR is not initialized. Therefore, set the value of the PDR before setting the DDR to output.

• State in stop mode With the SPL bit of the standby-control register set to 1, the output impedance goes High in stop mode irrespective of the value of the DDR.

FU rsu

Fig. 2.10 Port 4

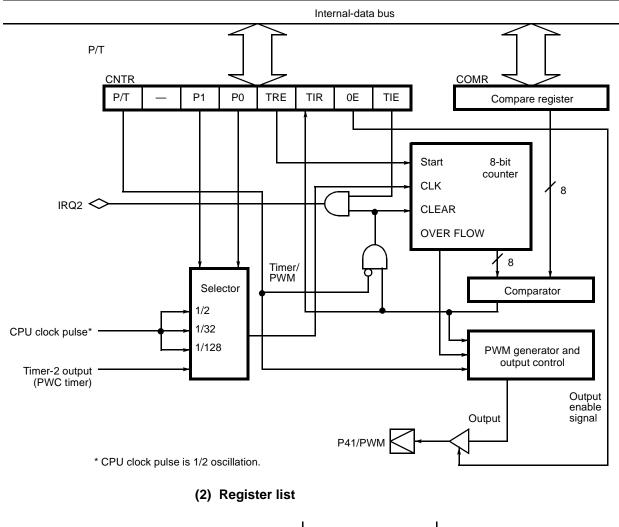

# 2.2.2 8-bit PWM Timer (Timer 1)

- This timer can be used as an 8-bit timer or PWM control circuit with 8-bit resolution.

- Four kinds of clock frequency can be selected.

# (1) Block diagram

# FUĴÎTSU

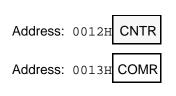

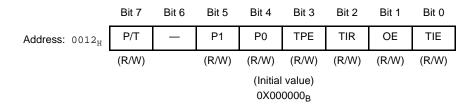

# (3) Description of registers

(a) Control register (CNTR)

[Bit 7] P/T: Timer/PWM operation mode switching bit

The operation is performed as the timer when bit 7 is set to 0, and as the

| 0 | Timer               |

|---|---------------------|

| 1 | PWM control circuit |

When switching, set channel to stop counting (TPE = 0), interrupt disabled (TIE = 0) and interrupt request flag cleared (TIR = 0).

[Bits 5 and 4] P1 and P0: Clock-pulse select bits

Clock pulses from the prescaler or WT0 output of timer 2 (pulse-width count timer) can be selected using P1 and P0.

| P1 | P0 | Clock cycle                                |

|----|----|--------------------------------------------|

| 0  | 0  | Internal clock pulse 1 instruction cycle   |

| 0  | 1  | Internal clock pulse 16 instruction cycles |

| 1  | 0  | Internal clock pulse 64 instruction cycles |

| 1  | 1  | Timer 2 cycle                              |

Note that these bits must not be rewritten when the counter is operating (TPE = 1).

[Bit 3] TPE: Counting enable bit

When these bits are set to 1, the timer or PWM control circuit starts operation.

| 0 | Stops counting  |

|---|-----------------|

| 1 | Starts counting |

[Bit 2] TIR1: PWM channel interrupt request flag bit

Bit 2 goes to 1 when an interrupt source occurs. To clear the generated interrupt source, write 0 at this bit. The meaning of bit to be read is as follows:

| 0 | Values of counter and COMR do not match. |  |

|---|------------------------------------------|--|

| 1 | Values of counter and COMR match.        |  |

Note that 1 is always read when the Read Modify Write instruction is executed.

The meaning of each bit to be written is as follows:

| 0 | Clears this bit                                |

|---|------------------------------------------------|

| 1 | Does not change this bit nor affect other bits |

Note: In the PWM operation mode, neither the read nor write values of these bits have any meaning.

[Bit 1] OE: Output signal control bit

When bit 1 is 1, the port serves as the PWM timer output. In the timer operation mode, a signal that is reversed each time the values of the counter and the compare register match is output. In the PWM operation mode, a PWM signal is output.

| 0 | General-purpose ports (P41)   |

|---|-------------------------------|

| 1 | Counter/PWM output pins (PWM) |

Even if the DDR of P41 is set for input (bit 1 of DDR4 is set to 1), when this bit is 1, it serves as the counter/PWM output pin.

[Bit 0] TIE: Interrupt enable bit (Timer mode)

If bit 0 is set to 1, an interrupt occurs when the values of the counter and the compare register match.

| 0 | Disables counter interrupt output |

|---|-----------------------------------|

| 1 | Enables counter interrupt output  |

However, in the PWM operation mode, an interrupt does not occur irrespective of the value of this bits.

| Address: | 0012н | CNTR |

|----------|-------|------|

| Address: | 0013H | COMR |

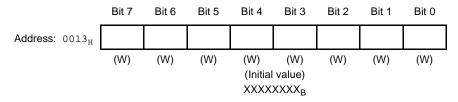

#### (b) Compare register (COMR)

This register holds the value to be compared with the counter value in the timer operation mode, and also clears the counter when the value agrees with the counter value. In the PWM operation mode, the High pulse width can be specified by this register value.

### (4) Description of operation

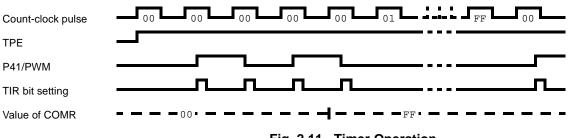

#### (a) Timer function

Setting the P/TX bit of the CNTR to 0 gives the timer-operation mode. When the TPE bit of the CNTR is set to 1, the counter starts incrementing from  $00_{\rm H}$ . When the value of the counter agrees with that of the COMR, the counter is cleared on the next count clock pulse and incrementing restarts. Therefore, the TIR bits are set and the output pin is reversed (but, when the TPE bit is 0, the output pin is fixed at Low level) in cycles of the count clock pulses when  $00_{\rm H}$  is written at the COMR, or in cycles 256 times longer than those of the count clock pulses when  ${\rm FF}_{\rm H}$  is written.

If the value of the COMR is rewritten in the timer-operation mode, it becomes effective from the next cycle (when the value of the counter is  $00_{\rm H}$ , the value of the COMR is transferred to the comparator latch).

Fig. 2.11 Timer Operation

If the TIE bit of the CNTR is set to 1, an interrupt occurs when the values of the counter and COMR match. During interrupt processing, the TIR bit is used as the interrupt flag. The TIR bit is set irrespective of the value of the TIE bit. However, if the values of the counter and COMR match, the TIR bit is set to 1 even after an interrupt is disabled.

Writing 0 at the TIR bit permits clearing of the interrupt source or the TIR bit. When the Read Modify Write instruction is read, the TIR bit is set so that 1 can always be read to prevent erroneous clearing.

By using P0 and P1 bit in CNTR, 1 out of 4 clock sources can be selected for the counter.

# FUJITSU

# Peripherals

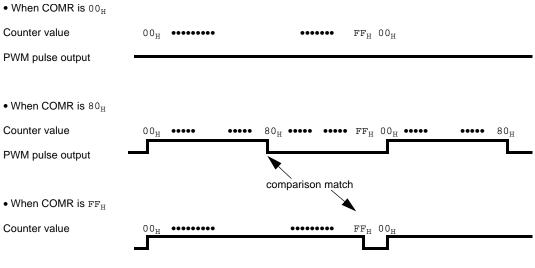

#### (b) PWM operation

Setting the P/TX bit of the CNTR to 1 gives the PWM operation mode. The COMR specifies the duty of the output pulse. Pulses can be output with 1/256 resolution and a duty of 0% to 99.6%.

When  $0 (00_H)$  is written at the COMR, the duty of the PWM output pulse is 0%; when 128 ( $80_H$ ) is written, the duty is 50%, and when 255 (FF<sub>H</sub>) is written, it is 99.6%.

The value of COMR is transferred to the comparator latch when the value of the counter is  $00_{\rm H}$ . If the value of the COMR is rewritten in the PWM operation mode, it becomes effective from the next cycle.

At starting (counter = 00), output is high. When the counter matches the compare register, output goes low.

Fig. 2.12 PWM Pulse Output

In the PWM operation mode, the values at the TIR bit of the CNTR have no meaning. No interruption occurs even if the TIE bit are 1.

The cycle of the PWM pulse can be changed by switching the count clock pulse.

The count clock pulse can be selected from three clock pulses of the prescaler and the clock pulse of the internal timer by the clock pulse select bits P1 and P0 of the CNTR.

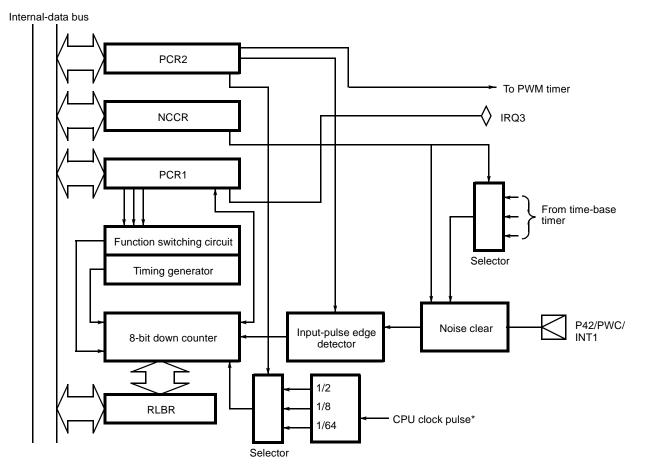

# 2.2.3 Pulse-width Count Timer (Timer 2)

- This timer has timer and pulse-width measurement functions.

- The timer function has two modes: reload timer and one-shot.

- In the reload timer mode, the set values are counted down repeatedly.

- In the one-shot mode, counting down is started from the set values and stops at the first underflow.

- The pulse-width measurement function enables measurement of High, Low, or one-cycle widths of pulses input from pins.

- For inputting from pins, the 5-bit noise-clearing circuit is selectable.

- (1) Block diagram

\* The CPU clock pulse is an oscillation-divided pulse.

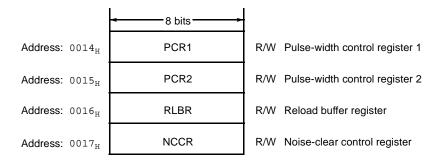

#### (2) Register list

#### (3) Description of registers

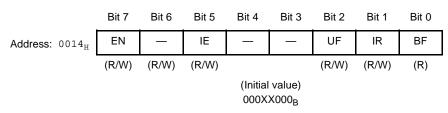

(a) Pulse-width control register 1 (PCR1)

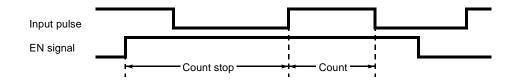

## [Bit 7] EN: Count enable bit

At the timer function, when 1 is written at this bit, the value of the data register is loaded to start counting down. When 0 is written, counting down stops. At the pulse-width measurement function, when 1 is written at this bit, the measurement-enable state is set. Under this condition, counting down is started when the edge of the measured pulse is detected. When 0 is written at this bit during measurement, counting down stops; the count is not transferred to the reload buffer register (RLBR).

|   | Timer function     | Pulse-width measurement function     |

|---|--------------------|--------------------------------------|

| 0 | Count disable      | Pulse-width measurement stop/disable |

| 1 | Count enable/start | Pulse-width measurement enable/start |

[Bit 5] IE: Interrupt request enable bit

When bit 5 is 1, an interrupt request is output when the interrupt request flags (UF, IR, and BF) are set.

| 0 | Interrupt disabled |

|---|--------------------|

| 1 | Interrupt enabled  |

[Bit 2] UF: Underflow interrupt request bit

Bit 2 indicates whether the timer underflowed. The meaning of each bit to be read is as follows:

| 0 | No underflow       |

|---|--------------------|

| 1 | Underflow occurred |

1 is always read when the Read Modify Write instruction is executed.

The meaning of each bit to be written is as follows:

| 0 | Clears this bit                              |

|---|----------------------------------------------|

| 1 | Unchanges this bit and other bits unaffected |

[Bit 1] IR: Measurement-end interrupt request bit

When the IE bit (bit 5) of the PCR1 is 1, an interrupt occurs at the end of pulse-width measurement.

The meaning of each bit to be read is as follows:

| 0 | Pulse-width measurement not terminated |

|---|----------------------------------------|

| 1 | Pulse-width measurement terminated     |

1 is always read when the Read Modify Write instruction is executed.

The meaning of each bit to be written is as follows:

| 0 | Clears this bit                              |

|---|----------------------------------------------|

| 1 | Unchanges this bit and other bits unaffected |

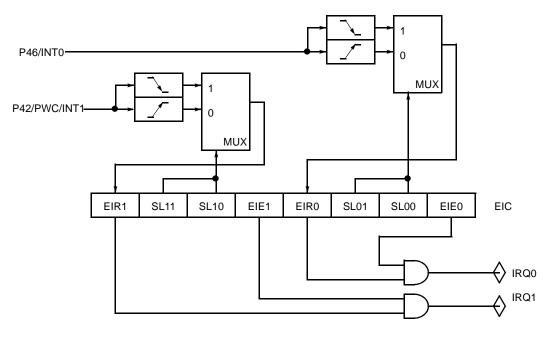

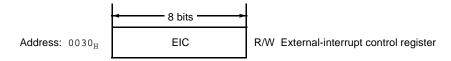

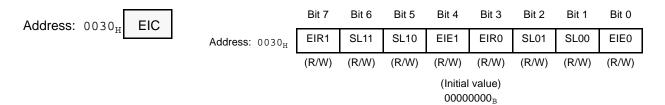

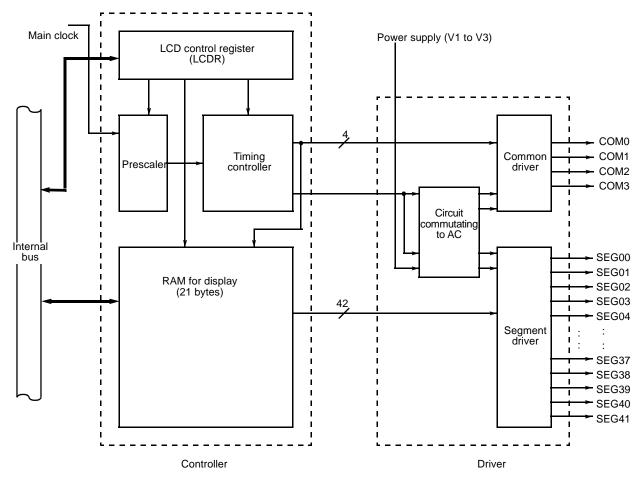

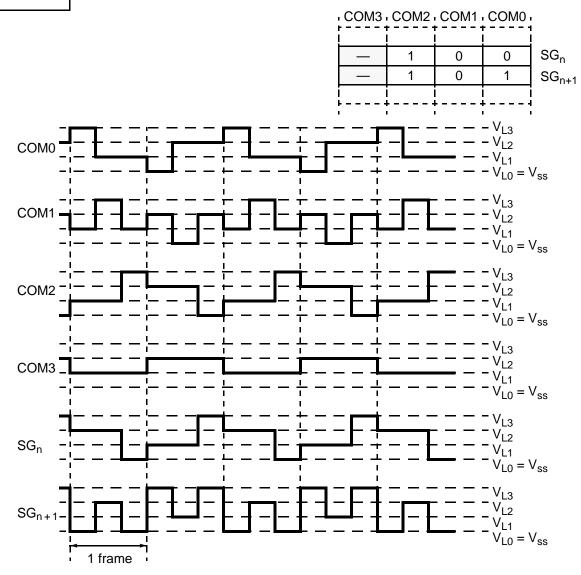

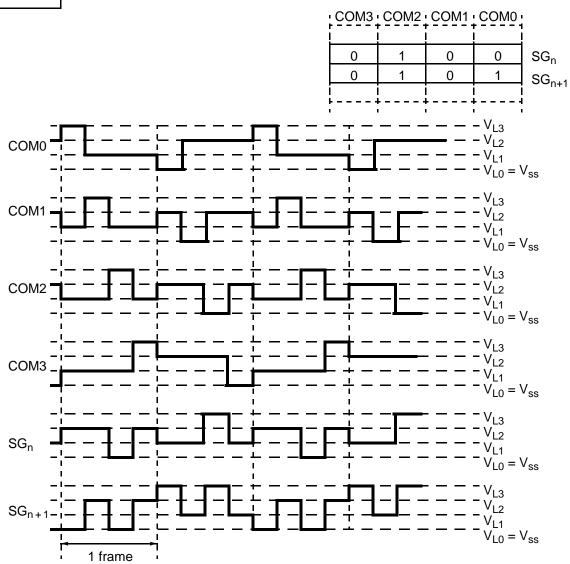

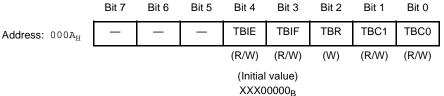

[Bit 0] BF: Buffer-full flag