# DMA08 DIRECT MEMORY ACCESS

**REFERENCE MANUAL**

# DMA08

Direct Memory Access Reference Manual

© Motorola, Inc., 1996; All Rights Reserved

Motorola reserves the right to make changes without further notice to any products herein to improve reliability, function, or design. Motorola does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part.

Motorola and the Motorola logo are registered trademarks of Motorola, Inc.

Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

# List of Sections

| Introduction                |

|-----------------------------|

| Overview and Features 21    |

| DMA Module Description      |

| DMA Transfers 35            |

| DMA Registers 49            |

| DMA Application Examples 67 |

| DMA Module 105              |

| DMA08 Version B 109         |

| Glossary 111                |

| Index                       |

# List of Sections

All M68HC08 microcontrollers are modular, customer-specified designs. To meet customer requirements, Motorola is constantly designing new modules and creating new versions of existing modules.

The *DMA08 Reference Manual* introduces version A of the DMA08, the direct memory access (DMA) of the Motorola HC08 Family. Version B is described in Appendix A. Information concerning future versions of the DMA08 will be included in appendices in later versions of the reference manual.

### **Revision History**

This table summarizes differences between this revision and the previous revision of this reference manual.

| Previous<br>Revision | Original Release                  |

|----------------------|-----------------------------------|

| Current<br>Revision  | 1.0                               |

| Date                 | 08/96                             |

| Changes              | Format and organizational changes |

| Location             | Throughout                        |

# **Table of Contents**

### Introduction

| Contents         | <br> | <br>17 |

|------------------|------|--------|

| Introduction     | <br> | <br>   |

| The DMA08 Module | <br> | <br>   |

#### **Overview and Features**

| Contents     |  |

|--------------|--|

| Introduction |  |

| Features     |  |

### DMA Module Description

| Contents                              |

|---------------------------------------|

| Introduction                          |

| Source and Destination Base Addresses |

| Address Extension Module              |

| Byte Count                            |

| Block Length                          |

| Arithmetic Logic Unit (ALU)           |

| DMA Control and Status                |

| Memory Stretch                        |

| Low-Power Modes                       |

| Wait Mode                             |

| Breakpoints                           |

| DMA in Expanded Mode                  |

|                                       |

### **DMA** Transfers

| Contents                                            |

|-----------------------------------------------------|

| DMA Operation                                       |

| Transfer Types                                      |

| Cycle-By-Cycle Operation                            |

| Byte Transfers                                      |

| DMA Activity During a Byte Transfer41               |

| Word Transfers                                      |

| DMA Activity During a Word Transfer                 |

| DMA Transfer Latency                                |

| Example of the DMA Transfer Programming Procedure44 |

| Address Calculation                                 |

| Bandwidth Control                                   |

### **DMA Registers**

# DMA Application Examples

| Contents                                            | 67              |

|-----------------------------------------------------|-----------------|

| Introduction                                        | <mark>68</mark> |

| Software-Initiated Block Transfer                   | 69              |

| B – Flexible, Large Block Transfer                  |                 |

| DMA Service of Serial Communications                | 73              |

| A – Transmitting a Buffered Message Using the CPU   | 74              |

| B – Servicing the SCI Transmitter Using the DMA     | 75              |

| Summary                                             | 76              |

| DMA Timer Servicing                                 | 77              |

| A – Generating a Pseudo Buffered PWM                | 77              |

| B – Buffering Input Captures for Period Calculation | 81              |

| Summary                                             | 83              |

| Full Assembler Listings                             | 84              |

| Listing 1 – Fixed Block Length Transfer             | 84              |

| Listing 2 – Variable Block Length Transfer          | 86              |

| Listing 3 – SCI Transmitter                         | 90              |

| Listing 4 – SCI Transmitter                         | 92              |

| Listing 5 – Timer Output Compare                    | 94              |

| Listing 6 – PWM Generation                          | 96              |

| Listing 7 – Timer Input Capture                     |                 |

| Listing 8 – Period Measurement1                     | 01              |

#### **DMA Module**

| Contents                                    | 105 |

|---------------------------------------------|-----|

| Introduction                                | 106 |

| 708XL36 DMA Registers                       | 107 |

| 708XL36 DMA Transfer Source Mapping         | 108 |

| 708XL36 Peripheral Interrupt Prioritization | 108 |

| DMA08 Version B |  |  |

|-----------------|--|--|

| DMA Version B   |  |  |

| Glossary        |  |  |

| Index           |  |  |

| Index           |  |  |

# List of Figures

| Figure | Title                                                                                         | Page     |

|--------|-----------------------------------------------------------------------------------------------|----------|

| 1      | Simplified Block Diagram of a System with DMA                                                 | 18       |

| 2      | Diagram of the MC68HC708XL36 Layout                                                           | 20       |

| 3      | DMA Module Functional Block Diagram                                                           | 22       |

| 4      | DMA Module Functional Block Diagram                                                           | 26       |

| 5      | Address Extension Registers                                                                   | 28       |

| 6      | DMA Operation                                                                                 | 30       |

| 7      | DMA Operation                                                                                 | 36       |

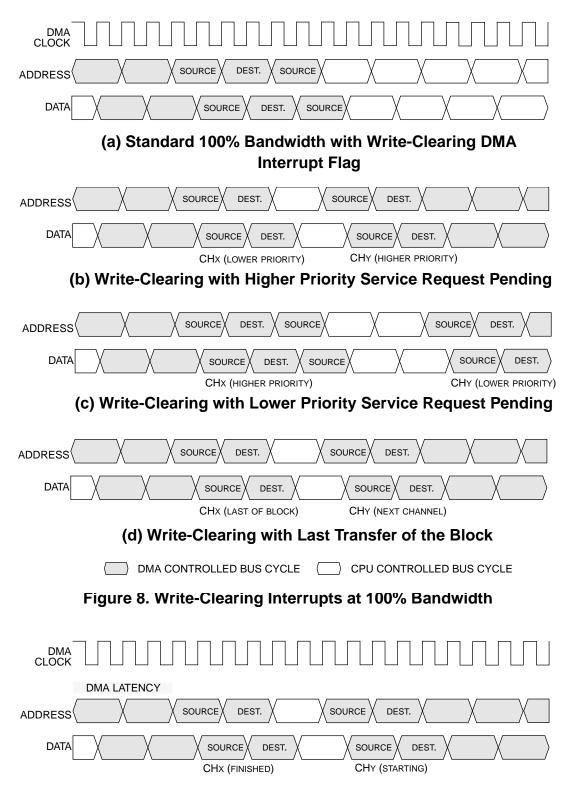

| 8      | Write-Clearing Interrupts at 100% Bandwidth                                                   | 39       |

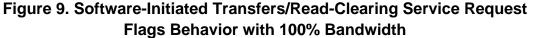

| 9      | Software-Initiated Transfers/Read-Clearing<br>Service Request Flags Behavior with 100% Bandwi | idth .39 |

| 10     | MCU Bus Activity During a DMA Byte Transfer                                                   | 40       |

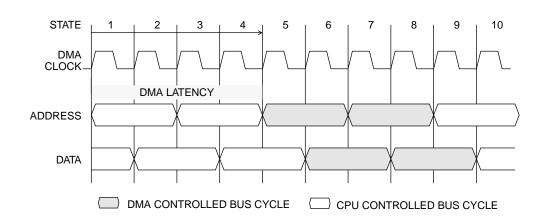

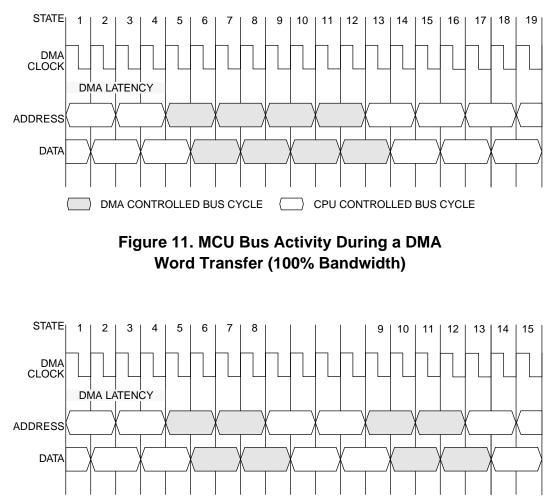

| 11     | MCU Bus Activity During a DMA<br>Word Transfer (100% Bandwidth)                               | 42       |

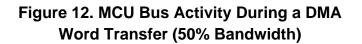

| 12     | MCU Bus Activity During a DMA<br>Word Transfer (50% Bandwidth)                                | 42       |

| 13     | DMA and CPU Use of the IBUS                                                                   | 47       |

| 14     | DMA Control Register (DC1)                                                                    | 52       |

| 15     | DMA Status and Control Register (DSC)                                                         | 54       |

| 16     | DMA Control Register 2 (DC2)                                                                  | 57       |

| 17     | DMA Channel Control Register (D0C)                                                            | 59       |

| 18     | DMA Source Base Address Registers (D0SH and D0S                                               | L)62     |

| 19     | DMA Destination Base Address<br>Registers (D0DH and D0DL)                                     | 63       |

| 20     | DMA Block Length Register (D0BL)                                                              | 64       |

| 21     | DMA Byte Count Register (D0BC)                                                                | 65       |

| Figure | Title                               | Page |

|--------|-------------------------------------|------|

| 22     | Minimum PWM High Time               | 80   |

| 23     | Diagram of the MC68HC708XL36 Layout | 106  |

| 24     | MCU Bus Activity During DMA Byte    |      |

|        | and Word Transfers (50% Bandwidth)  | 110  |

# List of Tables

| Table | Title                                                   | Page |

|-------|---------------------------------------------------------|------|

| 1     | Byte Transfer Activity                                  | 41   |

| 2     | Word Transfer Activity                                  | 43   |

| 3     | DMA/CPU Bus Bandwidth Sharing                           | 47   |

| 4     | DMA Transfer Source Selection                           | 57   |

| 5     | DMA Channel Control Register                            | 59   |

| 6     | DMA Word Transfer                                       | 61   |

| 7     | Relative Performance in Two Block Transfer Methods      | 70   |

| 8     | Relative Performance in Two Block Transfer Methods      | 72   |

| 9     | Relative Performance in DMA<br>and CPU Transfer Methods | 76   |

| 10    | MC68HC708XL36 DMA Registers                             | 107  |

| 11    | DTS Bits                                                | 108  |

| 12    | MC68HC708XL36 Peripheral<br>Interrupt Prioritization    | 108  |

| 13    | DMA/CPU Bus Bandwidth<br>Sharing (DMA08 Version B)      | 109  |

# List of Tables

# Introduction

| Introduction       | <br> | <br>1 | 7  |

|--------------------|------|-------|----|

| The DMA08 Module . | <br> | <br>  | 20 |

#### Introduction

Direct memory access (DMA) is a method of data transfer whereby large amounts of information may be stored in and retrieved from memory and/or buffers without the need for central processing unit (CPU) intervention. This method is the first example of coprocessing associated with the HC08 Family; the technique traditionally has been used in large, complex, multi-chip computer systems to move blocks of data around the system. Its use in single-chip and embedded control systems is a more recent development brought about by the demands for higher performance and ever increasing integration of functions onto a single silicon chip. The on-chip M68HC08 DMA module (DMA08) takes two bus cycles to transfer a byte of data and four bus cycles to transfer a 16-bit word.

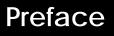

Figure 1. Simplified Block Diagram of a System with DMA

While the use of DMA techniques was relatively obvious and straightforward when large amounts of memory were involved, the usefulness of DMA in an M68HC08 application is, perhaps, less clear. The DMA exists principally because it works with whole blocks of data, rather than on a byte-by-byte basis. CPU intervention is, therefore, only required at block boundaries and not at the end of each byte transfer, thus providing fast, low-latency servicing of peripheral functions, such as serial communications interface (SCI) transmit data, serial peripheral interface (SPI) receive data, etc.

For example: It is highly advantageous (in terms of response time and software size and complexity) to be able to continually write data to an SPI communications module with minimal CPU involvement. This approach can be taken with many peripheral functions, for example, servicing SPI and SCI modules and supporting a timer with data required for input capture and output compare functions. The DMA module also may be used simply to move blocks of memory around, as in the traditional high-end use (including reordering data). Or it can replace a CPU interrupt if the service routine is purely a data transfer, that is, when no data manipulation is involved.

Whether software- or interrupt-driven, data input or output requires considerable CPU involvement. For example, when data is required by a peripheral function, the CPU must first fetch the data from memory and

then write it to the appropriate location. Conversely, when a peripheral signals that it has data to transfer, the CPU must stop what it is doing, read the data and store it at the correct address. The following tasks contribute to the CPU interrupt overhead (limiting the overall transfer rate between the CPU and the peripheral):

- Stacking and unstacking CPU registers

- Loading interrupt vectors

- Loading address pointers

- Reading/writing transfer data

- Incrementing address pointers

- Storing address pointers

- Clearing interrupt flags

- Returning from interrupt

The normal CPU interrupt overhead is 16 cycles. The term "latency" is used to describe the delay between the request for an action and the action's actual start. The DMA operates with a much lower latency than the CPU and, therefore, can improve system performance.

For a DMA transfer to occur within a system, the DMA subsystem must take control of the system bus, thus temporarily replacing the CPU as the bus master. In general terms, there are two basic methods of DMA operation: cycle stealing and CPU halt. By halting CPU execution, the DMA has access to the system buses all of the time and, therefore, will be able to transfer the data in the minimum time (at the expense of any CPU tasks). In most situations, this method is only really practicable for transferring small amounts of data. For larger amounts of data, however, the DMA can be allocated a proportion of the bus bandwidth. This means that both DMA and CPU effectively process data concurrently by sharing their use of the bus. The overall DMA transfer rate is thereby reduced, but CPU tasks continue to progress.

By using the DMA to move data, the load on the CPU is reduced, as is the amount of executable code required for each move, thus giving faster response times and more efficient use of the available program memory space.

#### The DMA08 Module

The DMA08 is a coprocessor module for the M68HC08 that can take control of the system address and data buses at any bus cycle boundary. It is designed to allow the transfer of data between any two CPU addressable locations with a minimum of latency. Normal interrupt latency is nine bus cycles, with a total overhead of 16 bus cycles. DMA transfers (when enabled) can have a latency of only two cycles.

The DMA implementation on the M68HC08 is based on a modular approach: One or more independent DMA channels may be provided in a given hardware implementation. Data transfer may be either interruptor software-driven.

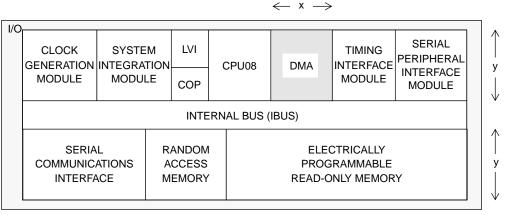

The modular design approach means that it is an easy matter to expand the DMA from one to seven channels. **Figure 2** shows the layout of the 708XL36 die and illustrates the common module height and its advantages. The 708XL36 has three DMA channels; more could be added by expanding the DMA module horizontally.

| D |                                                            | I                     |     |                                                  |     | 1                   |                                   |

|---|------------------------------------------------------------|-----------------------|-----|--------------------------------------------------|-----|---------------------|-----------------------------------|

|   | CLOCK<br>GENERATION                                        | SYSTEM<br>INTEGRATIOI |     | CPU08                                            | DMA | TIMING<br>INTERFACE | SERIAL<br>PERIPHERAL<br>INTERFACE |

|   | MODULE                                                     | MODULE                | COP |                                                  |     | MODULE              | MODULE                            |

|   | INTERNAL BUS (IBUS)                                        |                       |     |                                                  |     |                     |                                   |

|   | SERIAL RANDOM<br>COMMUNICATIONS ACCESS<br>INTERFACE MEMORY |                       |     | ELECTRICALLY<br>PROGRAMMABLE<br>READ-ONLY MEMORY |     |                     |                                   |

Note: 'x' indicates the direction in which the modules may be expanded; 'y' is the standard module height

#### Figure 2. Diagram of the MC68HC708XL36 Layout

# **Overview and Features**

#### Contents

|          | <br> |

|----------|------|

| Features | <br> |

#### Introduction

The M68HC08 direct memory access module (DMA08) is constructed in a modular fashion to ensure flexibility and ease of use, while shortening the design effort required each time a DMA module is specified for a new device. From one to seven DMA channels may be specified for a particular implementation; each channel is independent and is enabled only when required. If the DMA module is not enabled or is enabled but not active, it does not consume bus cycles.

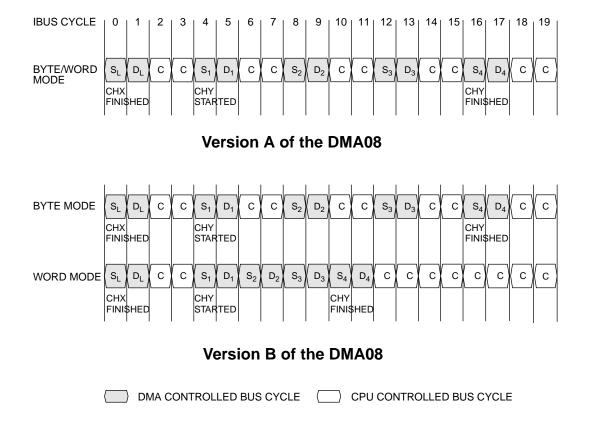

There are two versions of the DMA08 module. Version A, implemented in the MC68HC708XL36, is described in the main body of this book. Version B of the DMA08 operates differently in word mode. Version B is described in DMA08 Version B on page 109.

In this manual, the modular nature of the DMA is exploited and only one channel (channel 0) is discussed in detail. For information on precise register addresses, bit names and positions and channel assignments, refer to the specific device's data sheet.

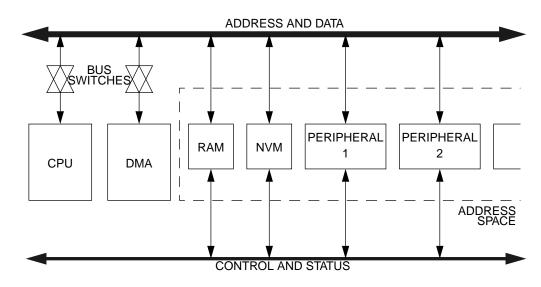

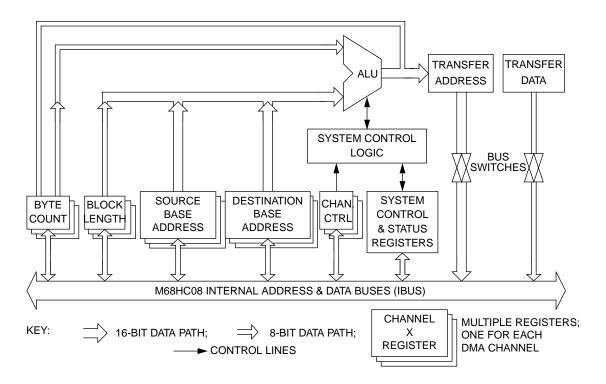

**Figure 3** is a simplified representation of the DMA module, showing its functional blocks as perceived by the user. The system control logic enables the DMA to select the set of registers for the DMA channel required, controls the incrementing or decrementing of source and destination addresses and controls the movement of data within the DMA module.

Figure 3. DMA Module Functional Block Diagram

#### Features

The following are features of the DMA08:

- Modular and Expandable Architecture; Up to Seven Independent Channels with Eight Transfer Source Inputs May Be Specified

- Interrupt-Driven Operation Without CPU Intervention

- Data Transfer Rates of up to 4 Mbytes/sec (8 MHz bus); One Byte Transferred Every Two Bus Cycles

- Low Latency for Data Moves (Two Cycles)

- Separate 16-Bit Source and Destination Addresses

- Byte or Word Transfer Capability

- Single Block or Loop (Repeated Block) Transfer Options

- Programmable Block Length, up to 256 Bytes

- Optional CPU Interrupt Request on Completion of Block Transfer or on Loop Restart

- Programmable DMA Bus Bandwidth. 25, 50, 67, or 100% of Total Bus Bandwidth Can Be Allocated to the DMA Module

- Programmable DMA Transfer Priority, DMA Transfers Can Either Take Priority Over CPU Interrupts, or CPU Interrupts Can Halt the DMA transfer

- Arbitration of Priorities in Multichannel Implementation

- Automatic Peripheral Flag Clearing During DMA Transfer Mode

- Programmable DMA Enable During Wait Mode

- Memory Stretch Capability For Interfacing to Slow Memory

- Built-in Support for Optional Memory Address Extension Module, Allowing the DMA to Access up to 16 M Address Space

- Breakpoint Feature Capable of Halting DMA Operation

# **DMA Module Description**

### Contents

| Introduction                          |

|---------------------------------------|

| Source and Destination Base Addresses |

| Address Extension Module              |

| Byte Count                            |

| Block Length                          |

| Arithmetic Logic Unit (ALU)           |

| DMA Control and Status                |

| Memory Stretch                        |

| Low-Power Modes                       |

| Wait Mode                             |

| Stop Mode                             |

| Breakpoints                           |

| DMA in Expanded Mode                  |

#### Introduction

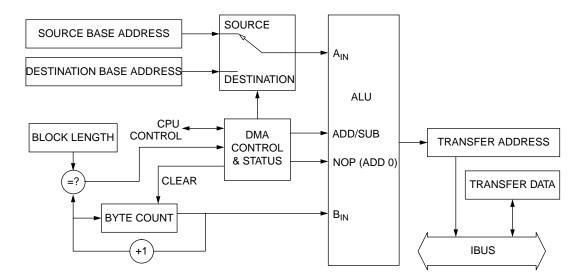

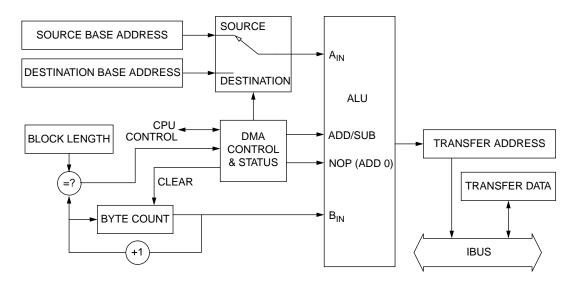

**Figure 4** shows a simplified representation of the DMA module from a user's perspective. As shown in **Figure 4**, all the registers may be both read and written by the CPU. The system control logic enables the DMA to select the set of registers for the required DMA channel, controls the incrementing or decrementing of source and destination addresses, and controls the movement of data within the DMA module. DMA access to the M68HC08 bus and the ratio of DMA to CPU cycles is also controlled.

The function of each of the blocks is discussed in the following paragraphs. How to program a DMA transfer is covered in DMA Transfers on page 35 and details of the registers are given in DMA Registers on page 49.

Figure 4. DMA Module Functional Block Diagram

#### Source and Destination Base Addresses

Each channel has a 16-bit source base and a 16-bit destination base address register. These registers are used to contain the *base of addresses* for the data transfer process. The CPU writes the desired addresses to these registers before the DMA transfer starts. Writing to any of these locations clears the byte count register.

The state of these registers on reset is undefined. See DMA Source Base Address Registers on page 62 and DMA Destination Base Address Registers on page 63 for details.

**NOTE:** Source base and destination base registers are unchanged by the transfer process. It is not advisable to write to these registers while transfers on the corresponding channel are enabled.

#### **Address Extension Module**

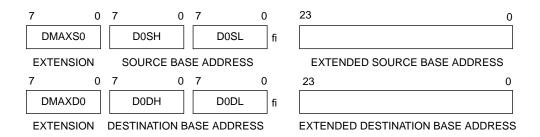

Support for this optional HC08 Family module is built into the DMA. By programming and using the 8-bit DMA source base and destination base extension registers provided in the address extension module (ADX), the DMA has the capability to access up to 16 M of address space. In the ADX module, each channel has a separate source base and destination base address extension register pair.

#### Figure 5. Address Extension Registers

When the address extension capability is used, the DMA addresses are formed by concatenating the source base (or destination base) address register and the relevant address extension register to form the complete address. The address extension register provides the most significant bits of the address. The DMA operation has no other change.

### **Byte Count**

The byte count register is usually written to by the arithmetic logic unit (ALU) of the DMA, although it is also accessible by the CPU. In normal operation, the ALU increments the byte count register after every byte that is transferred. See DMA Byte Count Register on page 65 for details.

This register is cleared:

- by reset

- at the end of a byte transfer, when its contents match those of the block length register

- when either the source base or destination base registers are written

- by writing zero to it

#### **Block Length**

The block length register is used to define the number of bytes to be moved in a particular transfer operation. Prior to the start of a transfer, the block length register should be written by the CPU.

When the content of the byte count register, which gets incremented by one with each byte transferred, matches that of the block length register, the current transfer is complete. Subsequent action depends on the state of the loop bit; either the transfer restarts or control reverts to the CPU.

The state of this register on reset is undefined. See DMA Block Length Register on page 64.

**NOTE:** A block length of zero results in a block transfer of 256 bytes.

Figure 6. DMA Operation

#### Arithmetic Logic Unit (ALU)

The ALU is used for calculation of the actual source and destination transfer addresses and for incrementing the byte count register. The ALU is a 16-bit subsystem and therefore can operate on the 16-bit source and destination address registers in a single cycle.

Under the direction of the system control logic, the DMA combines the content of the source (or destination) base address register with that of the byte count register to form a transfer source (or destination) address. This address is stored in the temporary address register and is output on the internal bus (IBUS) at the appropriate time.

#### **DMA Control and Status**

The operation of the DMA module is defined and monitored by two groups of registers: one group controls the entire DMA module and the other group is specific to the individual DMA channel. See DMA Module Registers on page 52 and DMA Channel Control Register on page 59 for details.

#### **Memory Stretch**

For slow, off-chip or on-chip peripherals that require extra bus cycles, the DMA can stretch the address phase of the bus cycle by an integer number of bus cycles. When this operation is required, a stretch signal is supplied to the DMA module for the number of bus cycles that the address needs to operate correctly.

#### **Low-Power Modes**

The CPU08 WAIT and STOP instructions put the MCU in low-power consumption standby modes. The effect on DMA operation is explained in the following paragraphs.

Wait Mode The DMA wait enable bit (DMAWE) controls the activity of the DMA in wait mode.

- DMAWE set. The DMA can execute a transfer during wait mode, whenever it receives a valid DMA service request. If a CPU WAIT instruction is executed during a transfer, the transfer will continue until completion.

- DMAWE clear. The DMA cannot respond to service requests in wait mode. If a CPU WAIT instruction is executed during a transfer, the transfer will be suspended and will resume when the processor exits wait mode.

- Stop ModeThe DMA module is inactive during stop mode. A STOP instruction<br/>suspends any DMA transfer in progress. If an external interrupt brings<br/>the MCU out of stop mode, the suspended DMA transfer resumes. If a<br/>reset brings the MCU out of stop mode, the transfer is aborted.

#### **Breakpoints**

If an address match occurs on a DMA address, then the BREAK state is not entered until the end of the current CPU instruction. Thus, a DMA transfer cannot be aborted due to a match on a DMA address comparison with one exception. A DMA transfer can be aborted if a DMA transfer is pending after the BREAK state has been entered from an address match on the previous CPU instruction.

#### **DMA in Expanded Mode**

The DMA can be used to access external resources. The control of access to these devices is normally done via an EBI (external bus interface) module. In general, if the CPU can address these external components, so can the DMA.

# **DMA** Transfers

### Contents

### **DMA** Operation

To transfer a byte of data, the DMA first uses the contents of the source base address register and the byte count register (according to the instructions in the control registers) to generate a transfer source address. The DMA then takes control of the IBUS to read a byte of data from the source location at the transfer source address into a temporary register in the DMA. The transfer destination address is then generated in the same manner and the data byte is written to this destination address.

**NOTE:** All DMA registers may be read from or written to at any time by the CPU or by the DMA module. Accessing these registers during a transfer can increase transfer latency. See DMA Transfer Latency on page 44.

Figure 7. DMA Operation

# **Transfer Types**

The DMA module supports two main types of transfer: hardware interrupt-driven and software-initiated.

Hardware interrupt-driven transfers may be initiated by one of the MCU peripheral subsystems, for example, SCI, SPI, timer, A/D, etc. In this type of transfer, one or more of the system's peripherals is configured to generate a request for DMA transfer. (This configuration is by means of a read/write bit in one of the peripheral's control registers.) The DMA service request is passed to the DMA channel, assuming that this transfer source has been allocated to the channel. The DMA module then arbitrates between the channels, where necessary, and begins the highest priority transfer by halting the CPU clocks and taking control of the IBUS. The relative channel priority increases as the DMA channel number decreases. This means that channel 0 has the highest priority. channel 1 the next highest, and so on. Depending on the state of the DMAP bit, CPU interrupts from other modules may be recognized within a block transfer and the transfer is suspended as a consequence. The transfer will then resume only if the transfer enable bit for the channel is set again. See DMA Status and Control Register on page 54 for further information on the operation of the DMAP bit.

Software-initiated transfers are similar in operation to those that are hardware interrupt-driven. The major difference is that software-initiated transfers are started by setting a bit in the DMA control register (DC2), whereas hardware-initiated transfers are started by a peripheral module setting a flag bit. Software-initiated transfers may be used to initiate a DMA data block transfer. As before, whichever transfer source bit is used to initiate the transfer must have been assigned to an enabled DMA channel.

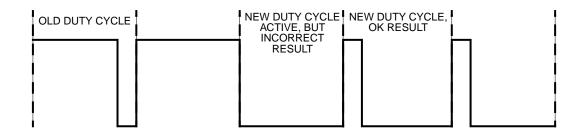

Interrupt-driven DMA transfers automatically clear the peripheral's DMA flag bit as the DMA reads or writes specific registers within the peripheral. The user must take special care with registers that are "write-cleared" with DMA bus bandwidths of 100%. Under these conditions the number of CPU cycles between one channel finishing and another starting can vary depending on when the interrupt was cleared.

# **DMA** Transfers

**Figure 12** (a) shows a standard 100% bandwidth write-clearing transfer. The DMA08 is not cleared for the next transfer, which is subsequently aborted, until after the write to the destination. The DMA, therefore, issues an unused source read.

**Figure 12** (b), **Figure 12** (c), and **Figure 12** (d) show how the DMA operation is affected under different circumstances.

Software-initiated transfers and read-clearing interrupts have DMA behavior as shown in **Figure 9**.

# Cycle-By-Cycle Operation

When the DMA transfers data, it takes control of the address bus, data bus and read/write (R/ $\overline{W}$ ) line. During the transfer, the DMA instructs the system integration module (SIM) to suspend the CPU clock; the state of the CPU, therefore, remains unchanged until the end of the transfer when the DMA relinquishes control of the buses and R/ $\overline{W}$  line to the CPU. The CPU then resumes operation as though nothing had happened.

The DMA uses two bus cycles to transfer a byte and four cycles to transfer a 16-bit word. A two cycle latency allows the DMA to respond to an interrupt. During these two cycles normal CPU operation continues. Selection of the transfer mode is via the byte-word control (BWC) bit in the channel control register. The actions of the DMA for byte and word transfer modes, respectively, are discussed in the following paragraphs.

**NOTE:** During a DMA transfer, any CPU interrupts can be recognized at the end of a byte/word transfer. See DMA Module Registers on page 52.

Byte Transfers Figure 10 shows the timing of a single-byte DMA transfer, with reference to the DMA clock, which is twice the bus frequency.

Figure 10. MCU Bus Activity During a DMA Byte Transfer

# DMA Activity During a Byte Transfer

An explanation of principal DMA actions during each state is given in **Table 1**. The numbers refer to the state numbers shown in **Figure 10**.

| State | Operation                                                                                                                                                                                    |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | Service request occurs (software or hardware)                                                                                                                                                |

| 2     | Arbitrates channel priorities and activates a channel                                                                                                                                        |

| 3     | Generates internal control signals                                                                                                                                                           |

| 4     | Calculates the source address                                                                                                                                                                |

|       | Stores the source address in a temporary register                                                                                                                                            |

|       | Takes control of the address bus                                                                                                                                                             |

|       | Drives the source address onto the address bus                                                                                                                                               |

| 5     | Takes control of the $R/\overline{W}$ line and drives it high                                                                                                                                |

|       | Calculates the destination address                                                                                                                                                           |

|       | Stores the destination address in a temporary register                                                                                                                                       |

|       | Takes control of the data bus                                                                                                                                                                |

| 6     | Latches source data in a temporary register                                                                                                                                                  |

|       | Increments the byte count register                                                                                                                                                           |

|       | Drives the destination address onto the address bus                                                                                                                                          |

| -     | Drives the R/W line low                                                                                                                                                                      |

| 7     | Subtracts the byte count register from the block length register.<br>If the result is zero, the channel enable bit is cleared.<br>Interrupts the CPU if the interrupt enable (IE) bit is set |

| 8     | Drives the source data onto the data bus                                                                                                                                                     |

| 9     | Releases the address bus and $R/\overline{W}$ to the CPU                                                                                                                                     |

| 10    | Relinquishes the data bus to the CPU                                                                                                                                                         |

# Table 1. Byte Transfer Activity

# **DMA** Transfers

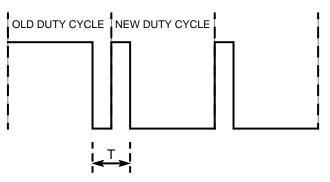

Word Transfers A word transfer occurs when the source and/or destination is set to static and the relevant BWC bit is set. Figure 12 shows the timing of a 16-bit word DMA transfer, with reference to the DMA clock, which is at twice the bus frequency.

DMA CONTROLLED BUS CYCLE

DMA Activity During a Word Transfer An explanation of principal DMA actions during each state is given in **Table 2**. The numbers refer to the state numbers shown in **Figure 12**, that is, at 100% bandwidth.

| State | Operation                                                                                                                                                                            |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | Service request occurs (software or hardware)                                                                                                                                        |

| 2     | Arbitrates channel priorities and activates a channel                                                                                                                                |

| 3     | Generates internal control signals                                                                                                                                                   |

| 4     | Calculates the source address and stores it in a temporary register                                                                                                                  |

|       | Takes control of the address bus                                                                                                                                                     |

|       | Drives the source address onto the address bus                                                                                                                                       |

| 5     | Takes control of the $R/\overline{W}$ line and drives it high                                                                                                                        |

|       | Calculates the destination address                                                                                                                                                   |

|       | Stores the destination address in a temporary register                                                                                                                               |

|       | Takes control of the data bus                                                                                                                                                        |

| 6     | Latches source data in a temporary register                                                                                                                                          |

|       | Increments the byte count register                                                                                                                                                   |

|       | Drives the destination address onto the address bus                                                                                                                                  |

| 7     | Drives the R/W line low                                                                                                                                                              |

|       | Subtracts the byte count register from the block length register                                                                                                                     |

|       | Drives the source data onto the data bus                                                                                                                                             |

| 8     | Calculates the source address for the second byte                                                                                                                                    |

|       | Stores the source address in a temporary register                                                                                                                                    |

|       | Drives the source address for the second byte onto the address bus                                                                                                                   |

| 0     | Drives the R/W line high                                                                                                                                                             |

| 9     | Calculates the destination address for the second byte                                                                                                                               |

|       | Stores the destination address in a temporary register                                                                                                                               |

| 10    | Latches source data into a temporary register                                                                                                                                        |

| 10    | Increments the byte count register                                                                                                                                                   |

|       | Drives the destination address for the second byte onto the address bus                                                                                                              |

| 11    | Drives the R/W line low                                                                                                                                                              |

|       | Subtracts the byte count register from the block length register. If the result is zero, the channel enable bit is cleared. Interrupts the CPU if the interrupt enable (IE) bit set. |

| 12    | Drives the source data for the second byte onto the data bus                                                                                                                         |

| 13    | Releases the address bus and $R/\overline{W}$ to the CPU                                                                                                                             |

| 14    | Relinquishes the data bus to the CPU                                                                                                                                                 |

# Table 2. Word Transfer Activity

# **DMA Transfer Latency**

DMA transfer latency is usually two bus cycles, but it can be extended to three if a read/write to a DMA channel register is taking place during the last of these two cycles. The access does not have to be to the active channel to increase latency. Applications that use multiple DMA channels may have to allow for a 3-cycle latency in performance calculations.

For comparison, the interrupt latency of the CPU is nine bus cycles.

# Example of the DMA Transfer Programming Procedure

The following procedure illustrates the required sequence of actions to program a DMA transfer. In all DMA channels, the operation and the register structure are identical, so only channel 0 will be described here:

- 1. Turn off channel if previously enabled.

- 2. Write the source base address to source base address registers (D0SH and D0SL).

- 3. Write the destination base address to destination base address registers (D0DH and D0DL).

- 4. In the DMA channel control register (D0C):

- a. Select increment/decrement/remain static for the source base addresses and for the destination base addresses.

- b. Select byte/word (takes effect only if source and/or destination base address calculation is set to static).

- c. Assign the DMA channel to a DMA transfer source input.

- 5. In the DMA channel block length register (D0BL), enter the number of bytes to be transferred.

- **NOTE:** Because each word equals two bytes, the block length should always be an even number for word transfers.

- 6. In the DMA status and control register (DSC):

- a. Enable or disable looping of the source and destination addresses for the channel.

- b. Select DMA transfers priority.

- c. Enable or disable DMA transfer operation during wait mode.

- 7. To control the DMA transfer with software, set the SWIx bit in DMA control register 2 (DC2) that corresponds to the selected transfer source input. The transfer will begin two cycles after the channel is enabled.

- 8. For a hardware interrupt-driven transfer, the transfer begins two cycles after the selected peripheral generates a DMA service request, providing the DMA channel is enabled.

- d. In DMA control register (DC1):

- a. Enable or disable CPU interrupt request generation on completion of DMA transfer.

- b. Select the DMA bandwidth.

- c. Enable the DMA channel.

# Address Calculation

The arithmetic logic unit (ALU) is a 16-bit subsystem that can calculate the 16-bit source and destination addresses in one cycle. During a DMA transfer, the ALU performs the following actions:

- Calculates the transfer source and transfer destination addresses

- Increments the byte count register for each byte transferred

- Determines when a block or loop transfer is complete by comparing the content of the byte count register with the value programmed into the block length register

The DMA source base address registers and destination base address registers contain the base addresses for a DMA transfer. The ALU uses these address registers as base pointers when it starts the transfer. The byte count register contains the number of bytes transferred to this point in the current DMA operation. The ALU uses the base address registers and the byte count register to calculate the actual source and destination addresses in the following manner:

- When an address is configured to increment, the ALU adds the contents of the byte count register to the base address.

- When an address is configured to decrement, the ALU subtracts the contents of the byte count register from the base address.

- When an address is configured to remain static, the ALU simply uses the base address (for example, it adds \$0000 to the base address).

The DMA module can be programmed to stop after a number of bytes is transferred (block mode) or to loop back to the base addresses and continue the transfer (loop mode).

**Figure 7** shows schematically how the DMA module calculates source and destination addresses.

# **Bandwidth Control**

The bandwidth control bits in DMA control register 1 are used to apportion the available MCU bus cycles between the DMA and the CPU. By setting these two bits, it is possible to assign the DMA either 25, 50, 67, or 100% of the bus cycles. See DMA Control Register 1 on page 52 for information on setting the bus bandwidth bits. Together with the DMAP bit, the bus bandwidth bits control the relative priorities of the DMA and the CPU.

|         | DMA/CPU Bus Bandwidth Sharing |                                                   |  |  |  |  |  |  |

|---------|-------------------------------|---------------------------------------------------|--|--|--|--|--|--|

| BB1:BB0 | Ratio<br>(DMA/CPU)            | DMA:CPU cycles                                    |  |  |  |  |  |  |

| 00      | 25/75%                        | 2:6                                               |  |  |  |  |  |  |

| 01      | 50/50%                        | 2:2                                               |  |  |  |  |  |  |

| 10      | 67/33%                        | 2:1                                               |  |  |  |  |  |  |

| 11      | 100/0%                        | The DMA controls the bus for as long as required. |  |  |  |  |  |  |

#### Table 3. DMA/CPU Bus Bandwidth Sharing

† THE CPU WILL ALWAYS GET AT LEAST ONE CYCLE EVERY TIME A CHANNEL STARTS A TRANSFER.

# Figure 13. DMA and CPU Use of the IBUS

- **NOTE:** Bus activity looks the same for both byte and word modes.

- **NOTE:** Regardless of the bandwidth setting, the DMA only consumes bus cycles during a transfer.

When the bus bandwidth is set to 25%, two out of every eight bus cycles are available for DMA transfers. Similarly, for 50% and 67%, the ratios are two out of four and two out of three, respectively. This also applies in word transfer mode. (See DMA Control Register 1 on page 52 for more information.) When 100% is selected, the DMA is allocated every available bus cycle.

**NOTE:** The CPU always executes at least one cycle before the next DMA loop begins, even if the DMA has been allocated 100% of the bus bandwidth. This ensures that it is impossible to lock out the CPU completely through inadvertently programming an endless DMA transfer.

Clearly, since there is only one system bus for addressing memory, sharing it with the DMA means that the performance of the CPU will be affected. When deciding on the bus allocation, care needs to be taken to understand the size and frequency of the expected DMA transfers, so that an appropriate share of the common bus resource is chosen. For a small and relatively infrequent transfer, it may be appropriate to give the DMA 100% of the bus to ensure that the transfers occur as quickly as possible. However, where large or frequent transfers are concerned, due consideration must be given to the needs of the main CPU routines. Further caution is required when DMA transfers are given priority over CPU interrupts (by setting the DMAP bit) and the DMA is given 100% of the bus bandwidth. For example:

- 1. When CPU interrupts have priority (DMAP bit = 0):

- a. The CPU will have access to those bus cycles not allocated to DMA.

- b. Any CPU interrupt will suspend any current DMA transfer at the end of the byte or word transfer in progress. All channel enable bits are cleared. DMA operation will resume only when a channel is specifically re-enabled.

- 2. When DMA transfers have priority:

- a. The CPU will have access to those bus cycles not allocated to DMA.

- b. CPU interrupts will not be recognized until all current DMA activity is complete.

# **DMA Registers**

# Contents

| Introduction                           | 50 |

|----------------------------------------|----|

| DMA Register Latency                   | 51 |

| DMA Module Registers                   | 52 |

| DMA Control Register 1                 | 52 |

| DMA Status and Control Register        | 54 |

| DMA Control Register 2                 | 57 |

| Individual DMA Channel Registers       | 59 |

| DMA Channel Control Register           | 59 |

| DMA Source Base Address Registers      | 62 |

| DMA Destination Base Address Registers | 63 |

| DMA Block Length Register              | 64 |

| DMA Byte Count Register                | 65 |

|                                        |    |

# Introduction

The M68HC08 DMA module may be implemented on silicon with one to seven independent DMA channels. Since the operation of each channel is identical, only channel 0 is described here.

In addition to the general control registers that control the operation of the entire DMA module, each channel requires seven 8-bit registers to define the details of its own operation. Four of these registers are concatenated into the two 16-bit source base and destination base address registers; the others are used for individual channel control, for specifying the size of the transfer block and for counting the number of bytes transferred.

| Register name                   | Adress   | Bit 7 | 6    | 5    | 4    | 3     | 2    | 1    | Bit 0 |

|---------------------------------|----------|-------|------|------|------|-------|------|------|-------|

|                                 |          |       |      |      |      |       |      |      |       |

| DMA control 1 (DC1)             | \$xxxx   | BB1   | BB0  |      |      |       |      | TEC0 | IEC0  |

| DMA status and control (DSC)    | \$xxxx   | DMAP  |      |      | L0   | DMAWE |      |      | IFC0  |

| DMA control 2 (DC2)             | \$xxxx   | SWI7  | SWI6 | SWI5 | SWI4 | SWI3  | SWI2 | SWI1 | SWI0  |

|                                 |          | [     |      | 1    | 1    |       |      |      |       |

| Channel 0 register name         | Address  | Bit 7 | 6    | 5    | 4    | 3     | 2    | 1    | Bit 0 |

| Source base address (D0SH)      | \$xxxx   | AD15  | AD14 | AD13 | AD12 | AD11  | AD10 | AD9  | AD8   |

| Source base address (DOSL)      | \$xxxx+1 | AD7   | AD6  | AD5  | AD4  | AD3   | AD2  | AD1  | AD0   |

|                                 |          |       |      |      |      |       |      |      |       |

| Destination base address (D0DH) | \$xxxx   | AD15  | AD14 | AD13 | AD12 | AD11  | AD10 | AD9  | AD8   |

| Destination base address (D0DL) | \$xxxx+1 | AD7   | AD6  | AD5  | AD4  | AD3   | AD2  | AD1  | AD0   |

|                                 |          |       |      |      |      |       |      |      |       |

| Control (D0C)                   | \$xxxx   | SDC3  | SDC2 | SDC1 | SDC0 | BWC   | DTS2 | DTS1 | DTS0  |

| Block length (D0BL)             | \$xxxx+1 | BL7   | BL6  | BL5  | BL4  | BL3   | BL2  | BL1  | BL0   |

|                                 |          |       |      |      |      |       |      |      |       |

| Byte count (D0BC)               | \$xxxx   | BC7   | BC6  | BC5  | BC4  | BC3   | BC2  | BC1  | BC0   |

**NOTE:** Shaded bits are reserved for additional DMA channels. For the maximum number of channels, registers DC1A and DSCA are required. The extra TECx, IECx, Lx, and IFCx bits for each channel are added.

Reference should be made to the specific device data sheet for details of the number of channels, register addresses, and bit names.

# **DMA Register Latency**

The following registers control and monitor operation of the channel of the DMA module:

- DMA control register 1 (DC1)

- DMA status and control register (DSC)

- DMA control register 2 (DC2)

- **NOTE:** The operation of a single channel is described throughout this manual for consistency.

DC1, DSC, and DC2 can be read/written during a DMA transfer with no affect on DMA latency.

The following registers control operation of an individual DMA channel. (Each channel has an identical set of these registers.)

- DMA channel 0 source base address register, high and low byte (D0SH:D0SL)

- DMA channel 0 destination base address register, high and low byte (D0DH:D0DL)

- DMA channel 0 control register (D0C)

- DMA channel 0 block length register (D0BL)

- DMA channel 0 byte count register (D0BC)

Writing to any of these registers during the cycle prior to a transfer can add one cycle to DMA latency.

# DMA Registers

# **DMA Module Registers**

The following registers affect all the DMA channels.

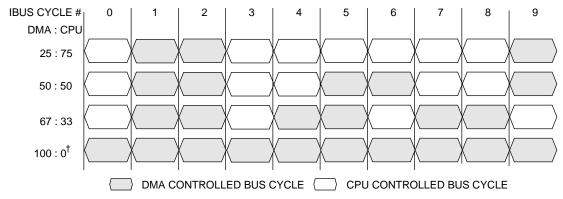

DMA ControlDMA control register 1 (DC1) is used to enable individual channels toRegister 1transfer data, to enable DMA interrupts to the CPU, and to allocate the<br/>amount of the total bus bandwidth that the DMA can use.

Figure 14. DMA Control Register (DC1)

#### BB1:BB0 — Bus bandwidth control bits

These read/write bits control the ratio of DMA to CPU bus activity. The DMA can be allocated 25%, 50%, 67%, or 100% of the total bus bandwidth, with the CPU taking the remaining cycles. After a DMA transfer, the next transfer is inhibited until the required number of cycles has been executed by the CPU. See Figure 7 on page 36 and Figure 13 on page 47.

For DMA transfers of a few bytes, giving the DMA module 100% of the bus bandwidth may be appropriate. However, for large, software-initiated transfers, limiting the bus bandwidth of the DMA module may be necessary to maintain an acceptable level of CPU activity.

TEC0 — Transfer enable (channel 0)

This read/write bit enables channel 0 to take control of the M68HC08 data and address buses two cycles after a valid request for DMA transfer occurs.

- 1 = DMA channel 0 enabled.

- 0 = DMA channel 0 disabled.

This bit is cleared on completion of a block transfer if looping is disabled. (See DMA Status and Control Register on page 54.)

**NOTE:** A CPU interrupt request (if recognized) will disable all DMA channels by clearing the transfer enable control (TECx) bit for each channel if DMAP = 0.

IEC0 — CPU interrupt enable (channel 0)

This read/write bit enables channel 0 to generate a CPU interrupt when the interrupt flag IFC0 becomes set.

- 1 = DMA interrupt to the CPU enabled (channel 0)

- 0 = DMA interrupt to the CPU disabled (channel 0)

# **DMA Registers**

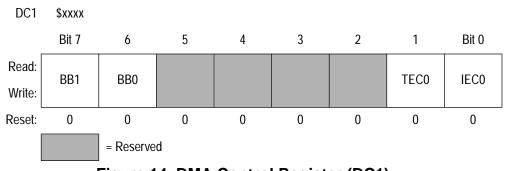

# DMA Status and Control Register

The DMA status and control register contains a flag that indicates the completion of DMA block transfer. It also controls the DMA loopback facility and the priority of DMA transfers with respect to CPU interrupts. One bit is used to enable DMA operation during wait mode.

#### DMAP — DMA priority

This read/write bit controls the priority of DMA module transfers with respect to CPU interrupt requests.

1 = DMA has priority.

DMA activity cannot be interrupted by the CPU. CPU interrupts are recognized only after the DMA releases the internal bus.

0 = CPU has priority.

CPU interrupts are recognized at the end of the current byte or word transfer.

When DMAP = 1, CPU interrupts are recognized only after the DMA module releases the internal bus. In this case, the increase in CPU interrupt latency depends on the size of the block and the state of the bus bandwidth bits, BB0:BB1. For example, for a 256-byte block transfer with a 100% bandwidth, the worst case latency is 512 cycles. This is only true if the DMA request is permanently asserted, as is the case with a software-initiated transfer. A hardware-initiated transfer will continue to transfer bytes or words until the request bit is cleared. This is normally done by reading or writing to a data register of the module that made the request. In situations where the DMA does not have 100% of the bus bandwidth, CPU interrupts will be serviced during the CPU-controlled bus cycles.

When DMAP = 0, CPU interrupts are recognized after the DMA completes the byte or word transfer in progress; the CPU then disables the DMA by clearing the transfer enable bit(s) for all channels. Therefore, the DMA can increase CPU interrupt latency by up to three cycles, or five in the case of a word transfer. Software must re-enable a DMA channel, if required, by setting the channel enable bit (TEC0). When this is done, the DMA transfer can continue.

L0 — Loop enable bit

This read/write bit enables DMA transfer looping. On completion of a block transfer, the DMA restarts the transfer from the addresses contained in the source base address and destination base address registers. In this way, a circular buffer can be set up or serviced. Reset clears the L0 bit.

1 = Looping is enabled (loop mode).

0 = Looping is disabled (block mode).

When looping is enabled (L0 = 1), the DMA module takes the following actions after it has completed transferring the number of bytes specified in the block length register:

- Sets the channel interrupt flag (IFC0)

- Generates an interrupt request, if enabled (IEC0 = 1)

- Clears the byte count register

- Continues transfer from the base address.

When looping is disabled (L0 = 0), the DMA module takes the following actions after it has completed transferring the number of bytes specified in the block length register:

- Sets the channel interrupt flag (IFC0)

- Generates an interrupt request, if enabled (IEC0 = 1)

- Clears the byte count register

- Disables the channel by clearing the TEC0 bit

- **NOTE:** The CPU always executes at least one cycle before the next DMA loop begins, even if the DMA has been allocated 100% of the bus bandwidth. This ensures that it is impossible to lock out the CPU completely through inadvertently programming an endless DMA transfer. Care must be

taken when using the settings DMAP =1, BB1:BB0 = 11, and L0 = 1 during a software-initiated transfer.

#### DMAWE — DMA wait enable

This read/write bit is used to enable DMA operation while the CPU is in wait mode. Reset clears the DMAWE bit.

- 1 = DMA transfer possible during wait mode.

- 0 = DMA transfers suspended in wait mode.

#### IFC0 — Interrupt flag

This read/write bit becomes set when a DMA transfer is complete or at the end of each transfer loop. The interrupt flag (IFC0) becomes set when the content of the byte count register equals that of the block length register. IFC0 = 1 will generate a CPU interrupt request if the corresponding IEC0 bit is set in the DMA status and control register. If interrupts are disabled, IFC0 can be polled by software to see when a transfer or loop is complete. But care must be taken not to inadvertently clear the IFCx bits of other channels in a multi-channel implementation. IFC0 is cleared by reading it and then writing a zero to it. Reset clears this bit.

- 1 = DMA transfer complete

- 0 = DMA transfer not complete

DMA08 Reference Manual - Rev. 1.0

## DMA Control Register 2

DMA control register 2 is used to initiate a DMA transfer.

#### DC2 \$xxxx Bit 7 5 2 1 Bit 0 6 4 3 Read: SWI7 SWI6 SWI5 SWI4 SWI3 SWI2 SWI1 SWI0 Write: 0 Reset: 0 0 0 0 0 0 0

Figure 16. DMA Control Register 2 (DC2)

SWI7–SWI0 — Software initiate 7–0

Each of these read/write bits is used to initiate a DMA request from one of the eight DMA transfer sources (see **Table 4**). For the transfer to begin, the channel first must be enabled by the TEC0 bit in the DMA control register. The channel also must be assigned, by its DMA channel control register, to the relevant DMA transfer input.

- 1 = Start software-initiated DMA transfer

- 0 = No software-initiated DMA transfer

The DMA responds to the setting of an SWIx bit in the same way that it responds to a hardware service request. The DC2 bit position corresponds to the DTS [2:0] assignment in the channel. The SWIx bit is ORed with the hardware service request. The SWIx bits are cleared only by a write to the DC2 registers.

| DTS[2:0] | Interrupt-Driven Transfer Source | Software-Driven |

|----------|----------------------------------|-----------------|

| 000      | DMA service request input 0      | SWI0            |

| 001      | DMA service request input 1      | SWI1            |

| 010      | DMA service request input 2      | SWI2            |

| 011      | DMA service request input 3      | SWI3            |

| 100      | DMA service request input 4      | SWI4            |

| 101      | DMA service request input 5      | SWI5            |

| 110      | DMA service request input 6      | SWI6            |

| 111      | DMA service request input 7      | SWI7            |

**NOTE:** Because the SWIx bits are ORed with the hardware service requests, take care when choosing which SWIx bits to use. Choose a bit that corresponds to a hardware service request that is not being used. The DMA service request enable bit in the corresponding peripheral should be turned off.

A software-initiated DMA transfer differs from a normal hardware-initiated transfer in that the entire block of data can be transferred before any CPU interrupts are recognized. In the case of loop mode, the CPU may have only one cycle in every 512 cycles to execute its code. SWIx remains asserted after a transfer is complete, but TEC will be cleared. To repeat the same transfer, it is only necessary to reassert TEC.

# Individual DMA Channel Registers

Each channel in the DMA module has the following set of registers.

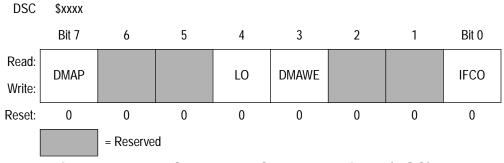

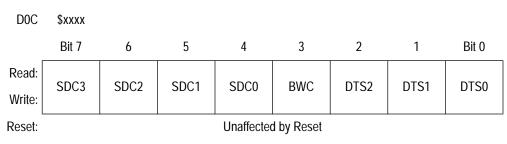

DMA ChannelThe DMA channel control register (D0C) contains bits to control the<br/>calculation of the source base and destination base addresses<br/>throughout a transfer, selects byte or word transfer mode, and assigns<br/>the channel to one of the eight possible DMA transfer sources. The state<br/>of the bits in the DMA channel control register is undefined after reset.

#### Figure 17. DMA Channel Control Register (D0C)

SDC3–SDC0 — Source/destination base address control bits 3–0

These read/write bits control calculation of the source base and destination base addresses as shown in **Table 5**.

| Table 5. DMA Ch | annel Control | Register |

|-----------------|---------------|----------|

|-----------------|---------------|----------|

| SDC[3:0] | Source Address | Destination Address |

|----------|----------------|---------------------|

| 1010     | Increment      | Increment           |

| 1001     | Increment      | Decrement           |

| 1000     | Increment      | Static              |

| 0110     | Decrement      | Increment           |

| 0101     | Decrement      | Decrement           |

| 0100     | Decrement      | Static              |

| 0010     | Static         | Increment           |

| 0001     | Static         | Decrement           |

| 0000     | Static         | Static              |

The DMA calculates an incremented address by adding the contents of the byte count register to the base address contained in the source base (or destination base) address register. Similarly, to calculate a decremented address, the DMA subtracts the byte count register from the base address. For static addressing modes, the DMA simply adds zero or one to the base address, depending on whether the DMA is configured for byte or word transfers.

#### BWC — Byte/word control

This read/write bit determines whether the DMA channel transfers 8-bit bytes or 16-bit words. A DMA byte transfer takes two bus cycles and a word transfer takes four bus cycles. CPU interrupts can be recognized only after the completion of a byte or word transfer.

1 = 1 = DMA transfers 16-bit words

0 = 0 = DMA transfers 8-bit bytes

The BWC bit has no effect unless either the source base or destination base address is static or both are static. **Table 6** shows how the DMA calculates addresses in word transfers. When both the source base and destination base addresses are static, the first byte of the word transfers from the source base address to the destination base address. The second byte transfers from the source base address plus one to the destination base address plus one. When either the source base or destination base address increments or decrements, the DMA module transfers bytes from or to incrementing or decrementing addresses.

|      |      | STATIC SOURCE | STATIC DESTINATION | INCREMENTED SOURCE | STATIC DESTINATION | STATIC SOURCE | INCREMENTED DESTINATION | DECREMENTED SOURCE | STATIC DESTINATION | STATIC SOURCE | DECREMENTED DESTINATION |

|------|------|---------------|--------------------|--------------------|--------------------|---------------|-------------------------|--------------------|--------------------|---------------|-------------------------|

| Word | Byte | From          | То                 | From               | То                 | From          | То                      | From               | То                 | From          | То                      |

| 1    | 1    | SBA           | DBA                | SBA                | DBA                | SBA           | DBA                     | SBA                | DBA                | SBA           | DBA                     |

|      | 2    | SBA+1         | DBA+1              | SBA+1              | DBA+1              | SBA+1         | DBA+1                   | SBA-1              | DBA+1              | SBA+1         | DBA–1                   |

| 2    | 3    | SBA           | DBA                | SBA+2              | DBA                | SBA           | DBA+2                   | SBA–2              | DBA                | SBA           | DBA–2                   |

|      | 4    | SBA+1         | DBA+1              | SBA+3              | DBA+1              | SBA+1         | DBA+3                   | SBA–3              | DBA+1              | SBA+1         | DBA–3                   |

| 3    | 5    | SBA           | DBA                | SBA+4              | DBA                | SBA           | DBA+4                   | SBA-4              | DBA                | SBA           | DBA–4                   |

| 3    | 6    | SBA+1         | DBA+1              | SBA+5              | DBA+1              | SBA+1         | DBA+5                   | SBA–5              | DBA+1              | SBA+1         | DBA–5                   |

|      | V    | V             |                    | V                  | V                  | V             | V                       | V                  |                    |               |                         |

| n    | 2n–1 | SBA           | DBA                | SBA+<br>2n–2       | DBA                | SBA           | DBA+<br>2n–2            | SBA–<br>(2n–2)     | DBA                | SBA           | DBA–<br>(2n–2)          |

|      | 2n   | SBA+1         | DBA+1              | SBA+<br>2n–1       | DBA+1              | SBA+1         | DBA+<br>2n–1            | SBA-<br>(2n-1)     | DBA+1              | SBA+1         | DBA–<br>(2n–1)          |

Table 6. DMA Word Transfer

Note: SBA = Source Base Address, DBA = Destination Base Address

DTS2–DTS0 — DMA transfer source bits 2–0

These read/write bits assign the individual DMA channel to one of the eight transfer source inputs, as shown in **Table 4**. This information is hardwired for each M68HC08 device. For details about peripheral module interrupts designated as service request inputs, refer to the specific device data sheet.

# **DMA Registers**

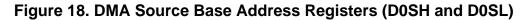

## DMA Source Base Address Registers

The DMA channel reads its data from the source base address defined in the 16-bit source base address register. During a block transfer, the DMA determines successive source base addresses by adding to (increment) or subtracting from (decrement) the base address. In static address transfers, the DMA finds the source address by simply adding zero or one to the address, depending on whether the DMA is configured for byte or word transfers.

| D0SH            | \$xxxx     |      |      |            |            |      |     |       |

|-----------------|------------|------|------|------------|------------|------|-----|-------|

|                 | Bit 7      | 6    | 5    | 4          | 3          | 2    | 1   | Bit 0 |

| Read:<br>Write: | AD15       | AD14 | AD13 | AD12       | AD11'      | AD10 | AD9 | AD8   |

| Reset:          |            |      |      | Unaffected | d by Reset |      | -   |       |

|                 |            |      |      |            |            |      |     |       |

| D0SL            | \$xxxx + 1 |      |      |            |            |      |     |       |

|                 | Bit 7      | 6    | 5    | 4          | 3          | 2    | 1   | Bit 0 |

| Read:<br>Write: | AD7        | AD6  | AD5  | AD4        | AD3        | AD2  | AD1 | AD0   |

| Reset:          |            |      |      | Unaffected | d by Reset |      |     |       |

# DMA Destination Base Address Registers

The DMA channel writes data to the destination address defined by the 16-bit destination base address register. During a block transfer, the DMA determines successive destination base addresses by adding to (increment) or subtracting from (decrement) the base address. In static address transfers, the DMA finds the destination base address by simply adding zero or one to the base address, depending on whether the DMA is configured for byte or word transfers. The state of the destination base address registers is undefined after reset.

| D0DH            | \$xxxx              |      |      |            |            |      |     |       |  |  |

|-----------------|---------------------|------|------|------------|------------|------|-----|-------|--|--|

|                 | Bit 7               | 6    | 5    | 4          | 3          | 2    | 1   | Bit 0 |  |  |

| Read:<br>Write: | AD15                | AD14 | AD13 | AD12       | AD11       | AD10 | AD9 | AD8   |  |  |

| Reset:          |                     |      |      | Unaffected | d by Reset |      |     |       |  |  |

| D0DL            | \$xxxx + 1          |      |      |            |            |      |     |       |  |  |

|                 | Bit 7               | 6    | 5    | 4          | 3          | 2    | 1   | Bit 0 |  |  |

| Read:<br>Write: | AD7                 | AD6  | AD5  | AD4        | AD3        | AD2  | AD1 | AD0   |  |  |

| Reset:          | Unaffected by Reset |      |      |            |            |      |     |       |  |  |

# Figure 19. DMA Destination Base Address Registers (D0DH and D0DL)

**NOTE:** Support for the optional address extension module is built into the DMA. In this case, the source base and destination base address registers are effectively 24 bits. See Address Extension Module on page 28.

# **DMA Registers**

# DMA Block LengthThe read/write block length register controls the number of bytesRegisterThe read/write block length register controls the number of bytestransferred.In word mode, the block length register must be written with<br/>the number of words times two. During a block transfer, the DMA<br/>compares the number programmed into the DMA block length register<br/>to the number in the DMA byte count register. When the byte count<br/>reaches the value in the block length register, the DMA does the<br/>following:

- Sets the channel interrupt flag (IFC0)

- Generates CPU interrupt request, if enabled (IEC0 = 1)

- Clears the byte count register

If looping is disabled (L0 = 0), the DMA then stops the transfer by clearing the TEC0 bit in DMA control register 1, thus disabling the channel. If looping is enabled (L0 = 1), the DMA continues the transfer from the base address.

A value of \$00 in the register designates the maximum block length of 256 bytes. After reset, the state of the DMA block length registers is undefined.

DOBL \$xxxx

|                 | Bit 7               | 6   | 5   | 4   | 3   | 2   | 1   | Bit 0 |

|-----------------|---------------------|-----|-----|-----|-----|-----|-----|-------|

| Read:<br>Write: | BL7                 | BL6 | BL5 | BL4 | BL3 | BL2 | BL1 | BL0   |

| Reset:          | Unaffected by Reset |     |     |     |     |     |     |       |

Figure 20. DMA Block Length Register (D0BL)

# DMA Byte Count Register

The read/write DMA byte count register contains the number of bytes transferred on the channel during the current DMA transfer.

D0BC \$xxxx

|                 | Bit 7               | 6   | 5   | 4   | 3   | 2   | 1   | Bit 0 |

|-----------------|---------------------|-----|-----|-----|-----|-----|-----|-------|

| Read:<br>Write: | BC7                 | BC6 | BC5 | BC4 | BC3 | BC2 | BC1 | BC0   |

| Reset:          | Unaffected by Reset |     |     |     |     |     |     |       |

Figure 21. DMA Byte Count Register (D0BC)

Writing to the source base address or destination base address register clears the byte count register. The byte count register also is cleared when its count reaches the value in the block length register. Reset clears the byte count register.

# **DMA Registers**

# **DMA Application Examples**

# Contents

|                                                     | 68  |

|-----------------------------------------------------|-----|

| Software-Initiated Block Transfer                   | 69  |

| A – Simple, Small Block Transfer                    | 69  |

| B – Flexible, Large Block Transfer                  | 71  |

| Summary                                             | 73  |

| DMA Service of Serial Communications                | 73  |

| A – Transmitting a Buffered Message Using the CPU   | 74  |