## Motorola Semiconductor Application Note

## AN1736

### Variations in the Motorola MC68HC05Px Family

By Joanne Field PPCM System Engineering, Motorola Ltd. East Kilbride, Scotland

#### Introduction

The Motorola MC68HC05 P Family of 8-bit microcontrollers is one of the largest and most widely used. This application note clarifies the important differences among the various HC05P Family devices for anyone who may be developing an application using one of these devices. It is particularly useful for those familiar with one of the members of the family but wishes to move to another.

Since Motorola is improving specifications and optimizing its MCU portfolio constantly, the reader is always encouraged to consult the latest data books for specification details and availability.

This application note discusses:

- Similarities and comparisons

- Pinouts

- The A strategy

- Changing from OTP/FLASH to ROM

- Changing from non-A to A versions

- Voltage, frequency, and temperatures tables

- Development tools

#### **Recommendations for Future Designs**

Although this application note covers all current variants of the HC05P Family, it is recommended that these two devices not be used, as they do not have OTPs (one-time programmer), which emulate them specifically:

- HC05P8

- HC05P15

Regarding the HC05P1, HC05P4, and HC05P9, Motorola offers the A equivalent for new designs exclusively, for example HC05P1A, HC05P4A, and HC05P9A.

The HC705P6 and the HC705P9 will be discontinued in the future and the HC705P6A will be the replacement OTP.

## Similarities and Comparisons

| Similarities                                    | Similarities exist in the 16-bit input capture/output compare timer and the COP watchdog.                                                                                                                                                                                                                                                                     |

|-------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 16-Bit Input<br>Capture/Output<br>Compare Timer | The timer core is a 16-bit, free-running counter, which provides the timing reference for the input capture and output compare functions. The input capture and output compare functions provide a means of latching the times at which external events occur and generating output waveforms and timing delays.                                              |

|                                                 | The HC05P8 is the only member of the P Family which does not have a 16-bit programmable timer. It has a 15-stage ripple counter.                                                                                                                                                                                                                              |

| COP Watchdog                                    | A COP watchdog (computer operating properly) is used in a system to<br>make sure that the software operates correctly. At regular intervals, the<br>COP must be refreshed. If this does not happen because the application<br>software has "run away" or it has entered a loop that it cannot exit, the<br>COP watchdog will time out and force an MCU reset. |

|                                                 | The only P Family device which does not have a COP is the HC05P1.<br>On all other P Family devices, the COP is enabled by mask option.<br>However, there are variations in the way the COP is refreshed.                                                                                                                                                      |

| Comparisons                                     | The P Family variations are summarized in Table 1 and Table 2.                                                                                                                                                                                                                                                                                                |

| Device                                                                                                        | 05P1           | 05P1A                            | 05P3                   | 705P3                  | 05P4                             | 05P4A                            | 05P6                             | 705P6                            | 705P6A                           |

|---------------------------------------------------------------------------------------------------------------|----------------|----------------------------------|------------------------|------------------------|----------------------------------|----------------------------------|----------------------------------|----------------------------------|----------------------------------|

| COP<br>enable                                                                                                 | No             | Mask<br>Option                   | Mask<br>Option         | Clear bit 1<br>\$0F    | Mask<br>Option                   | Mask<br>Option                   | Mask<br>Option                   | Set bit 0<br>\$1F00              | Set bit 0<br>\$1F00              |

| $\begin{array}{c} \text{COP} \\ \text{timeout} \\ \text{f}_{\text{op}} = \text{f}_{\text{osc}}/2 \end{array}$ | No             | 2 <sup>17</sup> /f <sub>op</sub> | Software<br>selectable | Software<br>selectable | 2 <sup>17</sup> /f <sub>op</sub> |

| COP<br>clear                                                                                                  | No             | Clear bit 0<br>\$1FF0            | Clear bit 0<br>\$0FF0  | Clear bit 0<br>\$0FF0  | Clear bit 0<br>\$1FF0            |

| Stop<br>disable                                                                                               | No             | Mask<br>option                   | No                     | No                     | No                               | No                               | Mask<br>option                   | Bit 5<br>MOR                     | Bit 5<br>MOR2                    |

| Port A<br>pullups                                                                                             | No             | Mask<br>option                   | No                     | No                     | No                               | Mask<br>option                   | No                               | No                               | Yes<br>MOR1                      |

| High<br>current                                                                                               | No             | PC0, PC1                         | No                     | No                     | No                               | PC0, PC1                         | No                               | No                               | PC0, PC1                         |

| A/D                                                                                                           | No             | No                               | No                     | No                     | No                               | No                               | 4<br>channel,<br>8 bit           | 4<br>channel,<br>8 bit           | 4<br>channel,<br>8 bit           |

| RC, OSC                                                                                                       | Mask<br>option | Mask<br>option                   | No                     | No                     | Mask<br>option                   | Mask<br>option                   | Mask<br>option                   | No                               | No                               |

| LVR                                                                                                           | No             | No                               | No                     | No                     | No                               | No                               | No                               | No                               | No                               |

| SIOP<br>clock rate<br>$f_{op} = f_{osc}/2$                                                                    | _              | _                                | _                      | _                      | 1/4 f <sub>op</sub>              | 1/4 f <sub>op</sub>              | Software<br>selectable           | Software<br>selectable           | Software<br>selectable           |

| SIOP<br>MSB/LSB                                                                                               | _              | _                                | _                      | _                      | Mask<br>option                   | Mask<br>option                   | Mask<br>option                   | Bit 2<br>MOR                     | Bit 2<br>MOR2                    |

| Mask<br>option<br>register                                                                                    | No             | No                               | No                     | \$0F                   | No                               | No                               | No                               | \$1F00                           | \$1EFF,<br>\$1F00                |

| Security                                                                                                      | No             | No                               | No                     | No                     | No                               | Yes                              | No                               | No                               | Yes                              |

| EEPROM                                                                                                        | No             | No                               | 128                    | 128                    | No                               | No                               | No                               | No                               | No                               |

| RAM                                                                                                           | 128            | 128                              | 128                    | 128                    | 176                              | 176                              | 176                              | 176                              | 176                              |

| EP(ROM)<br>exc.<br>vectors                                                                                    | 2096           | 2304                             | 3072                   | 3072                   | 4144                             | 4144                             | 4656                             | 4656                             | 4656                             |

| Recom-<br>mended<br>OTP                                                                                       | 705P6A         | 705P6A                           | 705P3                  | _                      | 705P6A                           | 705P6A                           | 705P6A                           | _                                | _                                |

### Table 1. P Family Variations

| Device                                                                                                        | 05P7                             | 05P8                  | 05P9                             | 05P9A                            | 705P9                            | 05P15                            | 05P18                            | 805P18                           |

|---------------------------------------------------------------------------------------------------------------|----------------------------------|-----------------------|----------------------------------|----------------------------------|----------------------------------|----------------------------------|----------------------------------|----------------------------------|

| COP<br>enable                                                                                                 | Mask<br>option                   | Mask<br>option        | Mask<br>option                   | Mask<br>option                   | Set bit 0<br>\$0900              | Mask<br>option                   | Mask<br>option                   | Set bit 0<br>\$3F00              |

| $\begin{array}{c} \text{COP} \\ \text{timeout} \\ \text{f}_{\text{op}} = \text{f}_{\text{osc}}/2 \end{array}$ | 2 <sup>17</sup> /f <sub>op</sub> | Program-<br>mable     | 2 <sup>17</sup> /f <sub>op</sub> |

| COP clear                                                                                                     | Clear bit 0<br>\$1FF0            | Clear bit 0<br>\$1FF0 | Clear bit 0<br>\$1FF0            | Clear bit 0<br>\$1FF0            | Clear bit 0<br>\$1FF0            | Clear bit 0<br>\$1FF0            | Clear bit 0<br>\$3FF0            | Clear bit 0<br>\$3FF0            |

| Stop<br>disable                                                                                               | No                               | Mask<br>option        | No                               | Mask<br>option                   | No                               | Mask<br>option                   | Mask<br>option                   | Yes                              |

| Port A pullups                                                                                                | No                               | No                    | No                               | Yes                              | No                               | Yes                              | Yes                              | Yes                              |

| High<br>current                                                                                               | No                               | No                    | No                               | PC0, PC1                         | No                               | No                               | PC0, PC1                         | PC0, PC1                         |

| A/D                                                                                                           | No                               | 4 channel,<br>8 bit   | 4 channel,<br>8 bit              | 4 channel,<br>8 bit              | 4 channel,<br>8 bit              | Compar-<br>ator                  | 4 channel,<br>8 bit              | 4 channel,<br>8 bit              |

| RC OSC                                                                                                        | Mask<br>option                   | No                    | No                               | Mask<br>option                   | No                               | Mask<br>option                   | No                               | No                               |

| LVR                                                                                                           | No                               | No                    | No                               | No                               | No                               | No                               | Yes                              | Yes                              |

| SIOP<br>clock rate<br>f <sub>op</sub> = f <sub>osc</sub> /2                                                   | 1/4 f <sub>op</sub>              | _                     | 1/4 f <sub>op</sub>              | 1/4 f <sub>op</sub>              | 1/4 f <sub>op</sub>              | _                                | Software selectable              | Software selectable              |

| SIOP<br>MSB/LSB                                                                                               | Mask<br>option                   |                       | Mask<br>option                   | Mask<br>option                   | Bit 2 MOR                        | _                                | Mask<br>option                   | Bit 2<br>MOR1                    |

| Mask<br>option<br>register                                                                                    | No                               | No                    | No                               | No                               | \$0900                           | No                               | No                               | \$3F00,<br>\$3F01                |

| Security                                                                                                      | No                               | No                    | No                               | Yes                              | No                               | No                               | No                               | No                               |

| EEPROM                                                                                                        | No                               | 32                    | No                               | No                               | No                               | No                               | 128                              | 128+8048                         |

| RAM                                                                                                           | 128                              | 112                   | 128                              | 128                              | 128                              | 128                              | 192                              | 192                              |

| EP(ROM)<br>exc<br>vectors                                                                                     | 2096                             | 2048                  | 2096                             | 2096                             | 2096                             | 3136                             | 8048                             | _                                |

| Recom-<br>mended<br>OTP                                                                                       | 705P9/<br>705P6A                 | 705P9/<br>705P6A      | 705P9/<br>705P6A                 | 705P6A                           | _                                | _                                | 805P18                           | _                                |

Table 2. Comparisons among the P Family Devices

Stop Disable

These P Family devices do not have an option to disable stop mode:

- HC05P1

- HC05P3

- HC705P3

- HC05P4

- HC05P4A

- HC05P7

- HC05P8

- HC05P9

- HC705P9

On all other devices, stop can be disabled by a mask option.

Analog- to-DigitalThese P Family members do not have an analog-to-digital (A/D)Converterconverter:

- HC05P1

- HC05P1A

- HC05P3

- HC705P3

- HC05P4

- HC05P4A

All other devices, with the exception of the HC05P15, have a 4-channel, 8-bit successive approximation A/D converter. The A/D subsystem shares its inputs with port C pins PC3–PC7.

The HC05P15 has one analog voltage comparator with a digital output. It shares its pins with PB5–PB7.

*RC Oscillator* The P Family devices which have an RC oscillator option are:

- HC05P1

- HC05P1A

- HC05P4

- HC05P4A

- HC05P6

- HC05P7

- HC05P9A

- HC05P15

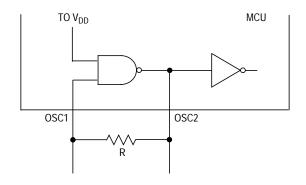

The RC oscillator option provides a low-cost oscillator and is enabled by a mask option. An external resistor is required. **Figure 1** shows the resistor connected to the oscillator pins.

Figure 1. RC Oscillator Circuit Diagram

Since the accuracy of the RC oscillator is  $\pm$ 50%, the nominal design frequency must be limited to 66% of the maximum frequency to ensure that the operating frequency remains below the upper limit of operating frequency. The 50% tolerance only allows for the MCU variation, and additional allowance must be for the tolerance(s) of any external components. Refer to the device specification for the graph showing the relationship between the external resistor, R, and the operating frequency, f<sub>op</sub>.

Low-Voltage Reset (LVR) The only devices which have a low-voltage reset (LVR) are:

- HC05P18

- HC805P18

These devices do not have an SIOP subsystem:

Serial Input/Output Port (SIOP)

- HC05P1

- HC05P1A

- HC05P3

- HC705P3

- HC05P8

- HC05P15

All other P Family devices have an SIOP. It is possible to choose whether the most significant bit (MSB) or least significant bit (LSB) comes first. On some devices, the SIOP clock rate can be chosen through software or it is fixed at 1/4 of the operating frequency ( $f_{op}$ ).

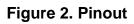

*Pinouts* There is variation in the pin positions of the P Family devices, although they each have 28 pins.

The pinout for these devices are shown in Figure 2:

- HC05P1

- HC05P1A

- HC05P4

- HC05P4A

- HC05P6

- HC705P6

- HC705P6A

- HC05P7

- HC05P9

- HC05P9A

- HC705P9

- HC05P18

- HC805P18

- **NOTE:** The HC05P1A has two pinouts. While it has the pinout described in **Figure 2**, it also has a low-noise pinout, which is shown in **Figure 4**. This pinout is chosen on the ROM header as part number MC68LNC05P1A.

The HC05P3 and HC705P3 have the pinout shown in **Figure 5** and the HC05P8 pinout is shown in **Figure 7**. The HC05P15 has the pinout shown in **Figure 6**.

| RESET               | 1 <sup>•</sup> | 28 | V <sub>DD</sub> |

|---------------------|----------------|----|-----------------|

| IRQ/V <sub>PP</sub> | 2              | 27 | OSC1            |

| PA7                 | 3              | 26 | OSC2            |

| PA6                 | 4              | 25 | PD7/TCAP        |

| PA5                 | 5              | 24 | TCMP            |

| PA4                 | 6              | 23 | PD5             |

| PA3                 | 7              | 22 | PC0             |

| PA2                 | 8              | 21 | PC1             |

| PA1                 | 9              | 20 | PC2             |

| PA0                 | 10             | 19 | PC3             |

| PB5                 | 11             | 18 | PC4             |

| PB6                 | 12             | 17 | PC5             |

| PB7                 | 13             | 16 | PC6             |

| V <sub>SS</sub> [   | 14             | 15 | PC7             |

|                     |                |    |                 |

Figure 3. LNC05P1A Pinout

| IRQ   | 1 <sup>●</sup> |           | 28 | V <sub>SS</sub> |

|-------|----------------|-----------|----|-----------------|

| RESET | 2              |           | 27 | V <sub>DD</sub> |

| OSC1  | 3              |           | 26 | PA0             |

| OSC2  | 4              |           | 25 | PA1             |

| PB7   | 5              |           | 24 | PA2             |

| PB6   | 6              | Ъ3        | 23 | PA3             |

| PB5   | 7              | HC(7)05P3 | 22 | PA4             |

| PB4   | 8              | Ĕ         | 21 | PA5             |

| PB3   | 9              | Ŧ         | 20 | PA6             |

| PB2   | 10             |           | 19 | PA7             |

| PB1   | 11             |           | 18 | PC0             |

| PB0   | 12             |           | 17 | PC1             |

| PC5   | 13             |           | 16 | PC2             |

| PC4   | 14             |           | 15 | PC3             |

|       |                |           |    |                 |

Figure 4. HC705P3 Pinout

| OSC1            | 1 <sup>●</sup> |        | 28 | RESET |

|-----------------|----------------|--------|----|-------|

| OSC2            | 2              |        | 27 | IRQ   |

| PB7             | 3              |        | 26 | PA0   |

| PB6             | 4              |        | 25 | ] PA1 |

| PB5             | 5              |        | 24 | PA2   |

| PB4             | 6              | 80     | 23 | PA3   |

| PB3             | 7              | HC05P8 | 22 | PA4   |

| PB2             | 8              | Ŕ      | 21 | PA5   |

| PB1             | 9              |        | 20 | PA6   |

| PB0             | 10             |        | 19 | PA7   |

| V <sub>DD</sub> | 11             |        | 18 | PD0   |

| V <sub>SS</sub> | 12             |        | 17 | PD1   |

| V <sub>RL</sub> | 13             |        | 16 | PD2   |

| V <sub>RH</sub> | 14             |        | 15 | PD3   |

Figure 5. HC05P8 Pinout

| RESET [<br> RQ _<br> PA7 [<br> PA6 [<br> PA5 ]<br> PA4 [<br> PA3 ]<br> PA2 [<br> PA1 ]<br> PA0 [<br> PB5 ] | 1●<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12 | HC05P15 | 28<br>27<br>26<br>25<br>24<br>23<br>22<br>21<br>20<br>19<br>18<br>17 | V <sub>SS</sub><br>V <sub>DD</sub><br>OSC1<br>OSC2<br>TCAP/PD7<br>TCAP/PD7<br>TCAP<br>PC0<br>PC0<br>PC1<br>PC2<br>PC2<br>PC3<br>PC4<br>PC5 |

|------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|---------|----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                            |                                                              |         |                                                                      |                                                                                                                                            |

| PB7 [<br>PWM1 [                                                                                            | 13<br>14                                                     |         | 16<br>15                                                             | ] PC6<br>] PWM0                                                                                                                            |

Figure 6. HC05P15 Pinout

The A Strategy The A strategy was introduced in the P Family and other families within the Motorola 8-bit microcontrollers portfolio to enhance the features that the device offers.

The A features include:

- Port A pullups

- High current drive capability on PC0 and PC1

- (EP)ROM security

#### Port A Interrupts/Pullups

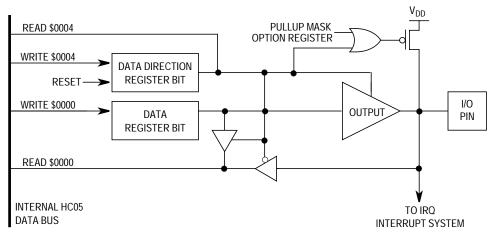

Port A has mask options to enable pullup devices and interrupt capability on each pin. **Figure 7** shows the port A setup.

Figure 7. Port A I/O and Interrupt Circuitry

High Current Drive<br/>on PC0, PC1The output current drive capability on port C bit 0 and bit 1 has been<br/>increased. Table 3 shows the differences between the non-A and A<br/>devices.

| Table 3 | . Port C Pin | 7 Characteristics |

|---------|--------------|-------------------|

|---------|--------------|-------------------|

| Characteristic                                                                                                                                                                    | Non-A            | P1A/P4A           | P9A/705P6A        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------------|-------------------|

| $V_{DD} = 5.0 V$ PC0, PC1 current drive (I <sub>OH</sub> )<br>@ V <sub>OH</sub> = V <sub>DD</sub> -0.8 V<br>PC0, PC1 current sink (I <sub>OL</sub> )<br>@ V <sub>OL</sub> = 0.4 V | 0.8 mA<br>1.6 mA | 5.0 mA<br>15.0 mA | 5.0 mA<br>10.0 mA |

| $V_{DD} = 3.0 V$ PC0, PC1 current drive (I <sub>OH</sub> )<br>@ V <sub>OH</sub> = V <sub>DD</sub> -0.3 V<br>PC0, PC1 current sink (I <sub>OL</sub> )<br>@ V <sub>OL</sub> = 0.3 V | 0.2 mA<br>0.4 mA | 1.5 mA<br>6.0 mA  | 1.2 mA<br>2.5 mA  |

#### (EP)ROM Security

Security has been incorporated into the P Family A devices to help prevent unauthorized reading of code in the (EP)ROM. On the ROM devices, this is fixed during manufacturing, not as a mask option on the ROM header.

On the HC705P6A, the security is enabled by setting bit 7 in the mask option register at address \$1F00.

**NOTE:** The only exception to this is the HC05P1A, which does not have ROM security.

| Changing from    | These conversions are discussed in this application note: |

|------------------|-----------------------------------------------------------|

| OTP/FLASH to ROM | • HC705P6A to HC05P6                                      |

- HC705P6A to HC05P7

- HC705P6A to HC05P8

- HC705P6A to HC05P1A

- HC705P6A to HC05P4A

- HC705P6A to HC05P9A

- HC705P9 to HC05P6

- HC705P9 to HC05P7

- HC705P9 to HC05P8

- HC705P9 to HC05P1A

- HC705P9 to HC05P4A

- HC705P9 to HC05P9A

- HC805P18 to HC05P18

#### HC705P6A to HC05P6

*Memory* The memory maps of the HC705P6A and the HC05P6 are identical.

Mask Options These options are chosen by manipulating bits in the mask option register(s) on the HC705P6A, but on the HC05P6 they are chosen when submitting ROM code to the factory via the mask option header.

- COP watchdog, enable/disable

- Stop, enable/disable

- SIOP, MSB/LSB

- IRQ sensitivity, edge or edge and level

*Functional Blocks* The HC705P6A and HC05P7 have these differences:

- The SIOP clock rate is software selectable on the HC705P6A, but on the HC05P7 the clock rate is fixed at 1/4 operating frequency.

- The HC705P6A has stop disable, port A pullups/Interrupts, EPROM security (mask programmable options) and PC0 and PC1 as high current ports. The HC05P7 does not have these functions.

- The HC705P6A has an A/D subsystem, and the HC05P7 does not.

- The HC05P7 has an optional RC oscillator, and the 7HC05P6A does not.

| HC705P6A<br>to HC05P8 |                                                                                                                                                                                                                        |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Memory                | The HC705P6A has 176 bytes RAM starting at address \$0050. The HC05P8 has 112 bytes starting at address \$0090.                                                                                                        |

|                       | The HC705P6A has 4656 bytes of ROM starting at address \$0100. The HC05P8 has 2048 bytes starting at address \$1680.                                                                                                   |

|                       | The HC05P8 has 32 bytes of EEPROM starting at address \$0030. This is not on the HC705P6A.                                                                                                                             |

| Mask Options          | These two options are chosen by manipulating bits in the mask option register(s) on the HC705P6A, but on the HC05P8 they are chosen when submitting ROM code to the factory via the mask option header.                |

|                       | COP watchdog, enable/disable                                                                                                                                                                                           |

|                       | <ul> <li>IRQ sensitivity, edge or edge and level</li> </ul>                                                                                                                                                            |

| Functional Blocks     | The HC705P6A and the HC05P8 have these differences:                                                                                                                                                                    |

|                       | <ul> <li>The HC705P6A has stop disable, port A pullups/interrupts,<br/>EPROM security (mask programmable options), and PC0 and<br/>PC1 as high current ports. The HC05P8 does not have these<br/>functions.</li> </ul> |

|                       | <ul> <li>An SIOP subsystem is on the HC705P6A. This is not present on</li> </ul>                                                                                                                                       |

• An SIOP subsystem is on the HC705P6A. This is not present on the HC05P8.

#### HC705P6A to HC05P1A

| Memory            | The HC705P6A has 176 bytes of RAM starting at address \$0050. The HC05P1A has 128 bytes starting at address \$0080.                                                                                  |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                   | The HC705P6A has 4656 bytes of EPROM. The HC05P1A has 2304 bytes. Both devices have their main user (EP)ROM starting at address \$0100.                                                              |

|                   | The HC705P6A and HC05P1A both have their user vector areas starting at \$1FF8.                                                                                                                       |

| Mask Options      | These options are chosen by manipulating bits in the mask option register(s) on the HC705P6A, but on the HC05P1A they are chosen when submitting ROM code to the factory via the mask option header. |

|                   | COP watchdog, enable/disable                                                                                                                                                                         |

|                   | Port A pullups/interrupts, enable/disable                                                                                                                                                            |

|                   | Stop, enable/disable                                                                                                                                                                                 |

|                   | IRQ sensitivity, edge or edge and level                                                                                                                                                              |

| Functional Blocks | The HC705P6A has these functions and the HC05P1A does not:                                                                                                                                           |

|                   | <ul> <li>A/D subsystem</li> </ul>                                                                                                                                                                    |

|                   | SIOP subsystem                                                                                                                                                                                       |

|                   | <ul> <li>EPROM security, mask programmable option</li> </ul>                                                                                                                                         |

|                   | The HC05P1A has an optional RC oscillator, and the HC705P6A does not.                                                                                                                                |

| HC705P6A<br>to HC05P4A    |                                                                                                                                                                                                      |  |

|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Memory                    | The HC705P6A and the HC05P4A have 176 bytes of RAM starting at address \$0050.                                                                                                                       |  |

|                           | The HC705P6A has 4656 bytes EPROM. The HC05P4A has 4144 bytes. Both devices have their main user EPROM starting at address \$0100.                                                                   |  |

|                           | The HC705P6A and HC05P4A both have the user vector area starting at address \$1FF8.                                                                                                                  |  |

| Mask Options              | These options are chosen by manipulating bits in the mask option register(s) on the HC705P6A, but on the HC05P4A they are chosen when submitting ROM code to the factory via the mask option header. |  |

|                           | COP watchdog, enable/disable                                                                                                                                                                         |  |

|                           | Port A pullups/interrupts, enable/disable                                                                                                                                                            |  |

|                           | SIOP, MSB/LSB                                                                                                                                                                                        |  |

|                           | <ul> <li>IRQ sensitivity, edge or edge and level</li> </ul>                                                                                                                                          |  |

| Functional<br>Differences | The HC705P6A has an A/D subsystem, and the HC05P4A does not.                                                                                                                                         |  |

|                           | The HC05P4A has an optional RC oscillator, and the HC705P6A does not.                                                                                                                                |  |

|                           | The HC705P6A has optional stop disable, and the HC05P4A does not.                                                                                                                                    |  |

|                           | The SIOP clock rate is software selectable on the HC705P6A, but on the HC05P4A the clock rate is fixed at 1/4 operating frequency.                                                                   |  |

#### HC705P6A to HC05P9A

| Memory            | The HC705P6A has 176 bytes RAM starting at address \$0050. The HC05P9A has 128 bytes starting at address \$0080.                                                                                     |  |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                   | There are 4656 bytes of EPROM on the HC705P6A and 2096 bytes of ROM on the HC05P9A. Both devices have their main user (EP)ROM starting at address \$0100.                                            |  |

|                   | The HC705P6A and HC05P9A both have their user vector areas starting at address \$1FF8.                                                                                                               |  |

| Mask Options      | These options are chosen by manipulating bits in the mask option register(s) on the HC705P6A, but on the HC05P9A they are chosen when submitting ROM code to the factory via the mask option header. |  |

|                   | COP watchdog, enable/disable                                                                                                                                                                         |  |

|                   | Port A pullups/interrupts, enable/disable                                                                                                                                                            |  |

|                   | Stop, enable/disable                                                                                                                                                                                 |  |

|                   | • SIOP, MSB/LSB                                                                                                                                                                                      |  |

|                   | IRQ sensitivity, edge or edge and level                                                                                                                                                              |  |

| Functional Blocks | The HC05P9A has an optional RC oscillator, and the HC705P6A does not.                                                                                                                                |  |

|                   | The SIOP clock rate is software selectable on the HC705P6A, but on the HC05P9A the clock rate is fixed at 1/4 operating frequency.                                                                   |  |

| HC705P9<br>to HC05P6 |                                                                                                                                                                                                    |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Memory               | The HC05P6 has 176 bytes of RAM starting at address \$0050. The HC705P9 has 128 bytes starting at address \$0080.                                                                                  |

|                      | The HC05P6 has 4656 bytes of ROM and the HC705P9 has 2096 bytes.<br>Both devices have their main user (EP)ROM starting at address \$0100.                                                          |

| Mask Options         | These options are chosen by manipulating bits in the mask option register(s) on the HC705P9, but on the HC05P6 they are chosen when submitting ROM code to the factory via the mask option header. |

|                      | COP watchdog, enable/disable                                                                                                                                                                       |

|                      | • SIOP, MSB/LSB                                                                                                                                                                                    |

|                      | IRQ sensitivity, edge or edge level                                                                                                                                                                |

| Functional Blocks    | The HC05P6 has optional stop disable, and the HC705P9 does not.                                                                                                                                    |

|                      | The HC05P6 has an optional RC oscillator, and the HC705P9 does not.                                                                                                                                |

|                      | The SIOP clock rate is software selectable on the HC05P6, but on the HC705P9 the clock rate is fixed at 1/4 operating frequency.                                                                   |

#### HC705P9 to HC05P7

| Memory               | The memory maps of the HC705P9 and the HC05P7 are identical.                                                                                                                                       |  |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Mask Options         | These options are chosen by manipulating bits in the mask option register(s) on the HC705P9, but on the HC05P7 they are chosen wh submitting ROM code to the factory via the mask option header.   |  |

|                      | COP watchdog, enable/disable                                                                                                                                                                       |  |

|                      | <ul> <li>IRQ sensitivity, edge or edge and level</li> </ul>                                                                                                                                        |  |

| Functional Blocks    | The HC705P9 has an A/D subsystem, but the HC05P7 does not.                                                                                                                                         |  |

|                      | The HC05P7 has an optional RC oscillator, but the HC705P9 does not.                                                                                                                                |  |

| HC705P9<br>to HC05P8 |                                                                                                                                                                                                    |  |

| Memory               | The HC705P9 has 128 bytes of RAM starting at address \$0080. The HC05P8 has 112 bytes starting at address \$0090.                                                                                  |  |

|                      | The HC705P9 has 2096 bytes of ROM starting at address \$0100. The HC05P8 has 2048 bytes starting at address \$1680.                                                                                |  |

|                      | The HC05P8 has 32 bytes of EEPROM starting at address \$0030. The HC705P9 does not have EEPROM.                                                                                                    |  |

| Mask Options         | These options are chosen by manipulating bits in the mask option register(s) on the HC705P9, but on the HC05P8 they are chosen when submitting ROM code to the factory via the mask option header. |  |

|                      | COP watchdog, enable/disable                                                                                                                                                                       |  |

|                      | IRQ sensitivity, edge or edge and level                                                                                                                                                            |  |

| Functional Blocks    | The HC05P9 has an SIOP subsystem, and the HC05P8 does not.                                                                                                                                         |  |

| HC705P9<br>to HC05P1A     |                                                                                                                                                                                                              |

|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Memory                    | The HC705P9 and the HC05P1A both have 128 byes of RAM starting at address \$0080.                                                                                                                            |

|                           | The HC705P9 has 2096 bytes of EPROM. The HC05P1A has 2304 bytes of ROM. Both devices have their main user EPROM beginning at address \$0100.                                                                 |

|                           | The HC705P9 and HC05P1A both have their user vector areas starting at address \$1FF8.                                                                                                                        |

| Mask Option               | These two options are chosen by manipulating bits in the mask option register(s) on the HC705P9, but on the HC05P1A the option is chosen when submitting ROM code to the factory via the mask option header. |

|                           | COP watchdog, enable/disable                                                                                                                                                                                 |

|                           | <ul> <li>IRQ sensitivity, edge or edge and level</li> </ul>                                                                                                                                                  |

| Functional<br>Differences | The HC05P1A has stop disable, port A pullups/interrupts, mask programmable options, and PC0 and PC1 as high current ports. The HC705P9 does not have these functions.                                        |

|                           | There is an A/D subsystem on the HC705P9, but it is not on the HC05P1A.                                                                                                                                      |

|                           | There is no RC oscillator option on the HC705P9, but it is an option on the HC05P1A.                                                                                                                         |

|                           | There is an SIOP subsystem on the HC705P9, but it is not present on the HC05P1A.                                                                                                                             |

#### HC705P9 to HC05P4A

| Memory            | The HC05P9 has 128 bytes of RAM starting at address \$0080. The HC05P4A has 176 bytes of RAM starting at address \$0050.                                                                            |  |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                   | There are 2096 bytes of EPROM on the HC705P9. On the HC05P4A, there are 4144 bytes. Both devices have their main user EPROM beginning at address \$0100.                                            |  |

|                   | The HC705P9 and the HC05P4A both have their user vector areas starting at address \$1FF8.                                                                                                           |  |

| Mask Options      | These options are chosen by manipulating bits in the mask option register(s) on the HC705P9, but on the HC05P4A they are chosen when submitting ROM code to the factory via the mask option header. |  |

|                   | COP watchdog, enable/disable                                                                                                                                                                        |  |

|                   | SIOP, MSB/LSB                                                                                                                                                                                       |  |

|                   | IRQ sensitivity, edge or edge and level                                                                                                                                                             |  |

| Functional Blocks | The HC05P4A has stop disable, port A pullups/interrupts (mask programmable options), ROM security, and PC0 and PC1 as high current ports. The HC705P9 does not have these functions.                |  |

|                   | There is an A/D subsystem on the HC705P9 that is not on the HC05P4A.                                                                                                                                |  |

|                   | The HC705P9 has no RC oscillator option, but it is an option on the HC05P4A.                                                                                                                        |  |

#### HC705P9 to HC05P9A

| Memory            | The HC705P9 and the HC05P9A both have:                                                                                                                                                              |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                   | <ul> <li>128 bytes of RAM starting at address \$0050</li> </ul>                                                                                                                                     |

|                   | <ul> <li>2096 bytes of ROM starting at address \$0100</li> </ul>                                                                                                                                    |

|                   | <ul> <li>User vector areas starting at address \$1FF8</li> </ul>                                                                                                                                    |

| Mask Options      | These options are chosen by manipulating bits in the mask option register(s) on the HC705P9, but on the HC05P9A they are chosen when submitting ROM code to the factory via the mask option header. |

|                   | COP watchdog, enable/disable                                                                                                                                                                        |

|                   | • SIOP, MSB/LSB                                                                                                                                                                                     |

|                   | IRQ sensitivity, edge or edge and level                                                                                                                                                             |

| Functional Blocks | The HC05P9A has stop disable, port A pullups/interrupts (mask programmable options), EPROM security, and PC0 and PC1 are high current ports. The HC05P9 does not have these functions.              |

There is no RC OSC option on the HC705P9, but it is an option on the HC05P9A.

#### HC805P18 to HC05P18

Memory The memory maps of the HC805P18 and the HC05P18 are identical.

Mask OptionsThese options are chosen by manipulating the bits in the mask option<br/>registers on the HC05P18, but on the HC05P18 they are chosen when<br/>submitting ROM codes to the factory via the mask option header.

- IRQ sensitivity, edge or edge and level

- SIOP, MSB/LSB

- SIOP clock rate

- COP watchdog, enable/disable

- Port A pullups/interrupts, enable/disable

*Functional Blocks* All functional blocks on the HC805P18 and the HC05P18 are identical.

Changing from Non-A to A Versions These conversions are discussed in this application note:

- HC05P1 to HC05P1A

- HC05P4 to HC05P4A

- HC05P9 to HC05P9A

- HC705P6 to HC705P6A

- HC705P9 to HC705P6A

| HC05P1<br>to HC05P1A | The HC05P1 and the HC05P1A have differences. For instance, the HC05P1A has:                                                                                                                                                                                                                                                                                      |  |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                      | <ul> <li>Port A pullups/interrupts, mask option</li> </ul>                                                                                                                                                                                                                                                                                                       |  |

|                      | <ul> <li>COP watchdog enable/disable, mask option</li> </ul>                                                                                                                                                                                                                                                                                                     |  |

|                      | <ul> <li>Stop conversion to halt mode, mask option</li> </ul>                                                                                                                                                                                                                                                                                                    |  |

|                      | <ul> <li>High current drive capability on PC0 and PC1</li> </ul>                                                                                                                                                                                                                                                                                                 |  |

|                      | <ul> <li>2304 bytes of ROM; HC05P1 has 2096 bytes</li> </ul>                                                                                                                                                                                                                                                                                                     |  |

|                      | To provide compatibility with the HC05P1, choose these mask options:                                                                                                                                                                                                                                                                                             |  |

|                      | Port A pullups disabled                                                                                                                                                                                                                                                                                                                                          |  |

|                      | COP watchdog disabled                                                                                                                                                                                                                                                                                                                                            |  |

|                      | Stop enabled                                                                                                                                                                                                                                                                                                                                                     |  |

| HC05P4<br>to HC05P4A | <ul> <li>HC05P4 and the HC05P4A have differences. The HC05P4A has:</li> <li>ROM security, transparent to user</li> <li>Mask programmable pullups/interrupts on port A, mask option</li> <li>High current drive capability on PC0 and PC1</li> <li>To provide compatibility with the HC05P4, choose this mask option:</li> <li>Port A pullups disabled</li> </ul> |  |

| HC05P9<br>to HC05P9A | <ul> <li>The HC05P9 and the HC05P9A have differences. For instance, the HC05P9A has:</li> <li>RC oscillator, mask option</li> <li>Port A pullups/interrupts, mask option</li> <li>Stop enable/disable, mask option</li> </ul>                                                                                                                                    |  |

|                      | <ul> <li>High current drive capability on PC0 and PC1</li> </ul>                                                                                                                                                                                                                                                                                                 |  |

• ROM security, transparent to user

To provide compatibility with the HC05P9, choose these mask options:

- Port A pullups disabled

- Stop enabled

- Internal OSC input should be crystal/ceramic resonator

HC705P6The HC705P6A is a pin-compatible upgrade of the HC705P6 with theseto HC705P6Aenhancements:

- EPROM/OTP secure mode added

- Keyboard interrupts and pullup options for port A lines

- Two high current drive pins added, PC0 and PC1

The HC705P6 mask option register (MOR) is located at \$1F00 and is used to control these options:

- COP watchdog, enable/disable

- IRQ sensitivity, edge or edge and level

- SIOP, MSB/LSB

- SIOP clock rate

- Stop, enable/disable

On the HC705P6A, two mask option registers (MOR) are at addresses \$1EFF and \$1F00.

\$1EFF controls whether port pullups/interrupts capability is enabled for each of the port A I/O lines. \$1F00 controls these options:

- COP watchdog, enable/disable

- IRQ sensitivity, edge or edge and level

- SIOP, LSB/MSB

- SIOP clock rate

- Stop, enable/disable

- EPROM security, enable/disable

The M68HC705P9PGMR programs 68HC705P6As without modification, using the same  $V_{PP}$  and following the same procedure as programming HC705P6s. If you are using a third party programmer, make sure you contact the manufacturer for a possible software upgrade to support programming HC705P6As.

MOROn both the HC705P6 and the HC705P6A, the mask option registerProgramming(MOR) is programmed in bootloader mode, using the hardware shown<br/>in the respective specifications.

On the HC705P6 the programming procedure is:

- 1. Write the desired data to the MOR.

- 2. Apply the programming voltage to the IRQ/V<sub>PP</sub> pin.

- 3. Set the MPGM (mask option register programming) bit in the EPROM programming register at address \$001C.

- 4. Wait for programming time, t<sub>EPGM</sub>.

- 5. Clear the MPGM bit.

- 6. Remove the programming voltage from the  $IRQ/V_{PP}$  pin.

The HC705P6A has no MPGM (mask option register programming) bit.

On the HC705P6A, the procedure is:

- 1. Set the ELAT (EPROM latch) bit in the EPROM programming register at address \$001C.

- Write the desired data to the desired MOR address, \$1EFF or \$1F00.

- 3. Set the EPGM (EPROM programming) bit in the EPROM programming register at address \$001C.

- 4. Wait for programming time, t<sub>EPGM</sub>.

- 5. Clear the ELAT and EPGM bits.

- 6. Remove the programming voltage from the IRQ/V<sub>PP</sub> pin.

AN1736 Rev. 1

HC705P9The HC705P6A is a pin-compatible upgrade of the HC705P9 with theseto HC705P6Aenhancements:

- RAM memory increased from 128 bytes to 176 bytes

- EPROM/OTP memory increased from 2096 bytes to 4656 bytes

- EPROM/OTP secure mode added

- Keyboard interrupts and pullup options for port A lines

- Two high current drive pins added, PC0 and PC1

- Stop enable/disable

- SIOP clock rate

The HC705P9 mask option register (MOR) is located at \$0900 and is used to control these options:

- COP watchdog, enable/disable

- IRQ sensitivity, edge or edge and level

- SIOP, MSB/LSB

The HC705P6A uses address \$0900 for EPROM/OTP program area. Two new mask option registers are used on the HC705P6A.

\$1EFF controls whether port pullups/interrupts capability is enabled for each of the port A I/O lines. \$1F00 controls these options:

- COP watchdog, enable/disable

- IRQ sensitivity, edge or edge and level

- SIOP, MSB/LSB

- SIOP clock rate

- Stop, enable/disable

- EPROM security, enable/disable

The M68HC705P9PGMR programs 68HC705P6As without modification, using the same  $V_{PP}$  and following the same procedure as programming HC705P9s. If you are using a third party programmer, make sure to contact the manufacturer for a possible software upgrade to support programming HC705P6As.

| MOR<br>Programming | On both the HC705P9 and the HC705P6A, the mask option register (MOR) is programmed in bootloader mode using the hardware shown ir the respective specifications. The procedures for both devices are identical.                                                                                                                                                                                                                     |  |  |  |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                    | <ol><li>Set the ELAT (EPROM latch) bit in the EPROM programming register at address \$001C.</li></ol>                                                                                                                                                                                                                                                                                                                               |  |  |  |

|                    | <ol> <li>Write the desired data to the desired MOR address, \$1EFF or<br/>\$1F00.</li> </ol>                                                                                                                                                                                                                                                                                                                                        |  |  |  |

|                    | <ol> <li>Set the EPGM (EPROM programming) bit in the EPROM<br/>programming register at address \$001C.</li> </ol>                                                                                                                                                                                                                                                                                                                   |  |  |  |

|                    | 10. Wait for programming time, t <sub>EPGM</sub> .                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

|                    | 11. Clear the ELAT and EPGM bits.                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|                    | 12. Remove the programming voltage from the $IRQ/V_{PP}$ pin.                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| Shrink Level       | The A parts are manufactured as 1.2 $\mu m$ technology or smaller, whereas the non-A parts are 1.5 $\mu m$ or 1.75 $\mu m$ technology.                                                                                                                                                                                                                                                                                              |  |  |  |

|                    | While the electrical and functional specifications of the device remain<br>unchanged, the EMC (electromagnetic compatibility) performance of a<br>device may change with package type, shrink level, ROM size, and type<br>of programmable memory (EPROM or ROM). Every new MCU should<br>be treated and tested independently. Sensible application design<br>guidelines should be used to minimize the noise presented to the MCU. |  |  |  |

Three application notes and one article, designed to help customers develop good EMC behavior into their applications, are available. The application notes can be ordered through Motorola channels as documents or can be found on the Worldwide Web at http://motorola.com.sps.

- Designing for Electromagnetic Compatibility with Single Chip MCUs, Motorola document order number AN1263/D

- Designing for Electromagnetic Compatibility with HCMOS MCUs, Motorola document order number AN1050

- System Design and Layout Techniques for Noise Reduction in MCU-Based Systems, Motorola document order number AN1259/D

The article *Fast Transients and Noise Susceptibility of 8-Bit Microcontroller Applications* can be found in the October/November 1996 issue of the publication "Embedded System Engineering" (Vol. 4, No. 6).

The HC05P18 and the HC805P18 are the only two non-A parts which are manufactured at 1.2  $\mu$ m technology.

#### Voltage, Frequency, and Temperature

**Table 4** provides the voltage, speed, and temperature specifications for the P Family of MCUs.

Temperature ranges are:

- 0 °C to +70 °C

- C = -40 °C to +85 °C

- V = -40 °C to +105 °C

- M = -40 °C to +125 °C

The high speed and low power options on the ROM devices are chosen at the time of submission of ROM code to the factory.

| Device       | Maximum bus<br>speed/voltage options                                                                                                                                                                                                                                                                                         | Temperature                                                                                     | Comments                                                        |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|

| MC68HC05P1   | $\begin{array}{c} V\pm10\%/2.1\ \text{MHz}\\ 3.3\ \text{V}\pm10\%/1\ \text{MHz}\\ 5\ \text{V}\pm10\%/4\ \text{MHz}\\ 3.3\ \text{V}\pm10\%/2.1\ \text{MHz}\\ 5\ \text{V}\pm10\%/2.1\ \text{MHz}\\ 2.4\ \text{V}\ \text{to}\ 3.6\ \text{V}/1\ \text{MHz}\\ 1.8\ \text{V}\ \text{to}\ 3.6\ \text{V}/0.5\ \text{MH} \end{array}$ | 0–70, C, V, M<br>0–70, C, V, M<br>0–70 only<br>0–70 only<br>0–70 only<br>0–70 only<br>0–70 only | High speed<br>High speed<br>Low power<br>Low power<br>Low power |

| MC68HC05P1A  | $\begin{array}{c} 5 \ V \pm 10\% \ / \ 2.1 \ MHz \\ 3.3 \ V \pm 10\% \ / \ 1 \ MHz \\ 5 \ V \pm 10\% \ / \ 4 \ MHz \\ 3.3 \ V \pm 10\% \ / \ 2.1 \ MHz \\ 5 \ V \pm 10\% \ / \ 2.1 \ MHz \\ 2.4 \ V \ to \ 3.6 \ V \ / \ 1 \ MHz \\ 1.8 \ V \ to \ 3.6 \ V \ / \ 0.5 \ MHz \end{array}$                                      | 0-70, C, V<br>0-70, C, V<br>0-70, C<br>0-70, C<br>0-70 only<br>0-70 only<br>0-70 only           | High speed<br>High speed<br>Low power<br>Low power<br>Low power |

| MC68HC05P3   | 5 V ± 10% / 2.1 MHz<br>3.3 V ± 10% / 1 MHz                                                                                                                                                                                                                                                                                   | 0–70, C, V<br>0–70, only                                                                        |                                                                 |

| MC68HC705P3  | 5 V ± 10% / 2.1 MHz<br>3.3 V ± 10% / 1 MHz                                                                                                                                                                                                                                                                                   | 0–70, C<br>0–70, C                                                                              |                                                                 |

| MC68HC05P4   | $5 V \pm 10\% / 2.1 MHz$<br>$3.3 V \pm 10\% / 1 MHz$<br>$5 V \pm 10\% / 4 MHz$<br>$3.3 V \pm 10\% / 2.1 MHz$<br>$5 V \pm 10\% / 2.1 MHz$<br>2.4 V to 3.6 V / 1 MHz<br>1.8 V to 3.6 V / 0.5 MHz                                                                                                                               | 0-70, C, V<br>0-70, C, V<br>0-70, C<br>0-70, C<br>0-70 only<br>0-70 only<br>0-70 only           | High speed<br>High speed<br>Low power<br>Low power<br>Low power |

| MC68HC05P4A  | $5 V \pm 10\% / 2.1 MHz$<br>$3.3 V \pm 10\% / 1 MHz$<br>$5 V \pm 10\% / 4 MHz$<br>$3.3 V \pm 10\% / 2.1 MHz$<br>$5 V \pm 10\% / 2.1 MHz$<br>2.4 V to 3.6 V / 1 MHz<br>1.8 V to 3.6 V / 0.5 MHz                                                                                                                               | 0–70, C, V<br>0–70, C, V<br>0–70, C<br>0–70, C<br>0–70 only<br>0–70 only<br>0–70 only           | High speed<br>High speed<br>Low power<br>Low power<br>Low power |

| MC68HC05P6   | 5 V ± 10% / 2.1 MHz<br>3.3 V ± 10% / 1 MHz                                                                                                                                                                                                                                                                                   | 0–70, C, V, M<br>0–70, C, V, M                                                                  |                                                                 |

| MC68HC705P6  | 5 V ± 10% / 2.1 MHz<br>3.3 V ± 10% / 1 MHz                                                                                                                                                                                                                                                                                   | 0–70, C<br>0–70, C                                                                              |                                                                 |

| MC68HC705P6A | 5 V ± 10% / 2.1 MHz<br>3.3 V ± 10% / 1 MHz                                                                                                                                                                                                                                                                                   | 0–70, C<br>0–70, C                                                                              |                                                                 |

# Table 4. Voltage, Speed, and Temperature Specificationsfor the P Family

| Device       | Maximum bus speed/voltage options          | Temperature                    | Comments |

|--------------|--------------------------------------------|--------------------------------|----------|

| MC68HC05P7   | 5 V ± 10% / 2.1 MHz<br>3.3 V ± 10% / 1 MHz | 0–70, C, V, M<br>0–70, C, V, M |          |

| MC68HC05P8   | 5 V ± 10% / 2.1 MHz<br>3.3 V ± 10%/ 1 MHz  | 0–70, C<br>0–70, C             |          |

| MC68HC05P9   | 5 V 10% / 2.1 MHz<br>3.3 V ± 10% / 1 MHz   | 0–70, C, V, M<br>0–70, C, V, M |          |

| MC68HC05P9A  | 5 V ± 10% / 2.1 MHz<br>3.3 V ± 10% / 1 MHz | 0–70, C, V, M<br>0–70, C, V, M |          |

| MC68HC705P9  | 5 V ± 10% / 2.1 MHz<br>3.3 V ± 10% / 1 MHz | 0–70, C<br>0–70, C             |          |

| MC68HC05P15  | 5 V ± 10% / 2.1 MHz                        | 0–70, C, V                     |          |