## AN1522

## Analog Phase Lock Loop for H4EPlus<sup>TM</sup> and M5C<sup>TM</sup> Series Arrays

Prepared by: Roy Jones

Edited by: Clarence Nakata, Nick Spence Application Specific Integrated Circuits Division, Chandler AZ

| ge |

|----|

| 1  |

| 1  |

| 5  |

| 7  |

| 15 |

| 16 |

| 18 |

| 19 |

| 21 |

| 22 |

| 23 |

|    |

#### 1 Introduction

This application note describes the implementation and use of an analog phase-locked loop, or APLL, which is available on two families of CMOS gate arrays offered by Motorola: the H4EPlus Series arrays and the M5C Series arrays.

Section 2 describes the various versions of the APLL which are offered as different library macros. This section also contains APLL performance data and signal descriptions, and shows the physical placement of the APLL on H4EPlus and M5C arrays.

Section 3 describes design considerations that should be taken into account when using the APLL.

Section 4 describes how the APLL Verilog simulation model works and how it is used for "system-mode" simulations (as opposed to "option release" simulations).

Section 5 describes Motorola's strategy for testing H4EPlus and M5C arrays that contain an APLL. A Motorolainternal test program is used to test the APLL itself, while user-supplied option release test vectors are used to test the remainder of the chip.

The Appendices provide general background information on the operation and use of the APLL.

#### 2 Feature Description

The APLL provides a capability to synchronize high speed interchip communication and / or synthesize on-chip clock signals, without the need for external filter components.

It can be used to synchronize high speed chip-to-chip transfers by cancelling out on-chip clock network insertion delay. Appendix A and Appendix B contain a comprehensive discussion and analysis of the use of Motorola's APLL to cancel out on-chip clock network insertion delay.

The APLL can also be used for on-chip frequency synthesis, which enables a slower/quieter backplane clock frequency to be multiplied up to the desired on-chip clock frequency. The APLL is provided as a macro is the design system. There are a number of variants, depending upon the technology, the system voltage and input signal type.

Table 1 APLL Macros

| Macro | Technology           | Analog<br>Power | FREF<br>Input Type |

|-------|----------------------|-----------------|--------------------|

| AP1   | H4EPlus <sup>1</sup> | 5 V             | CMOS               |

| APD1  | H4EPlus <sup>1</sup> | 5 V             | PECL               |

| APT1  | H4EPlus <sup>1</sup> | 5 V             | TTL                |

| APL1  | H4EPlus <sup>1</sup> | 3.3 V           | CMOS               |

| APDL1 | H4EPlus <sup>1</sup> | 3.3 V           | PECL               |

| APL1  | M5C                  | 3.3 V           | CMOS               |

| APDL1 | M5C                  | 3.3 V           | PECL               |

(1) On H4EPlus arrays which use both 3.3V and 5V power, the APLL I/O must be powered by the same voltage level as the array core.

PECL is defined as positive- or pseudo-ECL. Table 2 summarizes the performance of the H4EPlus and M5C APLL macros. The "Output Frequency Range" is the *linear* range of the VCO; its full range extends somewhat further. "Max clk tree delay" is the maximum delay that the APLL can handle in its feedback loop before going unstable.

Table 2 APLL Performance

|                                       | H4E       | M5C         |              |

|---------------------------------------|-----------|-------------|--------------|

|                                       | 3.3 V     | 5 V         | MDC          |

| Output Frequency Range                |           |             |              |

| FVCO (MHz)                            | 60 - 160  | 70 - 250    | 100 - 350    |

| FVCO_DIV2 (MHz)                       | 30 - 80   | 35 - 125    | 50 - 175     |

| Output Duty Cycle                     |           |             |              |

| FVCO                                  | 25% - 75% | 25% - 75%   | 25% - 75%    |

| FVCO_DIV2                             | 50%       | 50%         | 50%          |

| Loop Divider Value, N                 | 1 - 16    | 1 - 16      | 1 - 16       |

| Reference Frequency                   |           |             |              |

| Range (MHz)                           |           |             |              |

| Normal use:                           | 3.8 - 160 | 4.4 - 250   | 6.25 - 350   |

| On tester (N=8)                       | 7.5 - 20  | 8.75 - 31.2 | 12.5 - 43.75 |

| Phase Error                           |           |             |              |

| Single-Ended Inputs                   | 50ps      | 50ps        | 50ps         |

| PECL Differential Inputs              | 200ps     | 200ps       | 200ps        |

| Jitter                                | 200ps     | 200ps       | 200ps        |

| Max. Clock Tree Delay<br>(Worst-Case) | 25ns      | 20ns        | 20ns         |

| Max. Lock-Acquisition<br>Time         | 10µs      | 10µs        | 10µs         |

#### 2.1 APLL Macrocell Descriptions

Up to two APLLs can be used on an H4EPlus array, in the lower left and upper right corners where they are isolated from digital pwr/gnd/signal interconnects to minimize coupling of digital noise into the APLL. If only one APLL is used on an array, the APLL must reside in the lower left corner.

On M5C Series arrays, up to three APLLs can be used. If only one APLL is used, it must reside in the upper left corner. If two APLLs are used, they must reside in the upper left and upper right corners. If three APLLs are used, the only restriction is that there is no APLL in the lower left corner.

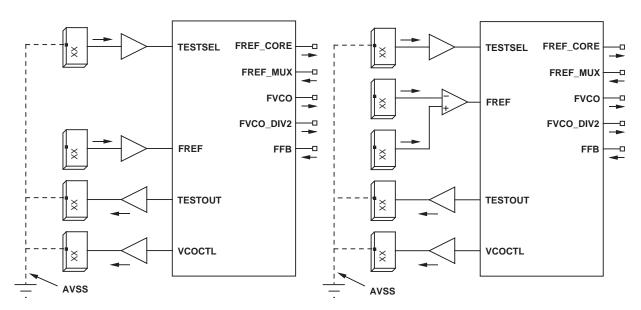

The APLL macro symbol is shown in Figure 1. All H4EPlus and M5C Series APLLs require the following six or seven pins (see Figure 2):

- AVDD: analog power

- AVSS: analog ground

- FREF: reference frequency input pin (also used by tester to clock the core logic)

- FREFB: reference frequency differential input pin (only required for PECL input versions)

- TESTSEL: configures the APLL for tester measurements

- TESTOUT: divided-down APLL output frequency for tester

- VCOCTL: for measuring VCO control voltage and charge pump current

TESTOUT, TESTSEL, and VCOCTL are dedicated test pins which must be grounded during normal system operation. The additional input pin, FREFB, is required if the reference frequency is a PECL differential clock. Each APLL also has the following five signals which interface to the array core:

- FREF\_CORE: output of FREF pin input buffer; drives FREF\_MUX directly, or through a PLLDELAY macro to cancel phase error due to a core divider (see Section 4.1)

- FREF\_MUX: phase detector reference frequency input

- FVCO: VCO output frequency

- FVCO\_DIV2: FVCO frequency divided by 2

- FFB: phase detector feedback frequency input

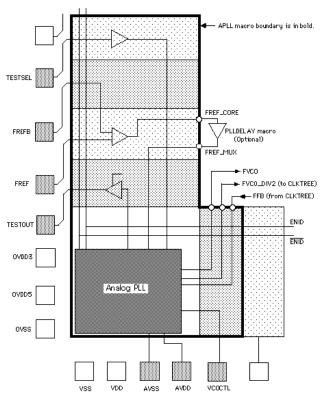

Figure 1 Analog PLL Macro Symbols (Single-ended and Differential Input versions)

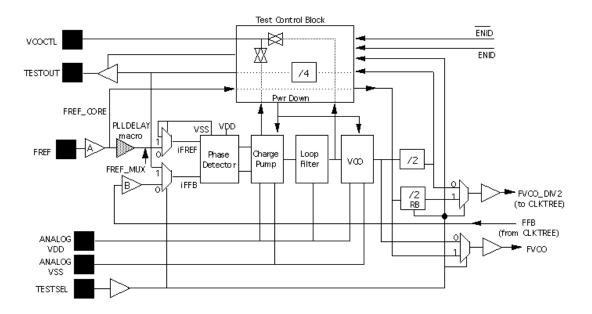

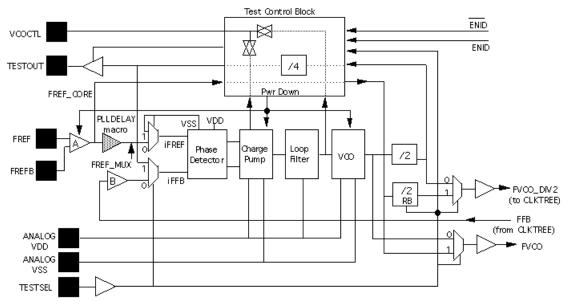

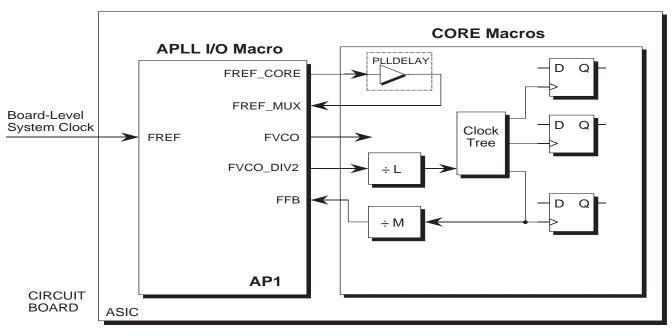

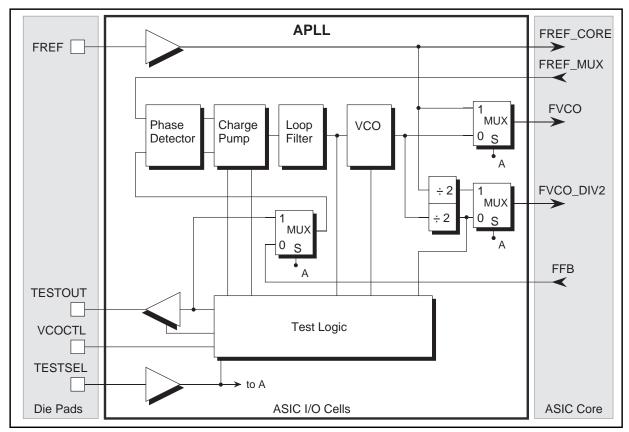

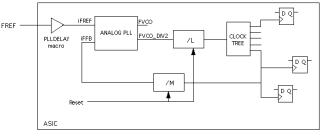

A block diagram representation for the APLL is shown in Figure 2 (CMOS or TTL single-ended input) and Figure 3 (PECL differential input).

The phase error between the FREF (and FREFB) input and the clock tree must be minimized in order to synchronize data transfer between devices. This is accomplished in two ways. Firstly the propagation delay of the input clock through buffer A is matched to the propagation delay of the feedback clock path through buffer B, and both paths include the same multiplexor gate design. Secondly, in the H4EPlus series the PLLDELAY macro can be placed in the array core between the APLL's FREF\_CORE output and FREF\_MUX input in order to prevent a core divider's propagation delay from adding to the phase error between the FREF pin and the clock tree (see Section 4.1). The PLLDELAY macro is matched to have the same delay as the CK to Q delay of a DFFRP macro.

No external components are required for filtering of the VCO control voltage.

Figure 2 Analog PLL Block Diagram (Single-Ended Input)

Figure 3 Analog PLL Block Diagram (PECL Differential Input)

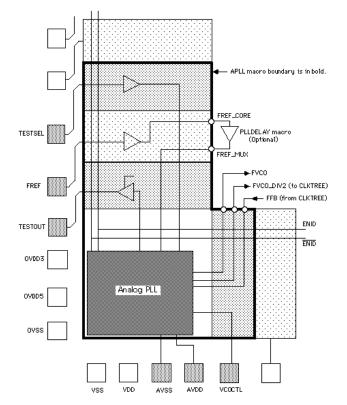

The physical layout for the APLL macro is shown in Figure 4 (single-ended input) and Figure 5 (differential input), for placement in the lower left corner of the die. The layout is similar but rotated for APLL placement in the other corners. The APLL macro covers the corner and also four adjacent I/O sites (five I/O sites if FREF is a PECL input). Accordingly, the pad locations are fixed for the APLL I/O signals.

The Manufacturing Rules Verification (MARV) program contained in Motorola's OACS<sup>™</sup> system checks that the designer has made correct pin assignments for the APLL I/O.

Figure 4 Analog PLL Layout (CMOS or TTL Input)

Figure 5 Analog PLL Layout (PECL Input)

#### 3 Design Considerations

#### 3.1 APLL Application

Figure 6 contains a typical application of the APLL. The divider blocks ( $\div$  L and  $\div$  M) are used to adjust for desired clock frequencies and to center the APLL FVCO and FVCO\_DIV2 outputs in the linear region of the VCO as described in Appendix E.

The PLLDELAY macro is a delay element for matching the delay of the M divider block when M > 1.

As an example, assume a 5.0 Volt core, and a 40 MHz clock tree is desired. With an input reference frequency of 20 MHz, L = 2 and M = 2.

By selecting N = 8,  $(2 \times 2 \times 2)$ , the FVCO\_DIV2 is forced to 80 MHz. This is approximately the middle of the operation frequency range, since the FVCO\_DIV2 range is between 35 and 125 MHz. (In this example, macro PLLDELAY is used to adjust delay times.)

Figure 6 Clock Distribution with APLL

#### 3.1.1 APLL Operation

Figure 7 contains a block diagram of the APLL macro. Basically, the APLL is a classical second order system that compares the phase of the input reference clock (FREF) with the phase of the feedback signal (FFB), and adjusts the phase of the FFB signal to be locked in phase and frequency with the FREF signal. It uses a type IV phase/frequency detector that sends correction pulses to a charge pump. The charge pump, based on the correction pulses, either adds or subtracts charge from the on-chip passive loop filter, thereby altering the control voltage of the VCO. The VCO, in turn, produces a different phase and frequency which is feedback to the phase detector. Correction pulses are generated until the APLL is locked. Frequency multiplication is easily implemented by putting a digital divider in the feedback path.

#### 3.1.2 APLL Power Supply

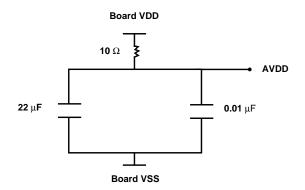

A separate analog power supply is not necessary to provide power to an APLL; however, to improve APLL jitter performance, the analog AVDD and AVSS pins must be noise free. The ideal noise rejection circuitry is design/board environment dependent. The following two schemes are recommended as possible solutions.

Figure 7 APLL Block Diagram

#### 3.1.2.1 Isolation Scheme 1

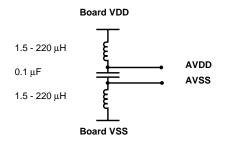

Figure 8 shows an analog isolation scheme 1 which can be effective in most applications.

Figure 8 Analog Isolation Scheme 1

The inductors are necessary to ensure low jitter (<600 ps) operation in a digital environment. The VCO has a gain of approximately 250 MHz/V. It is sensitive to any noise on the power and ground planes. Surface mount inductors were

used on production boards to successfully isolate the analog portion from a noisy digital environment with long-term jitter being less than +300 ps.

A range of inductor values (1.5 --  $220 \mu$ H) was specified since it is impossible to predict the magnitude and frequency of noise present in every system. Surface mount inductors with identical footprints are available in this range of values from several vendors. Several inductor manufacturers and respective part numbers are listed in Table 3

In addition to the 0.1  $\mu F$  bypass capacitor shown in the analog isolation diagram, there should be a 0.1  $\mu F$  bypass capacitor between each of the other (digital) four V<sub>CC</sub> pins and the board ground plane. This will reduce output switching noise caused by the ASIC outputs, in addition to reducing potential for noise in the "analog" section of the chip. These bypass capacitors should also be tied as close to the 88915 package as possible.

| Inductor<br>Manufacturer | Part<br>Number       | Inductance | Self Resonant<br>Frequency | Footprint (W x L x H)      | Telephone<br>Number |

|--------------------------|----------------------|------------|----------------------------|----------------------------|---------------------|

| Coilcraft                | 1812CS-822           | 8.2 μH     | 80 MHz                     | 0.15 x 0.195 x 0.135 (in)  | (708) 639-6400      |

| Coilcraft                | 1812LS-224           | 220 μH     | 6 MHz                      | 0.15 x 0.195 x 0.135 (in)  |                     |

| Dale                     | IMC-1812 1.5 H ± 10% | 1.5 μH     | 70 MHz                     | 0.126 x 0.177 x 0.126 (in) | (605) 665-9301      |

| Dale                     | IMC-1812 220 H ± 10% | 220 μH     | 4 MHz                      | 0.126 x 0.177 x 0.126 (in) |                     |

| Toko                     | 380LB-1R5K           | 1.5 μH     | 75 MHz                     | 2.5 x 3.2 x 2.2 (mm)       | (708) 297-0070      |

| Toko                     | 380HB-221K           | 220 μH     | 3.9MHz                     | 2.5 x 3.2 x 2.2 (mm)       |                     |

| Murata-Erie              | LQH3C2RM03M00-01     | 2.2 μH     | 64 MHz                     | 2.5 x 3.2 x 2.0 (mm)       | (404) 436-1300      |

| Murata-Erie              | LQH3C221K03M00-01    | 220 μH     | 6.8 MHz                    | 2.5 x 3.2 x 2.0 (mm)       |                     |

Table 3 Inductor Manufacturers, Part Numbers, and Selected Specifications

#### 3.1.2.2 Noise Filter Scheme 2

Figure 9 shows a noise filter scheme 2 associated with the analog VDD port.

For both schemes suggested, the components involved should be tied as close to the associated analog pin(s) as possible.

Figure 9 Noise Filter Scheme 2

#### 4 APLL Modelling for Simulation

#### 4.1 Overview

Figure 10 is a generic block diagram showing clock distribution using an APLL. Either or both of the divide-by-L and divide-by-M may be used. If used, they reside in the array core. The phase detector reference frequency iFREF is actually an internal signal in the APLL. As shown in Figure 2 and Figure 3, iFREF drives directly into the phase detector and is delayed from the APLL's FREF\_MUX input port by a mux prop delay. Similarly, iFFB is actually an APLL internal signal which connects directly to the phase detector and is delayed from the APLL's FREF provide the prop delay through a buffer and a mux. These mux and buffer delays are such that

when the APLL has phase-locked iFFB to iFREF, then the FREF pin will be phase-locked to the clock tree output, which is the ultimate objective. A special PLLDELAY macro can be used to cancel phase error between the clock tree and FREF which is caused by the divide-by-M. The PLLDELAY macro has the same delay as the CK->Q of a resetable flip-flop, therefore if a divide-by-M is used it should be designed using resetable flip-flops.

Note: Use of another divider in place of the PLLDELAY macro is not supported. The Motorola-internal vectors used to test the APLL in silicon require that the frequency at iFREF be the same as the frequency at the FREF pin. See Section 5 for details of the test strategy for APLL arrays.

The feedback loop between the VCO and phase detector resides in the array core, external to the APLL, and contains the clock tree and possibly a frequency divider, which will be referred to as the core divider. If a core divider exists it typically would follow the clock tree as does the divide-by-M. However the core divider could also precede the clock tree, as does the divide-by-L, if the clock tree is to be driven by a frequency lower than the minimum possible FVCO\_DIV2 from the APLL. A third possibility is that the core divider is composed of both the divide-by-L and divide-by-M.

Figure 10 Clock Distribution Using an Analog PLL

In addition to generating the VCO frequency FVCO, the APLL contains a divide-by-2 to generate FVCO\_DIV2, which has a 50% duty cycle. FVCO\_DIV2 typically is the signal used to drive the clock tree, where FVCO is available for fast-

er clocking of a small, localized block of logic. Therefore, throughout this document it is assumed that the clock tree is driven by FVCO\_DIV2 rather than FVCO. In this case, FVCO gets divided by 2 (within the APLL itself) and then divided again by the core divider, if one exists, before arriving at the phase detector feedback input FFB. The product of these two divider values equals the *loop divider* value "N." The APLL model measures the reference frequency iFREF and the loop divider value N and generates VCO frequency required for phase-lock, FVCO = N x iFREF. The phase of FVCO\_DIV2 compensates for the clock tree plus core divider delay in the core feedback loop such that the output of the clock tree is in phase with the board reference clock at the FREF pin.

In its default mode, the model acquires phase-lock approximately 20 cycles after the start of iFREF (or after reset of the core divider eliminates its 'X' state at simulation startup). However, if the user prefers, the model can also be set-up to emulate the actual time required by the APLL to achieve phase-lock in the real-world. During this "acquisition delay" the model puts out a constant (but not phase-locked) VCO frequency, which will change abruptly to the phase-locked frequency FVCO = N x iFREF after 10us has expired. Other than accurate acquisition delay, this behavior does not model the true transient response of the APLL. However, what is important is accurate modeling of the APLL's steady-state performance after phase-lock has been achieved.

The model generates FVCO and FVCO\_DIV2 such that after phase-lock is achieved the clock signal fed back to the phase detector, iFFB, has the specified worst-case phase error relative to the phase detector reference clock, iFREF. The user can select this steady-state phase error to be leading, lagging, or randomly jittering between the two as described in Section 4.6. The model also does a variety of checks for such things as loss of phase-lock, the FVCO frequency required is out of range, etc.

The Verilog model emulates the APLL only during system simulations and not during option release simulations, which generate test vectors used for testing of parts. The reason is that the APLL is inactive during tester application of option release test vectors, which verify all circuitry except for the APLL. Consequently, during option release simulations the clock applied at the APLL's FREF pin will bypass the APLL and drive the core directly. For information on how to control the APLL during option release simulations, as well as information on how the APLL is verified on the tester, see Section 5, "Test Strategy for APLL Arrays."

#### 4.2 Initialization/Reset of Dividers

When an APLL array is on a board in a system, it is unnecessary to reset the two dividers in Figure 10. However, during *system-mode simulation* these dividers must be initialized to a known state before the FREF and FVCO clocks can propagate to phase detector inputs iFREF and iFFB, respectively. Unfortunately, prior to phase-lock, FVCO and FVCO\_DIV2 have no fixed timing relationship with respect to the chip's input pins. Consequently, trying to do a synchronous hardware initialization/reset of the core divider may be difficult to do without generating timing violations, such as a reset recovery time violation. A more practical approach during system-mode simulations *(but not option release simulations)* would be to use the Verilog "force" and "release" commands to initialize the states of the flip-flops in the core divider. This can be done by "forcing" the D inputs of the divider flops to known states until FVCO starts, at which time these states will get clocked into the flops. When "release" occurs the flops are released to function normally. "Release" can occur at any time with respect to the arrival of clock edges at the core divider without causing the divider state to go unknown.

Alternatively, an asynchronous set/reset of the dividers can be done via chip logic or a pin at simulation start-up, *before the iFREF clock starts toggling*, since the model will not generate an FVCO clock until iFREF starts to toggle. In this way an asynchronous set or reset of all dividers can be done without generating timing violations.

#### Note: The reset signal for these dividers cannot be shared with any circuitry that must be reset after phaselock is acquired, since resetting the APLL's dividers would cause the APLL to lose phase-lock.

Artificial initialization of the core dividers using "force" and "release" can be used for system-mode simulations *but not for option release simulations*, where simulation output states must match chip output states on the tester. By driving the clock tree, the divide-by-L in Figure 10 affects chip output states. Therefore *during option release simulations* the divide-by-L must be initialized/reset via chip logic or a pin, and not by using "force" and "release." The same is true of the divide-by-M if it is made observable at an output pin in order to test it. If the divide-by-M drives only FFB then it affects no output pin during option release simulations and is therefore not testable (since the APLL is inactive). In this case it need not be initialized. The divide-by-M still needs to be initialized/reset during system-mode simulations, however.

#### 4.3 Acquisition Mode

The APLL model starts in acquisition mode at simulation start-up. It measures the frequency of the phase detector reference clock, iFREF, as well as the loop divide-by-N in order to calculate the required VCO lock frequency FVCO = iFREF x N. The model starts generating an FVCO clock which has an arbitrary phase relationship to iFREF. The resulting feedback clock at the phase detector, iFFB, has an initial phase error with respect to iFREF. The model measures this phase error and corrects the phase of FVCO such that iFFB will be in phase with iFREF, producing phase-lock.

At the start of simulation the model waits for a clock signal to appear at iFREF, and then measures the period of iFREF by keeping track of the time between successive iFREF rising edges. The model now starts generating FVCO and FVCO\_DIV2, where FVCO is the center frequency of the VCO. While the VCO free-runs, the model waits until the state at iFFB is no longer 'X,' indicating that the core divider has been initialized to a known state as described previously. The model then waits until a 0->1 rising edge occurs at iFFB (as opposed to an X->1 rising edge), indicating that the core divider has been released to function normally after having been initialized/reset.

When the second iFFB rising edge occurs the model measures the frequency at iFFB and calculates the loop divider ratio 'N', where N = FVCO frequency/(iFFB frequency). If N is not within the specified range for the APLL macro used (see Section 2), the model stops the simulation after printing a message to the effect that the user must modify the loop divider circuitry such that N does lie within the specified range. If N is within the specified range but iFREF x N = FVCO is not within the specified frequency range for the VCO, the user must modify FREF and/or N such that FVCO does lie within the VCO's range. To modify N, circuitry in the array core must be changed; however, FREF can be modified interactively during Verilog simulation as described in Section 4.6. If iF-REF x N = FVCO is, in fact, out of the VCO's range the model will now return to the start of the acquisition mode. Otherwise operation proceeds as follows.

Once a "legal" loop divider ratio N has been determined, the following information is printed to the screen:

- Loop divider value, N

- Phase detector reference frequency, iFREF

- VCO frequency, FVCO

- VCO/2 frequency, FVCO\_DIV2

- Duration of FVCO high and low pulses (FVCO duty cycle, effectively)

Then a series of pulses is generated at FVCO for use in measuring the propagation delay through the feedback loop, which is equal to the sum of the clock tree propagation delay and loop divider propagation delay.

This is done in order to verify that the loop delay is not so large as to cause the APLL to go unstable and never acquire phase-lock. After generating an FVCO pulse the model waits long enough to see if the FVCO pulse causes a rising edge at iFFB. It will take anywhere from 1 to N FVCO pulses to generate a rising edge at iFFB, depending on the initial state of the loop divider. When a rising edge does occur at iFFB, the loop delay is measured as the time delay between the rising edge at iFFB and the last FVCO rising edge. If the loop delay is larger than the specified limit, the model prints a message to that effect and stops the simulation to allow the clock tree or loop divider to be re-designed. Otherwise the model will now begin its 10us acquisition delay, as described in Section 4.1. At the end of this delay, the VCO stops long enough for the clock tree to empty of all pulses generated by the free-running VCO during the acquisition delay. (If the APLL was not set-up to emulate the real-world acquisition delay, the model will skip down to this point if the feedback loop delay measured was within spec.) The APLL model now waits for the next rising edge of iFREF to start generating N cycles of the VCO lock frequency FVCO = iFREF x N. N cycles of FVCO span a complete cycle of iFREF, and the last of these N FVCO cycles should produce the next rising edge at iFFB (due to the state in which the loop divider was left after the loop delay was measured). The rising edge of the first of these N FVCO cycles is delayed from the iFREF rising edge by the "VCO\_offset" such that the resultant iFFB rising edge

is aligned with a subsequent iFREF rising edge (within the APLL's specified phase error), producing phase-lock. The model calculates the VCO\_offset using the previously measured feedback loop delay.

If the N<sup>th</sup> FVCO pulse does not produce a rising edge at iFFB, something's probably wrong with the core divider; for example, it may have been disabled or reset. In this case, the APLL will print an error message to that effect and then restart its acquisition routine to try again to acquire phase-lock. If, on the other hand, phase-lock has indeed been acquired, the following information is printed to the screen:

- Time at which phase-lock was acquired.

- APLL steady state phase error at iFFB with respect to iFREF.

Now the APLL model goes into tracking mode.

#### 4.4 Tracking Mode

Whenever a rising edge occurs on iFREF, the model measures the time difference between this edge and the associated rising edge on iFFB. If this "phase error" is less than the specified worst-case phase error of the APLL, then the APLL is still in lock. In this case the model will generate the next N FVCO cycles in the manner described previously in Section 4.3, in order to produce the next rising edge on iFFB. However if the phase error between iFREF and iFFB is greater than the specified worst-case phase error of the APLL, lock has been lost. In this case the model prints a "loss-of-lock" message which includes the simulation time at which lock was lost. The model waits long enough for the clock tree to empty of all 'pipelined' FVCO pulses, and then returns to acquisition mode to try to re-acquire phase-lock.

#### 4.5 Initialization of APLL Simulation Parameters

For best accuracy, Verilog simulations involving APLL's in system mode should be done with the following timescale setting: `timescale lns/lps

Therefore the timescale statement in the *asic\_verilog* 'verilog.control' file should be changed to 1ps resolution, as shown above. For option-release simulations, the timescale can be left at the default value of 10ps.

In addition, there are four user-settable parameters whose range of values are hard-coded inside the APLL Verilog model because they cannot be specified in the Standard Delay Format (SDF) *verilog.timing* file output by DECAL. These parameters are:

- jitter -- determines whether iFFB will always lead, always lag, or randomly jitter between leading and lagging with respect to iFREF. The amount of lead or lag is always equal to the APLL's maximum steadystate phase error. Valid values for *jitter* are "lead", "lag" or "random". The default value is "random".

- **use\_silicon\_delay** -- determines whether the model will emulate the real-world APLL acquisition delay (described in Section 4.1). Valid values for *use\_silicon\_delay* are "yes" or "no". The default value is "no".

- vco\_duty\_cycle -- determines the duty-cycle of the FVCO output for this simulation. Valid values for vco\_duty\_cycle are "min", "typ" or "max". The default value is "min".

- *ptv* -- determines whether the best-, typical-, or worst-case process/temperature/voltage (PTV) value is to be used for the *maximum feedback loop delay*. Valid values for *ptv* are "bst", "typ" or "wst". The default value is "wst".

These four parameters are used only during system-mode simulations. They are not used during option release simulations, during which the FREF input clock bypasses the APLL and drives the clock tree directly. (See Section 4 for details regarding option release simulations.)

In a non-interactive simulation, the value used for *maximum feedback loop delay* is determined by one of the following Verilog command line "plus arguments": +mindelays, +typdelays or +maxdelays. Therefore if the OACS tool *asic\_verilog* is used, the *maximum feedback loop delay* value will be chosen automatically according to the PTV conditions selected for the array; the *ptv* parameter is ignored. However in an interactive simulation, the *maximum feedback loop delay* value is determined by assigning the *ptv* parameter a value of "bst", "typ" or "wst". In this case the designer must set the *ptv* parameter value to match the PTV conditions chosen for the array. Otherwise the value for *maximum feedback loop delay* may be for a different PTV condition than that used for the rest of the array.

The FVCO\_DIV2 output has a 50% duty cycle, but the FVCO duty cycle can vary over a wide range. Designs which use the APLL's FVCO output, system-mode simulations should be done at the following four sets of conditions:

i) PTV = best-case, vco\_duty\_cycle = "min"

ii) PTV = best-case, vco\_duty\_cycle = "max"

iii) PTV = worst-case, vco\_duty\_cycle = "min"

iv) PTV = worst-case, vco\_duty\_cycle = "max"

Because of the way that the APLL model generates "random" jitter, it is possible that the model will falsely swallow low-going FVCO pulses when *vco\_duty\_cycle* = "max", if the FVCO is operating at the upper end of its frequency range. These two conditions, coupled with random jitter, can combine to make the low-going FVCO pulses narrow enough that they get swallowed by the FVCO output buffer within the APLL model. In such cases, if FVCO is used in the design then the *jitter* parameter must be restricted to values of "lead" or "lag".

The user can assign a value to a particular parameter by putting a 'defparam' statement in the HDL stimulus file, such as:

```

defparam stim.cell1.\TC_TOP/APLL.448P_4

.core_apll.ptv = "wst";

```

The pathname is taken from a real design named "TC\_TOP." "stim" is the name of the module which applies

stimulus to "TC\_TOP", "cell1" is the name of the instantiation of "TC\_TOP" within module "stim", "\TC\_TOP/APLL.448P\_4" is the instance name generated by the OACS NETLIST tool for the APLL macro used in "TC\_TOP", and *core\_apll* is the sub-module within the APLL Verilog model in which the *ptv*, *jitter*, *vco\_duty\_cycle*, and *use\_silicon\_delay* parameters are defined. Note that in this particular design a space is required after the APLL instance name because its first character is a backslash. Similar statements can be used to assign values to the *jitter*, *vco\_duty\_cycle* and *use\_silicon\_delay* parameters, for example:

```

defparam stim.cell1.\TC_TOP/APLL.448P_4

.core_apll.jitter = "lead";

defparam stim.cell1.\TC_TOP/APLL.448P_4

.core_apll.vco_duty_cycle="max";

defparam stim.cell1.\TC_TOP/APLL.448P_4

.core_apll.use_silicon_delay="yes";

```

Alternatively, these four parameters can be changed "on the fly" within an interactive Verilog run if the designer wishes to re-simulate without having to re-compile. If such a resimulation is to be at a different PTV, the *ptv* parameter must be changed accordingly. The following interactive Verilog commands show how to change these parameters prior to a re-simulation (">" represents the Verilog prompt in interactive mode):

```

> $reset;

> $scope(stim.cell1.\TC_TOP/APLL.448P_4

.core_apll);

> ptv = "wst";

> jitter = "lead";

> vco_duty_cycle = "max";

> use_silicon_delay = "yes";

>.

```

The designer may even want to change one of these three parameters prior to the first simulation after compilation. If so, a *\$stop* command could be included at the start of the HDL stimulus to cause Verilog to stop at time zero and give a ">" prompt. At this time the designer can enter the same interactive Verilog commands shown above, although in this case the *\$reset* command is unnecessary. Alternatively, 'defparam' statements can be put in the HDL stimulus file, as described previously.

This same method can be used to change FREF interactively if necessary. If the VCO frequency FVCO = iFREF x N is out of the APLL's range, the APLL model prints a message to the screen stating that iFREF and/or N must be changed. Referring to Figure 10, changing N

$(N = L \times M)$  requires a circuit change. However if the designer chooses to change only FREF, he can do so by scoping into his HDL stimulus module and updating the FREF period parameter.

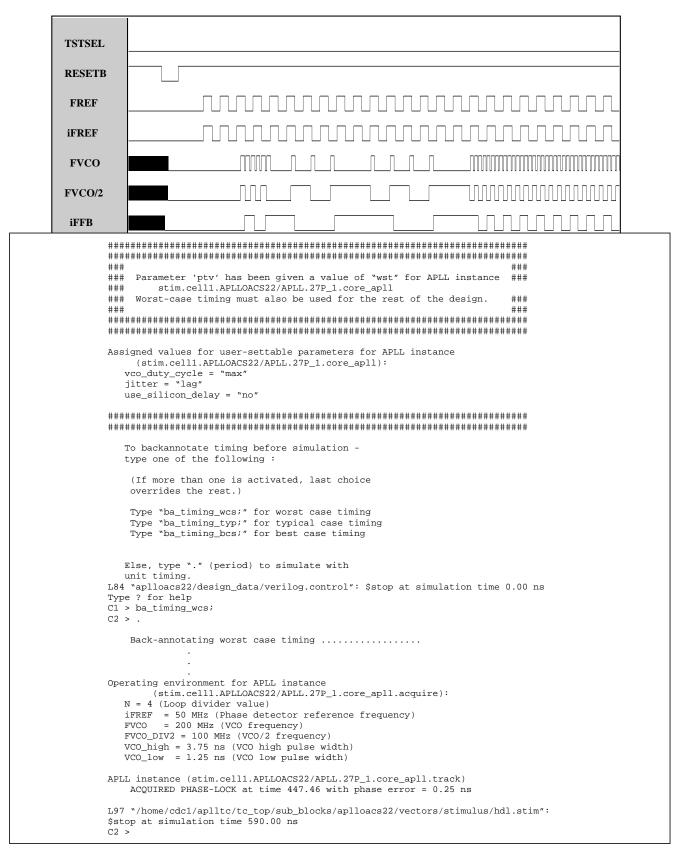

#### 4.6 Example Simulations of an APLL

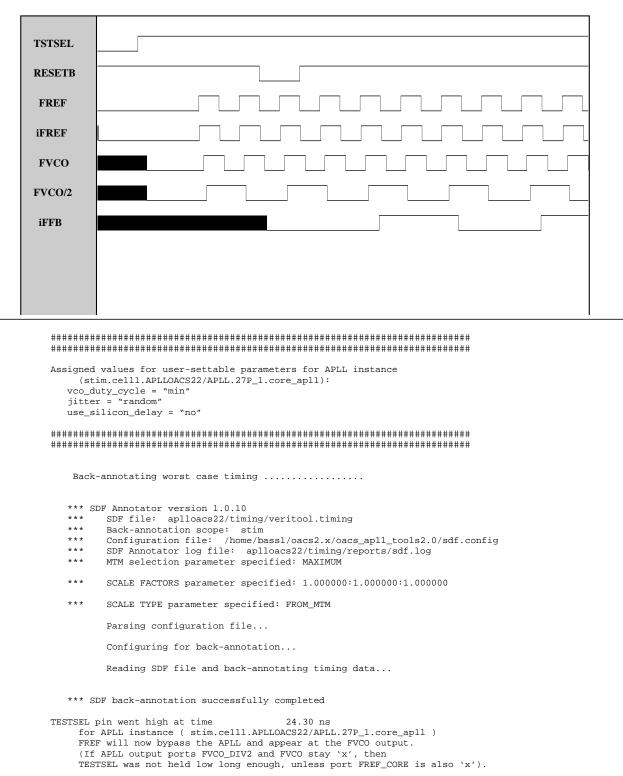

Figure 11 shows the Verilog graphical waveforms for an interactive system mode simulation using an APLL. Also shown is a portion of the transcript window containing messages printed out by the APLL model. For this simulation, the

APLL model has been set-up to <u>not</u> emulate the real-world acquisition delay of the APLL. Note that the TSTSEL waveform, which corresponds to the TESTSEL input on the APLL, is held low throughout the simulation. (For an option release simulation, TSTSEL = TESTSEL would be taken <u>high after</u> the first test cycle, and held high throughout the rest of the simulation. See Section 5.1, "Testing the Array Core".) Referring to Figure 10, at simulation start-up the APLL is configured with L = 1 and M = 2.

In this example, the divide-by-M is reset by a RESETB signal (top waveform in Figure 11) rather than by the "force" and "release" commands, which were previously described in Section 4.6. While the divide-by-M is held in reset iFFB remains low.

Initially, FVCO and FVCO\_DIV2 are unknown, as is FFB prior to reset of the loop divider. The loop divider consists of a divide-by-2 flip-flop in the array core along with the flip-flop internal to the APLL which divides FVCO down to FVCO\_DIV2. When RESETB goes active the loop divider state becomes known, at which time the APLL model outputs a low on both FVCO and FVCO\_DIV2. Now the loop divider's reset signal, RESETB, can return to its inactive state, since there is no longer an 'x' at the clock input to the loop divider. Since FVCO and FVCO\_DIV2 will start toggling as soon as FREF starts toggling, FREF is not started until after RESETB goes inactive in order to prevent reset recovery time violations in the loop divider (discussed in Section 4.2).

The APLL model waits for the first two iFREF pulses to determine the frequency of iFREF and to start generating FVCO\_mid and FVCO\_mid/2, where FVCO\_mid is the VCO center frequency. The model waits for feedback pulses at iFFB. After the second iFFB rising edge, the model measures the iFFB frequency and calculates the loop divider value.

N = FVCO\_max/(iFFB frequency). N is then used to calculate the in-lock VCO frequency:

FVCO = iFREF x N. N, iFREF, FVCO, and FVCO\_DIV2 are printed to the screen, as well as the high and low pulse widths of FVCO (FVCO duty cycle, effectively). At this point the model stops generating FVCO long enough for the clock tree to empty of all pulses. After this pause the model starts generating individual FVCO pulses and looking for a rising edge to result at iFFB. In this example it takes 3 FVCO pulses to cause the next rising edge on iFFB, due to the initial state of the loop divider. These three pulses are followed by N additional FVCO pulses (N happens to be four in this case) to verify that N more FVCO pulses will cause another iFFB rising edge at the expected time. At this point the model starts generating the in-lock frequency FVC0 = N x iFREF, with the proper phase such that the next rising edge of iFFB will be phase-locked to iFREF.

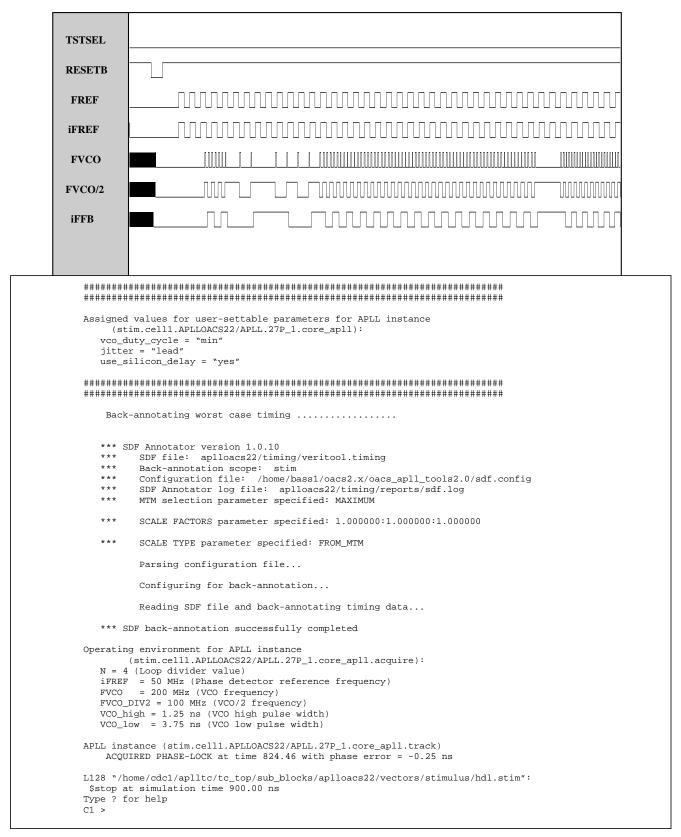

Figure 7 shows Verilog graphical waveforms and part of the transcript window for a non-interactive system mode simulation in which the APLL model has been set-up to emulate the real-world acquisition delay of the APLL. (Section 4.5 explains how to do this.) For this example simulation, the acquisition delay was shortened in order to fit the waveforms on the page. At the end of the acquisition delay the model stops generating the VCO center frequency at FVCO and waits long enough for the clock tree to empty of all pulses. After this pause the model starts generating the in-lock frequency  $FVC0 = N \times iFREF$ , with the proper phase such that the next rising edge of iFFB will be phase-locked to iFREF.

Figure 8 shows Verilog graphical waveforms and part of the transcript window for the start of an option release simulation using an APLL. Note that the TSTSEL waveform, which corresponds to the TESTSEL input on the APLL, is taken <u>high</u> <u>after the first test cycle</u> and held high throughout the rest of the simulation. The FREF clock is low at simulation start-up, and stays low until after TESTSEL goes high. Similarly RE-SETB, which resets the loop divider, is inactive (high) until after TESTSEL goes high.

Figure 11 Example Verilog System-Mode Simulation of an APLL (acquisition delay excluded)

Figure 12 Example Verilog System-Mode Simulation of an APLL (acquisition delay included)

L96 "/home/cdcl/aplltc/tc\_top/sub\_blocks/aplloacs22/vectors/stimulus/hdl.stim": \$stop at simulation time 250.00 ns Type ? for help C1 >

Figure 13 Example Verilog Option Release Simulation of an APLL

#### 5 Test Strategy for APLL Arrays

#### 5.1 Testing the Array Core

On the tester, customer "option release" test vectors are used to test all of the array except the APLL. Consequently the APLL is not used to clock the array core. The ASIC designer must use an external test clock to generate test vectors for option release, as is done for any non-APLL design. This external test clock is applied at the FREF pin.

At simulation start-up TESTSEL must be low, and must stay low for at least one test cycle, in order to initialize some flip-flops inside the APLL. During this time the model must output an 'x' on APLL outputs FVCO and FVCO\_DIV2, since the VCO will be oscillating freely in silicon. To ensure that FVCO and FVCO\_DIV2 remain 'x' while TESTSEL is low, the following two conditions must be met:

- 1. FREF should be low at simulation start-up, and should remain low at least until TESTSEL goes high.

- 2. If there is a reset signal for the loop divider, this reset must be inactive at simulation start-up, and must remain inactive at least until TESTSEL goes high. This condition is required because as soon as a known logic state appears at iFFB, the model outputs a known (low) state at FVCO and FVCO\_DIV2 to facilitate reset of the loop divider during system simulations.

After TESTSEL goes high the APLL will be powered down, and the reference clock at the FREF pin will bypass the APLL and come out at the APLL's FVCO port (see Figure 2 and Figure 3). Similarly, FREF/2 comes out on the APLL's FVCO\_DIV2 port. Once TESTSEL goes high it must stay high throughout the rest of the option release simulation.

#### 5.2 Testing the APLL

The APLL is tested at Motorola by a canned test routine, during which the rest of the array does not toggle. This procedure is used to eliminate coupling of digital switching noise into the APLL through AVDD and AVSS, which are tied to the core VDD and VSS on the tester in order to eliminate the need for special test hardware for APLL arrays. In a customer's system, of course, AVDD and AVSS provide isolated power and ground for the APLL.

The APLL contains a divide-by-4 which is driven by VCO/ 2 in order to produce a frequency at the TESTOUT pin which is slow enough to be measured on a production tester. As shown in Table C.1 in Appendix C, the following tests are performed on the tester while in APLL test mode (TSTQ1 = 1):

Allow the APLL to lock at its center frequency and measure the VCO/8 frequency at the TESTOUT pin, with the VCOCTL pin turned off.

- ii) Allow the APLL to lock at its center frequency and measure the VCO/8 frequency at the TESTOUT pin, and the VCO control voltage at the VCOCTL pin.

- iii) Allow the APLL to lock at its center frequency and measure the VCO/8 frequency at the TESTOUT pin, and the charge pump current at the VCOCTL pin.

- iv) Measure the dynamic IDD of the APLL. (A CMOS input APLL still will be in phase-lock from the previous step. For a PECL input APLL, the PECL input will be turned off by ENID ("Enable IDD" pin, see OACS User/Reference Guide); therefore the dynamic IDD measurement will be made while the APLL is not phase-locked but is free running at the minimum possible VCO frequency, since the phase detector reference frequency input, iFREF, will not be toggling).

On the tester, frequency measurement is effectively done by locating an edge on TESTOUT and then examining several more cycles to see that subsequent edges occur within the expected window. CMOS-input APLL's will remain phaselocked when moving from test (i) to test (ii), and from test (ii) to test (iii), etc. However PECL-input APLL's will lose lock when moving from one test to another. As shown in Table C.1, toggling the ENID pin is what causes the transition from one test to the next. However taking ENID high also powersdown the PECL input buffer, at which time a PECL-input APLL will lose phase-lock. Therefore after ENID is taken back low to begin the next test, a PECL-input APLL must be given time to re-acquire phase-lock before measurements are taken.

Tests i-iv are repeated at the APLL minimum and maximum *operating* frequencies, which are the most extreme frequencies achievable within the linear range of the VCO transfer function. These frequency limits are given in Section 2.

The VCOCTL pin is used to measure the VCO control voltage and charge pump current. These measurements can be related to the stability and bandwidth of the APLL. This pin should be tied to analog VSS in the customer's system to prevent noise from being injected onto the VCO control voltage during normal system operation.

During static IDD testing of the chip as a whole, which occurs during tester application of option release vectors, APLL bias currents are turned off under control of the ENID pin.

The canned APLL vector set, which performs tests (i)-(iv) above, toggles the ENID pin, which has no simulation model. Therefore, the customer cannot simulate these canned vectors.

#### Appendix A PLL Basics

#### A.1 INTRODUCTION

Transferring data between ASIC chips at frequencies above 40 MHz requires special on-chip circuitry in current sub-micron technologies. Phase locked loops can provide skew management in ASIC devices to help compensate for clock tree insertion delays and process, temperature and voltage variations allowing maximum multi-chip system performance.

This application note is written to help designers of multichip ASIC systems maximize system performance by managing clock distribution and optimizing clock skew and data path relationships. It contains equations relating measurable timing and skew parameters to maximum frequencies of operation. It explains techniques available to minimize critical parameters which contribute to clock skew.

#### A.2 BACKGROUND

# A.2.1 REGISTER-TO-REGISTER DATA TRANSFER BETWEEN ASIC CHIPS

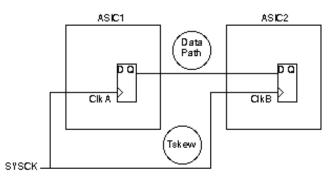

When determining the maximum frequency at which data can be transferred from one ASIC device to another, a designer must carefully consider both the delay of the data path and the skew of the clock. The data path is the delay from a register in the sending ASIC (including clock to Q) to the D input of a register in the receiving ASIC (including the setup and hold times), see Figure A.1. The clock skew or Tskew is the difference between a rising edge on ClkA in ASIC1 and ClkB in ASIC2.

Figure A.1 Chip-to-Chip Timing Parameters

Tskew in this document refers to clock skew in both the positive and negative directions. Positive skew is when the rising edge of ClkB occurs later than a rising edge of ClkA. Positive skew affects data transfer from a hold time standpoint. Negative skew is when the rising edge of ClkB occurs earlier than a rising edge on ClkA. Negative skew affects data transfer from a setup time standpoint. A complete analysis of clock skew is performed in Appendix B.

#### A.2.2 SETUP AND HOLD TIME CONSIDERATIONS

To insure error-free data transitions between ASIC1 and ASIC2, the data path from the sending flip- flop in ASIC1 to the receiving flip flop in ASIC2 must not be so long that a setup time violation is realized on the receiving flop- flop. The same data path must also be long enough to avoid a holdtime violation on the receiving flip-flop. This setup and hold time relationship must take into consideration clock skew between the rising edge of ClkA, which initiates the data transfer and the rising edge of ClkB which clocks in the transferred data.

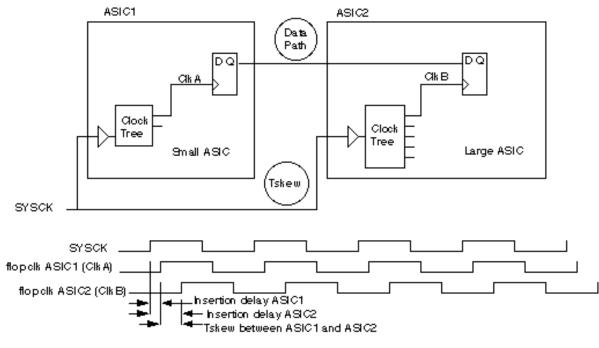

# A.2.3 INSERTION DELAY AND THE EFFECT OF THE CLOCK TREE

Insertion delay is defined as the delay from the rising edge of the external system clock to the rising edge of the clock on any given flip- flop on the ASIC. In Figure A.2, it's the delay from SYSCK to ClkA or ClkB. Insertion delay is made up of the clock input buffer and clock tree delays. The insertion delay in one ASIC can be very different from the insertion delay in another ASIC, depending on the size of the ASIC and the number of elements that must be clocked by the clock tree. Differences in insertion delays between ASIC devices directly contribute to clock skew (Tskew). In the example circuit (Figure A.2): if ASIC1 has an insertion delay of 5 ns and ASIC2 an insertion delay of 10 ns, then a rising edge in ASIC 1 will be skewed by at least 5 ns from a rising edge in ASIC 2.

#### A.2.4 PTV VARIATIONS

Process, Temperature and Voltage (PTV) variations can increase the difference in insertion delays. Most ASIC technologies use a multiplier to adjust delays due to PTV. In the H4C technology, a worst-case multiplier (WCM) and a bestcase multiplier (BCM) are used. The WCM modifies a typical delay to represent worst-case conditions. The WCM is greater than one. The BCM is less than one and modifies a typical delay to represent a best-case condition. The "process spread" is the difference between a best-case delay and a worst-case delay for a given data path. The process spread can be found by dividing the WCM by the BCM (WCM/BCM). Choosing a technology with a minimum process spread will allow higher overall performance.

#### A.2.5 MAXIMUM FREQUENCY OF OPERATION

An equation can be derived that relates setup and hold times, insertion delay and process spread to determine the maximum frequency at which data can be safely transferred from chip-to-chip. A full derivation of this equation is provided in Appendix E. The equation in terms of the minimum period is,

$$\begin{array}{l} \text{MinPer} = \text{Tskew} (\text{WCM/BCM} + 1) + \text{WCM} (\text{Tsu} + \text{Th} + \\ \text{TDm}) \end{array}$$

(A.1)

where,

| MinPer | Minimum clock period in ns (1/max frequency of operation).                                    |

|--------|-----------------------------------------------------------------------------------------------|

| Tskew  | Total skew (positive and/or negative) between rising edges of ClkA and ClkB (see Figure A.2). |

| WCM    | Worst Case Multiplier.                                                                        |

| BCM    | Best Case Multiplier.                                                                         |

| Tsu    | Setup delay of flip flop in receiving ASIC (ASIC2 in Figure A.2).                             |

| Th     | Hold delay of flip flop in receiving ASIC (ASIC2                                              |

|        | in Figure A.2).                                                                               |

| TDm    | Data path delay margin                                                                        |

Two things become apparent in looking at Equation (A.1). First, Tskew is the dominant parameter affecting the maximum frequency at which data can be transferred between ASIC devices. Secondly, the process spread for the chosen technology is also very important. Clearly, Tskew and the process spread must be minimized to allow maximum performance.

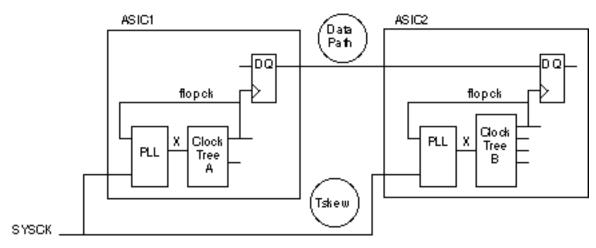

To address the problem of clock skew, a Phase Locked Loop (PLL) can be added to each ASIC device to reduce the effects of insertion delay differences and help manage the skew from chip-to-chip. The PLL will synchronize the rising edge on SYSCK such that it will be simultaneous with a rising edge on flop ck, see Figure A.3. If the PLL is used on each ASIC device, all flop ck signals on every ASIC will be simultaneous within the error of the PLL. The PLL will compensate for differences in insertion delays from ASIC-to-ASIC as well as PTV variations.

Figure A.3 PLL Solution

#### Appendix B Derivation of Minimum Period Equation

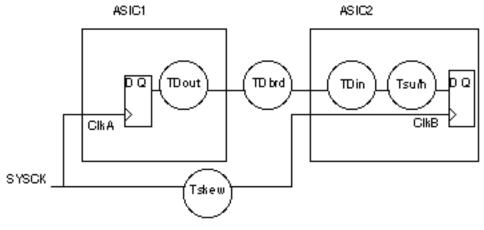

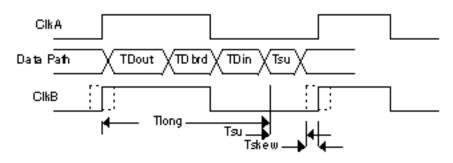

This section contains a derivation of the equation that relates clock skew, process spread, and flip-flop specifications to determine the minimum period or maximum frequency at which data can be transferred between ASIC devices. Figure B.1 illustrates the data and clock paths between two ASICs. If data is to be transferred reliably from ASIC1 to ASIC2, the set up and hold time requirements of the receiving flip flop in ASIC2 must be satisfied in the presence of clock skew and process spread. First, we will analyze the setup and hold time requirements of the receiving flip flop. This is similar to the classic shift register problem where clock skew can cause setup or hold problems on the receiving flip flop.

The data delay path from ASIC1 to ASIC2 includes 1) the delay from a rising edge of ClkA to the output of ASIC1 - TD-out, 2) the delay of the PC board trace - TDbrd and 3) the delay of the input path of ASIC2 - TDin. The setup and hold time parameters of the receiving flip flop Tsu and Th must also be considered. The total data path delay is,

When considering the setup time requirements of ASIC2, the worst case path from ASIC1 to ASIC2 must be considered. The minimum period at which data can be safely trans-

ferred in the presence of clock skew without violating the setup requirements of the receiving flip flop is,

$$MinPer = WCM(TD + Tsu) + Tskew$$

(B.2)

Note that typical delay values are used in these equations. These values are modified for best case and worst case by the multipliers BCM and WCM respectively. Additionally, the worst- case path assumes the edge direction, rising or falling that results in the longest delay.

Figure B.2 illustrates the setup time requirement. The dashed lines on ClkB represent clock skew.

When considering the hold- time requirements of ASIC2, the best-case path must be considered. The best-case path assumes the edge direction, rising or falling that results in the shortest delay. The equation relating the data path, hold time and Tskew is,

$$BCM(TD) \ge Tskew + BCM(Th)$$

(B.3)

We now have two equations relating the data path. To find the minimum period, first consider the ideal case, then generalize it. Ideally, assume the data path delay TD is just long enough to prevent a hold-time violation, or the best-case data delay is equal to the hold time plus the clock skew,

Figure B.1 Chip-to-Chip Data Transfers

#### Appendix C APLL Internal Test Circuitry

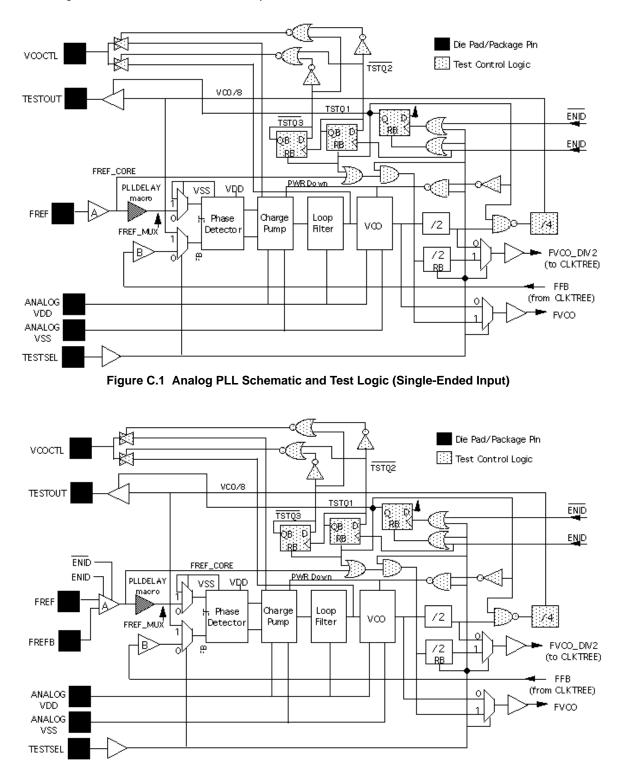

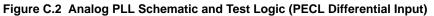

Figure C.1 and Figure C.2 are more detailed versions of Figure 2 and Figure 3, respectively, showing the test control circuitry built into the APLL. Table C.1 shows how the TEST-SEL and ENID signals are used to control this circuitry in or-

der to move the APLL into each of its operating modes. The top portion of Table C.1 shows how the Motorola-internal APLL test program performs the tests described in Section 5.2.

|                                                 | Inp     | outs | APLL  | Internal | Nodes |                                                            |  |  |

|-------------------------------------------------|---------|------|-------|----------|-------|------------------------------------------------------------|--|--|

| Test                                            | TESTSEL | ENID | TSTQ1 | TSTQ2    | TSTQ3 | Simulation and Test Modes                                  |  |  |

|                                                 | 0       | 0    | 0     | 0        | 0     | Reset test flops.                                          |  |  |

|                                                 | 0       | 1    | 0     | 0        | 0     | (Set-up Test)                                              |  |  |

| la                                              | 1       | 1    | 1     | 0        | 0     | (Set-up Test)                                              |  |  |

| Test Provided at Motorola<br>(Not User Defined) | 1       | 0    | 1     | 0        | 0     | Measure frequency; VCOCTL pin 3-state.                     |  |  |

| t Mc<br>ed)                                     | 1       | 0    | 1     | 0        | 0     | (Running Test)                                             |  |  |

| Test Provided at M<br>(Not User Defined)        | 1       | 1    | 1     | 1        | 0     | (Set-up Next Test)                                         |  |  |

| vide<br>er D                                    | 1       | 0    | 1     | 1        | 0     | Measure frequency & VCO control voltage.                   |  |  |

| Pro<br>Us                                       | 1       | 0    | 1     | 1        | 0     | (Running Test)                                             |  |  |

| Test<br>(No1                                    | 1       | 1    | 1     | 0        | 1     | (Set-up Next Test)                                         |  |  |

| APLL -                                          | 1       | 0    | 1     | 0        | 1     | Measure frequency & charge pump current.                   |  |  |

| AP                                              | 1       | 0    | 1     | 0        | 1     | (Running Test)                                             |  |  |

|                                                 | 1       | 1    | 1     | 1        | 1     | Measure dynamic IDD of APLL.                               |  |  |

|                                                 | 1       | 1    | 1     | 1        | 1     | (Running Test)                                             |  |  |

|                                                 | 0       | 0    | 0     | 0        | 0     | Reset test flops.                                          |  |  |

| ed)                                             | 1       | 0    | 0     | 0        | 0     | Start functional testing of array core with APLL inactive. |  |  |

| Core Test<br>(User Defined)                     | 1       | 0    | 0     | 0        | 0     | (Running Test)                                             |  |  |

| ore<br>er D                                     | 1       | 1    | 0     | 0        | 0     | IDD vector (at Motorola only)                              |  |  |

| (Use                                            | 1       | 0    | 0     | 0        | 0     | (Running Test)                                             |  |  |

|                                                 | 1       | 0    | 0     | 0        | 0     | (Running Test)                                             |  |  |

|                                                 | 0       | 0    | 0     | 0        | 0     | Customer board simulation with APLL active.                |  |  |

Table C.1 APLL Simulation and Test Mode Sequence

\* User can only simulate states in which ENID is low/inactive.

### Appendix D APLL Equations

The APLL is a classical second order type 2 control system. Its transfer functions are:

Phase Detector Transfer Function:

$$K_{\rm p} = I_{\rm p}/2\pi \tag{D.1}$$

where  ${\sf I}_{\sf p}$  is the charge pump current.

Filter Transfer Function:

$$K_{f} = R + 1/sC \tag{D.2}$$

where R is the loop resistor and C is the loop capacitor.

VCO Transfer Function:

$$K_{o} = 2\pi K_{v}/s \tag{D.3}$$

where  $K_v$  is the gain of the VCO in the linear region.

The feedback transfer function is:

$$H(s) = 1/N$$

(D.4)

where N is the number of dividers in the feedback path.

The feed forward transfer function is:

$$G(s) = K_p(K_f)(K_0)$$

(D.5)

These can be combined to give the Open Loop Gain Transfer Function:

$$G(s)H(s) = K_{p}(K_{f})(K_{p})/N$$

(D.6)

where N is the value of the divider in the feedback path.

This provides the open loop gain:

$$OLG = K_p(K_o)R/N = K_v I_p R/N$$

(D.7)

Closed Loop Transfer Function:

$$CLTF = G(s)/[1 + G(s)H(s)]$$

(D.8)

which can be reduced to the following form for a type 2 second order system:

CLTF = N

$$[2\zeta \omega_{n}s + \omega_{n}^{2}] / (s^{2} + 2\zeta \omega_{n}s + \omega_{n}^{2})$$

(D.9)

where

Natural frequency =

$$\omega_n = (K_v I_p / CN)^{1/2}$$

(D.10)

Damping factor =

$$\zeta = RC\omega_n/2$$

(D.11)

Typical values for the loop parameters are shown below:

Table D.1 Typical Loop Parameter Values

|                        | H4E   | M5C  |      |

|------------------------|-------|------|------|

| Parameter              | 3.3 V | 5 V  | WIGC |

| Ι <sub>p</sub> (μΑ)    | 70    | 100  | 100  |

| K <sub>v</sub> (MHz/V) | 200   | 250  | 170  |

| R (Ohm)                | 2100  | 1400 | 750  |

| C (pF)                 | 50    | 50   | 200  |

From these typical values and the closed loop transfer function, the user can determine the characteristics of the loop and generate Bode Plots, if desired.

#### Appendix E VCO Frequency Selection

In order to obtain the best performance from the APLL macro care should be taken when selecting the VCO frequency. As shown in Figure 10, on page 7, the designer must select values for the dividers L and M. The following formulas show how the input reference, clock tree and VCO frequency are related when the APLL is locked:

$$F_{clock tree} = F_{input reference} * M$$

(E.1)

$$F_{vco,div2} = F_{clock,tree} * L$$

(E.2)

In Figure 10 the "/L" divider is driven from the  $F_{vco\_div2}$  output which already contains a "/2" stage. The "/L" divider may be driven from the  $F_{vco}$  output instead, with the appropriate removal of the factor of 2. The values of L and M must be chosen with the following constraints:

- The divide factor (2 \* L \* M) must be within the Loop Divider Range.

- F<sub>vco</sub> must be within the VCO Frequency Range give in Table 2.

Whenever possible the VCO frequency selected should be in the middle of the linear region, as shown in Figure E.1.

Figure E.1 H4EPlus Typical VCO Frequency vs. Voltage

One of the considerations for selecting a Divide Factor is the minimum frequency at which the APLL will lock.

In order for the APLL to lock the Open Loop Gain must be less than the reference frequency at the phase detector. The Open Loop Gain is determined in Equation (D.7). To add a safety margin, the Open Loop Gain is multiplied by 3 to give the minimum reference frequency as shown in Figure E.1.

**Table E.1 APLL Characteristics**

|             | H4EPlus        |                   |                              |                |                |                              |                | M5C            |                              |

|-------------|----------------|-------------------|------------------------------|----------------|----------------|------------------------------|----------------|----------------|------------------------------|

| Divide      |                | 3.3 V             |                              |                | 5 V            |                              |                | WIGC           |                              |

| Factor<br>N | ω <sub>n</sub> | Damp ing, $\zeta$ | F <sub>refmin</sub><br>(MHz) | ω <sub>n</sub> | Damp<br>ing, ζ | F <sub>refmin</sub><br>(MHz) | ω <sub>n</sub> | Damp<br>ing, ζ | F <sub>refmin</sub><br>(MHz) |

| 1           | 16.8           | 0.88              | 88                           | 22.4           | 0.78           | 105                          | 9.2            | 0.69           | 38                           |

| 2           | 11.8           | 0.62              | 44                           | 15.8           | 0.55           | 53                           | 6.5            | 0.49           | 19                           |

| 3           | 9.7            | 0.51              | 29                           | 12.9           | 0.45           | 35                           | 5.3            | 0.40           | 13                           |

| 4           | 8.4            | 0.44              | 22                           | 11.2           | 0.39           | 26                           | 4.6            | 0.35           | 10                           |

| 5           | 7.5            | 0.39              | 18                           | 10.0           | 0.35           | 21                           | 4.1            | 0.31           | 8                            |

| 6           | 6.8            | 0.36              | 15                           | 9.1            | 0.32           | 18                           | 3.8            | 0.28           | 6                            |

| 7           | 6.3            | 0.33              | 13                           | 8.5            | 0.30           | 15                           | 3.5            | 0.26           | 5                            |

| 8           | 5.9            | 0.31              | 11                           | 7.9            | 0.28           | 13                           | 3.3            | 0.24           | 5                            |

| 9           | 5.6            | 0.29              | 10                           | 7.5            | 0.26           | 12                           | 3.1            | 0.23           | 4                            |

| 10          | 5.3            | 0.28              | 9                            | 7.1            | 0.25           | 11                           | 2.9            | 0.22           | 4                            |

| 11          | 5.1            | 0.26              | 8                            | 6.7            | 0.24           | 10                           | 2.8            | 0.21           | 3                            |

| 12          | 4.8            | 0.25              | 7                            | 6.5            | 0.23           | 9                            | 2.7            | 0.20           | 3                            |

| 13          | 4.6            | 0.24              | 7                            | 6.2            | 0.22           | 8                            | 2.6            | 0.19           | 3                            |

| 14          | 4.5            | 0.23              | 6                            | 6.0            | 0.21           | 8                            | 2.5            | 0.18           | 3                            |

| 15          | 4.3            | 0.23              | 6                            | 5.8            | 0.20           | 7                            | 2.4            | 0.18           | 3                            |

| 16          | 4.2            | 0.22              | 6                            | 5.6            | 0.20           | 7                            | 2.3            | 0.17           | 2                            |

**Example**: Using an H4EPlus 5V APLL, the desired clock tree frequency (CLK) is 50 MHz and FREF is 25 MHz, with the circuit configuration shown in Figure 10.

From Equation (E.1) select "/M" = 2. Since the range of acceptable loop dividers for an H4EP5 APLL are 1 to 16 and the  $F_{vco\ div2}$  output is being used, the value of L could be 1 to 4.

A table for the possible L values can be constructed:

Table E.2 Possible values for "L"

| Divide<br>Factor,<br>L | Total Divide<br>Factor,<br>N | F <sub>refmin</sub><br>(MHz)<br>(Table E.1) | F <sub>vco</sub><br>(MHz) |

|------------------------|------------------------------|---------------------------------------------|---------------------------|

| 1                      | 4                            | 26                                          | 100                       |

| 2                      | 8                            | 13                                          | 200                       |

| 3                      | 12                           | 9                                           | 300                       |

| 4                      | 16                           | 7                                           | 400                       |

The Total Divide Factor is L \* M \* 2 (using div2 output). The  $F_{refmin}$  is found in Table E.1 for the Divide Factor N. The  $F_{vco}$  is 25 MHz \* L \* M \* 2 (using div2 output).

From this table a Divide Factor L of 2 is the best since it exceeds the  $F_{refmin}$  value and is near the center of the linear range of the VCO as shown in Figure E.1. For L=3 or 4 the Fvco is greater than the 250 MHz maximum frequency specified in Table 2, so cannot be used.

Result: Use APLL  $F_{vco\_div2}$  output from the APLL, "/L" = 2 and "/M" = 2.

#### Appendix F Spectrum Spread Clocking

Radiated emissions from clock trees and clocked signals can generate significant interference. APLLs can help reduce this by enabling low frequency clocks to be distributed around the board, and multiplied up on-chip using frequency synthesis.

A second method often used is Spectrum Spread Clocking. This requires the use of a clock generator which provides a variable output frequency, centered on the desired system clock rate. A small variation in the clock frequency can provide a significant reduction in the radiated noise.

When using a spread spectrum clocking method, it is important to verify that the APLL will remain in lock and that the resulting jitter is acceptable. In practice the jitter is the most critical factor, since it determines the ability of the ASIC to communicate with other devices.

There are two parts to the system that may be considered separately. First the clock distribution to the ASIC. The results of this analysis are independent of the presence of an APLL.

This is analyzed by E. McCune - Spectrum Spread Clocking, High Performance System Design Conference, Super-Con 96:

The jitter at the IC clock input can be determined as follows:

$$F_{max} (MHz) = F * (1 + V)$$

(F.1)

$$F_{min} (MHz) = F * (1 - V)$$

(F.2)

where,

F = Center source frequency (MHz)

V = Variation of clock frequency from center (fraction of F)

So long as V<0.05:

peak-to-peak period jitter (nS) = 2000 \* V / F (F.3)

The period is assumed to change linearly so the cycle-tocycle jitter will be:

cycle-to-cycle jitter (nS) =  $\pm$  pk-to-pk jitter / T\*F (F.4)

where,

T = Time for source to change from  $F_{max}$  to  $F_{min}$  ( $\mu$ S)

The second part of the system to be considered is the APLL. Since the APLL uses a charge pump to adjust the VCO frequency there will always be a lag between a change in the incoming clock period and the VCO adjusting. This can also be considered as cycle-to-cycle jitter. For this closed loop second order system, including the phase detector delay:

cy-to-cy APLL jitter (nS)

$$\cong \pm$$

cy-to-cy jitter \* 1.5 (F.5)

The cycle-to-cycle jitter of the source and the APLL must be added together to get the worst case jitter (which can be positive or negative). **Example**: Using an H4EPlus 5V APLL, the source clock is centered around 32 MHz and varies by  $\pm$  5.0% over 16  $\mu$ S.

The additional peak-to-peak period jitter from the source is:

pk-to-pk period jitter = 2000 \* 0.05 / 32 = 3.125 nS (F.6)

The worst case cycle-to-cycle jitter from the source is:

cy-to-cy jitter =

$$3.125 / (16 * 32) = \pm 0.0061 \text{ nS}$$

(F.7)

The additional worst case cycle-to-cycle jitter from the APLL is:

cy-to-cy jitter =

$$0.0061^* 1.5 = \pm 0.009$$

(F.8)

The total worst case cycle-to-cycle jitter is  $\pm$  0.015 nS.

## ASIC REGIONAL DESIGN CENTERS - U.S.A.

California, San Jose (408) 749-0510 Illinois, Chicago (708) 490-9500 Massachusetts, Marlborough (508) 481-8100

### ASIC REGIONAL DESIGN CENTERS - International

**European Headquarters,** Germany, Munich (089) 92103-0

Holland, Eindhoven (04998) 61211

Japan, Tokyo (03) 440-3311 England, Aylesbury, Bucks (0296) 395252

Hong Kong, Kwai Chung 480 8333

Sweden, Stockholm

(08) 734-8800

Italy, Milan (02) 82201

France, Vanves

(01) 40355877

H4EPlus and M5C are trademarks of Motorola, Inc. Verilog is a trademark of Cadence Design Systems, Inc. Synosys is a trademark of Synopsys, Inc.

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarding the suitability of its products for any particular purpose, nor dose Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without consequential or incidental damages. "Typical" parameters can and do vary in different applications. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola dose not convey any licence under its patent rights nor of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and **s** are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

Literature Distribution Centers:

| USA:          | Motorola Literature Distribution; P.O. Box 20912, Phoenix, Arizona 85036                                    |

|---------------|-------------------------------------------------------------------------------------------------------------|

| EUROPE:       | Motorola Ltd.; European Literature Center; 88 Tanners Drive, Blakelands, Miltion Keynes MK14 5BP, England   |

| JAPAN:        | Nippon Motorola Ltd.; 4-32-1, Nishi-Gotanda, Shinagawa-ku, Tokyo 141 Japan                                  |

| ASIA-PACIFIC: | Motorola Semiconductors H.K. Ltd.; Silicon Harbour Center, No. 2 Dai King Street, Tai Po Industrial Estate, |

|               | Tai Po, N.T., Hong Kong                                                                                     |