Order this document by AN1554/D

# **SRAM Built-in Self Test**

Prepared by: Steve Bradley 1300 N. Alma School Rd. Chandler Arizona

# INTRODUCTION

Built-in Self Test (BIST) is a test methodology in which on-chip test circuitry automatically and efficiently tests memories and other devices for various types of faults.

### SRAM BIST can provide many advantages:

- Cycle time is reduced by greatly decreasing the test pattern generation time of specialized vectors for embedded RAM verification.

- 2. Embedded RAMs can be quickly tested with a very high fault coverage. High test coverage can be obtained without having direct access to the RAMs.

- 3. Cost is reduced by minimizing tester requirements and reducing vector counts.

Motorola ASIC has developed two implementations of SRAM BIST. A Comparator BIST provides the highest fault coverage and best test capabilities. The Comparator BIST implements a deterministic test algorithm capable of 100% fault detection. The Comparator BIST provides this superior performance with the penalty of greater circuit complexity and a high gate count. The Pseudo-Random BIST uses a Linear Feedback Shift Register (LFSR) to generate a unique test signature. The Pseudo-Random BIST provides adequate fault coverage with minimum complexity and a low gate count.

Motorola ASIC requires that all embedded RAMs have BIST. The Pseudo-Random BIST provides sufficient fault coverage to fulfill the RAM-BIST requirement. Table 1 identifies differences between Pseudo-Random BIST and Comparator BIST.

# Motorola's ASIC BIST Features:

- 1. Significantly reduces tester use and cost

- 2. 100% fault detection (using Comparator BIST)

- 3. At-speed test to 40 MHz (using Comparator BIST)

- Independent of memory architecture and technology

- 5. Verifies both memory and BIST circuitry

- 6. Configurable to any memory size

- 7. JTAG scan, ATPG compatible

- 8. BIST test vector count can be compressed by 1000 to 1 ratio

| Feature                   | Pseudo-Random<br>BIST        | Comparator BIST              |

|---------------------------|------------------------------|------------------------------|

| Application               | meets RAM BIST requirement   | high reliability/performance |

| Algorithm                 | LFSR pseudo-random signature | Deterministic 21 N march     |

| Gate Requirement *        | 907                          | 1282                         |

| Maximum Fault Coverage    | 99%                          | 100%                         |

| At Speed Testing (40 MHz) | < 64 words                   | Total Memory                 |

| Test Time *               | 16 msec.                     | 4 msec.                      |

| Simulation Time **        | 0.8 hr.                      | 3 hrs.                       |

| RAM Diagnostic Capability | No                           | Yes                          |

| Clear Memory              | No                           | Yes                          |

| Fault Location            | No                           | Yes                          |

| Address Stress Test       | No                           | Yes                          |

#### Table 1. Comparison of Pseudo-Random BIST and Comparator BIST

\* Data based on 1024x8 diffused SRAM for comparison

\*\* Performance based on 2MIPs.

) MOTOROLA —

© MOTOROLA, INC. 1996

This section is intended to provide a general understanding of the capabilities of the two BIST implementations. For complete descriptions please refer to the application note: Embedded RAM BIST (AN1502).

# 1. Pseudo-Random BIST Description

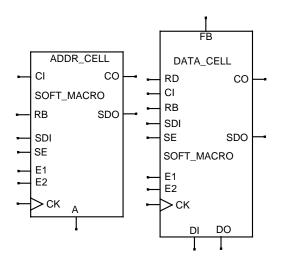

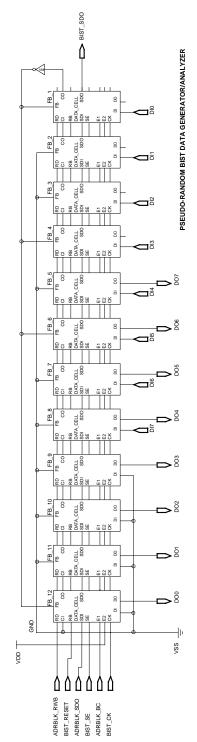

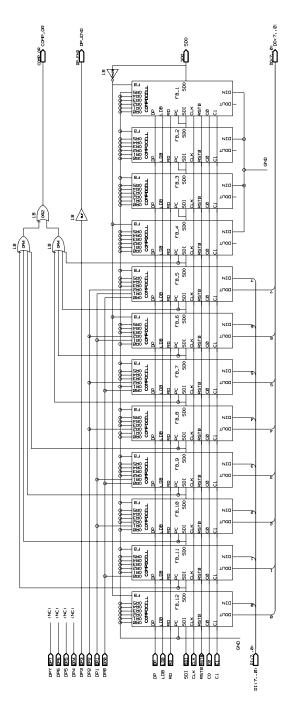

The Pseudo-Random BIST design is based upon two soft macros (ADDR\_CELL, DATA\_CELL) which are included in the H4CP & H4EP library. See Figure 1. These one bit macros can be used to construct a pseudo-random BIST circuit for any Motorola supplied RAM block.

Figure 1. Pseudo-Random BIST Soft Macro Symbols

#### ADDR\_CELL macro I/O signal description:

| input  | BIST Clock<br>BIST reset - active low                                  |

|--------|------------------------------------------------------------------------|

|        | Counter carry                                                          |

| input  | in - daisy chain carry                                                 |

| input  | Scan path serial data input                                            |

| input  | Scan path scan enable                                                  |

| input  | Scan path enable 1                                                     |

| input  | Scan path enable 2                                                     |

| output | BIST Address bit                                                       |

| output | Counter carry                                                          |

| output | out - daisy chain carry<br>Scan path data out                          |

|        | input<br>input<br>input<br>input<br>input<br>input<br>output<br>output |

#### DATA\_CELL macro I/O signal description:

| DATA_CELL-DI<br>DATA_CELL-RB<br>DATA_CELL-RD<br>DATA_CELL-RD<br>DATA_CELL-FB<br>DATA_CELL-CI<br>DATA_CELL-SDI<br>DATA_CELL-SE<br>DATA_CELL-E1<br>DATA_CELL-E2<br>DATA_CELL-DO<br>DATA_CELL-DO<br>DATA_CELL-CO | input<br>input<br>input<br>input<br>input<br>input<br>input<br>input<br>output<br>output | BIST data input - from RAM<br>BIST reset - active low<br>BIST clock<br>LFSR read mode operation<br>LFSR feedback input<br>LFSR carry input<br>Scan path serial data In<br>Scan path serial data In<br>Scan path serial data In<br>Scan path enable 1<br>Scan path enable 1<br>BIST data output - to RAM<br>LFSR carry output |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DATA_CELL-CO<br>DATA_CELL-SDO                                                                                                                                                                                 | output<br>output                                                                         |                                                                                                                                                                                                                                                                                                                              |

|                                                                                                                                                                                                               |                                                                                          |                                                                                                                                                                                                                                                                                                                              |

The customer, by the BIST module construction, will control: test fault coverage, probability of aliasing the data signature, and circuit performance. Connection to scan based architecture or JTAG will require additional customer consideration. Extra logic will be required if the BIST is to test multiple RAMs or various sized RAMs.

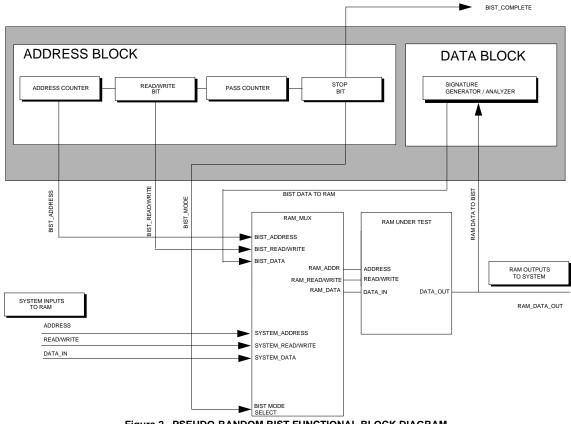

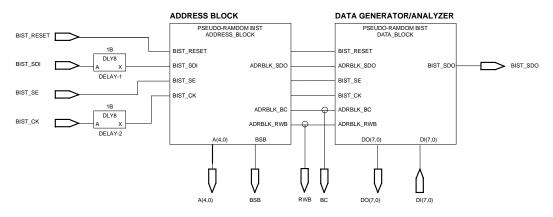

#### 1.1 Pseudo-Random BIST Functional Block Description

- 1. Address Block- address counter

- Address Block- read/write bit 2.

- 3. Address Block- pass counter

- 4. Address Block- stop bit

- 5.

- Data Block- data generator/analyzer

- 6. RAM mux- external mux for RAM address, data, and control lines

#### See Figure 2.

The address counter will increment the RAM address from zero to the number of RAM words. For RAMs with non-binary word counts (NOT 2, 4, 8, 16, 32, 64, 128, 256, 512, 1024, 2048, 4096, etc.) additional "end of count" carry/reset logic will be required.

The read/write bit will toggle after the address counter has reached its maximum count. Initially the read/write bit will be reset to "write". After the entire RAM has been written, the bit toggles and the next count through the RAM address field will "read". A single write/read cycle through the entire RAM address field is considered one pass.

The pass counter increments at the completion of each complete RAM write/read cycle pass. The level of fault coverage is determined by this block. The fault coverage increases with the number of test patterns written to and read from the RAM. Motorola ASIC recommends a count of 64 for the pass counter limit.

The stop bit will toggle after the final pass through the ram. Initially this bist is reset to the "test", toggling to the "test\_complete" state at the end of BIST test.

The data generator/analyzer will generate a pseudorandom pattern in its Linear Feedback Shift Register (LFSR). During the BIST "write" mode, the LFSR generates a pseudo-random data pattern for the RAM. During the BIST "read" mode, the data from the RAM will be fed into the same LFSR to build the RAM test signature. At the completion of BIST testing the value of this signature can be serially shifted from the BIST for comparison. If a serial shift is not desired, comparing the carry out pins of the data generator/analyzer DATA\_CELLs against a known good value can generate a "test pass/test fail" signal.

The RAM mux is required for H4CP & H4EP diffused and metallized RAMs. The RAM mux will select RAM input signal from either the BIST or the customer's design. The "BIST select" signal from the stop bit will select between the RAM receiving signals from the pseudo-random BIST or the customer's design.

Figure 2. PSEUDO-RANDOM BIST FUNCTIONAL BLOCK DIAGRAM

### 1.2 Pseudo-Random BIST Algorithm

| RAM Address                       | read/write                                          | pass_counter                                         | stop_bit                                                      | Data Generator/Analyzer                                                                                       | Pass 1  |       |

|-----------------------------------|-----------------------------------------------------|------------------------------------------------------|---------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|---------|-------|

| 0<br>1                            | 0 (write)<br>0 (write)                              | 0<br>0                                               | 0 (testing)<br>0 (testing)                                    | Reset data value<br>pseudo-random signature                                                                   |         | write |

| :<br>Nword-2<br>Nword-1<br>0<br>1 | :<br>0 (write)<br>0 (write)<br>1 (read)<br>1 (read) | :<br>0<br>0<br>0<br>0                                | :<br>0 (testing)<br>0 (testing)<br>0 (testing)<br>0 (testing) | :<br>pseudo-random signature<br>pseudo-random signature<br>pseudo-random signature<br>pseudo-random signature |         | read  |

| :<br>Nword-2<br>Nword-1           | :<br>1 (read)<br>1 (read)                           | :<br>0<br>0                                          | :<br>0 (testing)<br>0 (testing)                               | :<br>pseudo-random signature<br>pseudo-random signature                                                       |         |       |

| 0<br>1                            | 0 (write)<br>0 (write)                              | 1<br>1                                               | 0 (testing)<br>0 (testing)                                    | pseudo-random signature<br>pseudo-random signature                                                            |         | write |

| Nword-2<br>Nword-1<br>0<br>1      | 0 (write)<br>0 (write)<br>1 (read)<br>1 (read)      | 1<br>1<br>1                                          | 0 (testing)<br>0 (testing)<br>0 (testing)<br>0 (testing)      | pseudo-random signature<br>pseudo-random signature<br>pseudo-random signature<br>seudo-random signature       |         | read  |

| Nword-2<br>Nword-1                | 1 (read)<br>1 (read)                                | 1<br>1<br>1                                          | 0 (testing)<br>0 (testing)<br>:                               | pseudo-random signature<br>pseudo-random signature                                                            |         |       |

| :                                 | :                                                   |                                                      | :                                                             |                                                                                                               |         |       |

| :                                 | :                                                   | :                                                    | :                                                             | :                                                                                                             | Pass 64 | L     |

| 0<br>1<br>:                       | 0 (write)<br>0 (write)<br>:                         | final (63)<br>final (63)<br>:                        | 0 (testing)<br>0 (testing)<br>:                               | pseudo-random signature<br>pseudo-random signature<br>:                                                       |         | write |

| Nword-2<br>Nword-1<br>0           | 0 (write)<br>0 (write)<br>1 (read)<br>1 (read)      | final (63)<br>final (63)<br>final (63)<br>final (63) | 0 (testing)<br>0 (testing)<br>0 (testing)<br>0 (testing)      | pseudo-random signature<br>pseudo-random signature<br>pseudo-random signature<br>pseudo-random signature      |         | read  |

| Nword-2<br>Nword-1<br>0           | 1 (read)<br>1 (read)<br>0 (write)                   | final (63)<br>final (63)<br>0                        | 0 (testing)<br>0 (testing)<br>1 (done)                        | -<br>pseudo-random signature<br>pseudo-random signature<br>BIST test signature                                |         |       |

#### 1.3 Fault Coverage

The pseudo random BIST uses a Linear Feedback Shift Register (LFSR) to generate the data pattern stimulus for the RAM test and to store the RAM test signature. This is a statistical method where pseudo-random data patterns are used to test for hard memory faults. The test patterns do not test for specific types of hard faults, but are used to exercise the memory devices for correct functionality. As a result the fault coverage is controlled by two factors,

(a) the probability of the stimulus testing for a particular fault,

(b) the probability of the faulty signature not being the same as the good one.

The total fault coverage is found by multiplying these two fault coverages together.

# 1.3.1 Stimulus Fault Coverage

Three types of RAM faults are generally considered:

- 1. <u>Stuck at</u> The value of a data bit is stuck either high or low and cannot be changed.

- <u>State coupling</u> The value of one data bit A is controlled by the state of another data bit B. This fault is unidirectional so that while A is affected by B, B is unaffected by A. This fault will cause A to always be a constant function of data bit B. The function may either be normal (such that A = B) or inverting (such that A = not B).

3. <u>Transition coupling</u> - Transition of one data bit A cause a state change in data bit B. This is similar to State coupling, except that it is the actual transition of data bit B that changes the contents of data bit A.

The Pseudo Random BISTs data generator does not create test patterns specifically to test each fault type.

The "randomness" of the test pattern prevents a deterministic calculation of fault coverage. Instead the fault coverage is derived statistically.

The fault coverage increases with the number of passes through the RAM.

Table 2 below shows the probabilistic fault coverage for each type of fault over a range of passes.

|                     |     |     |     |     | e renage |      |      |

|---------------------|-----|-----|-----|-----|----------|------|------|

| Passes              | 1   | 2   | 4   | 8   | 16       | 32   | 64   |

| Stuck At            | 50% | 75% | 94% | 99% | 100%     | 100% | 100% |

| State Coupling      | 25% | 37% | 47% | 49% | 50%      | 50%  | 50%  |

| Transition Coupling | 6%  | 11% | 20% | 32% | 44%      | 49%  | 50%  |

Table 2. Pseudo Random BIST estimated fault coverage

The coupling faults have a maximum coverage of 50% because the address counter only increments, so no faults can be found which effect higher addresses.

The apparently low fault coverage for coupling faults is not a severe limitation because of the fault clustering that is observed during manufacture.

Table 2 was constructed using the standard simplistic assumption that one (1) fault will exist. In practice a physical defect will normally cause multiple faults which are clustered within a small area. The detection of any one of these faults is sufficient to determine that the RAM is failing.

### 1.3.2 Signature Aliasing

Aliasing occurs when a signature resulting from a "failed" test matches the expected "good" signature of a passed test. The probability of aliasing is determined by the formula:

$$P(alias) = \underbrace{1}_{(2^n)-1}$$

where "n" is the number of signature bits. The probability of signature aliasing decreases as the number of signature bits in the data generator/analyzer section increases. The probability of signature aliasing is determined by the BIST construction (i.e. the customer). **Table 3** shows the aliasing probability for different signature lengths. Motorola ASIC is currently recommending using a minimum of 12 signature bits in the data generator/analyzer section.

#### Table 3. Pseudo Random BIST aliasing probability for different signature lengths

|                   | -                       | -                              |

|-------------------|-------------------------|--------------------------------|

| signature<br>bits | aliasing<br>probability | Probability of<br>NOT aliasing |

| 1                 | 50.000%                 | 50.000%                        |

| 2                 | 33.333%                 | 66.667%                        |

| 3                 | 14.286%                 | 85.714%                        |

| 4                 | 6.667%                  | 93.333%                        |

| 5                 | 3.226%                  | 96.774%                        |

| 6                 | 1.588%                  | 98.412%                        |

| 7                 | 0.787%                  | 99.213%                        |

| 8                 | 0.392%                  | 99.608%                        |

| 9                 | 0.196%                  | 99.804%                        |

| 10                | 0.098%                  | 99.902%                        |

| 11                | 0.049%                  | 99.951%                        |

| 12                | 0.024%                  | 99.976%                        |

| 13                | 0.012%                  | 99.988%                        |

| 14                | 0.006%                  | 99.994%                        |

| 15                | 0.003%                  | 99.997%                        |

| 16                | 0.002%                  | 99.998%                        |

| 17                | 0.001%                  | 99.999%                        |

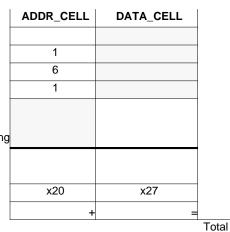

### 1.3.3 Pseudo-Random BIST construction.

#### Gate count estimation of a Pseudo-Random BIST

A gate count estimate can be generated by counting the required ADDR\_CELL and DATA\_CELL macros in the pseudo-random BIST. Logic for generating BIST control signals and the RAM mux have been ignored.

#### Number of Macros Required

one ADDR\_CELL for each address line of the RAM

- one ADDR\_CELL for the read/write control bit

- six ADDR\_CELL for the pass counter (64 passes)

- one ADDR\_CELL for the stop bit

- choose the greater number of DATA\_CELLs a) one DATA\_CELL for each RAM data line

- b) 12 DATA\_CELLs to minimize signature aliasing

sum total macros equivalent gates per macro sum of equivalent gates

#### Construction of a Pseudo-Random BIST

The construction of a pseudo-random BIST will be described by drawing its schematic. Associated diagrams are of a BIST for testing a generic 32 word x 8 bit RAM. Please refer to Figure 5.

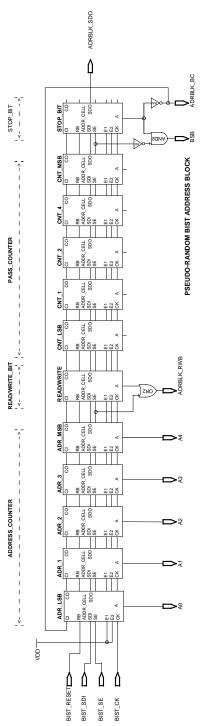

# Placement of ADDR\_CELL macros for the Address Block. Please refer to Figure 3.

- <u>Address\_counter</u> place one ADDR\_CELL macro for each address bit of the RAM in a row from left to right. The left macro will be for the RAM address LSB. The right macro will be for the RAM address MSB.

- <u>Read/write controller</u> place one ADDR\_CELL to the right of the address counter MSB ADDR\_CELL macro.

- Pass\_counter place six ADDR\_CELLs to the right of the read/write controller ADDR\_CELL. This will build a 64 test pass counter. The number of test passes is defined by: N(passes) = (2<sup>n</sup>) where "n" is the number of ADDR\_CELLs

macros in the pass counter.

4. <u>Stop bit places one ADDR\_CELL macro to the</u> right of the <u>pass counter</u>.

#### **Connecting signals for the Address Block**

- 1. Connect all ADDR\_CELL-SE inputs to a common BIST Scan Enable control signal.

- Connect all ADDR\_CELL-E1 inputs high (VDD). (The pseudo-random BIST doesn't use this scan control.)

- Connect all ADDR\_CELL-E2 inputs high (VDD). (The pseudo-random BIST doesn't use this scan control)

- 4. Connect all ADDR\_CELL-CK inputs to a common clock node. The BIST clock should be a separate clock and not tied to a system wide clock tree. It may be necessary to delay this clock to fulfill RAM address hold time constraints. This delay will be design dependent.

- 5. Connect the ADDR\_CELL-SDI input and ADDR\_CELL-SDO output.

- 5a) Address\_counter LSB ADDR\_CELL-SDI is the serial data input to the pseudo-random BIST block (BIST\_SDI). It may be necessary to delay this signal due to scan path hold time considerations.

- 5b) Connect the ADDR\_CELL-SDO output to the ADDR\_CELL-SDI input of ADDR\_CELL macro to the right.

- 5c) The stop\_bit ADDR\_CELL-SDO will later connect to the SDI input of the "data\_generator/ analyzer".

- Connect the ADDR\_CELL-CI input and ADDR\_CELL-CO output to configure the carry chain.

- 6a)The ADDR\_CELL-CI input of the address\_counter LSB macro (left most) will be driven by the signal "ADRBLK\_BC".This signal will be defined in step 11.

- 6b)The remaining ADDR\_CELL macros in the address counter will have their ADDR\_CELL-CI inputs driven by the ADDR\_CELL-CO output of the macro to the left.

- 6c)The Read/write\_controller ADDR\_CELL-CI input may be driven by one of two sources. First determine if the RAM has an "even power of 2" number of words (i.e. 32, 64, 128, 256, 512, 1024...).

If so,the read/write\_controller ADDR\_CELL-CI input will be driven by the address\_ counter MSB macro's ADDR\_CELL-CO output.

If not,the read/write\_controller ADDR\_CELL-CI input will be driven by logic which detects the address count reaching "number of RAM words -1".

- 6d)For the ADDR\_CELL-CI inputs of the pass\_counter and stop\_bit, drive the CI inputs with the CO output from the ADDR\_CELL macro on the left.

- Connecting the ADDR\_CELL-RB input for address block reset and end of count functions.

- 7a) Connect the ADDR\_CELL-RB input of the read/ write\_controller, pass\_counter, and the stop\_bit macros to a common node driven by the BIST reset signal.

- 7b) The address counter ADDR\_CELL-RB input may be driven by one of two sources. First determine if the RAM has an "even power of 2" number of words (i.e. 32, 64, 128, 256, 512, 1024...).

If so, the address counter ADDR\_CELL-RB input will be driven by the BIST reset signal. If not, the address counter ADDR\_CELL-RB input will be driven by the BIST reset signal -AND-logic which detects the address count reaching "number of RAM words -1" (active low)

- Identify the BIST address lines. The address\_counter ADDR\_CELL-A outputs will go to the RAM\_mux as the BIST address bus.

- 9. Generate the output signal "RWB" (read/ write\_bar) by "OR"ing the read/write\_controller ADDR\_CELL-A output with the BIST Scan Enable control signal to generate the BIST RWB signal.

- 10.Generate the output signal "BSB" (BIST select\_bar) by "AND"ing the stop bit ADDR\_CELL-A output with the inverse of the BIST Scan Enable control signal.

- Generate the output signal "ADRBLK\_BC" (BIST complete) by inverting the stop\_bit ADDR\_CELL-A output. This signal was reference in step "6a".

### <u>Note:</u>

If the carry chain used to enable the address counters limits the high speed operation of the BIST, the use of carry look ahead logic in the address\_counter and pass\_counter may be useful.

The above BIST configuration will drive the RAM inputs from the BIST circuit during scan mode. This is used when scan chains, other than the BIST, exist in the design. Scan operation forces the BIST control signal "BSB" into "BIST\_mode" and the BIST control signal "RWB" to "read". This will prevent spurious writes and corruption of the RAM content during scan. If it is desirable to drive the RAM by the standard system inputs

a) generate the BIST control signal "RWB" directly from read/write\_controller ADDR\_CELL-A output.

b) generate the BIST control signal "BSB" by "OR"ing the stop bit ADDR\_CELL-A output with the BIST Scan Enable control signal.

Figure 3. Pseudo Random BIST Address\_Block

#### Placement of DATA\_CELL macros for the Data Generator/Analyzer. Please refer to Figure 4.

- Place twelve DATA\_CELL macros in a row from left to right. The probability of signature aliasing is considered acceptable with twelve bits. (0.0024%) refer to Table 3.

- If RAM has more than twelve data bits, place one DATA\_CELL for each RAM data bit greater than 12 to the right of the previously placed DATA\_CELLs.

- 3. For RAMs with more than 32 data bits, split data\_generator/analyzer block into multiple LFSR shift registers with separate MLLFSR feedback connections. This will make it possible to predict the proper signature before simulations. *Contact ASIC Option Development Engineering for details.*

### <u>Note:</u>

There should always be 12 DATA\_CELL macros or one DATA\_CELL macro for each RAM data bit, whichever is greater.

# Connecting signals for the Data\_Generator/Analyzer Block

- Connect all DATA\_CELL-RD inputs to a common node. Connect to the signal "ADRBLK RWB".

- Connect all DATA\_CELL-RB inputs to a common node. Connect this node to the BIST reset signal (active low).

- Connect all DATA\_CELL-SE inputs to a common node. Connect to the BIST scan path enable signal (active high).

- Connect all DATA\_CELL-E1 inputs to a common node. Connect to the signal "ADRBLK\_BC". It selects function of the data\_generator/analyzer during BIST testing.

- Connect all DATA\_CELL-E2 inputs high (VDD). This function is not used in the standard pseudo-random BIST circuit.

- Connect all DATA\_CELL-CK inputs to a common clock node. The BIST clock should be a separate clock and not tied to a system wide clock tree. It may be necessary to delay this clock to meet RAM address hold time constraints. Required delay will be design dependent.

- 7. Connect the data\_generator/analyzer carry chain.

- 7a) Connect the left most DATA\_CELL-CI input low (VSS).

- 7b) Connect DATA\_CELL-CO output to the adjacent DATA\_CELL-CI input of the macro to the right.

- 7c) The right most DATA\_CELL-CO output will be inverted and used to drive the LFSR feedback tap connections DATA\_CELL-FB.

- 8. Connection the data\_generator/analyzer scan path.

- 8a) Connect the left most DATA\_CELL-SDI input to the signal "ADRBLK\_SDO".

- 8b) Connect DATA\_CELL-SDO output to the adjacent DATA\_CELL-SDI input of the macro to the right.

- 8c) The right most DATA\_CELL-SDO output will be the BIST Scan Data Out signal "BIST\_SDO".

- Connection the data\_generator/analyzer data out bus "DO" (from BIST to RAM\_MUX)

- 9a) Connect the left most DATA\_CELL-DO output to the RAM mux LSB BIST data input.

- 9b) Continue right connecting DATA\_CELL-DO output to the next highest RAM mux BIST data input.

- 9c) If the LFSR is wider than the RAM data bus, leave extra DATA\_CELL-DO output unconnected.

- 10.Connecting the data\_generator/analyzer data in bus "DI" (from RAM to BIST)

- 10a) Connect the right most DATA\_CELL-DI input to the RAM's LSB data out signal. This is the reverse direction as the BIST DO bus.

- 10b) Continue left connecting DATA\_CELL-DI inputs to the next highest RAM data out signal.

- 10c) If the LFSR is wider than the RAM data bus, connect the extra DATA\_CELL-DI inputs low (VSS).

- 11. Connect of the data\_generator/analyzer LFSR feedback

- 11a) Connect the appropriate DATA\_CELL-FB inputs to the inverted right most macro DATA\_CELL-CO output. See Table 4 for LFSR feedback tap connections for the sizes of Data\_Generator/Analyzer registers.

- 11b) Connect the remaining unconnected DATA\_CELL-FB inputs low (VSS).

Figure 4. Pseudo Random BIST Data\_Generator/ Analyzer Block

| LFSR bits | Sequence Length | Feedback Taps | Feedback Taps                    |

|-----------|-----------------|---------------|----------------------------------|

| 12        | 4095            | [12,6,4,1]    | [12,9,3,2]                       |

| 13        | 8191            | [13,4,3,1]    | [13,10,9,7,5,4]                  |

| 14        | 16384           | [14,12,2,1]   | [14,12,11,1]                     |

| 15        | 32767           | [15,1]        | [15,4]                           |

| 16        | 65535           | [16,12,3,1]   | [16,12,9,6]                      |

| 17        | 131071          | [17,3]        | [17,3,2,1]                       |

| 18        | 262143          | [18,7]        | [18,10,7,5]                      |

| 19        | 524287          | [19,5,2,1]    | [19,13,8,5,4,3]                  |

| 20        | 1048575         | [20,3]        | [20,9,5,3]                       |

| 21        | 2097151         | [21,2]        | [21,14,7,2]                      |

| 22        | 4194303         | [22,1]        | [22,9,5,1]                       |

| 23        | 8388607         | [23,5]        | [23,17,11,5]                     |

| 24        | 16777215        | [24,7,2,1]    | [24,4,3,1]                       |

| 25        | 33554431        | [25,3]        | [25,3,2,1]                       |

| 26        | 67108863        | [26,6,2,1]    | [26,22,21,16,12,11,10,8,5,4,3,1] |

| 27        | 134217727       | [27,5,2,1]    | [27,18,11,10,9,5,4,3]            |

| 28        | 298453455       | [28,3]        | [28,13,11,9,5,3]                 |

| 29        | 536870911       | [29,2]        | [29,20,11,2]                     |

| 30        | 1073741823      | [30,23,2,1]   | [30,6,4,1]                       |

| 31        | 2147483647      | [31,3]        | [31,3,2,1]                       |

| 32        | 4294967265      | [32,22,2,1]   | [32,7,5,3,2,1]                   |

Table 4. LFSR Feedback Connections Table

#### Note:

Table 4 has been copied with corrections from: 'Spread Spectrum Systems', by Robert C. Dixon. For any particular length MLLFSR there is more than one set of connections that will create a maximal length sequence. The connections vary depending upon the MLLFSR length. This table contains a list of two possible feedback taps for a number of different length MLLFSRs.

WARNING: The Feedback Taps numbers are ordered from right to left. This is the same direction as the DATA\_IN num-

bering order, however, Feedback Taps numbers start with "1" not "0" as DATA\_IN.

# Complete BIST connections - Address Block to Data\_Generator/Analyzer.

These connections are listed for completion. Many of them have already been made.

Please refer to Figure 5.

- 1. Connect the BIST reset "BIST\_RESET" to the appropriate node in the address and data block.

- 2. Connect the BIST scan enable "BIST\_SE" to the appropriate node in the address and data block.

- Connect the BIST serial data input "BIST\_SDI" the address counter's LSB ADDR\_CELL-SDI input.

- 4. Connect the BIST clock "BIST\_CK" to the ADDR\_CELL-CK and DATA\_CELL-CK inputs.

- Connect the address block stop\_bit ADDR\_CELL-SDO output "ADRBLK\_SDO" to the data block left most DATA\_CELL-SDI input.

- Connect the address block output signal "ADRBLK\_BC" to the data block DATA\_CELL-E1 inputs. The "ADRBLK\_BC" will also serve as

the Bist output "BC".

- Connect the address block output signal "ADRBLK\_RWB" to the data block DATA\_CELL-RD input. The "ADRBLK\_RWB" will also serve as the BIST output "RWB".

- 8. Identify the BIST address bus as the address counters ADDR\_CELL-A outputs.

- Identify the BIST data out bus as the data block DATA\_CELL-DO outputs. Ignore unconnected DATA\_CELL-DO outputs.

- 10.Identify the BIST data in bus as the data block DATA\_CELL-DI inputs. Ground unused DATA\_CELL-DI inputs.

- 11. The data block right most DATA\_CELL-SDO output will serve as the BIST serial data output "BIST\_SDO".

This construction has ignored additional gate requirements for signal buffers and delay insertion. These values are dependent on the customer's design. Expect to delay the BIST\_SDI and BIST\_CK by a similar amount. Heavily loaded signals will require additional buffering to meet edge rate and performance requirements. RAM interface signals must all meet RAM setup

and hold requirements. Timing requirements must be verified with Verilog<sup>TM</sup> simulation.

# Pseudo-Random BIST circuit I/O signal description:

#### **BIST Advisor**

Motorola ASIC Option Development Engineering can assist in developing a pseudo-random BIST for various RAM sizes with the use of the "BIST\_ADVISOR". This program will graphically show connection of the LFSR feedback tap and list the correct test data signature. This can predict the test signature determined by Verilog<sup>TM</sup> simulation. BIST\_ADVISOR can generate signatures for LFSR up to 32 bits in length.

# <u>Note:</u>

The schematics of BIST Advisor will drive the RAM inputs from the system inputs during scan mode. This is commonly used when the BIST contains the design's only scan path.

BIST Advisor

```

Version 1.01

Which type of BIST do you want?

0 = Pseudo Random BIST

1 = Comparator BIST

BIST type: 0

BIST Data

Number of data register bits : 12

Number of passes : 64

Ram Data

Number of data bits : 8

Number of data bits : 32

BIST Address Counter Configuration

```

The connections to the BIST address counter configuration should be made, in accordance with the application note. The diagram below shows how to make the connections:

BIST Data Register Configuration

The diagram below shows how the feedback connections to the BIST should be made, in accordance with the application note. In order to achieve a maximal sequence the following feedback taps should be used : [12,6,4,1]

The output from the last macro in the data register should be connected to these feedback pins as shown below. All other feedback pins should be tied to ground.

The data bits to the RAM should be connected from the BIST starting from the left most data register. The data bits from the RAM should be connected to the BIST in REVERSE order starting at the rightmost data register. Any unused data input pins should be tied to ground.

0 GND --/ \ v v | | v v ----FB SDI XXX

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

^

1 RAM GND GND GND GND D07 D06 D05 D04 D03 D02 D01 D00 то RAM D00 D01 D02 D03 D04 D05 D06 D07 TEST RESULTS \_\_\_\_\_ test length = 4096 clock cycles signature : SDI-> 0 0 1 1 0 1 0 0 1 0 1 1 -> SDO

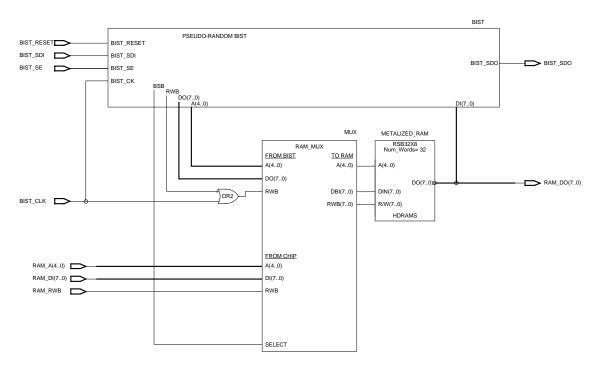

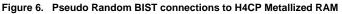

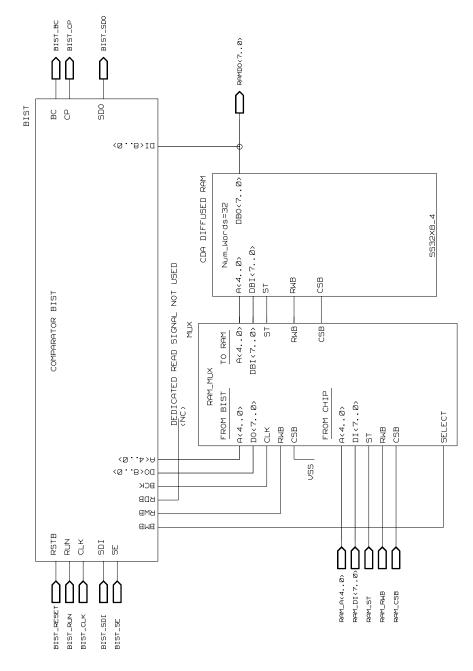

# **1.3.4** Pseudo-Random BIST connection to Metallized RAMs.

To test a H4CP or H4EP metallized RAM with the pseudo-random BIST, a RAM\_MUX block will be necessary. The RAM\_MUX will select the RAM inputs from either the BIST circuitry or the customer's system. Please refer to Figure 6.

- Use the pseudo-random BIST signal "BSB" as the RAM\_MUX select. A "BSB" low value indicates BIST testing. A "BSB" high value will indicate normal system operation.

- 2. The pseudo-random BIST output signal "RWB" must be "OR"ed with the BIST clock to generate the proper RAM write cycle timing.

3. Construct the RAM\_MUX of 2:1 mux cells which select between:

a) system address lines and BIST address lines b) system data \_in lines and BIST data\_in lines c) system read/write\_bar (RWB) and BIST read/write\_bar (RWB).

- The output of the RWB mux must be buffered sufficiently to drive all of the metallized RAM's "R/WB" input signals (one per data bit).

- 5. Connect the RAM "DO" (data out) bus to the pseudo-random BIST "DI" (data in) bus.

### <u>Note:</u>

The BIST clock polarity is the same at the BIST as the RAM, unlike the diffused ram, where the BIST uses the inverse of the RAM clock.

#### 1.3.5 Pseudo-Random BIST connection to Diffused RAMs

To test a H4CP or H4EP diffused RAM with the pseudo-random BIST, a RAM\_MUX will be necessary. The RAM\_MUX will select the RAM inputs from either the BIST circuitry or the customer's system. Please refer to Figure 7.

- Use the pseudo-random BIST signal "BSB" as the RAM\_MUX select. A "BSB" low value indicates BIST testing. A "BSB" high value will indicate normal system operation.

- 2. Construct the RAM\_MUX of 2:1 mux cells which select between:

a)system address lines and BIST address lines b)system data \_ in lines and BIST data\_in lines c)system RAM\_ST (strobe) signal and the inverse BIST input signal BIST\_CK. The BIST clock and system strobe timing should be the opposite polarity. (i.e. the BIST switches on the opposite edge as the RAM)

d)system read/write control and BIST control signal RWB. e)system CSB (RAM DBO tristate control enable) and hard wired enable (VSS) for the BIST.

3. Connect the RAM "DBO" (data bus out) bus to the pseudo-random BIST "DI" (data in) bus.

# 1.3.6 Pseudo-Random BIST testing of Diffused dual port RAMs

Pseudo-Random BIST testing will need port arbitration logic to prevent simultaneous accessing of both ports. This will prevent testing in a true parallel fashion. One port then the other will be tested. It is possible to interleave the port addresses, if desired. Gating the port inputs may be necessary. There may also be restrictions on the inactive port's address bus and data bus preventing these BIST inputs from being directly wired together.

# 1.3.7 Pseudo-Random BIST testing of Multiple RAMs

One BIST module may be used to test several RAMs to minimize the gate overhead for BIST. The two methods of sharing BIST between multiple RAMs are parallel and serial testing.

Figure 7. Pseudo Random BIST connections to H4CP CDA diffused RAM

Parallel BIST test all RAMs in one pass. This method is fast but the test time is still determined by the time it takes the BIST to test the largest RAM. All address and control signals are shared and must support the largest RAM. (Special considerations are required for testing dual port RAMs) This method requires:

- 1. Pseudo-Random BIST address block is designed to access the largest RAM.

- Pseudo-Random BIST data block will have one DATA\_CELL for each data bit on every RAMs under test.

Serial BIST tests one RAM at a time. It is useful for testing groups of RAMs which are configured into larger RAM blocks. This method is slower than parallel testing. All input and output data bussed are shared and must be as wide as the widest RAM. This method requires:

- Pseudo-Random BIST address block be able to exactly address each RAM sequentially. This will require some additional address counter carry logic.

- 2. Pseudo-Random BIST data block be wide enough to support the widest RAM. In the other RAM test the unused data bus in signals will be tied low (VSS).

# 1.3.8 Pseudo-Random BIST Test Vector and Signature Generation

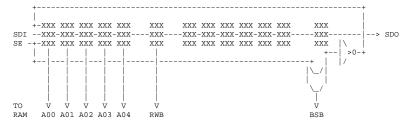

Simulation vectors are used as test vectors and to generate the "test" signature. The stimulus for the simulation is contained within three basic steps: initialization, BIST run, and signature scan. Please refer to Figure 8.

#### Pseudo-Random BIST Test Procedure:

- **1. Initialization:** RB should be low for at least 2 cycles.

- 2. Run BIST: Force RB high. The end of test is signalled when BSB goes high. The number of

cycles required to complete a test is Cycles = 2 (addresses) (passes).

- **3.** Scan Signature: Set SDI to "1" (HIGH), set SE to "1" (HIGH), and pulse CLK to scan out signature through SDO.

- 4. Exit Scan Mode: Force SE low to exit scan mode. The "1"s scanned into the BIST through SDI will put the BIST into an inactive mode.

#### 1.3.9 Pseudo-Random BIST On-chip operation

Once the customer has constructed the Pseudo-Random BIST circuit, decisions must be made on how the SRAM BIST testing is to be done in the customer's application. Section 1.3.8 describes how the BIST testing is activated using the BIST\_RESET signal. The BIST\_RESET could be activated by a "Power\_On\_Reset" signal or a dedicated "Execute\_BIST" or JTAG command. It is feasible to activate the BIST testing using the scan-path.

The standard use of the scan path is to disable the BIST during simulations used to create the UTIC.FINAL test program. By scanning in the inactive state into the BIST, the Pseudo-Random BIST testing cycle can be avoided. In this way, the customer will avoid a BIST test at the beginning of each test block.

#### **Compression of Final Test Vector count**

The OACS test flow uses the "repeat vector" tester mode to compress the BIST test vectors. This allows vector compression up to 1000:1. This is done one of two ways:

1) Have the input BIST clock be the only switching I/O on the chip. CONTEST will automatically compress the vectors. It may be necessary to tristate or gate switching outputs, including the BIST SDO signal.

2) Using the "Input Clock Burst" mode in Verilog<sup>tm</sup> simulation. The simulation must include the variables "UTIC\_PERIOD\_DEFINITION" and "BURST\_EN".

Please contact your Motorola ASIC representative for specific information on test vector compression.

Figure 8. Pseudo-Random BIST SImulation

# 2. Comparator BIST

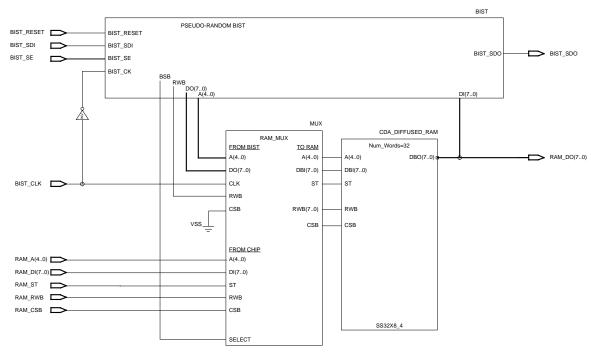

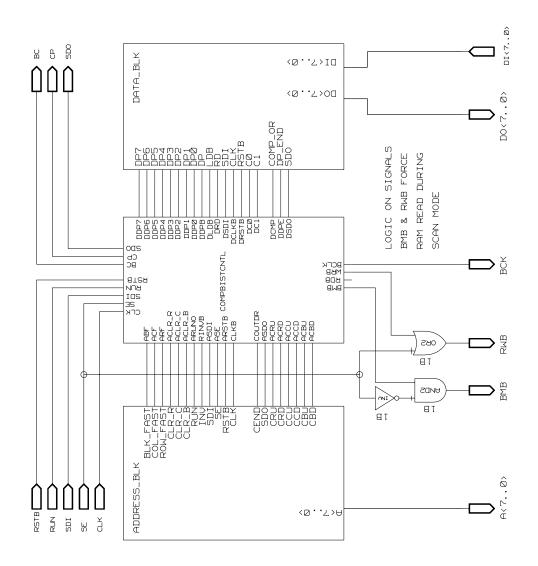

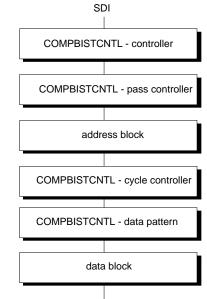

The Comparator BIST uses the 21N march, a deterministic test algorithm, designed to test for hard memory faults. Complete 100% fault coverage is possible using this algorithm. The Comparator BIST also provides additional capabilities: memory diagnostics, memory clear, fault location, and address stress test. This additional capability makes the Comparator BIST much more powerful and complex than the Pseudo Random BIST. The Comparator BIST provides this superior performance with the penalty of greater circuit complexity and a high gate count. Construction of the Comparator BIST requires additional information on the physical implementation of the RAM. In addition to the number of RAM words and word width; it will be necessary to know the number of word lines in the row decoder, the width of column decoder, and number of blocks in the final RAM. Please refer to Figure 9.

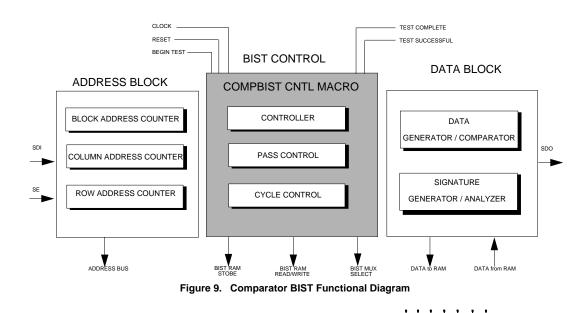

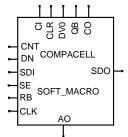

The Comparator BIST design utilizes three soft macros (COMPBISTCNTL, COMPACELL, & COMPD-CELL) found in the H4CP library. See Figure 10, 11, & 12. Using these soft macros and additional logic, a comparator BIST circuit can be built for any Motorola supplied RAM block.

**COMPBISTCNTL** controller block of the Comparator BIST.

**COMPACELL** up/down counter macro in the Comparator BIST "address block".

**COMPDCELL** data generator/analyzer macro in the Comparator BIST "data block".

A Comparator BIST design has three functional blocks: See Figure 9.

The "**controller block**" orders and synchronizes BIST testing. The "controller block" uses a single COM-PBISTCNTL soft macro of the H4CP library. The COM-PBISTCNTL contains three functional units: controller, pass control, cycle control. <u>controller</u> - interfaces between the control lines and the operation of the comparator BIST module. It determines the type of operation being performed, the number of passes, the type of data analysis, status of comparison test, and if BIST test is complete.

pass controller - manages the seven cycles in each pass of 21N march and controls the data polarity. It also determines which cycles should use the wait count in the data retention test.

cycle controller - manages the three phases in each cycle and controls the data polarity. It also provides an override for the "RDB" and "WRB" lines allowing direct memory access. The cycle consists of (read\_X, write\_Y, read\_Y) where "X" is the inverse pattern of "Y". The first read is suppressed in cycles 1 & 2.

The "address block" contains the RAM address up/down counters. The "address block" uses the COM-PACELL soft macro from the H4CP library. The "address block" will have a separate counter to test each type of address decoder individually (i.e. row decoder, column decoder, & block decoder). See Note\*

The "data block" contains the RAM data generator/ analyzer. The "data block" uses the COMPDCELL soft macro from the H4CP library. The "data block" will generate the deterministic 21N march data patterns and act as a Linear Feedback Shift Register (LFSR) during BIST signature generation.

#### <u>Note:</u>

Currently all RAMs supplied by Motorola ASIC are partitioned into only rows and columns. The block testing capability will not be necessary unless the design utilizes multiple block memories.

Additional logic will be required at the BIST's top hierarchy level to assure proper circuit timing.

### I/O description of COMPACELL

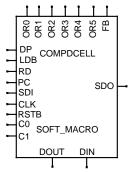

Figure 11. COMPDCELL Soft Macro

# I/O description of COMPDCELL

| ONT                                              | •<br>                                                                    | an unit an abla                                                                                                           | I/O description of COMPDCELL                                                        |                                                                                                                   |                                                                                                                                                                                                                                                                                                                                   |  |

|--------------------------------------------------|--------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| CNT<br>DN<br>RB<br>CLR<br>CI                     | input<br>input<br>input<br>input<br>input                                | count enable<br>count direction<br>synchronous reset<br>count clear<br>carry in                                           | LDB<br>RD<br>PC<br>RSTB                                                             | input<br>input<br>input<br>input                                                                                  | load RAM data<br>read<br>previous data bit<br>synchronous reset                                                                                                                                                                                                                                                                   |  |

| CLK<br>DVO<br>SDI<br>SE<br>CO<br>AO<br>SDO<br>QB | input<br>input<br>input<br>input<br>output<br>output<br>output<br>output | clock<br>highest bit value<br>scan data in<br>scan enable<br>carry out<br>address bit out<br>scan data out<br>inverted A0 | CLK<br>DIN<br>SDI<br>DP<br>OR0<br>OR1<br>OR2<br>OR3<br>OR4<br>OR5<br>FB<br>C0<br>C1 | input<br>input<br>input<br>input<br>input<br>input<br>input<br>input<br>input<br>input<br>input<br>input<br>input | clock<br>BIST data input<br>scan data in<br>data pattern<br>data bit order 0<br>data bit order 1<br>data bit order 2<br>data bit order 3<br>data bit order 3<br>data bit order 4<br>data bit order 5<br>LFSR feedback<br>ctrl 0 0 - signature analysis<br>ctrl 1 1 - analyze RAM data<br>2 - generate RAM data<br>3 - scan enable |  |

|                                                  |                                                                          |                                                                                                                           | DOUT<br>SDO                                                                         | output<br>output                                                                                                  | BIST data output<br>scan data out                                                                                                                                                                                                                                                                                                 |  |

MOTOROLA

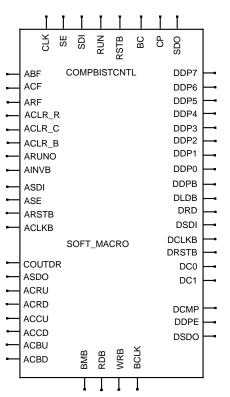

Figure 12. Comparator BIST Soft Macro Symbol COMP-BISTCNTL

#### ABF output address block fast address column fast ACF output ARF output address row fast ACLR\_R output address clear row ACLR\_C output address clear column ACLR\_B output address clear block ARUN0 output address run AINVB output count up/down control address scan data in ASDI output ASE output address scan enable ARSTB output address reset ACKB output address clock COUNTDR input carry out data retention ASDO input address scan data output ACRU input address carry row up ACRD input address carry row down ACCU input address carry column up ACCD address carry column down input ACBU input address carry block up ACBD address carry block down input DDP7 output data position 7 DDP6 output data position 6 DDP5 output data position 5 DDP4 output data position 4 DDP3 output data position 3 DDP2 output data position 2 DDP1 output data position 1 DDP0 output data position 0 DDPB output data polarity bar DLDB output data load bar DRD output data read data serial data in DSDI output DCLKB output data clock DRSTB output data reset DC0 data encoded control 0 output data encoded control 1 DC1 output 0 - signature analysis 1 - analyze RAM data 2 generate RAM data 3 - scan enable DCMP \*\*\* input data compare DDPE \*\*\* data pattern end input DSDO input data serial data out BMB BIST mode output RDB RAM read output WRB RAM write output

I/O description of COMPBISTCNTL

\*\*\*<u>WARNING</u> -- RAMs having only a 1 or 2 bit word length cause a DDPE generation exception due to limitations in the COMPBISTCNTL soft macro. DDP1 = DDPE is technically the correct choice for 1 and 2 bit wide RAMs. Simulation has shown that using DDP1 = DDPE causes unpredictable behavior of COMP-BISTCNTL. The COMPBISTCNTL state machine cannot take an pattern end that early. For 1 and 2 bit wide RAM, use DDP2 = DDPE and use the logic "or" of C(0) and C(1) for generation of DCMP.

BIST clock

output

BCLK

#### 2.1. Comparator BIST Test Description

The comparator BIST uses multiple test methods to verify the RAM operation. Multiple data patterns are used to check for interactions between bits. Address decoders are tested at full speed with three "fast" tests. The RAM data array is checked using a deterministic 21N march. A statistical signature analysis is done to verify both the BIST and RAM. The comparator BIST also supports additional debug and characterization capabilities including stop on fault, RAM control through scan path control, and limited data retention testing.

The standard testing order of the comparator BIST is: Data pattern #1

block fast 21N march with "block" addressing

column fast

21N march with "column" addressing row fast

21N march with "row" addressing

Data pattern #2

column fast

# Data pattern #3

Data pattern #FINAL

block fast 21N march with "block" addressing column fast 21N march with "column" addressing row fast

21N march with "row" addressing

signature test

#### 21N march RAM test pattern sequence

The comparator BIST utilizes a 21N march pattern to locate RAM coupling faults. The 21N march consists of 7 phases, each phase with 3 cycles. In phase 1, 2, 3, & 4 the address is incremented from its lowest to highest value. In phase 5, 6, & 7, the address is decremented from its highest to lowest value. Each of the seven phases has 3 cycles consisting of a Read, Write, Read pattern. All three cycles are completed at a data location before the address is changed. At address 0, the three cycles (R,W,R) are completed before the address is incremented (decremented). At the second address, the three cycles (R,W,R) are again completed before the address is incremented (decremented). The cycles continues until the reaching highest (lowest) address. There the current phase completes and the address is initialized for the next phase. At the end of phase seven, the 21N march algorithm is complete.

Table 5. 21N March Algorithm

| Phase   | (CY1,CY2,CY3) | first address | last address | address<br>counter |

|---------|---------------|---------------|--------------|--------------------|

| Phase 1 | (, W0, R0)    | lowest "0"    | highest      | increment          |

| Phase 2 | (, W1, R1)    | lowest "0"    | highest      | increment          |

| Phase 3 | (R1, W0, R0)  | lowest "0"    | highest      | increment          |

| Phase 4 | (R0, W1, R1)  | lowest "0"    | highest      | increment          |

| Phase 5 | (R1, W0, R0)  | highest       | lowest "0"   | decrement          |

| Phase 6 | (R0, W1, R1)  | highest       | lowest "0"   | decrement          |

| Phase 7 | (R1, W0, R0)  | highest       | lowest "0"   | decrement          |

Notes:

The first read is ignored in phase 1&2 because the RAM is not considered initialized.

W0 - indicates writing the data pattern from the data generator (no inversion)

W1 - indicates writing the inverted data pattern from the data generator

### Block Fast, Column Fast, Row Fast - Test Addressing

RAMs commonly have up to three types of address decoders: block select, column multiplexer, and row decoder. The comparator BIST can control each address decoder individually to test each at full speed.

The standard 21N march algorithm moves directly through the address field. Depending on the address multiplexing scheme, it could be several RAM cycles before an address decoder changes state. In the three "fast" tests the address will be changed in some "modulo" fashion so that in block\_fast testing, the block address decoder changes state every RAM cycle. In row\_fast testing the row decoder changes state every RAM cycle and in column\_fast testing the column decoder changes state each RAM cycle.

Example: An 8 word RAM has 2 blocks, 2 rows, and 2 columns. The three address bits are in the following fields: (blk, row, column) {msb-lsb}.

| block_fast addressing order:  | 000, | 100, | 001, | 101, | 010, | 110, | 011, | 111 | (0 4 1 5 2 6 3 7 modulo 4) |

|-------------------------------|------|------|------|------|------|------|------|-----|----------------------------|

| row_fast addressing order:    | 000, | 010, | 100, | 110, | 001, | 011, | 101, | 111 | (0 2 4 6 1 3 5 7 modulo 2) |

| column_fast addressing order: | 000, | 001, | 010, | 011, | 100, | 101, | 110, | 111 | (0 1 2 3 4 5 6 7)          |

These three address decoder tests are hard coded into the "COMPBISTCNTL" macro. The customer will configure a counter in the comparator BIST address block for each address decoder to be tested. Current H4CP diffused RAMs have only column and row decoders. H4CP metallized RAMs have only row (word) decoders. Unused "fast" tests will be repeated on one of the RAMs address decoder.

#### Comparator BIST data pattern generation

In order to fully test RAM's data array, multiple passes of the block\_fast, row\_fast, and column\_fast tests are performed using different data patterns. The background patterns are used to prove adjacent RAM bits will not affect the logic state of each other. The COMP-BISTCNTL/COMPDCELL logic can provide these independent test patterns for RAMs up to 128 bits wide.

The comparator BIST data pattern generator will use up to eight background patterns. The comparator BIST's 21N march algorithm uses the data patterns for the "R0" and "W0" data. It uses the <u>inverted</u> data pattern for the "R1" and "W1" data.

The number of background used depend on the RAM data width. The final data pattern always has all bits equal zero. For a 8 bit RAM the four backgrounds used are:

| 10101010 | pattern 1 |

|----------|-----------|

| 11001100 | pattern 2 |

| 11110000 | pattern 3 |

| 00000000 | pattern 4 |

The data pattern backgrounds are described in the following information.

#### Data Generator Background Pattern

| State |          | (maximum of 128 bits wide - 64 bits shown)   | data LSB            | PATTERN                 |

|-------|----------|----------------------------------------------|---------------------|-------------------------|

| 000   | 10101010 | 10101010 10101010 10101010 10101010 10101010 | 0 10101010 10101010 | 1(1's), 1(0's) repeat   |

| 001   | 11001100 | 11001100 11001100 11001100 11001100 11001100 | 11001100 11001100   | 2(1's),2(0's) repeat    |

| 010   | 11110000 | 11110000 11110000 11110000 11110000 11110000 | 11110000 11110000   | 4(1's), 4(0's) repeat   |

| 011   | 11111111 | 00000000 11111111 00000000 11111111 000000   | ) 11111111 00000000 | 8(1's), 8(0's) repeat   |

| 100   | 11111111 | 11111111 0000000 0000000 11111111 111111     | 00000000 00000000   | 16(1's), 16(0's) repeat |

| 101   | 11111111 | 11111111 1111111 11111111 0000000 000000     | 00000000 00000000   | 32(1's), 32(0's) repeat |

| 110   | 00000000 | 0000000 0000000 0000000 0000000 0000000      | 00000000 00000000   | 64(1's), 64(0's)        |

| 111   | 00000000 | 0000000 0000000 0000000 0000000 0000000      | 0000000 00000000    | 128(0's)                |

#### 2.2. Comparator BIST data analyzer

The data analyzer compresses the memory check information. The data analyzer has two distinct operating modes: data comparison and signature analysis.

During the data comparison testing a "1" is stored in the corresponding data analyzer bit for any RAM bit that doesn't match the expected pattern. In a characterization mode the Comparator BIST can be initialized to halt on the first data miss-match. Normally the memory is checked and the failing bits are marked. If any data errors are found, the CP (comparator pass) line will be set low and the test will stop before signature analysis is run.

During the signature analysis testing the data analyzer is configured into a Linear Feedback Shift Register (LFSR). During the "write" mode, the LFSR generates a pseudo-random data pattern for the RAM. During "read" mode, the RAM data will be fed into the same LFSR to build the RAM test signature. At the completion of the signature analysis the final signature is stored in the data analyzer. No comparison is done on the signature. External comparison logic must be added or the signature must be scanned out for comparison. The signature analysis verifies the operation of both the RAM and BIST circuitry. The LFSR must be sufficient length to avoid signature aliasing.

#### 2.3. Signature Aliasing

see section 6.3.2 on page 5 for Signature Aliasing

#### 2.4. Comparator BIST Construction

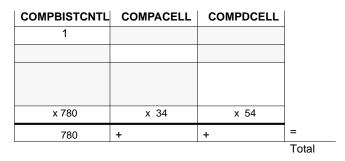

## 2.4.1. Gate count estimate of the Comparator BIST

A gate count estimate can be generated by counting the required COMPACELL, COMPDCELL, and COMP-BISTCNTL macros in the comparator BIST. Logic for generating BIST control signals and the RAM mux have been ignored.

#### Number of macros required

one COMPBISTCNTL macro

one COMPACELL for each RAM address line

choose the greater number of COMPDCELLs

- a) one COMPDCELL for each RAM data line

- b) 12 COMPDCELLs to minimize signature aliasing Multiply by equivalent gates per macro<u>x</u>

Sum number of equivalent gates total\_

# 2.4.2. Construction of a Comparator BIST

The construction of the comparator BIST will be described by drawing its schematic. Please refer to Figure 13, 14, & 15. The comparator BIST will be for testing a 192x8 RAM. The addressing is configured as 8 columns and 24 rows. (A full 256x8 ram in this configuration would have 8 columns and 32 rows) The comparator BIST will consist of:

- 1. an address block with a column counter and a row counter to generate A(0,7).

- 2. a controller block with a single COMP-BISTCNTL macro

- 3. a data block with a 12 bit data generator/analyzer to evaluate DI(0,7) & DO(0,7).

<u>Note:</u>

The signal names given in this description are used to identify nodes on the illustrations. It is not a requirement that customer designs use this naming convention.

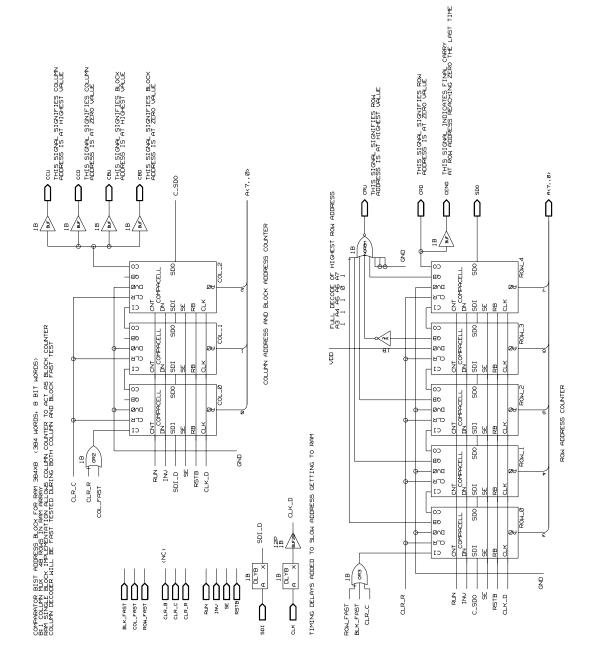

# 2.4.3. Construction of Comparator BIST address block

Please contact your Motorola ASIC representative for specific information on RAM implementation. Before a comparator BIST can be constructed certain information must be known:

- 1. Size of RAM, number of words, bits per word.

- 2. RAM memory array structure; use of block, row, & column decoders

- 3. the correspondence between the RAM address lines and the decoder they control

The diffused RAMs supplied by Motorola ASIC currently use only row and column address decoders. There are no block decoders in the diffused RAMs (this might be implemented in the customer design). Current Motorola supplied RAMs have the column decoder driven by the lowest address bits. The row decoder is driven by the higher address bits. The COMP-BISTCNTL macro is hardwired to execute all three tests, block fast, column fast, and row fast. In this ex-

ample the column counter will drive both the block\_fast & column\_fast control signals. Therefore the comparator BIST will run the column\_fast test twice, and the row\_fast test once. The choice to repeat the column\_fast test was an arbitrary one. There will be no difference in test time. Please refer to Figure 13.

#### Placement of macros for address block.

- For the column counter place one COMPA-CELL for each RAM address line going to the column decoder. In this example, three address bits are required for an 8:1 column decoder, and three COMPACELLs will be needed. The COM-PACELL on the left will generate the A0 signal, the middle COMPACELL will generate the A1 signal, the right COMPACELL will generate the A2 signal.

- 2. For the row counter place one COMPACELL for each RAM address line going to the row decoder. In this example, five address bits required to decode the 24 rows, five COMPA-CELLs macros will be required. The left most row counter COMPACELL will generate the A4 signal. The right most COMPACELL will generate the A7 signal.

#### Connection of the address block.

- Connect all COMPACELL pin "CNT" to a common node named "RUN". This will later connect to the COMPBISTCNTL signal "ARUN0".

- Connect all COMPACELL pin "DN" to a common node named "INV". This will later connect to the COMPBISTCNTL signal "RINVB"

- Connect all COMPACELL pin "SE" to a common node named "SE". This will later connect to the COMPBISTCNTL signal "ASE".

- 4. Connect all COMPACELL pin "RB" to a common node named "RSTB". This will later connect to the COMPBISTCNTL signal "ARSTB".

- 5. Connect all COMPACELL pin "CLK" to a common clock node named "CLK". Timing analysis may show this clock will need to be delayed from the COMPBISTCNTL signal "ACLKB" to eliminate hold time violations on the RAM address lines. If so, rename the signal "CLK" to "CLK\_D" (delayed), connect the COMP-BISTCNTL signal "ACLKB" to a delay macro (i.e. DLY8), and use the output to drive the common node "CLK\_D".

- Connect the <u>column counter's</u> COMPACELL pin "CLR" to a common node named CLR\_C. This will later connect to the COMPBISTCNTL signal "ACLR\_C".

- 7. Connect the <u>row counter's</u> COMPACELL pin "CLR" to a common node named CLR\_R. This will later connect to the COMPBISTCNTL signal "ACLR\_R".

- 8. Drive the column counter's LSB COMPACELL pin "CI" (example's "A0") with the logical "OR"ing of the COMPBISTCNTL signals "ACF" and "ACLR\_R". The effect is that the column counter will be enabled during the column\_fast testing and toggled at the end count of a row\_fast test. (by default it will also be toggled at the end of the block\_fast test).Connect the remaining column counter COMPACELL pin "CI" by the "CO" pin on the COMPACELL macro on the left. (i.e. "A1\_CI" is driven by "A0\_CO" and "A2\_CI" is driven by "A1\_CO")

- 9. The column counter's MSB COMPACELL pin "CO" (example's "A2") will drive the COMP-BISTCNTL signals "ACCU", "ACCD", "ACBU", and "ACBD". This is possible since the "CO" signal is active both when the column counter reaches its maximum count "7" and its minimum count "0". If the number of column were not a "power of 2" number (i.e. 2,4,8, or 16), additional maximum count logic would be required. This maximum count logic would then drive the "ACCU" and "ACBU" signals. Still, the signals "ACCD" and "ACBD" would be driven by the "CO" signal.

- 10. Drive the row counter LSB COMPACELL pin "CI" (example's "A3") with the logical "OR"ing of the COMPBISTCNTL signals "ABF", "ARF", and "ACLR\_C". The effect is that the row counter will be enabled during both the block\_fast and the row\_fast testing or toggled at the end count of a column\_fast test.

- 11. Connect the remaining row counter COMPA-CELL pin "CI by the "CO" output pin on the

COMPACELL macro on the left. (i.e. "A4\_CI is driven by "A3\_CO", "A5\_CI" is driven by "A4\_CO", etc.)

- 12. The row counter's MSB COMPACELL pin "CO" (example's "A7") will drive the COMPBISTCNTL signal "ACRD". In the example "24" is defined as the number of rows. Logic which decodes the COMPACELL "QB" output for the maximum row address, generates the COMPBISTCNTL "ACRU". If the row counter was addressing a "power of 2" number of rows (i.e. 2,4,8,16,32,64, etc.), the row counter's MSB COMPACELL pin "CO" (A7) could have driven both the COMPBISTCNTL signal "ACRU" & "ACRD".

- 13. The following connection is for a special data retention test mode, use the row counter's MSB COMPACELL pin "CO" (A7) signal to drive the COMPBISTCNTL signal "COUTDR".

- 14. The COMPACELL input "DV0" pin defines the macro's maximum count value. If the maximum count value is a "power of 2" value (2, 4, 8, 16, 32, 64, etc.) ground all COMPACELL "DV0" pins. This will load all "1's" into the counter. If the maximum count value is not a "power of 2" value, the maximum count bit state is loaded in by the "DV0" pin. The "DV0" loads the inverse of the maximum count bit state (beware).

- 15. Scan path connection: Connect the COMP-BISTCNTL "ASDI" signal to the RAM's LSB address bit's COMPACELL (example's "A0") "SDI" input. It may be necessary to delay this signal as the CLK signal to avoid scan path timing problems. Connect the "SDO" pin to the next greatest address bit's COMPACELL "SDI" pin. ("A0\_SDO" to "A1\_SDI", "A1\_SDO" to "A2\_SDI", "A2\_SDO" to "A3\_SDI", etc.) The highest address bit's COMPACELL (example's "A7") "SDO" pin will drive the COMPBISTCNTL "ASDO" pin.

- 16. BIST address line connections: Connect the column counter LSB to the BIST A(0) pin. Continue connecting all the COMPACELL's "A0" pins to the appropriate BIST address lines. The actual connections depend on the exact implementation of the RAM's address decoding scheme. In this example the column counter connects to the BIST address lines first. Then the row counter connects to the upper bits in the BIST address lines.

Figure 13. Comparator BIST address block.

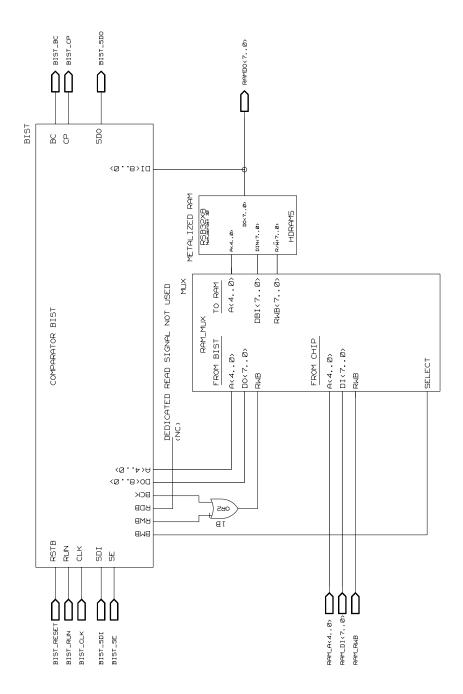

### 2.4.4. Construction of Comparator BIST data block

Before the Comparator BIST can be constructed it will be necessa4ry to know.Please refer to Figure 14.

- 1. number of bits in RAM data word.

- signature length required to obtain the desired aliasing protection. Motorola ASIC recommends minimum of 12 bits.

### Placement of macros for data block.

- 1. Determine the number of COMPDCELLs necessary for the data block. Choose the larger of the two numbers:

- a) 12, chosen to minimize chance of

- signature aliasing. b) the number of data bits in the RAM's word.

- Place the COMPDCELLs in a ROW from left to right. To assist in connecting the feedback signal for the signature Linear Feedback Shift Register (LFSR), name the COMPDCELLs from right to left, FB\_1, FB\_2, FB\_3, FB\_4, etc.

### Connection of the data block.

- Connect all COMPDCELL pin "DP" to a common node named "DP". This will later connect to the COMPBISTCNTL signal "DDPB".

- Connect all COMPDCELL pin "LDB" to a common node named "LDB". This will later connect to the COMPBISTCNTL signal "DLDB".

- Connect all COMPDCELL pin "RD" to a common node named "RD". This will later connect to the COMPBISTCNTL signal "DRD".

- Connect all COMPDCELL pin "CLK" to a common node named "CLK". This will later connect to the COMPBISTCNTL signal "DCLKB". This clock signal does not usually need to be delayed.

- 5. Connect all COMPDCELL pin "C0" to a common node named "C0". This will later connect to the COMPBISTCNTL signal "DC0".

- Connect all COMPDCELL pin "C1" to a common node named "C1". This will later connect to the COMPBISTCNTL signal "DC1".

- Connection of the COMPDCELL pin "FB"; See Table 4 for the LFSR feedback tap connection for various lengths of LFSR. Connect the appropriate "FB" inputs to the inverted "SDO" output of the right most COMPDCELL. Any unconnected "FB" inputs will be grounded. In the example the COMPDCELLs have been named FB\_1, FB\_2, to correspond to Table4.

- The six inputs on the COMPDCELL (OR5, OR4, OR3, OR2, OR1, OR0) will indicate the bit position in the RAM data word. These signals select the bit value for the test's background pattern. To connect the "ORx" signals the value of "0" indicates connecting to VSS. The value of "1"

indicates connecting the COMPDCELL "ORx" signal to the corresponding COMPBISTCNTL "DDPx" signal. The COMPDCELL which corresponds to RAM bit "D0" bit will be hardwired to "000000". The COMPDCELL which corresponds to RAM bit "D1" is hardwired to "000001". The COMPDCELL which corresponds to RAM bit "D2" is hardwired to "000010". The COMPDCELL which corresponds to RAM bit "D3" is hardwired to "000011". The COMPDCELL which corresponds to RAM bit "D4" is hardwired to "000100". This pattern will continue until all RAM data bits are located. If the COMPDCELL does not correspond to a RAM data bit (i.e. added for signature aliasing) tie all "ORx" signals to VSS.

- 9. The left most COMPDCELL (corresponds to RAM bit D0) SDI input will be driven by the COMPBISTCNTL "DSDI" signal.

- 10. The left most COMPDCELL (corresponds to RAM bit D0) PC input will be tied to VSS.

- 11. All other COMPDCELL "SDI" and "PC" inputs will be driven by the COMPDCELL "SDO" signal to its left.

- 12. The right most COMPDCELL (named FB\_1) SDO signal will drive the COMPBISTCNTL "DSDO" input.

- 13. To connect the COMPDCELL "DIN" pin; start at left most COMPDCELL and connect the "DIN" pin to RAM Dout(0) signal. The COMPDCELL immediately to the right will connect "DIN" to RAM Dout(1). Continue moving right until all RAM Dout bits are connected to a COMPD-CELL "DIN" pin. If the COMPDCELL does not correspond to a RAM data bit (i.e. added for signature aliasing) connect the "DIN" pin to VSS.

- 14. To connect the COMPDCELL "DOUT" pin; start at left most COMPDCELL and connect the "DOUT" pin to the RAM DI(0) signal. The COM-PDCELL immediately to the right will connect its "DOUT" pin to the RAM DI(1). Continue moving right until all RAM DI signals are connected to a COMPDCELL "DOUT" pin. If the COMPDCELL does not correspond to a RAM "DIN" signal (i.e. added for signature aliasing) leave the "DOUT" pin unconnected.

- 15. To generate the COMPBISTCNTL signal DDPE, invert the lowest numbered COMPBISTCNTL signal "DDPx" which is not connected to a COMPDCELL (example's "DDP3").

- 16.To generate the COMPBISTCNTL signal "DCMP", logic "OR" all COMPDCELL "SDO" pins which correspond to a RAM data bit. (i.e. NOT added just for signature aliasing).

Figure 14. Comparator BIST data block.

#### 2.5. Construction of Comparator BIST block

After the comparator BIST address block and data block are complete, construct the hierarchical icons/ bodies for both blocks. The three functional blocks, data, address, and COMPBISTCNTL will now be assembled for the final Comparator BIST schematic. Please refer to Figure 15.

# Placement of macros for Comparator BIST.

- 1. Place the hierarchical icon/body for the comparator BIST address block.

- 2. To its right place the COMPBISTCNTL macro.

- 3. To their right place the hierarchical icon/body for the comparator BIST data block.

#### Connection of the comparator BIST block.

Connection between the address block and the COMPBISTCNTL macro were discussed in 2.5.1 Construction of Comparator BIST address block. Use the following connections.

| ADDRESS BLOCK                                                                                                                                                  | to                                                                                                                                                                   | <u>COMPBISTCNTL</u>                                                                                                                                                                                                                                                                                                                                                         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BLK_FAST<br>COL_FAST<br>ROW_FAST<br>CLR_R<br>CLR_C<br>CLR_B<br>RUN<br>INV<br>SDI<br>SE<br>RSTB<br>CLK<br>CEND<br>SDO<br>CRU<br>CRD<br>CCU<br>CCD<br>CBU<br>CBD | ABF<br>ACF<br>ARF<br>ACLR_R<br>ACLR_C<br>ACLR_B<br>ARUN0<br>RINBB<br>ASDI<br>ASE<br>ARSTB<br>ACLKB<br>COUTDR<br>ASDO<br>ACRU<br>ACRD<br>ACCU<br>ACCD<br>ACBU<br>ACBD | block fast test<br>column fast test<br>row fast test<br>clear row counter<br>clear column counter<br>clear block counter<br>All counter enable<br>Increment/Decrement<br>scan data input<br>scan enable<br>reset<br>clock<br>data retention test carry<br>scan data output<br>row count up carry<br>row count up carry<br>column count down carry<br>block count down carry |

Connections between the COMPBISTCNTL macro and the data block were discussed in 2.6 Construction of Comparator BIST data block. Use the following connections.

DATA BLOCK to COMPBISTCNTL