*Communications and Advanced Consumer Technologies Group*

# Application Note Low Power on the SCM68000 (EC000 Core)

The SCM68000 (EC000 core) has been redesigned to provide low-power, fully static operation. This document describes the recommended method for placing the SCM68000 into low-power mode to reduce power consumption to its quiescent value<sup>1</sup> while maintaining the internal state of the processor. The low-power mode described below is part of the SCM68000 test vectors that Motorola provides.

The terms *assertion* and *negation* are used in this document to avoid confusion when describing a mixture of "active-low" and "active-high" signals. The term *assert* or *assertion* indicates that a signal is active or true, regardless of whether a high or low voltage represents that level. The term *negate* or *negation* indicates that a signal is inactive or false. The names of all "active-low" signals end with the letter *B*.

#### **RESETTING THE SCM68000**

Note:

Although the SCM68000 is a fully static device, it cannot be put into low-power mode until after it has completed the reset exception processing that is described in **Section 4.3.1 Reset** of the *EC000 Core Processor User's Manual*.

Warning: During and after reset exception processing, the SCM68000 will not be in a low-power state. The processor must be reset with the clock running, which is detailed in Section 4.3.1.1 Reset Operation in the *EC000 Core Processor User's Manual*. Once the SCM68000 is properly reset, the internal circuitry is in a valid state and can be put into low-power mode. Low-power mode process that is described in this document must be followed or the SCM68000 will not be in a low-power state.

## **ENTERING LOW-POWER MODE**

To successfully enter the low-power mode, the SCM68000 must be in the supervisor mode. The **trap** instruction should be used to enter low-power mode because it causes the processor to begin exception processing and enter supervisor mode. During the trap routine, the external circuitry should follow a sequence of steps to enable low-power mode.

<sup>&</sup>lt;sup>1.</sup>The current drain specification for the SCM68000 while in low-power mode is I<sub>dd</sub> < 2µA at 3.3V and <5µA at 5V.

This document contains information on a product under development. Motorola reserves the right to change or discontinue this product without notice.

Warning: If RESETIB is asserted while the SCM68000 is in low-power mode, the clock to the processor will be restarted and the processor will begin reset exception processing. Refer to Section 4.3.1 Reset in the *EC000 Core Processor User's Manual* to properly reset the device.

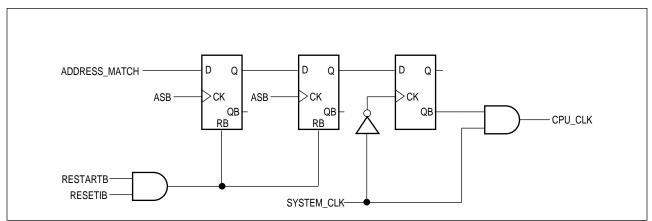

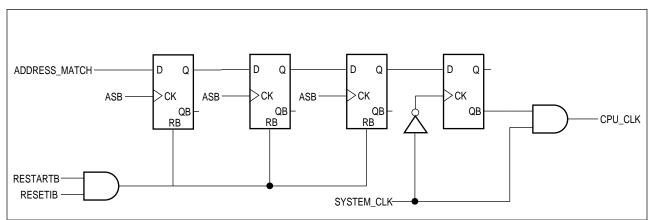

1. Externally detect a write to the low-power address. This user-selected address can be any in the 4G addressing range of the SCM68000. A write to the low-power address can be detected when RWB is a logic low, the function codes have a five (101) on their output, and the address bus contains the low-power address. At this time, the user-designed circuitry should assert the ADDRESS\_MATCH signal shown in Figure 1 or 2.

Figure 1. Low-Power Circuitry for 16-Bit Data Bus

Figure 2. Low-Power Circuitry for 8-Bit Data Bus

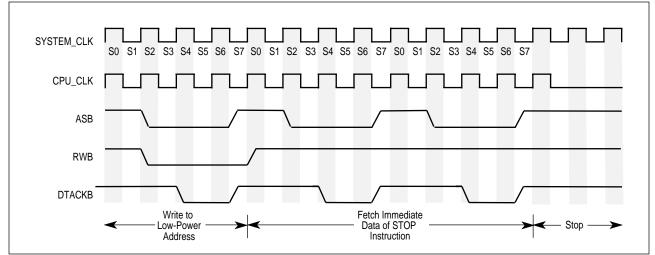

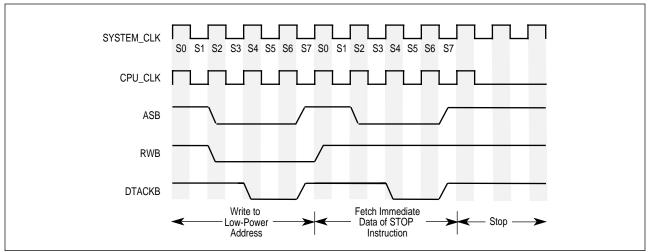

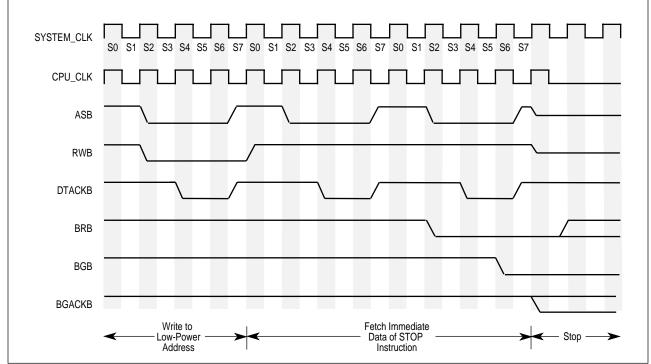

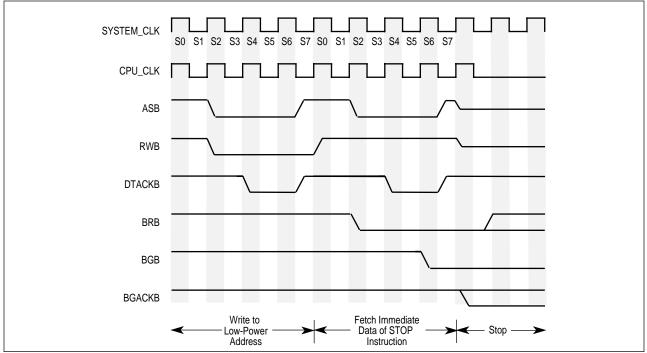

2. Execute the stop instruction. Using the stop instruction, set the interrupt mask level to bring the SCM68000 out of low-power mode. For example, the instruction stop #\$2300 sets the interrupt mask level to 3 and any interrupt higher than level 3 will tell the processor to start executing instructions. The external circuitry shown in Figures 1 and 2 will count the number of bus cycles starting with the write to the low-power address. It will stop the processor's clock on the first falling edge of the system clock after the bus cycle that reads the immediate data of the stop instruction. Figure 2 has one more flip-flop than Figure 1 because the SCM68000 in 8-bit mode requires two bus cycles to fetch the immediate data of the stop instruction. After the processor's clock is disabled, you can disable the clock to other sections of your system. Use caution to ensure that runt clocks and spurious glitches are not presented to the SCM68000. Figures 3 and 4 illustrate the timing diagrams for the 8- and 16-bit modes, respectively.

Figure 3. Clock Stop Timing for 8-Bit Data Bus

Figure 4. Clock Stop Timing for 16-Bit Data Bus

Note: While the SCM68000 is in low-power mode, all inputs must be driven to  $V_{DD}$  or  $V_{SS}$  or have a pull-up or pull-down resistor.

3. This step is optional depending on whether your applications need the three-stateable signals of the SCM68000 to be placed in a high-impedance state. To place the SCM68000 into a three-state condition, complete the proper method for arbitrating the bus during the status register data fetch for the **stop** instruction. The timing diagrams with the bus arbitration sequence are illustrated in Figure 5 (8-bit mode) and Figure 6 (16-bit mode). Refer to **Section 3.2 Bus Arbitration** in the *EC000 Core Processor User's Manual* for more information.

Figure 5. Clock Stop Timing with Bus Arbitration for 8-bit Data Bus

Figure 6. Clock Stop Timing with Bus Arbitration for 16-bit Data Bus

#### **EXITING LOW-POWER MODE**

Once you complete the previous steps, the SCM68000 remains in low-power mode until the clock is restarted. To restart the clock, external logic must poll IPLB2–IPLB0 to detect an interrupt higher than the one set in the **stop** instruction in step 2 of the previous section. When the correct interrupt level is received, follow these steps to bring the processor out of low-power mode:

- 1. Restart the system clock if it was stopped.

- 2. Wait for the system clock to become stable.

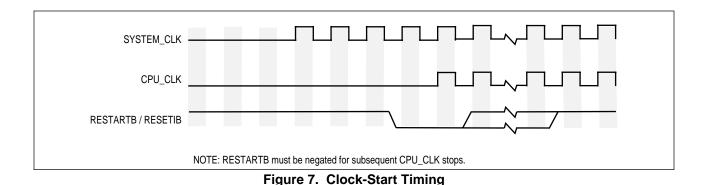

Assert the RESTARTB signal. This will cause the processor's clock to start on the next falling edge of the system clock. Figure 7 shows the timing for bringing the processor out of low-power mode. Both the RESTARTB and RESETB signals are subject to the asynchronous setup time that is specified in **Section 7 Electrical Characteristics** of the *EC000 Core Processor (SCM68000) User's Manual.*

**Note:** The processor will not recognize an interrupt until the clock has been restarted. If the external logic asserts RESTARTB with an interrupt level lower than the processor mask level, the **stop** instruction will not complete even though the clock has been restarted. To prevent glitches, the system clock must be stable before the RESTARTB signal can be asserted. An unstable clock can cause unpredictable results in the SCM68000.

3. If the SCM68000 was placed into a three-state condition, the BGACKB signal (used for 3-wire bus arbitration) or the BRB signal (used for 2-wire bus arbitration) must be negated before the processor

## **EXAMPLE TRAP ROUTINE**

can execute instructions.

TRAP\_xMOVE.B #0,\$low\_power\_address/\* Write that causes ADDRESS\_MATCH to

assert \*/

STOP #\$2000/\* STOP instruction with desired

interrupt mask \*/

RTE/\* Return from the exception \*/

The first instruction (**move.b** #0,\$low\_power\_address) writes a byte to the low-power address that notifies the external circuitry to begin the sequence that will stop the processor's clock. The second instruction (**stop** #\$2000) is the **stop** instruction that loads the status register with the immediate data that allows you to set the interrupt that will make the processor exit low-power mode. The final instruction (**rte**) signals the processor to return from the exception and resume normal processing.

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters can and do vary in different applications. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the substoner's statistical application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and (m) are registered trademarks of Motorola, Inc. Notorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

#### Literature Distribution Centers:

USA/EUROPE: Motorola Literature Distribution; P.O. Box 20912, Arizona 85036. JAPAN: Nippon Motorola Ltd.; 4-32-1, Nishi-Gotanda, Shinagawa-ku, Tokyo 141 Japan. ASIA-PACIFIC: Motorola Semiconductors H.K. Ltd.; Silicon Harbour Center, No. 2 Dai King Street, Tai Po Industrial Estate, Tai Po, N.T., Hong Kong.

#### SEMICONDUCTOR PRODUCT INFORMATION