# Motorola Semiconductor Application Note

# AN1740

# Applications Using the Analog Subsystem on MC68HC05JJ/JP Series Microcontrollers

By Mark L. Shaw

Member, Technical Staff, Sensor Products Division Transportation Systems Group Phoenix, Arizona

#### Introduction

The MC68HC05JJ/JP series of microcontrollers (MCUs) presents a unique combination of traditional digital peripherals with simple analog components which can be used to implement a variety of special functions.

These analog features include:

- A pair of voltage comparators

- Input channel multiplexer (MUX)

- A current source

- A temperature sensing diode

- Associated control bits and flags

The simple nature of these analog features requires very little silicon die area, but can provide functions normally seen in larger and more expensive MCUs. The designer has a great deal of flexibility in using these simple analog features; but with this flexibility comes the need to understand how these features can be combined and how they might

interact with each other. The intent of this application note is to present a range of uses for the MC68HC05JJ/JP analog features with details on how to set them up. It also points out some pitfalls the designer might encounter.

This application note covers these 12 topics:

- Analog subsystem overview

- Voltage comparators

- Current source/discharge

- Analog signal multiplexers

- Support circuitry

- Analog power-up considerations

- Analog-to-digital (A/D) conversion

- Pitfalls in using single slope A/D

- Manual A/D conversions

- Automated A/D conversions

- General A/D techniques

- Design check list

All members of the MC68HC05JJ/JP series of MCUs have the same analog subsystem and support timers, and they all have the same interface and control registers for these functions. Therefore, this application note covers all these members equally. The variations between series members are in memory type, memory size, number of I/O (input/output) pins, and personality EPROM. The designer should consult the individual MCU technical data book for specific information about the features on each member.

**NOTE:** Examples of "typical" data are given in this application note so that the reader has an idea of the general behavior of the devices. These typical data are taken using a few samples of the devices and do not represent the full range of variation in the given parameter. For more information on the range of parameters, the reader should refer to the appropriate data sheet or consult the factory.

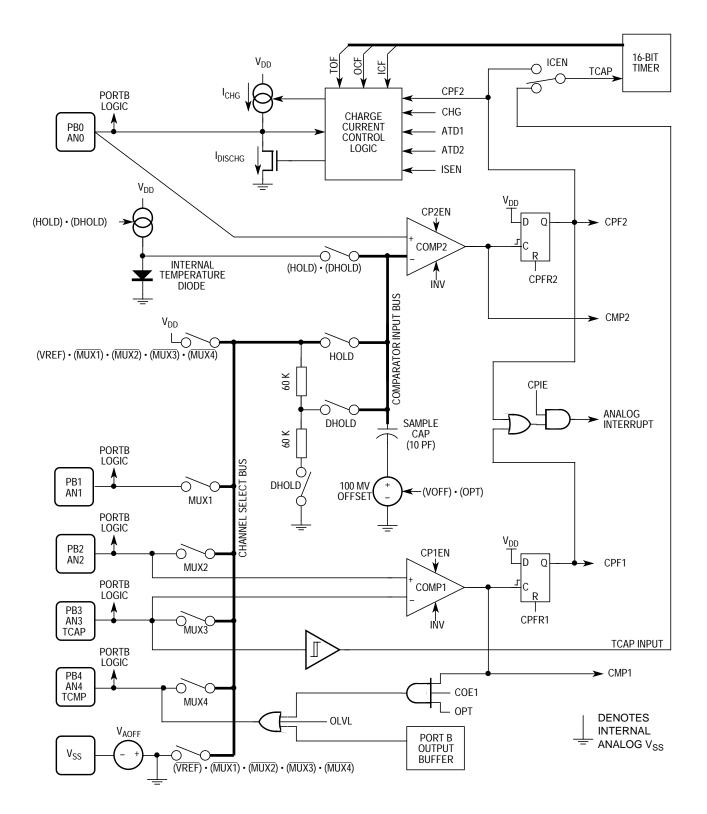

The block diagram of the analog subsystem is shown in **Figure 1**. The analog subsystem is structured around three basic components:

- Two voltage comparators

- A constant current source

An assortment of channel multiplexers, control logic, and control/status registers are provided in order to use these basic building blocks in typical analog interfaces.

| Voltage     | Each voltage comparator can compare voltages which are more than 1.5      |

|-------------|---------------------------------------------------------------------------|

| Comparators | volts below the $V_{DD}$ supply voltage. The input offset is typically 10 |

|             | millivolts and typical response time is less than a microsecond. Both     |

|             | comparators have identical performance and differ only in how they are    |

|             | connected to external pins. Each comparator can have its internal         |

|             | circuitry "flipped" so that any input offset can be referenced to either  |

|             | input. The value of this is included in the discussion of A/D techniques. |

|             | Each comparator also can be powered down to conserve supply current       |

|             | when its voltage comparison function is not needed.                       |

- Discharge Device A discharge device is also attached to the constant current source output. Either the current source is ON, the discharge device is ON, or both are OFF. This allows control of an external charge storage device,

such as a capacitor, to be attached to PB0 and used as an integrator which can be reset.

- ChannelVoltage comparator 2 can be interconnected to external pins andMultiplexerinternal sources using a 6-channel multiplexer.

- Input Divider The channel selection multiplexer can feed a voltage divider which allows the input signals to the channels to be higher than the common mode range of voltage comparator 2.

- Sample and Hold A provision at the input of comparator 2 is made for a sample and hold on an internal capacitor. The source for sample and hold can be the output of either the channel multiplexers or the input divider.

On-ChipThe temperature of the device can be inferred by measuring the voltageTemperatureon the internal diode. This voltage can be measured using the simpleSensing DiodeA/D convertor techniques discussed later.

Control/Status To use these basic building blocks in typical analog interfaces, there is Registers an assortment of channel multiplexers, control logic, and three registers containing 20 control bits and four status bits related to the analog subsystem. All the registers relating to the analog subsystem are shown in Figure 2.

These registers are:

- Analog MUX register (AMUX) at \$0003

- Analog control register (ACR) at \$001D

- Analog status register (ASR) at \$001E

- **NOTE:** Some analog features are enabled or disabled by an OPT bit. This OPT bit is in the mask option register (MOR) in the EPROM versions or is specified as a mask option on the ROM versions.

Figure 1. Analog Subsystem Block Diagram

| Addr.  | Register                       |                 | Bit 7  | 6     | 5           | 4          | 3       | 2     | 1     | Bit 0 |

|--------|--------------------------------|-----------------|--------|-------|-------------|------------|---------|-------|-------|-------|

| \$0001 | Port B data, PORTB             | Read:<br>Write: | PB7    | PB6   | PB5         | PB4        | PB3     | PB2   | PB1   | PB0   |

| \$0003 | Analog MUX register,<br>AMUX   | Read:<br>Write: | HOLD   | DHOLD | INV         | VREF       | MUX4    | MUX3  | MUX2  | MUX1  |

| \$0005 | Port B data direction,<br>DDRB | Read:<br>Write: | DDRB7  | DDRB6 | DDRB5       | DDRB4      | DDRB3   | DDRB2 | DDRB1 | DDRB0 |

| \$0011 | Port B pulldown, PDRB          | Read:<br>Write: | PDIB7  | PDIB6 | PDIB5       | PDIB4      | PDIB3   | PDIB2 | PDIB1 | PDIB0 |

| \$0012 | Timer control, TCR             | Read:<br>Write: | ICIE   | OCIE  | TOIE        | 0          | 0       | 0     | IEDG  | OLVL  |

| \$0013 | Timer status, TSR              | Read:<br>Write: | ICF    | OCF   | TOF         | 0          | 0       | 0     | 0     | 0     |

| \$0014 | Input capture MSB, ICRH        | Read:<br>Write: | Bit 15 | 14    | 13          | 12         | 11      | 10    | 9     | Bit 8 |

| \$0015 | Input capture LSB, ICRL        | Read:<br>Write: | Bit 7  | 6     | 5           | 4          | 3       | 2     | 1     | Bit 0 |

| \$0016 | Output compare MSB,<br>OCRH    | Read:<br>Write: | Bit 15 | 14    | 13          | 12         | 11      | 10    | 9     | Bit 8 |

| \$0017 | Output compare LSB,<br>OCRL    | Read:<br>Write: | Bit 7  | 6     | 5           | 4          | 3       | 2     | 1     | Bit 0 |

| \$001D | Analog control, ACR            | Read:<br>Write: | CHG    | ATD2  | ATD1        | ICEN       | CPIE    | CP2EN | CP1EN | ISEN  |

| \$001E | Analog status, ASR             | Read:<br>Write: | CPF2   | CPF1  | 0<br>CPFR2  | 0<br>CPFR1 | VOFF*   | COE1* | CMP2  | CMP1  |

|        |                                | = Unimplemented |        | d     | * Controlle | d by mask  | option. |       |       |       |

Figure 2. Analog Subsystem Related Registers

The voltage comparators are a basic design, but allow software compensation for the offset voltage. **Table 1** shows the main features of both voltage comparators. The common-mode voltage range is sufficient for most low-level signal sources, but may be a limiting factor for some applications where the input source must swing from  $V_{SS}$  to  $V_{DD}$ .

| Characteristic                                                                                                             | Symbol                                                           | Тур                  | Units          |

|----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|----------------------|----------------|

| Common mode input range                                                                                                    | V <sub>CMR</sub>                                                 | V <sub>DD</sub> -1.5 | V              |

| Input offset                                                                                                               | V <sub>IO</sub>                                                  | 10                   | mV             |

| Input impedance (with input pulldowns OFF)<br>Direct, either comparator<br>With divider connected to comparator 2          | Z <sub>IN</sub><br>Z <sub>IN</sub>                               | 1000<br>120          | kΩ<br>kΩ       |

| Response time<br>Output Switching (10 mV overdrive)<br>Power up delay (analog bias ON)<br>Power up delay (analog bias OFF) | t <sub>CPROP</sub><br>t <sub>CDELAY</sub><br>t <sub>CDELAY</sub> | 1<br>2<br>5          | μs<br>μs<br>μs |

| Supply current<br>Comparator only<br>Bias source for both comparators                                                      | I <sub>DDC</sub><br>I <sub>DDC</sub>                             | 100<br>65            | μΑ<br>μΑ       |

Table 1. Typical Voltage Comparator Features

Comparator 1 Comparator 1 is a basic voltage comparator with its positive and negative inputs tied permanently to the PB2 and PB3 pins respectively. Its output can be monitored by both dynamic output and static flag bits in the ASR (analog status register) located at address \$001E. The dynamic output bit, CMP1, becomes a logical 1 whenever the comparator's positive input is above its negative input and it follows the output of the comparator regardless of its prior conditions. The static flag bit, CPF1, becomes set whenever there is a rising output from the comparator and remains set until cleared by writing a logical 1 to the reset bit, CPFR1. Therefore, the CPF1 bit can be used to capture events when the comparator's positive input was above its negative input. Comparator 1, therefore, permits software subroutines to either poll the CMP1 or CPF1 bits or use an analog interrupt that is generated when the CPF1 bit is set.

Comparator 1 also has the provision to connect its output to the PB4 pin by setting the COE1 bit in the ASR. This makes this comparator useful for directly driving some external function. (The use of the COE1 bit is enabled by the OPT mask option.)

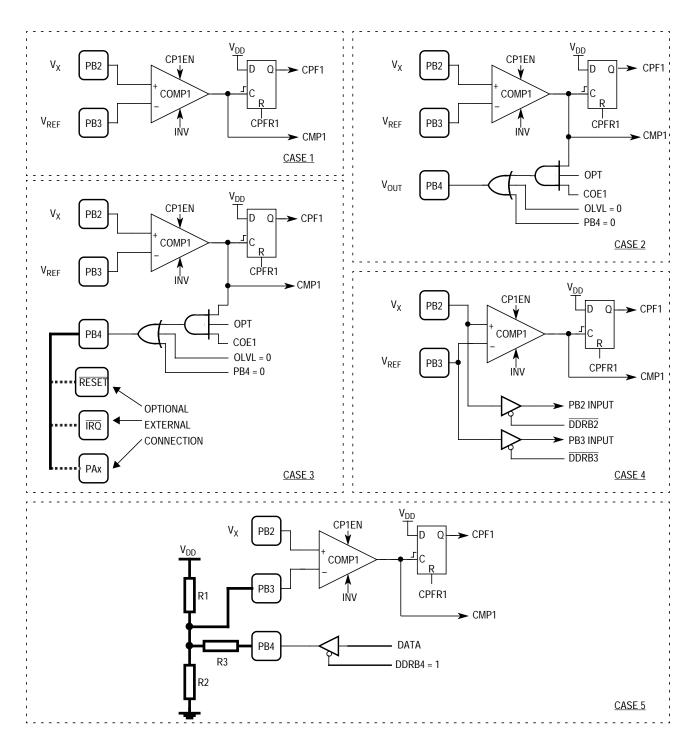

The connections to PB2, PB3, and PB4 mean that the user must decide the dominant use of these pins. While the inputs to comparator 1 will not affect the levels applied to PB2 and PB3 (even if above the commonmode range of comparator 2), the output of comparator 1 can be OR'ed with any internal source driving PB4. Comparator 1 can be used in a variety of configurations which are described in the following paragraphs and shown in **Figure 3**.

**Case 1** uses comparator 1 as a simple function to detect when the voltage on PB2 rises above PB3. In this case, port B would be configured with PB2 and PB3 as inputs. Normally, the user would deactivate the input pulldowns on PB2 or PB3, but there is no internal reason that they could not remain active if the external voltage sources can supply up to 300  $\mu$ A. A software subroutine can then be initiated by polling the state of the CMP1 output bit or the CPF1 flag bit or by an analog interrupt caused by CPF1 being set.

**Case 2** uses comparator 1 solely for an outside function. In this case, the user should configure the PB2 and PB3 pins to be inputs with their pulldowns deactivated and the PB4 pin as an output. The COE1 bit should be set with both the OLVL and PB4 data bit cleared.

**Case 3** uses comparator 1 as an additional detection means for another MCU pin. As in case 2, the PB2 and PB3 pins should be configured as inputs with their pulldowns deactivated and the PB4 pin as an output. The COE1 bit should be set with both the OLVL and PB4 data bit cleared. The comparator's output can then be wrapped around from the PB4 pin to the RESET, IRQ, or a port A pin which has IRQ capability (PA0:PA3). This essentially creates an adjustable threshold for resetting the MCU or causing an IRQ interrupt. Possible uses would be low battery detection, level alarms, and low-voltage reset. If the comparator 1 output drives the IRQ function, the additional IRQ source can be made

a lower priority than other IRQ sources by polling the CMP1 or CPF1 bits in the IRQ subroutine. If CPF1 is set, the IRQ subroutine could branch within the IRQ subroutine or cause the IRQ subroutine to be exited and, therefore, allow an analog interrupt to occur. In either case, the subroutine called should clear the CPF1 bit so that future detection is possible.

**Case 4** uses comparator 1 as a monitor, but also uses the digital inputs on PB2 and PB3 as a crude threshold detector. In this case, the software can determine whether the comparator is checking voltages above or below the digital threshold of port B. The digital threshold is typically 40% to 60% of the V<sub>DD</sub> supply voltage. In this case, it is important that the PB2 and PB3 pins are configured as inputs with their pulldowns disabled.

**Case 5** uses comparator 1 as a monitor, but it also uses the digital output on PB4 to alter the trip point for the comparator. As shown in **Figure 3**, the PB4 output buffer could shunt the external reference divider causing the comparator to set when the parallel combination of R1 and R3 is connected to  $V_{DD}$  and then reset when the parallel combination of R2 and R3 is connected to  $V_{SS}$ . Careful review of the port B description also will show that the shunting of the external reference divider can be done by the OR combination of the PB4, TCMP, or CMP1 functions so that the control can be based on software control, timer control, or direct feedback from comparator 1. In this case, it is important that the PB2 and PB3 pins are configured as inputs with their pulldowns disabled.

Figure 3. Comparator 1 Configurations

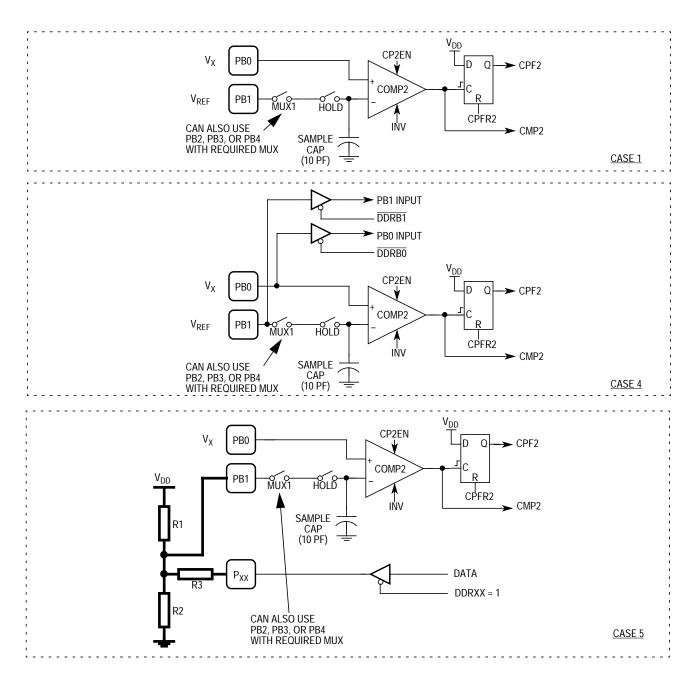

Comparator 2 Comparator 2 is a basic voltage comparator with its positive input tied permanently to the PB0 pin and its negative input being tied to a number of internal or external functions. The negative input of comparator 2 can be switched to various sources, but in all cases the internal sample capacitor of approximately 10 pF will remain connected from the negative input to  $V_{SS}$ . Its output can be monitored by the dynamic output and static flag bits in the ASR located at address \$001E. The dynamic output bit, CMP2, follows the output of the comparator regardless of its prior conditions and becomes a logical 1 whenever the comparator's positive input is above its negative input. The static flag bit, CPF2, becomes set whenever there is a rising output from the comparator and remains set until cleared by writing a logical 1 to the reset bit, CPFR2. Therefore, the CPF2 bit can be used to capture events where the comparator's positive input rose above its negative input.

Not only does comparator 2 allow software subroutines polling the CMP2 or CPF2 bits or an analog interrupt caused by CPF2 being set, the CPF2 flag bit also can trip the input capture function of the 16-bit timer if the ICEN bit is set in the ACR at location \$001D.

Comparator 2 has limited connection capabilities versus comparator 1. The primary purpose of comparator 2 is to construct a multiple channel integrating A/D convertor using the internal channel MUX, internal references, input divider, and sample and hold. Comparator 2 can be used as a simple comparator as shown in **Figure 4**. These uses are similar to cases 1, 4, and 5 for comparator 1 shown in **Figure 3**. However, due to the internal resources, comparator 2 has several unique cases of its own. These additional cases are shown in **Figure 5** and are described in the following paragraphs.

**Case 6** uses comparator 2 to monitor an outside function on PB0 with respect to the divided input on PB1, PB2, PB3, or PB4. In this case, the user should configure the PB1:PB4 input selected to be an input with its pulldown deactivated. The divider nominally divides the input by 2 which allows the selected PB1:PB4 pin to be tied to a voltage level up to  $V_{DD}$ . To activate the divider, the DHOLD MUX must be enabled.

Figure 4. Comparator 2 Configurations

Figure 5. Additional Comparator 2 Configurations

**Case 7** uses comparator 2 as a simple function to detect when the voltage on PB0 rises above the internal temperature sensing diode. In this case, port B would be configured with PB0 as an input. Normally, the user would deactivate the input pulldown on PB0, but there is no internal reason that it could not remain active if the external voltage source to PB0 can supply up to 300  $\mu$ A of current to the pulldown.

**Case 8** shows how both comparators can be tied to a common signal by using the internal channel MUX and leaving the HOLD MUX enabled. Notice that the negative input of comparator 2 can be tied to either the positive or negative input of comparator 1 by MUX2 or MUX3. If the positive input of comparator 2 needs to be tied to either input of comparator 1, then an external connection can be used.

#### Comparator Common Mode Range

The comparators can determine only which input is higher as long as at least one input stays within the common mode range from  $V_{SS}$  to  $V_{DD} - 1.5$  volts. If both inputs should fall outside this range, then the comparator's output will be undefined. It is important to constrain at least one input into the common mode range for reliable operation. Taking the input above  $V_{DD} - 1.5$  volts is only recommended when using the divided input to comparator 2.

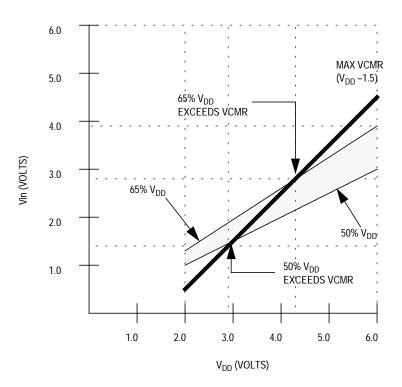

Care must be taken when using sources ratiometric to V<sub>DD</sub> to ensure that the common mode limits are not exceeded as the V<sub>DD</sub> level changes. When the supply voltage decreases, the common mode range decreases at a more rapid rate than the percentage drop in V<sub>DD</sub>. For example, consider an input source that only varies between 50% and 65% of V<sub>DD</sub>. As shown in **Figure 6**, when the V<sub>DD</sub> level is at 5.0 volts, the input will stay between 2.50 to 3.25 volts which are both within the common mode limits. However, the common mode range is defined by a fixed voltage drop below V<sub>DD</sub>. As V<sub>DD</sub> falls to 4.29 volts, the upper range of the ratiometric input is now at 2.79 volts, which is right at the limit of the common mode range. As V<sub>DD</sub> falls farther, the input can become greater than V<sub>DD</sub> – 1.5 volts. As V<sub>DD</sub> approaches the minimum operating limit of 2.7 volts, the input source range is completely above the common mode range.

**NOTE:** Be sure to calculate the common mode range over the range of voltage levels expected for  $V_{DD}$  and always keep one input to the voltage comparators within the common mode range.

In practice, the common mode range can extend below V<sub>SS</sub> until the internal input protection diode starts to conduct at about –0.3 volts (at 125 °C). If the input is taken further negative, the diode conduction can become excessive which can seriously affect analog functions. In a like manner, the inputs can be taken up to 0.3 volts above V<sub>DD</sub> before the upper input protection diode starts to conduct.

Figure 6. Ratiometric Sources vs. Common Mode Range

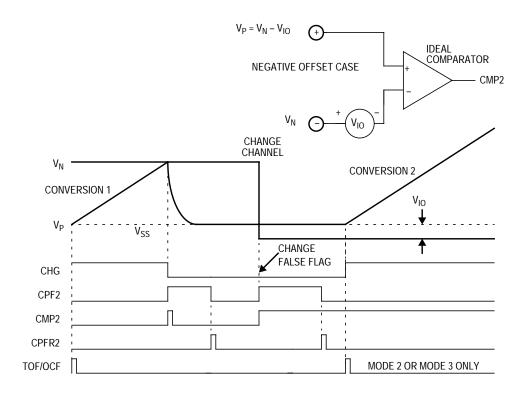

Comparator Input<br/>Offset VoltageThe voltage comparator design used in the MC68HC05JJ/JP series of<br/>MCUs was selected for its simplicity and small silicon area on the device.<br/>Basic comparators like this can have input voltage offsets of up to 15<br/>millivolts. This amount of offset can be significant, especially when<br/>monitoring signals near  $V_{SS}$ . If one of the comparator inputs must go<br/>below  $V_{SS}$  to overcome the  $V_{IO}$ , then the comparator's output will not<br/>change state and the comparator will look "stuck" even though both

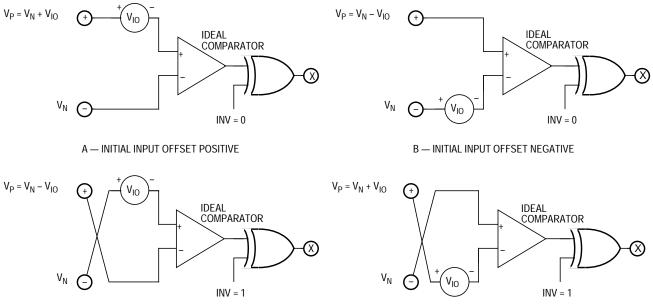

inputs may be within the common mode range above  $V_{SS}$ . The input offset voltage of a comparator can be modeled as a small internal voltage source in series with either input of a voltage comparator as shown in Figure 7.

In case A, the small  $V_{IO}$  source is in series with the positive input of the comparator. If both inputs to the comparator are to be equal, then the applied positive input must rise an additional amount equal to  $V_{IO}$ . Thus, the comparator trip condition occurs when:

$$V_P = V_N + V_{IO}$$

In case B, the small  $V_{IO}$  source is in series with the negative input of the comparator. If both inputs to the comparator are to be equal, then the applied positive input must fall an additional amount equal to  $V_{IO}$ . Thus, the comparator trip condition occurs when:

$$V_{p} = V_{N} + V_{I0} + V_{$$

$V_P = V_N - V_{IO}$

IN BOTH CASES, THE OUTPUT (X) RISES WHEN THE (+) INPUT RISES ABOVE THE (-) INPUT.

#### Figure 7. Comparator Input Offset Model

ComparatorIf the input offset can be moved between the inputs, then the sign of its<br/>contribution to VP can effectively change. Since the input offset is<br/>actually the result of silicon device sizes and their matching, it cannot<br/>actually "move" between inputs. But the sense of the inputs can be<br/>redefined by interchanging what the inputs to the comparator are called<br/>while also inverting the comparator's output sense as shown in Figure<br/>8. In these cases, the actual offset stays with the same internal

comparator input, but results in the addition or subtraction from the same external input to the comparator. This inversion action is performed by the INV bit in the AMUX register.

The INV bit, therefore, can be used to check for an input condition where the difference between the inputs is less than the offset voltage or for the case where one input is within the offset voltage of  $V_{SS}$ . For example, in case B in Figure 8 where  $V_N$  is 5 mV above  $V_{SS}$  and  $V_{IO}$  is 10 mV with respect to the internal negative input of the comparator, then:

$$V_{P} = V_{N} - V_{IO} = 5 \text{ mV} - 10 \text{ mV} = -5 \text{ mV}$$

Therefore, the comparator output will not change states, since the  $V_P$  must be at least 5 mV below  $V_{SS}$ .

IN ALL CASES, THE OUTPUT (X) RISES WHEN THE (+) INPUT RISES ABOVE THE (-) INPUT.

#### Figure 8. Inverted Comparator Offset Model

However, if we invert, the sense of the comparator is inverted using the INV bit, then  $V_N$  will still be at 5 mV, but it is now connected to the internal positive input of the comparator. The 10-mV input offset is still with respect to the internal negative input, but now is "moved" to the external  $V_P$  so that:

$$V_{P} = V_{N} + V_{IO} = 5 \text{ mV} + 10 \text{ mV} = +15 \text{ mV}$$

Therefore, the comparator will now change states if the voltage on  $V_P$  is near 15 mV.

In this discussion, the offset voltage has been described with respect to the negative input of the comparator, but in practice this offset may be with respect to either input of the comparator. Therefore, the resulting output states for each state of the INV bit gives the user an indication of the relative voltages on  $V_P$  and  $V_N$  as given in **Table 2**.

The two conditions where the comparator outputs change states based on the state of the INV bit can be further analyzed to show that each of these conditions is unique to a given polarity of the input offset voltage.

| Output state o | of comparators | Polarity of input offset               |  |  |

|----------------|----------------|----------------------------------------|--|--|

| INV = 0        | INV = 1        | (see Figure 7)                         |  |  |

| 0              | 1              | Case A, positive, $V_P = V_N + V_{IO}$ |  |  |

| 1              | 0              | Case B, negative, $V_P = V_N - V_{IO}$ |  |  |

Table 2. Results Using INV Bit on Comparators

The user, therefore, can determine the polarity of the input offset voltage for any particular comparator by simply connecting both of its inputs to the same voltage and then checking the comparator output state for each state of the INV bit versus **Table 2**. The inputs can both be tied to  $V_{SS}$  by using the associated port B pins as outputs, if the inputs are connected to a source impedance greater than 2 k $\Omega$ . In this case, the user should first clear the associated port B data bit and then set the associated data direction bit. Another approach to tie together the inputs of comparator 1 is to set the MUX2 and MUX3 bits and clear the HOLD, DHOLD, MUX1, MUX4, and VREF bits in the AMUX register. This will connect the PB2 and PB3 pins by connecting them both to the channel multiplexer, which also has been isolated from other sources.

**NOTE:** When operating with one comparator input near  $V_{SS}$ , it is recommended that the input always be tested with the INV bit both set and clear. If the results are different, then the inputs are both within  $V_{IO}$  of  $V_{SS}$ .

It is impossible to control the outputs of the comparators when changing the state of the INV bit since it interchanges the inputs and inverts the output of both comparators at the same time. Therefore, the comparator flags, CPF1 and CPF2 in the ASR, may get set during any change in the INV bit.

The user should use caution also when changing the state of the INV bit if either flag bit is enabled to trigger a timer input capture or analog interrupt. Any change to the INV bit should be done with these interrupts disabled or during a time when an interrupt is not expected before the flag bits can be cleared.

- **NOTE:** Changes to the INV, CP1EN, CP2EN, and ICEN bits can cause the comparator static flags to get set. Always clear the CPF1 and CPF2 static flag bits after changing any configuration of the comparators by writing a logical 1 to both the CPFR1 and CPFR2 bits in the ASR.

- Comparator InputThe comparators themselves have a very high input impedance, butImpedanceseveral other circuits connected to their inputs will lower this idealimpedance.These currents or equivalent impedances are:

- 1. Input protection diodes for ESD which may have leakage currents up to  $\pm 2 \,\mu$ A (equivalent of 2.5 M $\Omega$  at 5 volts)

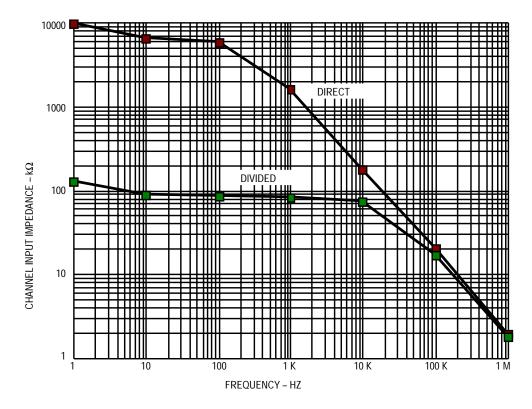

- 2. Parasitic capacitances in the input and multiplexer circuitry will cause the input impedance to decrease with frequency as shown in Figure 9.

- 3. The input divider of 2:1 has an impedance of 120 k $\Omega$  at DC, but decreases at high frequencies due to the sample capacitor as shown in **Figure 9**.

- 4. Software-controlled input pulldown devices which can sink up to 280  $\mu$ A (equivalent of 18 k $\Omega$  at 5 volts)

- 5. More than one input multiplexer being on at the same time and connecting the comparator input to other low impedances

- 6. Output devices on port B pins being active

The ESD protection (1) and the parasitic capacitances (2) are always present and will be the limiting factor on high input impedance. The divider (3) only affects the negative input of comparator 2 and can be removed from the input by not using the DHOLD bit in the AMUX register. The last three sources (4, 5, 6) all can be controlled by the

user's software code, but they can be a problem if they are overlooked in the application.

Figure 9. Typical Channel AC Input Impedance

**NOTE:** The most common cause of unwanted input current or low input impedance is a failure to turn off the input pulldown devices on port B. This is accomplished by writing logical 1s to the desired PDIB bits in the PDRB at location \$0011.

| Comparator<br>Speed                | The comparators have good speed and can power up or respond to their inputs changing within 2 microseconds. However, powering up a comparator when neither comparator nor the current source was previously active can result in a longer delay in stabilization for both the analog bias source and the comparator. It is, therefore, recommended that at least 10 microseconds of delay be provided by the software to allow the comparator to stabilize following a power up before trying to read or reset its output flag bits. The simplest way to add a time delay would be a series of NOP instructions (at $f_{OSC}$ of 4.2 MHz, each NOP takes 1 microsecond) or to insert other code which does not rely on the state of the comparator output flags.                                                                                                 |

|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Comparator<br>Power<br>Consumption | Each comparator typically draws 100 $\mu$ A of I <sub>DD</sub> current when it is<br>powered up by its appropriate CP1EN or CP2EN bit in the ACR. In<br>addition, when either or both comparators are powered up, an analog<br>bias source is also powered up which draws typically 65 $\mu$ A. This means<br>that a single comparator will draw about 165 $\mu$ A and both comparators<br>will draw about 265 $\mu$ A.                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Comparator<br>Output Sampling      | <ul> <li>There are two means to determine if a comparator has changed states:</li> <li>The static flags, CPF1 and CPF2</li> <li>The dynamic outputs, CMP1 and CMP2</li> </ul> The static flags are set whenever there is a rising edge on the output of the respective comparator, and they remain latched until cleared by writing a logical 1 to the respective CPFR1 and CPFR2 bits or by a reset of the device. These flags are useful for capturing events while the CPU is doing some other task. These flags also can generate an interrupt using the analog interrupt. In the case of comparator 2, a timer input capture interrupt also can be generated. As mentioned above, the state of the CPF1 and CPF2 flag bits should be ignored after changing the state of the INV bit until both flags have been reset using the CPFR1 and CPFR2 reset bits. |

|                                    | The dynamic output bits merely follow the state of the output of each comparator. There is no timing synchronization in passing the state of the CMP1 and CMP2 bits to the ASR. The dynamic output bits are useful                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

in testing the state of the comparator following the initiation of a static flag or simply to check that the comparator state is steady. Since there is no latching of the outputs, the user should be cautious about using the CMP1 or CMP2 bits when inputs to the comparator are changing at frequencies greater than the rate at which the software is sampling the ASR.

Shared FunctionsOne pin of port B, PB4, can be shared with the output of comparator 1,<br/>the output compare of the 16-bit timer, and the PB4 port I/O buffer itself.<br/>All of these functions are OR'ed together to drive the pin when it is<br/>configured as an output by setting the DDRB4 bit in the port B data<br/>direction register at location \$0005.

When the PB4 pin is configured as an output, the pulldown device is automatically disabled and the output compare and port B data register are OR'ed together. The output of comparator 1 can be added to the OR function if the COE1 bit is set and the additional analog options are selected by the OPT mask option.

Once the OR function is active, the user must disable the functions that are not wanted by clearing the correct bits as given in **Table 3**.

|                                              | Register bit requirements                                                      |                     |                                   |                                        |                              |  |  |

|----------------------------------------------|--------------------------------------------------------------------------------|---------------------|-----------------------------------|----------------------------------------|------------------------------|--|--|

| Desired output<br>driving function<br>on PB4 | Port B<br>data bit,<br>PB4<br>16-bit timer<br>output<br>compare<br>level, OLVL |                     | OPT mask<br>option,<br>MOR or ROM | Comparator 1<br>output<br>enable, COE1 | Comparator 1<br>output, CMP1 |  |  |

| Port B data register                         | PB4<br>data bit state                                                          | 0                   | 0                                 | Х                                      | Х                            |  |  |

|                                              |                                                                                |                     | 1                                 | 0                                      | Х                            |  |  |

|                                              |                                                                                |                     |                                   | 1                                      | 0                            |  |  |

|                                              |                                                                                |                     | 0                                 | Х                                      | Х                            |  |  |

| 16-bit timer<br>output compare               | 0                                                                              | Timer OLVL<br>state | 1                                 | 0                                      | Х                            |  |  |

|                                              |                                                                                |                     | I                                 | 1                                      | 0                            |  |  |

| Comparator 1 output                          | 0                                                                              | 0                   | 1                                 | 1                                      | CMP state                    |  |  |

Table 3. Logical OR Function on PB4

#### Comparator Output Analog Interrupt

The outputs of the comparators can be monitored also by using the analog interrupt. When using interrupt-driven detection of the transitions, the main consideration is the latency of entering the interrupt service routine and its later return to the background software. The CPU will always complete the instruction currently in process before beginning an interrupt service routine. The range of instruction times varies from two to 11 CPU bus cycles.

The three longest instructions are the MUL (11 cycles), the SWI (10 cycles), and the RTI (nine cycles). While the user can avoid using either the MUL or SWI instruction, the RTI is a necessary instruction if interrupts are being considered.

Once the interrupt is acknowledged, there is a delay of 10 cycles to stack the CPU state before executing the first instruction in the interrupt service routine. This means it takes from 12 to 21 cycles to acknowledge the interrupt and access its service routine. Once the service routine is completed, there will be nine cycles to execute its final RTI instruction and 10 more cycles to unstack the CPU state before the interrupt is complete and the CPU is ready to begin processing another one.

From this discussion, at least 46 CPU bus cycles are required to simply acknowledge and clear the CPF1 or CPF2 static flags as follows:

- 21 cycles to acknowledge; max instruction plus stacking

- Six cycles to clear the static flag (BSET)

- 19 cycles to return; RTI plus unstacking

This does include any software time to actually perform a task. Therefore, analog interrupts should not be used to detect pulses separated by less than about 60 CPU bus cycles. On the other hand, software polling can test and clear the CPF1 or CPF2 static flags within 11 CPU bus cycles as follows:

- Five cycles to test for the static flag being set (BRSET)

- Six cycles to clear the static flag (BSET)

Software polling should not be used for pulses separated by less than 30 CPU bus cycles.

**NOTE:** Avoid using both the input capture and the analog interrupt at the same time for the comparator trip detection. In this case, the ICF always wins priority and the analog interrupt essentially will be ignored.

#### **Current Source/Discharge**

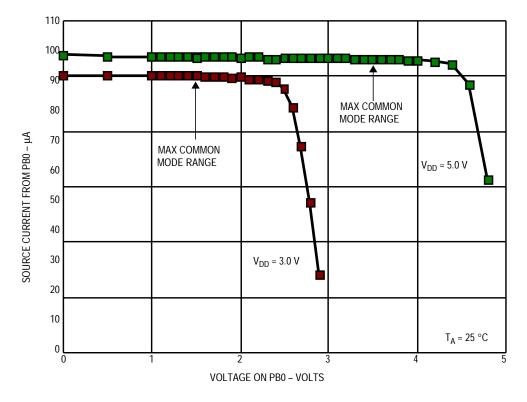

The analog system's other significant feature is the constant current source with discharge device that is connected directly to the PB0 pin. As given in **Table 4**, the current source and the discharge device can be operated in three modes which are dependent on the states of the ISEN and CHG bits in the ACR located at \$001E. ISEN controls whether the function is active and the CHG bit controls whether the PB0 pin sources 100  $\mu$ A or sinks at least 1 mA. When the ISEN bit is clear, the PB0 pin behaves the same as a standard I/O port pin.

| ACR cor | ntrol bits | Current | Discharge | Action                                            |  |  |

|---------|------------|---------|-----------|---------------------------------------------------|--|--|

| ISEN    | CHG        | source  | device    |                                                   |  |  |

| 0       | x          | OFF     | OFF       | Current source and discharge device both disabled |  |  |

| 1       | 0          | OFF     | ON        | Discharge current into PB0                        |  |  |

| 1       | 1          | ON      | OFF       | Source current from PB0                           |  |  |

Table 4. Current Source/Discharge Control

As shown in the block diagram in **Figure 1**, the current source, discharge device, and the positive input of comparator 2 all share PB0. Therefore, this current source can be used to supply current to external devices which the comparator can then test against some other voltage connected to its negative input through the channel select bus.

If PB0 is left unconnected, it appears like a 20-pF capacitor which requires about 800 nanoseconds to charge from  $V_{SS}$  to 4 volts.

Current SourceThe source current can vary as much as 10% due to the combination of<br/>temperature ranging from -40 °C to +85 °C, supply voltages within<br/> $\pm 15\%$ , and between different units. If the user wants a closer tolerance<br/>in the source current, then one or more of the various effects needs to<br/>be constrained to a tighter range.

The typical effects are:

- 1. A 10% change in the supply voltage typically creates about a 1.5% change in the source current.

- A temperature drop from 25 °C to -40 °C typically creates about a 1% change for each 10 °C change in temperature.

- 3. A temperature increase from 25 °C to 85 °C typically creates about a 0.01% change for each 10 °C change in temperature.

- As the voltage on PB0 changes, non-linearity creates up to about 1% variation in the nominal 100 μA source current.

- 5. Variations between different devices can typically have about 1% variation in the source current.

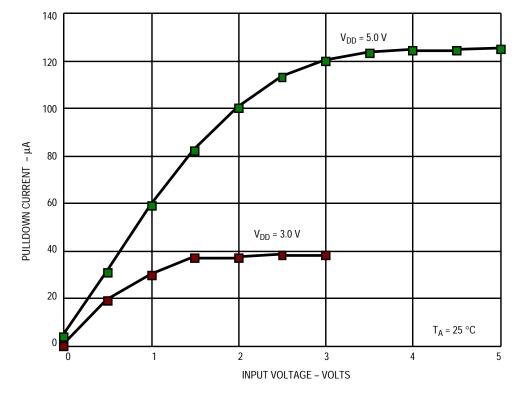

This source supplies a constant current out of PB0 at voltages from  $V_{SS}$  to within 0.5 volt of  $V_{DD}$ . Over the common mode range of  $V_{SS}$  to  $V_{DD} - 1.5$  volts, this current is constant within 1% of the nominal 100- $\mu$ A value. The current source continues to work above the common mode range, but starts to degrade below its nominal value as shown in **Figure 10**.

The internal current source circuitry contains a similar current mirror with bias currents totaling about 120  $\mu$ A. To prevent the current source from lagging when the PB0 pin is being switched between sourcing or discharging current, it is either directed out of the PB0 pin or redirected to V<sub>SS</sub>. Otherwise, the lag in the current source would affect the timing of single slope A/D conversions. Therefore, the current source draws about 220  $\mu$ A whenever the ISEN bit is set, even if the PB0 pin is not sourcing current and the discharge device is active. As the voltage on PB0 changes, non-linearity creates up to about 1% variation in the nominal 100- $\mu$ A source current.

Figure 10. Typical Current Source Behavior (PB0)

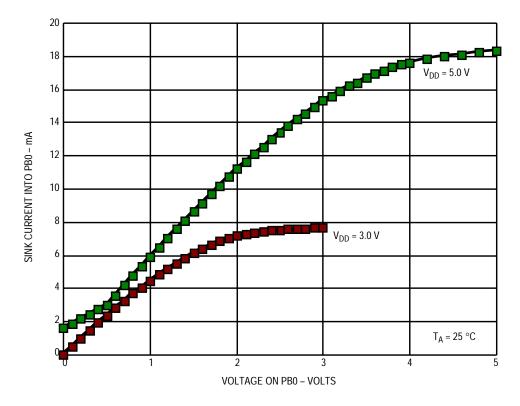

Discharge Device Also attached to PB0 is a MOS transistor designed to sink at least 1 mA of current from a source of 0.4 volts into V<sub>SS</sub>. The design goal was to provide a discharge current at least 10 times the source current. However, this device does not behave like a pure resistor as its current sinking capability varies with both the supply voltage and the voltage present on the PB0 pin.

The typical discharge current versus PB0 voltage and supply voltage is shown in **Figure 11**. For V<sub>DD</sub> of 3 volts, the equivalent discharge resistance is about 250  $\Omega$ , and for V<sub>DD</sub> of 5 volts, the equivalent discharge resistance is about 190  $\Omega$ .

Figure 11. Typical Discharge Current Behavior (PB0)

Current spikes can occur when discharging an external capacitor through PB0, which can be disruptive to the internal analog  $V_{SS}$  with respect to the external  $V_{SS}$  pin.

**NOTE:** Discharging large capacitors or low impedance loads into the PB0 pin can cause high current spikes which may disrupt the internal analog  $V_{SS}$  with respect to the  $V_{SS}$  pin and cause unwanted analog noise. Repeated high currents can also damage the discharge device and/or the device's interconnect metal. Using capacitors that are less than  $2\mu F$  and discharge current peaks that are less than 25 mA is recommended.

> The current source and discharge device is an important part of building a single slope A/D convertor. In conjunction with A/D conversions, the ATD1 and ATD2 mode bits in the ACR can provide some automatic switching between the current source and sink modes of operation.

#### **Analog Signal Multiplexers**

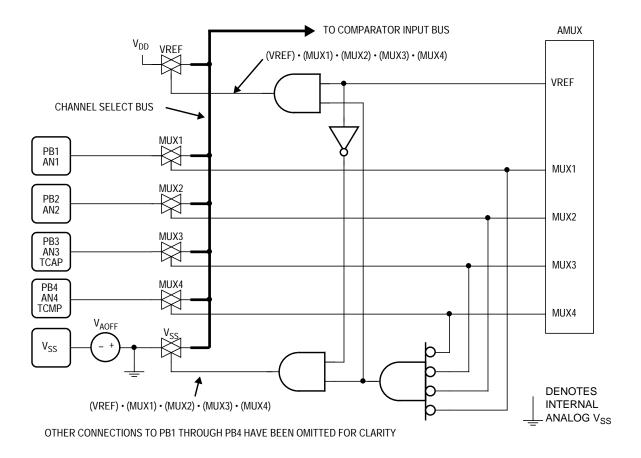

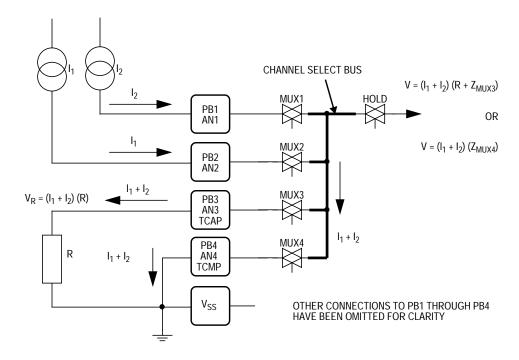

The analog signal multiplexer is shown in **Figure 12**. It is controlled by the bits in the AMUX register at location \$0003. By design, this register has minimal interlocking between some of these control bits. The reason for this is to allow combinations of channels to perform such tasks as current summing and load switching.

The analog signal multiplexer is divided into two sections:

- The channel select bus

- The comparator input bus

Figure 12. Analog Channel Bus

Channel SelectThe VREF, MUX1, MUX2, MUX3, and MUX4 bits in the AMUX registerBuscontrol which signals or pins are connected to the channel select bus.<br/>The MUX1:MUX4 bits can select any or all PB1:PB4 pins with no<br/>interlocks and connect them to the channel select bus. When none of the<br/>MUX1:MUX4 bits are set, the channel select bus is connected to either<br/>the internal V<sub>DD</sub> or V<sub>SS</sub> depending on the state of the VREF bit. If any<br/>MUX1:MUX4 bit is set again, then it opens the V<sub>DD</sub> or V<sub>SS</sub> connection<br/>regardless of the state of the VREF bit.

**NOTE:** The simple channel multiplexers do not include any automatic breakbefore-make or make-before-break control of multiple simultaneous changes. Therefore, the user must control the multiplexers in the proper sequence to avoid shorting two channels together during the transition. Unless the user has determined that switching transients are not a problem, it is recommended to avoid changing more than one MUX bit on a given write cycle to the AMUX register.

The channel multiplexers are always tied to the port pins regardless of the programming of pin pulldowns or the digital interface. Therefore, the channel multiplexers can monitor inputs to the digital interface. Similarly, the digital interface can feed outputs to the channel multiplexers, if desired.

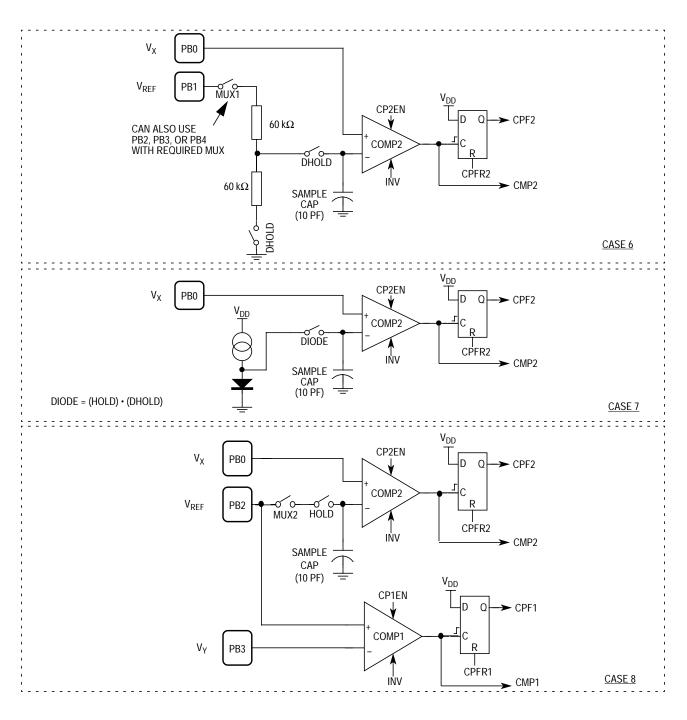

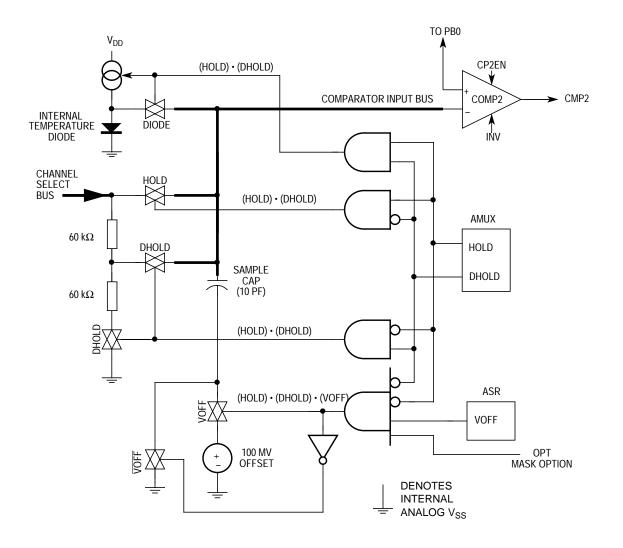

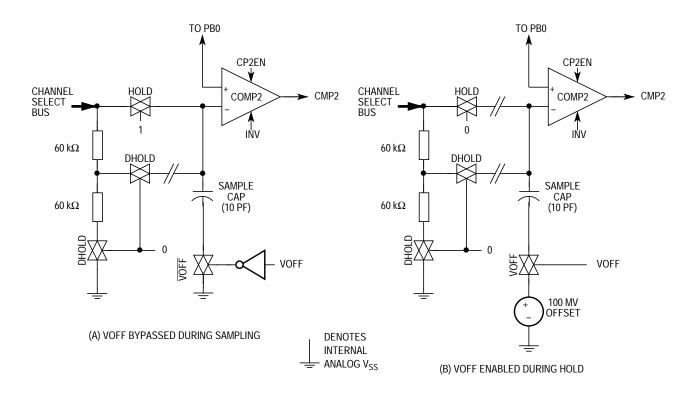

ComparatorOne end of the comparator input bus connects to the negative input of<br/>comparator 2. The other end of the comparator input bus can connect<br/>directly to the channel select bus, through a divider to the channel select<br/>bus or to the internal temperature sensing diode. A sample capacitor of<br/>approximately 10 pF is always connected to the negative input of<br/>comparator 2 regardless of what source is selected. The reference end<br/>of this sample capacitor is connected either to V<sub>SS</sub> or to an offset voltage<br/>depending on the state of the VOFF bit in the ASR. A block diagram of<br/>the comparator input bus is shown in Figure 13.

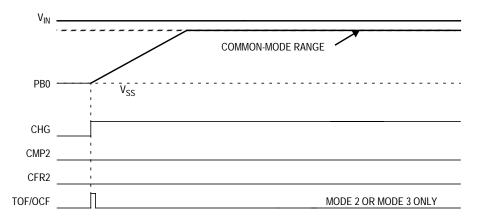

The HOLD and DHOLD bits in the AMUX register control the comparator input bus as given in **Table 5**. The normal mode is to have the HOLD bit set and the comparator input bus connected directly to the channel select bus. However, this limits input sources to the common mode range. When performing A/D conversions, the channel select bus needs to be tied to a reference voltage such as  $V_{DD}$  to make a  $V_{REF}$  conversion. To select  $V_{DD}$ , the divided input is needed by selecting the DHOLD bit instead of HOLD bit. When the divided input is used, the source could be as high as  $2 \times V_{DD} - 3$  volts and still not exceed the common mode range of the comparator. However, the input protection diode on the port B inputs will try to limit the voltage on the pins to  $V_{DD}$  + 0.3 volts. Supplying a higher voltage than  $V_{DD}$  + 0.3 volts could damage this diode and the device. The illogical case of setting both the HOLD and DHOLD bits does not actually short out the divider, but selects the temperature diode instead.

Figure 13. Comparator Input Bus

| AMUX register |       | Input source                                   |

|---------------|-------|------------------------------------------------|

| HOLD          | DHOLD |                                                |

| 0             | 0     | Open circuit; hold voltage on sample capacitor |

| 0             | 1     | Divided input from channel select bus          |

| 1             | 0     | Direct input from channel select bus           |

| 1             | 1     | Connected to internal temperature diode        |

AN1740

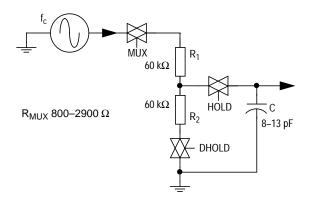

#### Multiplexer Impedance

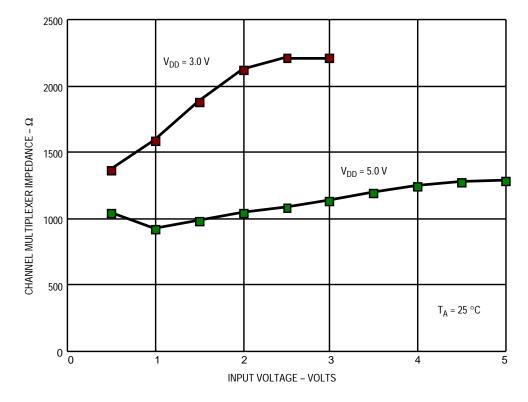

All the internal multiplexers are made identical for reasons of balancing the impedances seen by the input divider. The impedance of the multiplexers is not a simple resistive switch, but a complex transfer characteristic from the MOS transistors used in the multiplexer. Therefore, this impedance increases as the supply voltage decreases, the voltage across the multiplexer increases, or the device temperature increases. The actual impedance of each multiplexer is difficult to precisely determine, but the typical impedance behavior of a pair of multiplexers in series is shown in **Figure 14**. This impedance can be modeled as a resistor of 800–1500  $\Omega$  at a V<sub>DD</sub> of 5 volts and 1200–2900  $\Omega$  at a V<sub>DD</sub> of 3 volts.

When the channel select bus is connected directly to the input of comparator 2, the multiplexer impedance is not an issue since the comparator's input impedance is several orders of magnitude greater. The only effect would be a minor increase in the charge time of the sample capacitor. When the divided input is used, a compensation multiplexer is added to the bottom of the divider to track the impedance of the channel input multiplexer and keep the overall divider ratio at 0.5. However, this dummy multiplexer at the bottom of the divider cannot compensate for multiple input channels being on in parallel.

**NOTE:** The divided input is only compensated for one channel multiplexer at a time. If multiple channel multiplexers are on simultaneously, then the divider ratio will increase slightly.

Therefore, the exact impedance of the multiplexers is only a consideration when the user is operating with more than one multiplexer on at a time or is passing current into one channel multiplexer and out of another. A first order estimate can be made by taking the data given in **Figure 14** and dividing by two for two channels in parallel, dividing by three for three channels in parallel, and so on.

Parallel ChannelsThe ability to parallel input channels can be used to sum currents as<br/>shown in Figure 15. In this example, two current sources, I1 and I2, are<br/>fed into the channel select bus by PB1 and PB2. Their summed current<br/>then flows out of PB3 to a voltage conversion resistor, R.

Figure 14. Typical Channel Multiplexer Impedance

If PB1 and PB2 are being fed from current sources and sufficient voltage range is available, then the impedance of the MUX1 and MUX2 channel multiplexers does not create a voltage drop relative to the internal channel bus. The voltage on the internal channel bus with PB1, PB2, and PB3 all on will be:

$$V_{CHANNEL} = (I_1 + I_2) \times (R + Z_{MUX})$$

If the PB4 pin is connected to V<sub>SS</sub>, then MUX3 can be turned off and MUX4 turned on in its place. The voltage on the channel bus will now be:  $V_{CHANNEL} = (I_1 + I_2) \times (Z_{MUX4})$

Assuming that  $Z_{MUX3}$  is approximately equal to  $Z_{MUX4}$ , the difference between these two voltages, therefore, is the voltage on the external conversion resistor, and the effects of the channel multiplexer's impedances are cancelled. With this setup, the currents through port pins should be limited to less than 1 mA. For the widest operating range, the currents and conversion resistor should be selected such that the total voltage drop through two multiplexers and the conversion resistor is less than the common mode range for the comparators.

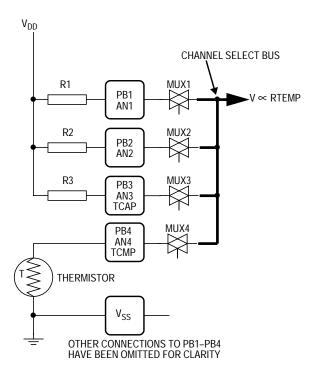

Figure 15. Current Summing Inputs

The multiplexer channels also can be connected to supply a source voltage to an external device as shown in **Figure 16**. As shown,  $V_{DD}$  can be applied through three different resistors to PB1, PB2, or PB3; through multiplexers MUX1, MUX2, and MUX3; and then out through MUX4 and PB4 to an external thermistor. Each resistor can be selected for a given temperature range of the thermistor. The resulting voltage can be measured on the channel bus. Even though there is a multiplexer on either side of the channel bus, there will be some effects from the temperature variation in the multiplexer impedances. This effect can be minimized at temperatures where the source resistor creates the same voltage drop across both the thermistor and the source resistor.

Input Limitations Avoid driving input pins below V<sub>SS</sub>, even if the channel multiplexers are OFF, as the input protection diodes will start turning on at about –0.3 volts and inject high currents through the V<sub>SS</sub> pin. Similarly, avoid driving the input pins more than 0.3 volts above the V<sub>DD</sub> supply level.

Figure 16. External Source Control

#### Support Circuitry

A number of specific support circuits provide additional capabilities or options as described in the next subsections.

**Input Divider** The primary purpose of the input divider is to extend the common mode range to allow measurement of pin voltages up to the V<sub>DD</sub> supply level. This divider can be switched in between the channel select bus and the comparator input bus by setting the DHOLD bit and clearing the HOLD bit in the AMUX register. The input divider can be used only on the channel select bus signals and cannot be used in conjunction with the temperature diode. The divider is created with two identical resistances, each of a nominal 60 k $\Omega$ . This provides a divider ratio of 0.5. The matching of these resistors is within ±1%, which results in the divider ratio varying from 0.49 to 0.51 between different devices.

The input impedance of the comparator is more than 1 M $\Omega$ , so the divider becomes a significant input impedance load when switched into the signal path. At DC, this input impedance looks like 120 k $\Omega$ , but at frequencies above 10 kHz the 10 pF sample capacitor starts to bypass the lower leg of the divider and both the input impedance degrades and the divider ratio starts to drop. Neglecting the parasitic capacitances in the multiplex circuitry, the input impedance can be roughly modeled as shown in Figure 17 with typical input impedance as shown previously in Figure 9.

Figure 17. Divider Equivalent Circuit

AN1740

To cancel the impedance of the channel multiplexers, an identical dummy multiplexer is switched in at the bottom whenever the DHOLD bit is set. If more than one channel multiplexer is turned on at the same time, there will be a shift in the divider ratio due to the parallel combination of the input multiplexers not being matched by the compensation multiplexer at the bottom of the divider. A second-order temperature-dependent term also will be present if the multiplexer impedance at the top is not equal to the dummy multiplexer at the bottom. Typical input impedance of both the direct and divided inputs is given previously in **Figure 9**.

- **NOTE:** The divided input is only compensated for one channel multiplexer at a time. If multiple channel multiplexers are on simultaneously, then the divider ratio will increase slightly.

- Sample and Hold The sample capacitor is always connected from the negative input of comparator 2 to V<sub>SS</sub>. It is typically 10 pF, but can vary from 8 to 13 pF between different devices. The capacitor can be charged within 99.9% of its final value within seven RC time constants.

When connected directly to the channel select bus, the worst case series impedance of the channel and the HOLD multiplexers is about 8 k $\Omega$  for an RC time of 104 nanoseconds. By comparison, it takes the software four CPU bus cycles to set and then turn off the HOLD bit. At the maximum oscillator frequency of 4.2 MHz, this is about a 2-microsecond delay or about 18 RC time constants. Therefore, if connected directly to the channel bus, there should always be sufficient time to charge the sample capacitor between any two instructions.

However, when connected through the divider to the channel bus, the series impedance of the channel and the DHOLD multiplexers is added to the 60-k $\Omega$  equivalent resistance of the divider. This increases the RC time constant to a worst case of 832 nanoseconds. With the same 2-microsecond software delay, this would give a little more than two RC time constants, which would allow only the sample capacitor to charge to about 85% of its final value. Therefore, if connected through the divider to the channel select bus, there should always be sufficient time to charge the sample capacitor (seven RC time constants or about six

microseconds). If four NOP instructions are inserted between the instructions that set and clear the DHOLD bit, then this will add an additional eight CPU cycles which, when combined with the original four CPU cycles, will give an equivalent delay of about six microseconds. If insufficient time is given to allow the sample capacitor to fully charge (or discharge) to a new voltage, then such measurements will be in error.

**NOTE:** It is important that the INV and VOFF bits are not changed during the time that a voltage is being held on the sample capacitor. The exchange of inputs and switching currents can easily corrupt, if not completely discharge, the sampled voltage.

The sample capacitor typically can hold its charge for several minutes at room temperature, but due to inherent leakage currents, this degrades quickly as the temperature is raised. Leakage currents in silicon double every 10 °C such that a minute decay time can degrade to less than a second at 85 °C. In practice, the decay rate of 0.2 V/second should be used for the overall temperature range of -40 °C to +85 °C.

**NOTE:** The window on erasable EPROM devices must be covered with an opaque material such as black electrical tape. Common white paper labels are not opaque enough to prevent light from affecting bias currents, trip points, and leakage in the analog subsystem.

One observed source of sample corruption comes from  $V_{SS}$  ground bounce noise, which tends to disturb the multiplexers attached to the sample capacitor. If they turn on, even for a few nanoseconds, the voltage to which they are connected, either higher or lower, will be connected to the sample capacitor and will alter its charged voltage. Input signals which remain connected to their source are not affected by these noise spikes signals due to their short durations. In many cases, the user is in control of the significant sources of ground bounce noise. These occur when the MCU's I/O pins suddenly turn on and sink high currents through the V<sub>SS</sub> pin. It is recommended that switching of any loads does not occur during the time the sample capacitor must hold its charge. Other sources can be poor layouts.

Another source of sample corruption comes from substrate current injection which can occur when the input protection diodes begin conduction in order to limit inputs which have gone above  $V_{DD}$  or below

$V_{SS}$ . The user also has some control over substrate current injection by limiting voltage and/or current excursions on the pins.

Refer to the application note *In-Circuit and Emulation Consideration for MC68HC05JJ/JP Series Microcontrollers*, Motorola document number AN1741/D, for more information on good PWB layout and limiting these noise source.

One particularly troublesome high current case occurs when using the discharge device on PB0 to discharge an external capacitor at the end of a single slope A/D conversion. While normally there is no need to make multiple A/D conversion measurements from the same sample, a diagnostic may try to do this to measure the leakage performance of the sample capacitor. In this case, the repeated measurements, with discharges into PB0 at the end of each one, will yield worse results than actually occur with a single A/D conversion.

- **NOTE:** Experience has shown that the least sensitivity to such noise sources is created when the channel select bus is connected to the internal  $V_{DD}$  after the HOLD or DHOLD multiplexer has been turned off. This also means that the input channel multiplexers are off. Leaving the channel bus connected to  $V_{SS}$  or a low voltage input creates the most sensitivity to  $V_{SS}$  ground bounce noise.

- **NOTE:** When trying to maintain the sample voltage, avoid discharging capacitors or other high current loads through the MCU's V<sub>SS</sub> pin or power supply return wiring.

- **NOTE:** In cases where severe system noise affects input signal measurements, it is recommended that the sample and hold method not be used. Instead, always leave the signal connected to the comparator through the HOLD or DHOLD and channel multiplexers.

Another source of sample errors can occur if the proper sequencing of the multiplexers is not followed. Since there is no automatic control of the multiplexers, the user should first turn off the HOLD or DHOLD multiplexer before changing any channel multiplexers. If all the multiplexers are changed on the same write cycle to the AMUX register, there can occur some charge redistribution due to the tiny variations in delays between all the multiplexers. The only exception to this is when switching to the temperature diode, where the HOLD and DHOLD must be changed at once and the sample and hold function is not available.

**NOTE:** When using the sample and hold capacitor, always turn off the HOLD and DHOLD bits on a separate write to the AMUX register before making any changes to the other channel multiplexers.

When comparator 2 is not being used to measure a voltage, it should have its sample capacitor and input tied through the HOLD multiplexer to the channel select bus which has been connected to  $V_{SS}$ . Otherwise, the input on comparator 2 may drift with stray leakage currents and cause unwanted output changes or flags.

Sample OffsetAs the input voltages get near the  $V_{SS}$  level, the magnitude and phaseVoltageof the comparator's own offset voltage can create a situation where an<br/>external pin must go below  $V_{SS}$  in order to flip the comparator output. To<br/>handle this case, the VOFF bit can add a small positive offset voltage<br/>(nominally 100 mV) to the voltage stored on the sample capacitor as<br/>shown in Figure 18.

During the sampling of the input pin, the lower end of the sampling capacitor is connected directly to the internal  $V_{SS}$  line. The sampling ends when both the HOLD and DHOLD bits are off. In this case, the sampling capacitor has the input voltage with respect to  $V_{SS}$ , and the lower end of the sampling capacitor is raised about 100 mV above  $V_{SS}$ . Now any input offset in the comparator will be added to or subtracted from the nominal 100 mV.

The VOFF bit is not active unless the OPT bit is selected as a mask option. About  $20 \,\mu\text{A}$  of I<sub>DD</sub> current is drawn when the VOFF bit is set, and the general analog bias source must be powered up. This can be done by setting either the ISEN, CP1E, or the CP2E bits in the ACR.

### Figure 18. Sample Voltage Offset Source

### Temperature Diode

If some measurement of temperature could be made, the MCU software could correct for some of its temperature effects on the current source, low-power oscillator, or MUX impedances. Such a temperature measuring device also could be used to monitor the device's temperature when one or more I/O pins is used to supply power to external loads.

A simple PN diode is provided for this purpose. It is connected to the internal  $V_{SS}$  and can be used to make such measurements of the temperature of the device. This diode is next to the current source which is located near the PB1 pin. The voltage on this diode is typically 0.7 volts. To create this voltage, about 20  $\mu$ A of current are supplied when both the HOLD and DHOLD bits are set. For this 20  $\mu$ A to be supplied, the general analog bias source must be powered up. This can be done by setting either the ISEN, CP1E, or CP2E bits in the ACR. Once powered, the diode's voltage will change approximately 2 mV/°C.

# **Application Note**

The diode voltage drop and change with temperature are not accurate enough to measure any closer than 10 °C, unless the device is calibrated with a table of values versus temperature that is stored in the personality EPROM or user EPROM found on the MC68HC705JJ7 or MC68HC705JP7.

Input Pulldowns External pulldown resistors are normally needed for inputs to switches or other high impedance sources. To reduce cost, it is advantageous to supply these pulldown currents internally in the MCU. The JJ/JP series has pulldowns, which can be controlled by software, on all pins on ports A, B, and C.

As the default condition following a reset or power-on condition, these pulldowns come up activated so that all I/O port inputs will be immediately defined. If the user does not want these pulldowns to be present during power on, they can be disabled by the SWPDI bit in the mask option register (MOR) or by a mask option on ROM-based devices. These pulldowns also can be individually disabled by software which writes to the PDRA and PDRB registers at \$0010 and \$0011, respectively.

These pulldowns are intended for digital functions to eliminate external resistors and are actually weak N-channel MOS devices connected to  $V_{SS}$ . Because they are MOS devices, they have non-linear pulldown behavior as shown in Figure 19.

**NOTE:** Be sure to turn off any pulldowns on the PB0:PB7 pins when these are used for analog signals. Leaving these pulldowns on, especially on PB0, can lead to unwanted analog parasitics and unexpected measurement results. When the pulldown for PB0 is on when charging an external capacitor, the ramp will look like an RC charge curve rather than a linear ramp.

Figure 19. Typical Input Pulldown Current

## 16-Bit Timer Input Capture

The 16-bit timer is the same one found on some other members of the MC68HC05 Family of MCUs. In the JJ/JP series, it has an additional purpose in providing the A/D timing in mode 2 or mode 3. It may be difficult to use the input capture and output compare timing functions for external events while still using them for the A/D conversions, but careful planning of the A/D sampling and conversion times will provide more capability for activities to be done in parallel.

When using the 16-bit timer for an A/D mode 2 or mode 3 conversions, the ICIE and IEDG bits in the TCR must be set in addition to the ICEN bit in the ACR. This is because the input capture function must be enabled and set up to trigger on the rising output of comparator 2. If one or more of these bits is left cleared, A/D conversions will not take place.

The ICF, OCF, and TOF timer flags interact to start and stop the current source driving PB0. Under this control, the ICF has priority over both the OCF and TOF. Further, the latched static flag, CPF2, of comparator 2 is

# **Application Note**

used to drive the input capture. Therefore, take care to follow these rules:

- Always clear the TOF and OCF before clearing the ICF. Otherwise, clearing the ICF immediately will enable any existing TOF or OCF to restart the charging cycle without regard for their proper timing points.

- 2. Avoid clearing the CPF2 comparator static flag too quickly after clearing the ICF as this enables the timer to capture a new time should the comparator output then rise again later.

- 3. Avoid changing the state of the INV bit after clearing the ICF as this will cause a switching pulse to set the CPF2 bit and trigger an unwanted ICF.

- 4. Changes to the ICEN, ICIE, or IEDG bits can cause the ICF flag bit to become set. Always clear the ICF flag following any change in the state of the ICEN, ICIE, and IEDG bits.

- 5. Account for the first TOF, OCF, and ICF flags which can get set without any enabling control. They can get set *before* the software is ready to use them.

The 16-bit timer continues to run while in wait mode, and this allows the mode 2 or mode 3 A/D conversions to take place during wait mode. When the conversion is complete, a timer interrupt will occur and the MCU will exit wait mode.

Analog Interrupt A separate analog interrupt is provided with a vector location at \$1FF2 and \$1FF3. This interrupt is triggered by either the CPF1 or CPF2 flags being set. These bits latch so that the triggering comparator can be determined by polling the CPF1 or CPF2 bits in the analog interrupt service routine. Since these latch bits are the triggering mechanism, they should both be cleared before exiting the analog interrupt service routine. All of the analog subsystem components can be powered down as an  $I_{DD}$  current saving technique. The controls for each comparator and the current source are contained in the ACR at location \$001D. Internally, there is an analog bias supply which provides bias currents for all of the analog features. When either comparator or the current source is powered up, the bias supply is turned on automatically.

The maximum time delay for an analog component to power up and stabilize is five microseconds. This delay is for individual components. If several of the analog components are all initially powered up on the first write cycle to the ACR, then the delay may be as long as 10 microseconds as both the bias supply and the comparators must come up together.

**NOTE:** Before sampling the comparator outputs or clearing the CPF1 or CPF2 flags, be sure to allow sufficient delay after the comparators are powered up. Otherwise, the outputs may be undefined or the flags may not be cleared.

# Analog-to-Digital Conversion

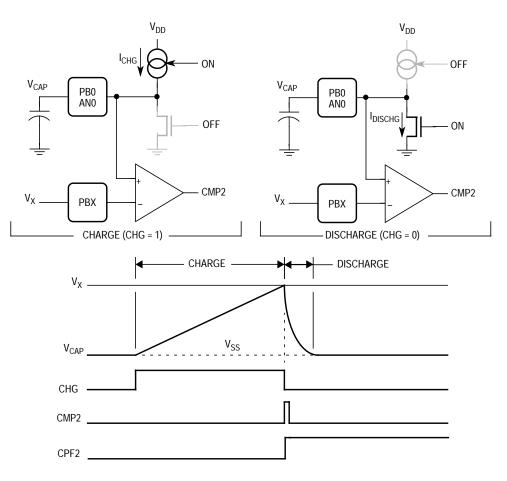

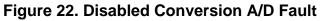

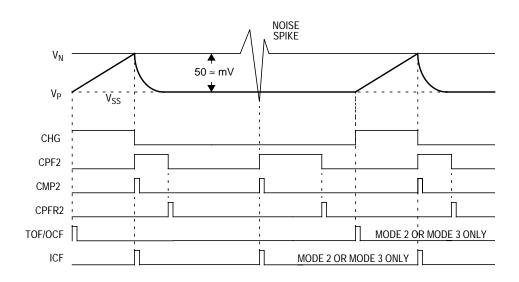

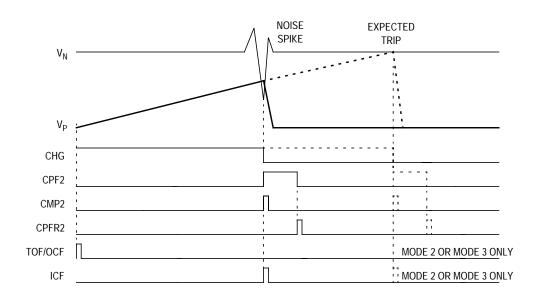

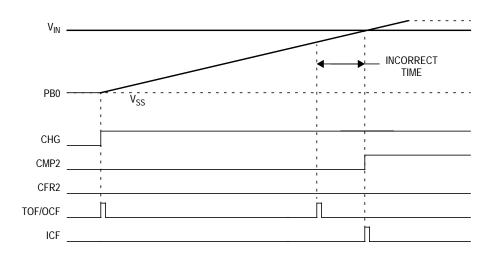

Analog-to-digital (A/D) conversion can be accomplished using the JJ/JP series by allowing the current source to charge up (ramp) an integration capacitor connected to PB0 and using comparator 2 to detect the time when the ramp voltage crosses the unknown voltage being measured as shown in **Figure 20**.

**Application Note**

Figure 20. Single Slope A/D Convertor

The advantages of this design are:

- Simple construction

- Minimal on-chip silicon compared to most 8-bit successive approximation register (SAR) A/D designs

- More flexible than an SAR A/D, which must always perform as an A/D and require its own D/A conversion circuitry

- Some "filtering" of input signal provided by the integration

- Inherently monotonic

- Up to 16 bits are possible with long conversion times

On the other hand, single slope A/D convertors have some disadvantages:

- · Slow conversion times, in the milliseconds

- More software required to do the actual conversion

- External ramp capacitor needed

Overall, the single slope A/D is well suited to many applications with slow-moving signals (<1000 Hz) which are common with many analog sensors and for user input sources like potentiometers. The additional software is offset by the smaller size of the single slope A/D circuitry. The single-slope A/D support circuitry on the MC68HC05JJ/JP series of MCUs uses about 20% less silicon area than the 8-bit SAR A/D commonly found on the MC68HC05P series; and this 20% reduction is equivalent in silicon area to about 400 bytes of ROM. Therefore, even with extensive software, the single slope A/D implementation will use less silicon area than a typical SAR A/D design.

PerformanceFundamental to the single slope A/D conversion technique is the<br/>equation relating time to voltage dependent on the external ramping<br/>capacitor and its charging current:

$$t_{CHG} = \frac{C_{EXT} \times V_X}{I_{CHG}}$$

where:

$t_{CHG}$  = Charge time (seconds)  $V_{x}$  = Voltage to reach (volts)

$C_{FXT}$  = External ramp capacitor ( $\mu$ F)

$I_{CHG}$  = Charge current ( $\mu A$ )

# **Application Note**

From this basic equation, the time can be translated into a number of counts at a given frequency:

$$t_{FS} = \frac{P \times N_{FS}}{f_{OSC}} = \frac{C_{EXT} \times V_{FS}}{I_{CHG}}$$

where:

t<sub>FS</sub> = Full scale charge time (seconds)

N<sub>FS</sub> = Full scale counts (counts)

P = Prescaler (counts out/counts in)

f<sub>OSC</sub> = Oscillator frequency (Hz)

V<sub>FS</sub> = Full scale voltage (volts)

From this relationship, the value of each component in the single slope A/D can be defined at the full-scale voltage input as:

$$V_{FS} = \frac{P \times N_{FS} \times I_{CHG}}{C_{EXT} \times f_{OSC}}$$

$$C_{EXT} = \frac{P \times N_{FS} \times I_{CHG}}{f_{OSC} \times V_{FS}}$$

$$N_{FS} = \frac{C_{EXT} \times V_{FS} \times f_{OSC}}{P \times I_{CHG}}$$

The general process is to begin with the desired full-scale voltage, resolution, and speed of conversion. This information will give

$$V_{FS}$$

,  $N_{FS}$ , and  $t_{FS}$ . Since the charge current,  $I_{CHG}$ , is fixed at 100  $\mu$ A, the only remaining variables are the size of the external capacitor and the effective clock rate which is the product of the prescaler, P, and the oscillator frequency,  $f_{OSC}$ . Usually, the clock frequency is fixed by other system factors, but the prescaler can be selected as eight for mode 2 or mode 3 and greater than eight for software routines using mode 0 or 1.

The last variable is the external capacitor size. But, capacitors come in finite sizes, so there is a trade-off in operating frequency, prescaler, and capacitor size that yields the desired count resolution for a given full-scale voltage range. There is no quick rule to select the best combination, as there are obviously several considerations.

The typical range of single slope A/D performance using the MC68HC05JJ/JP series MCUs is given in **Table 6** as a guide to selecting a starting point.

| Name             | Function                                                                                                                                                      | Min                                       | Тур                                        | Max                                                                | Units  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|--------------------------------------------|--------------------------------------------------------------------|--------|

| V <sub>X</sub>   | Unknown voltage on channel selection bus                                                                                                                      | V <sub>SS</sub>                           | _                                          | V <sub>DD</sub> –1.5                                               | V      |

| V <sub>CAP</sub> | Charging voltage on external capacitor                                                                                                                        | V <sub>SS</sub>                           | _                                          | V <sub>DD</sub> –1.5                                               | V      |

| V <sub>MAX</sub> | Maximum charging voltage on external capacitor                                                                                                                | _                                         | _                                          | V <sub>DD</sub> –1.5                                               | v      |

| I <sub>CHG</sub> | Charging current on external ramping capacitor $V_{DD} = 3 \text{ Vdc}$<br>$V_{DD} = 5 \text{ Vdc}$                                                           | 75<br>85                                  | 90<br>100                                  | 104<br>113                                                         | μA     |

| I <sub>DIS</sub> | Discharge current on external ramping capacitor $V_{DD} = 3 \text{ Vdc}$ $V_{DD} = 5 \text{ Vdc}$                                                             | 1.0<br>1.1                                |                                            |                                                                    | mA     |

| t <sub>CHG</sub> | Time to charge external capacitor<br>(100 kHz < f <sub>OSC</sub> < 4.0 MHz)<br>4-bit result<br>6-bit result<br>8-bit result<br>10-bit result<br>12-bit result | 0.032<br>0.128<br>0.512<br>2.048<br>8.192 | 0.128<br>0.512<br>2.048<br>8.196<br>32.768 | 2.56<br>10.24<br>40.96<br>120 <sup>(1)</sup><br>120 <sup>(1)</sup> | ms     |

| t <sub>DIS</sub> | Time to discharge external capacitor, C <sub>EXT</sub>                                                                                                        | _                                         | 5                                          | 10                                                                 | ms/μF  |

| $C_{\text{EXT}}$ | Capacitance of external ramping capacitor                                                                                                                     | 0.0001                                    | 0.1                                        | 2.0                                                                | μF     |

| Ν                | Number of counts for $I_{CHG}$ to charge $C_{\text{EXT}}$ to $V_{\text{X}}$                                                                                   | 1                                         | 1024                                       | 65536                                                              | counts |

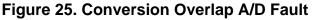

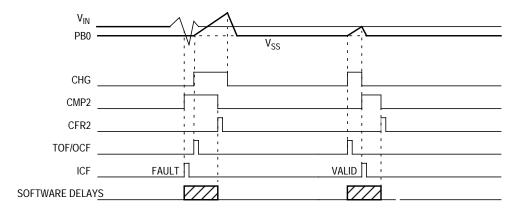

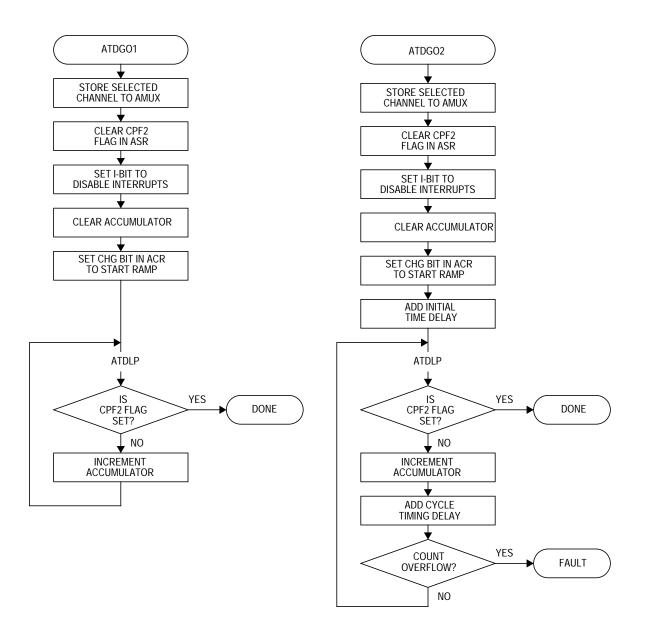

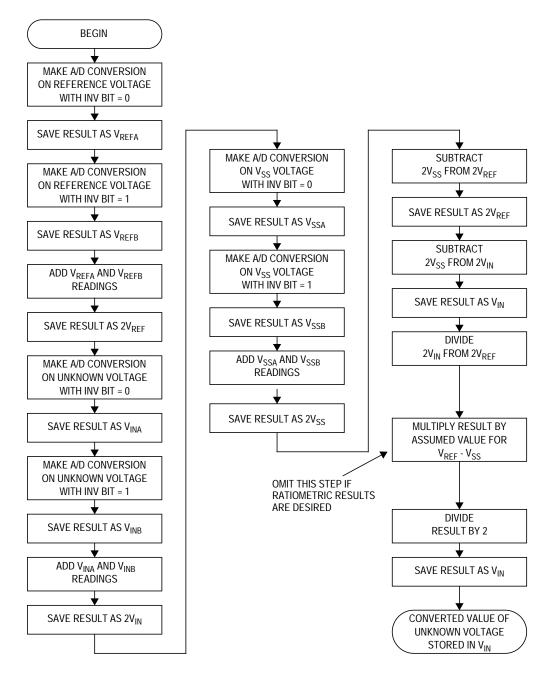

| Ρ                | Prescaler into timing function (÷ P)<br>Using core timer<br>Using 16-bit programmable timer<br>Using software loops                                           | 8<br>8<br>28                              | 8<br>8<br>user defined                     | 8<br>8<br>user defined                                             | ÷P     |