## Motorola Semiconductor Application Note

# AN1831

## Using MC68HC908 On-Chip FLASH Programming Routines

ROM-Resident Routines in the MC68HC908GR8, MC68HC908KX8, MC68HC908JL3, MC68HC908JK3, and the MC68HC908JB8

By Grant Whitacre MMD Applications Engineering Austin, Texas

#### Introduction

This application note describes how to use the routines that are stored in ROM (read-only memory) in the MC68HC908GR8, MC68HC908KX8, MC68HC908JL3/JK3, and the MC68HC908JB8 microcontrollers (MCU).

These routines are used to program, erase, and verify FLASH memory and may be accessed in either user mode or monitor mode<sup>1</sup>. There are additional routines in the MC68HC908KX8 to trim the internal clock generator, which are also described herein. This document describes the method of calling each of the routines in the collection and specifies what is performed and returned as confirmation of routine execution.

To illustrate how these routines are used in practice, a program is included, which can be configured for use in any of these devices to program FLASH in either user mode or monitor mode.

<sup>1.</sup> These routines are accessible in both user mode and monitor mode in all listed devices except the MC68HC908GR8. This device allows access to these routines in monitor mode only.

In addition, a host program, downloadable from the Motorola Web site, has been developed to provide a PC interface to download this program to a device to program FLASH.

#### **FLASH Overview**

The routines described here have been incorporated into ROM on these particular devices, which do not have enough RAM to allow for this functionality in a RAM routine. The type of FLASH for which these routines are applicable is called "split gate" FLASH because of the type of technology used, TSMC FLASH after the fabrication plant, or SST FLASH after the company who originally designed it.

Split gate FLASH has significant advantages. Some of these advantages are:

- Faster programming time. It takes 30 to 40 μs to program each byte, which translates to a little more than a quarter second of programming time to program an entire 8-Kbyte array.

- Better endurance. This type of FLASH is specified to withstand at least 10,000 program/erase cycles. Older technologies provided only about 100 program/erase cycles.

- Simpler programming algorithm. The programming algorithm for split gate FLASH is a simple process of turning on high voltage, applying it to the row to be programmed, and writing values to each byte to be programmed in turn. This differs from past technology which required an iterative process of turning on high voltage and applying it to a page, writing values to each byte in the page, checking all bytes for valid values in a "margin" read condition, and then repeating the program/verify process until all bytes are verified correctly.

Split gate FLASH is programmed generally on a row basis and erased on a page basis. Also, the entire array can be mass erased. A page always contains two rows, but the size of the page can vary from one device to another. A typical page size is 64 or 128 bytes. Before reprogramming a byte in one row that is currently programmed with a different value, the entire page must be erased and reprogrammed. Refer to the applicable data manual for the proper program and erase procedure for this FLASH.

#### The Routines

The collection consists of five callable<sup>2</sup> routines and each is described in **Table 1**. These routines are explained briefly here, but the parameters and the passing method are addressed in later sections.

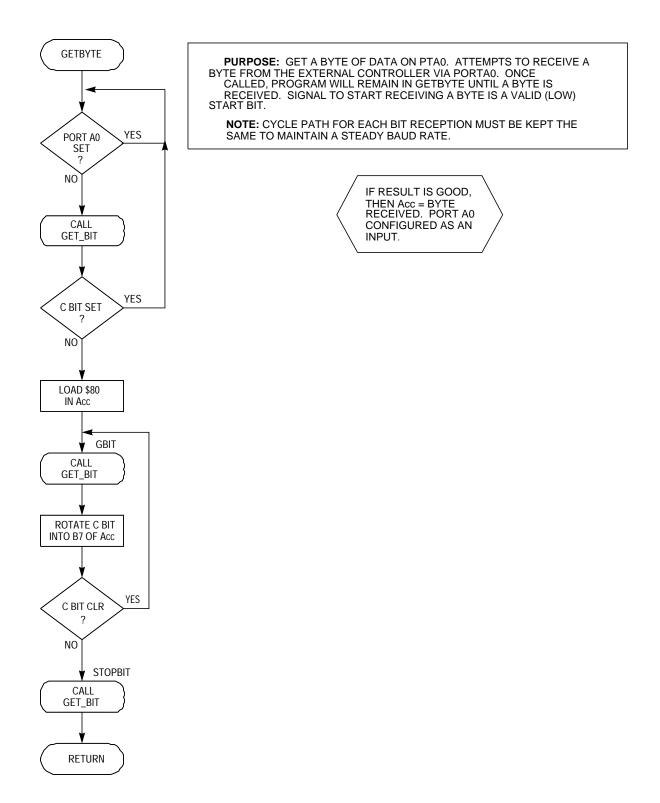

#### GETBYTE

GETBYTE is a routine that receives a byte on the monitor mode communication port defined for that particular device, and this received value is passed back to the calling routine in the accumulator. For these devices, the communication port is either port A0 or port B0. Check **Table 3** for the constant definition for COMMPORT for the port used for each device. This routine expects the same non-return-to-zero (NRZ) communication protocol and baud rate that is used in monitor mode<sup>3</sup>. The difference between this routine's method of receiving a byte and when the monitor receives a byte is that the monitor echoes back whatever is received. It may be more efficient for a RAM program to use this routine when receiving data from a host, to eliminate the time overhead in sending out every byte that is received. This is especially true if the host program and RAM routine already have a built-in error detection scheme, such as a message checksum, and there might not be a need to do an echo check for each byte sent.

<sup>2.</sup> These routines are accessible in both user mode and monitor mode in all listed devices except the MC68HC908GR8. This device allows access to these routines in monitor mode only.

<sup>3.</sup> The baud rate will be  $f_{OP}/256$  for all but the MC68HC908JB8. In this device, the bit rate for this routine as well as for the monitor mode send/receive routines have been changed to accommodate a "standard"  $f_{OP}$  for this device considering it is a USB part. The bit rate for the MC68HC908JB8 is  $f_{OP}/208$ .

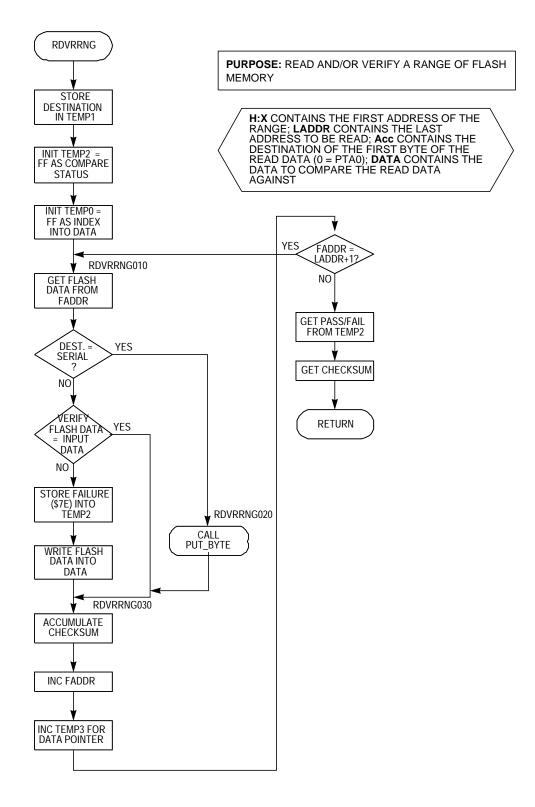

RDVRRNG

RDVRRNG routine serves two purposes:

- It can be used to read a range of FLASH locations.

- It can be used to verify a range of FLASH locations with data contained in the data array in RAM.

Actually, both functions are performed each time the routine is called, and the data in the specified FLASH range is returned. A degree of flexibility with this routine is that one can specify where the data is to be returned. If the accumulator is 0 when entering RDVRRNG, then the data read will be sent to the monitor mode communication port. If the accumulator is non-zero, then the data is placed in RAM in the data array, replacing the existing contents. The beginning and end of the range to be read and/or verified are specified as parameters to this routine. The carry bit of the condition code register is set if the data in the specified range is verified successfully against the data in the data array. One more added function of this routine is that it does a checksum on the data returned. This checksum, which is the LSB of the sum of all bytes in the entire data collection, is stored in the accumulator upon return from the function.

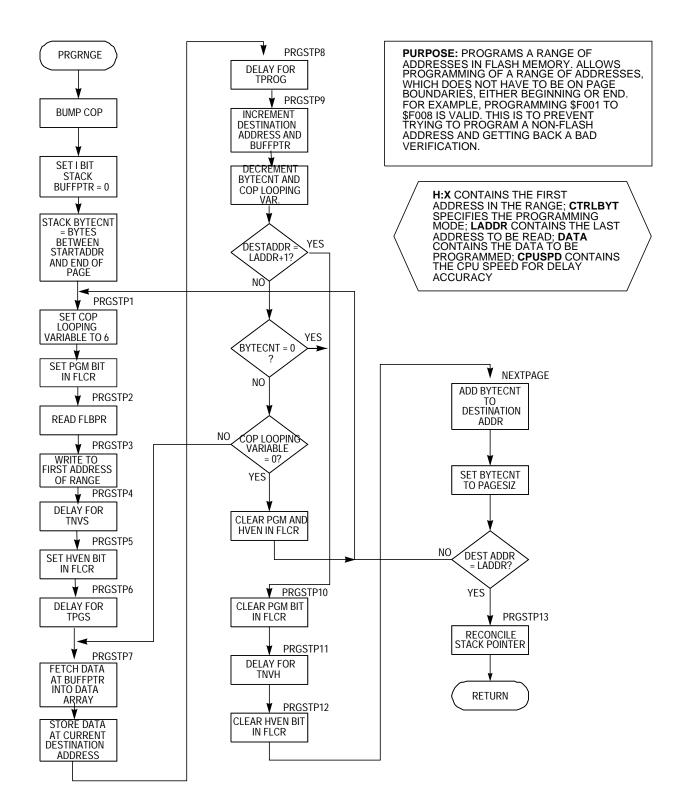

#### PRGRNGE

PRGRNGE is used to program a range of FLASH locations with data loaded into the data array. As with RDVRRNG, the start and end location of the range of addresses to be programmed is passed by parameter. A check to see that all bytes in the specified range are erased is not performed by this routine prior to programming. Nor does this routine do a verification after programming, so there is no return confirmation that programming was successful. It should be noted that PRGRNGE returns with the first-address variable, FADDR, set to the address of the next byte after the range just programmed. The last-address variable LADDR is not changed. Also, since this routine calls the delay routine DELNUS, parameter passing requirements for that routine must be met when calling PRGRNGE.

Another point worth noting is that this routine allows any range to be passed to it. That is, the range does not have to be coincident with row boundaries. The range specified can be at the beginning of a row, the middle of a row, the end of a row, or it can be a range overlapping row boundaries. The only two things that the user must assure is that the range specified is first erased and that whatever is specified as the range, the data for the range must be in the data array in RAM.

**NOTE:** This routine can be used in conjunction with RDVRRNG to perform a complete program and verification cycle of the specified range.

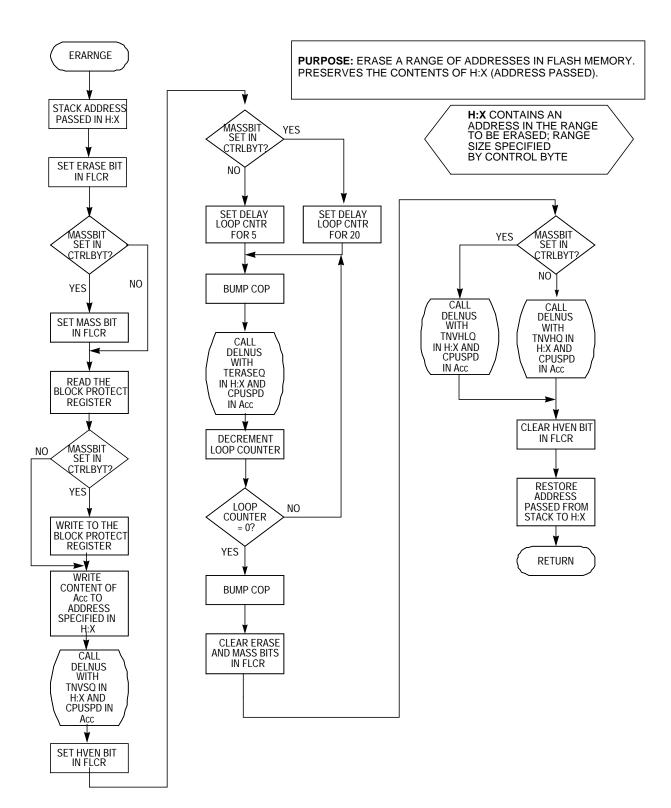

ERARNGE ERARNGE can be called to erase a range of locations in FLASH. This routine does not use the last address (LADDR) variable. The first address (FADDR) placed in H:X in the two previous routines actually can be any address in the range to be erased. There are only two sizes of erase ranges: a page or the entire array. Therefore, this routine needs to be told what type of erase is desired. This is done by setting a bit called the mass bit in a control variable in RAM called CTRLBYT. This is explained in more detail later in Variables.

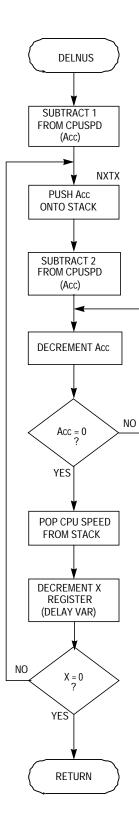

DELNUS The last routine is a delay routine used in support of the PRGRNGE and ERARNGE routines. It can, however, be called independently. DELNUS takes two parameters – one signifying the operating frequency passed via the accumulator and the other, a single byte value passed in the X register, specifying the length of the delay. Neither of these parameters is passed as an absolute value. The operating frequency variable is a value four times that of fOP actually used, and this value has an allowable lower limit of four representing 1-MHz operation. The delay value passed represents the number of 12 microsecond increments for the delay. Therefore, the resolution of the delay is 12 microseconds. The minimum delay is, of course, 12 microseconds and the maximum delay for this routine is a little more than 3 milliseconds (255 \* 12 µs). The precision of the delay is very high considering that it is normalized to the frequency of operation which can be specified to within 0.25 MHz. The worst precision occurs for short delays at relatively slow operating frequencies, where both values passed are midway between possible values<sup>4</sup>.

<sup>4.</sup> An example of this worst-case error would be an  $f_{OP}$  of 1.125 MHz and a desired delay of 18  $\mu$ s. For these conditions, a value for the frequency parameter could be either 4 or 5, signifying an  $f_{OP}$  of 1.00 or 1.25 MHz, respectively. The delay value passed could be either 1 or 2, signifying 12 or 24  $\mu$ s delay, respectively. In a case like this, choose the lower value for one parameter and the upper value for the other parameter to minimize the error of the delay.

When the delay routine is called by PRGRNGE or ERARNGE (the only routines in this collection which call the delay routine), the calling routine loads the X register with the value of the delay needed. The frequency parameter is loaded into the accumulator by reading the RAM variable CPUSPD. This variable, therefore, must be pre-loaded by the RAM routine calling PRGRNGE or ERARNGE.

| Routine<br>Name        | GETBYTE                                  | RDVRRNG                                                                                                                                                                                                                                            | PRGRNGE                                                                                                                                                                                             | ERARNGE                                                                                                                                        | DELNUS                                                                                  |

|------------------------|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| Routine<br>Description | Gets a byte<br>of data from<br>comm port | Reads and/or<br>verifies a range<br>of locations                                                                                                                                                                                                   | Programs a<br>range* of<br>locations                                                                                                                                                                | Erases** a page<br>or the entire<br>range                                                                                                      | Delays for<br>n x 12 μs                                                                 |

| Entry<br>Conditions    | Comm port<br>configured<br>as an input   | H:X contains first<br>address of<br>range; LADDR<br>contains last<br>address read;<br>Acc is tested to<br>see if read data<br>goes to comm<br>port<br>(Acc = \$00) or<br>to DATA;DATA<br>contains data<br>against which<br>to compare<br>read data | H-X contains first<br>address of<br>range; LADDR<br>contains last<br>address to be<br>programmed;<br>DATA contains<br>data used<br>during<br>programming;<br>CPUSPD<br>contains 4 * f <sub>OP</sub> | H:X contains any<br>address in<br>range to be<br>erased; range<br>size specified<br>by control byte;<br>CPUSPD<br>contains 4 * f <sub>OP</sub> | X contains<br>time ÷ 12 of<br>delay (in μs);<br>Acc contains<br>4 times f <sub>OP</sub> |

| Exit<br>Conditions     | Acc is loaded<br>with byte<br>received   | C bit is set if<br>good compare;<br>Acc contains<br>checksum;<br>DATA may<br>contain read<br>FLASH data                                                                                                                                            | H:X contains next<br>address after<br>range just<br>programmed                                                                                                                                      | Preserves<br>contents of H:X<br>(address<br>passed)                                                                                            |                                                                                         |

| Subroutines<br>Called  | Get_Bit                                  |                                                                                                                                                                                                                                                    | DELNUS                                                                                                                                                                                              | DELNUS                                                                                                                                         |                                                                                         |

| Variables<br>Read      |                                          | LADDR, DATA<br>ARRAY                                                                                                                                                                                                                               | CONTROL<br>BYTE, LADDR,<br>DATA ARRAY,<br>CPUSPD                                                                                                                                                    | Control Byte,<br>CPUSPD                                                                                                                        |                                                                                         |

| Variables<br>Modified  |                                          | DATA ARRAY                                                                                                                                                                                                                                         |                                                                                                                                                                                                     |                                                                                                                                                |                                                                                         |

| Stack Used             | 4 bytes                                  | 6 bytes                                                                                                                                                                                                                                            | 7 bytes                                                                                                                                                                                             | 5 bytes                                                                                                                                        | 3 bytes                                                                                 |

#### Table 1. FLASH Routines

\*Allows programming of a range of addresses, which does not have to be on a row boundary, either beginning or end. For example, programming \$F001 to \$F008 is valid.

\*\* Does not check for a blank range before (to see if erase is necessary) or after (to see if successful erase)

#### **Defined Constants**

**Table 2** lists the various constants defined for these routines. All but the FLCR address relate to delays used during programming and erasing. The constants ending in a Q are values passed to the delay routine. As mentioned previously, the delay routine takes a parameter which represents the number of 12 microsecond increments of delay time. Therefore, program time, TPROG, which is specified as a time between 30 and 40 microseconds, has a duration here of 12 times TPROGQ, or 36 microseconds.

Page erase and mass erase delays are done the same way, except that the routines are called ECALLS and MECALLS times, respectively. Therefore, a mass erase delay, which is specified to be 4000 microseconds, is actually 20 delays each with a duration of 17 \* 12 microseconds, which results in a total mass erase delay of 4080 microseconds (MECALLS \* TMERASEQ \* 12 microseconds).

| Constant<br>Name | Description                    | Value  |

|------------------|--------------------------------|--------|

| FLCR             | FLASH control register address | \$FE08 |

| TPROGQ           | Program time                   | 3      |

| TERASEQ          | Erase time                     | 17     |

| TMERASEQ         | Mass erase time                | 17     |

| TNVSQ            | HVEN setup time                | 1      |

| TPGSQ            | Program hold time              | 1      |

| TNVHQ            | HV hold time                   | 1      |

| TNVHLQ           | HV hold time (mass erase)      | 8      |

| TRCVQ            | Return to read time            | 1      |

| ECALLS           | Calls to delay for page erase  | 5      |

| MECALLS          | Calls to delay for mass erase  | 20     |

#### Table 2. Constants Used in Routines

Because of the differences in some of the constants used for each device, the following constants need to be specific to the particular device. **Table 3** shows the constant values for each device. Since these values are device-specific, they have not been included in the source code in **ROM Routines Source Code**.

| Constant<br>Name | Description                                                                               | MC68HC<br>908GR8 | MC68HC<br>908KX8 | MC68HC<br>908JL3/JK3 | MC68HC<br>908JB8 |

|------------------|-------------------------------------------------------------------------------------------|------------------|------------------|----------------------|------------------|

| RAM              | Start address of RAM                                                                      | \$40             | \$40             | \$80                 | \$40             |

| ROWSIZ           | Size of row for programming                                                               | 32               | 32               | 32                   | 64               |

| COMMPORT         | Communication port for monitor mode                                                       | PTA0             | PTA0             | PTB0                 | PTA0             |

| FLBPR            | FLASH block protect<br>register address                                                   | \$FF7E           | \$FF7E           | \$FE09               | \$FE09           |

| Get_Put          | Address of routine to<br>get and then output a<br>byte on the comm<br>port (monitor code) | \$FE99           | \$FE97           | \$FEBD               | \$FEC0           |

| Put_Byte         | Address of routine to<br>output a byte on<br>communication port<br>(monitor code)         | \$FEAE           | \$FEAA           | \$FED0               | \$FED5           |

| Get_Bit          | Address of routine to<br>get a bit on<br>communication port<br>(monitor code)             | \$FED2           | \$FECE           | \$FF00               | \$FF00           |

Table 3. Device-Specific Values for Constants

### Variables

**Table 4** shows the variables used in the routines. These variables are either passed in a register or as static variables in a predefined location in RAM. FADDR is a 2-byte value that represents the first address in the range on which to be operated. It is passed in the H:X registers when a call is made to one of the routines. The first address of a range can be any valid FLASH address and does not have to be on a row or page boundary.

LADDR is the last address in the range and is passed in the first byte of the data structure in RAM. This data structure is very simple, consisting of the last address, the CPU speed variable, a control byte, and the data array. It is discussed in detail in **The Data Structure**. The last address, like the first address, can be any valid FLASH address and is not restricted to being the last byte of a page or row.

The internal operating frequency of the device on which the FLASH operation is to be performed is passed in a variable called CPUSPD. It is a 1-byte value which is passed in the data structure and should be given as the rounded product of four times the actual internal operating frequency, such that if  $f_{OP}$  is 2.4576 MHz, then the value passed should be decimal 10, or \$0A. This variable is used to normalize the length of delays with respect to the operating frequency, and passing a value four times the actual frequency provides better resolution.

The remaining operating parameter used in these routines is a single bit value in the control byte. This bit is called the mass bit and is set when calling ERARNGE to perform a mass erase. If ERARNGE is called with the intention of performing a page erase, then the mass bit must be cleared. The other bits in CTRLBYT are not used and can be set at the user's discretion for other flags.

| Variable Name | Description                            | Size    | Location/Passing<br>Method |

|---------------|----------------------------------------|---------|----------------------------|

| FADDR         | First address of range<br>of locations | 2 bytes | H:X                        |

| LADDR         | Last address of range<br>of locations  | 2 bytes | Data structure             |

| CPUSPD        | 4 x f <sub>OP</sub>                    | 1 byte  | Data structure             |

| CTRLBYT       | CTRLBYT Mass bit (bit 6)               |         | Data structure             |

| DATA          | DATA Data array                        |         | Data structure             |

Table 4. Variables Used in Routines

#### The Data Structure

The data structure is a collection of static variables in RAM used in the execution of the three main routines – PRGRNGE, ERARNGE, and RDVRRNGE. The data structure is in the same relative location in RAM and the content is the same data and order for all of the devices containing these ROM routines. The structure always starts in the ninth byte of RAM and the order of the variables is as shown in **Table 5**.

| Location                 | Variable<br>Name | Size<br>(Bytes) | Description                                                                        |

|--------------------------|------------------|-----------------|------------------------------------------------------------------------------------|

| RAM + \$08               | CTRLBYT          | 1               | Includes mass flag as bit 6                                                        |

| RAM + \$09               | CPUSPD           | 1               | CPU speed passed as 4 x f <sub>OP</sub>                                            |

| RAM + \$0A<br>RAM + \$0B | LADDR            | 2               | Last address for read a range<br>and program a range                               |

| RAM + \$0C               | DATA             | Variable        | Variable number of bytes of passed<br>data for programming or verifying<br>a block |

Table 5. Data Structure Location and Content

Note that the data array DATA is variable in length. This is done to support a variable number of locations on which to perform any of the programming, reading, or verifying actions. Most of the time, these actions will be performed on a row of data at one time, although that need not be the case. Some of these devices have a rather small RAM array, and the size of the data array must be limited to the size of RAM minus the stack needed and the size of any RAM routine being executed. If the RAM routine is kept to a reasonable size, then there should not be a problem defining the data array to be the size of a row for any of the devices in this collection.

#### **Addresses of Routines**

The address to call each of the five routines varies among the devices. **Table 6** gives the absolute address that should be used when calling the routines.

| Routine | MC6868HC<br>908GR8 | MC68HC<br>908KX8 | MC68HC<br>908JL3/JK3 | MC68HC<br>908JB8 |

|---------|--------------------|------------------|----------------------|------------------|

| GETBYTE | \$1C00             | \$1000           | \$FC00               | \$FC00           |

| RDVRRNG | \$1C03             | \$1003           | \$FC03               | \$FC03           |

| ERARNGE | \$1C06             | \$1006           | \$FC06               | \$FC06           |

| PRGRNGE | \$1C09             | \$1009           | \$FC09               | \$FC09           |

| DELNUS  | \$1C0C             | \$100C           | \$FC0C               | \$FC0C           |

**Table 6. Addresses of Routines**

#### MC68HC908KX8 Trim Routine

The MC68HC908KX8 contains two additional routines in ROM, which have been included to support the trimming of the internal clock generator (ICG) module. ICGTRIM is located at \$1330 in the MC68HC908KX8 and can be called to trim the ICG by measuring the pulse width of a break signal received on port A0 or port B4. The baud rate used for the break signal must be equal to the internal frequency of the device divided by 256. Communication must be in conformance with normal monitor mode communication, that is, non-return-to-zero (NRZ) format. A break signal is defined as 10 consecutive low bits, so the pulse width of this signal is nominally 1.04 milliseconds at 9600 baud. This signal must be within 25 percent of the nominal value or the routine will not attempt to trim the ICG.

**Table 7** specifies the relationship between the internal frequency, the baud rate, and the pulse width of the break signal.

| f <sub>OP</sub> | Baud Rate | Brea    | ms)     |         |

|-----------------|-----------|---------|---------|---------|

| (MHz)           | (bps)     | Minimum | Nominal | Maximum |

| 1.2288          | 4800      | 1.5623  | 2.083   | 2.604   |

| 2.4576          | 9600      | 0.781   | 1.042   | 1.302   |

| 3.6864          | 14400     | 0.365   | 0.521   | 0.651   |

| 4.9152          | 19200     | 0.195   | 0.260   | 0.325   |

| 7.3728          | 28800     | 0.098   | 0.130   | 0.163   |

This routine checks to see how many cycles are measured during a break signal (10 low bits) sent at  $f_{OP}/256$  baud by a host and adjusts its trim register. If the break signal is more than 25 percent variation from what is expected (0.78-1.30 ms @ 9600), then ICG trimming will not be performed. This ICG accuracy limit is consistent with the extent of the ICG's ability to fine tune the trim register.

The main timing loop of this routine begins at the leading edge of the break signal and lasts until it sees the trailing edge. The break signal lasts for 10 bit times. Since communicating at  $f_{OP} \div 256$  bps, then the duration of 10 bit times is 2560 cycles. Each time through the loop is 10 cycles, so it is expected to execute the loop 256 times if the MC68HC908KX8 is in sync serially with the host.

If the loop is executed for more than 256 loop cycles, then the MC68HC908KX8 must be running faster than expected and needs to be slowed down. If the loop is executed for less than 256 loop cycles, then the MC68HC908KX8 must be running slower than expected and needs to be speeded up. The amount that the CPU speed is changed is equal to the number of loop cycles over or under 256. So if the loop is traversed 240 times, then we are running  $(256 - 240) \div 256 = 6.25$  percent fast.

Each incremental change that is made to the trim register (ICGTR) will result in a 0.195 percent change to the internal clock. That is, incrementing the register by one over the default value of \$80 stored there will decrease the internal clock by 0.195 percent. Each execution of the loop over or under what is expected (256 times) represents an error of 1/256 = 0.391 percent error. So the number of loop cycles is

doubled and this number is used to correct the trim register. The precision for trimming is therefore 0.391 percent.

Another routine that is unique to the MC68HC908KX8 is called ICGTEST. This routine simply toggles a port pin, port A4, at a rate that is 1/16th of the operating frequency. This allows verification that the ICG was trimmed accurately. ICGTEST is located at \$1369.

#### **Typical Routine Calls**

This section provides examples of how these routines may be called.

The following code makes a call to the delay routine (DELNUS). Assume  $f_{OP} = 7.37$  MHz, so the value passed in the accumulator is round  $(f_{OP} * 4) = 29$  (\$1D). The delay value is loaded into and passed through the X register. For example, let's use a value, TMERASEQ, which is the desired delay time divided by 12.

DELAYCALL:

LDA #\$1D LDX #TMERASEQ JSR DELNUS ;f<sub>OP</sub>\*4 ;delay time/12

The next block of code makes a call to the routine RDVRRNG to read and verify a range of FLASH from \$F000 to \$F010. The accumulator is cleared before calling the routine, which signals to the routine that the specified range is to be sent out the communication port instead of being copied into RAM.

The verify stage will be performed automatically and each byte in the FLASH range will be compared to the corresponding byte in the data array in RAM. That is, the first byte of the range, \$F000, will be compared with the first byte in the data array which is located at the 13th byte of RAM by definition. This process is repeated for all bytes in the range and if any of the comparisons is not equal, then the carry bit of the condition code register will be cleared upon return from RDVRRNG. Otherwise, it will be set. This code does not show the loading of the compare data into RAM.

Before calling the routine, the high byte and low byte of the last address of the range are placed in the 11th and 12th locations of RAM, respectively, and the H:X register is loaded with the first address of the range.

| RDCALL: |         |                                  |

|---------|---------|----------------------------------|

| CLRA    |         | ;COMMPORT IS DEST.               |

| LDHX    | #\$F010 | ;LAST ADDRESS IS STORED AT LADDR |

| STHX    | LADDR   |                                  |

| LDHX    | #\$F000 | ;FIRST ADDRESS IS STORED IN H:X  |

| JSR     | RDVRRNG |                                  |

The next few lines of code perform an erase of FLASH. The variable CPUSPD located at the 10th location of RAM is set to a value which reflects an 8-MHz operating frequency, that is 8 \* 4 = 32 (\$20). Since we are calling the erase routine, we must specify what type of erase we want to do: page erase or mass erase. This example illustrates the setup to perform a mass erase where the mass bit, bit 6, in CTRLBYT at the ninth location of RAM must be set. Any valid FLASH address is loaded into H:X when doing a mass erase. In the case of a page erase, any address within that page would be acceptable.

MASSERASE:

| MOV   | #\$20,CPUSPD | ;SET CLOCK VALUE AT 8 MHZ      |

|-------|--------------|--------------------------------|

| BSET6 | CTRLBYT      | ;SET TO MASS ERASE HERE        |

| LDHX  | #\$F000      | ;LOAD ANY FLASH ADDRESS IN H:X |

| JSR   | ERARNGE      |                                |

To call GETBYTE to receive a byte of data on the communication port, the only thing that needs to be done is to ensure that the communication port is configured as an input. The next code example assumes that port A0 is the communication port.

| RECEIVEBYTE: |         |              |                  |

|--------------|---------|--------------|------------------|

| BCLR         | 0, DDRA | ;CLEAR BIT 0 | DATA DIRECTION   |

|              |         | ; REGISTER F | OR INPUT ON PTA0 |

| JSR          | GETBYTE |              |                  |

The final two examples show how to call the ICG trim routine resident in MC68HC908KX8 ROM, and then call the test routine to verify the accuracy of the internal clock. To set up for the call to trim the ICG, several things must be done. First, we make sure that the ICG is enabled (ICGON bit in the ICG trim register is set) and the internal clock is selected (CS bit in the trim register is cleared). Then the accumulator is

set to select the port which is to receive the break signal. In this example, port A0 is used as the communication port and the one where the break signal will be received. To select port A0, the accumulator must contain a non-zero value. We'll also set this port as an input here.

| TRIMTH | EICG: |             |                                    |

|--------|-------|-------------|------------------------------------|

|        | BCLR  | 0,DDRA      | ;SET PTAO AS AN INPUT              |

|        | MOV   | #\$80,ICGTR | ;SET THE TRIM REGISTER TO MIDPOINT |

|        | MOV   | #\$08,ICGCR | ;TURN ON THE ICG AND SELECT IT A   |

|        |       |             | ; CLOCK SOURCE                     |

|        | LDA   | #\$FF       | ;ANY NON-ZERO VALUE TO SELECT PTA0 |

|        |       |             | ; FOR COMM                         |

|        | JSR   | ICGTRIM     |                                    |

There is no setup required to call the next routine which allows monitoring of a set fraction of the operating frequency. The port used to output 1/16th the operating frequency, port A4, is set as an output in the routine. Therefore, only the call is required. To stop execution of this routine, the IRQ pin needs to be pulled low. External interrupts can be disabled (I bit set in the CCR) so as not to generate an inadvertent interrupt when this pin is set low to exit this routine.

```

TESTTHEICG:

JSR ICGTEST

```

#### **Example RAM Routine**

This section describes a program containing a RAM routine which could be used in either monitor mode or user mode for the purpose of programming one of these devices. In monitor mode, the routine could be downloaded via monitor commands and in user mode the routine could be copied to RAM from FLASH.

Those readers who have read *In-Circuit Programming of FLASH Memory in the MC68HC908GP20*, Motorola document order number AN1770/D, will recognize the content and structure of this program. Refer to AN1770 for a complete description of the protocol used to send programming commands and data to this routine. The PC-based host program described in that application note has been expanded to support the programming of these and other devices and is available in

the software library of the Motorola Web site at: http://mot-sps.com/csic/techhelp/appsw/appsw.htm.

The RAM routine here is much smaller than that required for the MC68HC908GP20 because it makes calls to the ROM routine rather than have these routines included in the RAM routine. The latter situation would not be practical in small RAM-array devices such as the ones that include these routines. The source code for this program follows. The user of this routine must make sure that the assembler directives are set properly based on the device and the mode to be used.

This routine also differs from the GPZO's in that it only supports monitor comm port communication for both user and monitor mode programming. Since the SCI is not available on two of these devices, SCI communication is not described here. This program could be modified easily to support user mode SCI programming.

This program does not include support for trimming the ICG in the MC68HC908KX8. A RAM routine for monitor mode trimming or a FLASH-based routine for user mode trimming could be generated by the user. Note though that the host program referred to previously can be used to send the break signal for automatic trimming.

```

*****

* FILE NAME: GKJJRR.ASM

* PURPOSE: Provides a FLASH erase, program, and verify program

TARGET DEVICE: MC68HC908GR8, MC68HC908KX8, MC68HC908JL3/JK3 and the MC68HC908JB8

* ASSEMBLER: mcuEZ

*

VERSION: 1.0.5

*

PROGRAM DESCRIPTION:

* This program loads a RAM routine with instructions/data

*

located in FLASH memory that:

*

Receives data over the monitor comm. Port

Calls ROM routine to program FLASH with received data

Calls ROM routine to read/verify a FLASH range

Calls ROM routine to bulk erase device upon command

* The program has assembler directives to be able to program each device in both

* user and monitor modes. In monitor mode, the generated S-record file will contain

* only the RAM routine. It will not have any code that would reside out of RAM.

* In user mode, load routines are incorporated so that it could be contained in a

* user's application. The load routines load the programming routines into RAM and

* from there it looks just like the RAM routine executed in monitor mode.

```

```

*

* AUTHOR: Grant Whitacre

* LOCATION: Austin, Texas

* UPDATE HISTORY:

* REV

AUTHOR

DATE

DESCRIPTION OF CHANGE

* ===

______

========

_____

G. WHITACRE

* 0.0

11/02/98

INITIAL VERSION

01/19/99

* 0.1 G. WHITACRE

MOD. FOR KX6

* 0.2 G. WHITACRE

04/22/99

MOD. FOR JL3

* 0.3 G. WHITACRE

MOD. FOR JB8, GR8

11/18/99

* GENERAL CODING NOTES:

* Bit names are labeled with <port name><bit number> and are used in the commands

* that operate on individual bits, such as BSET and BCLR. A bit name followed by a

* dot indicates a label that will be used to form a bit mask.

* ASSEMBLER DIRECTIVES

* (INCLUDES, BASE, MACROS, SETS, CONDITIONS, RAM DEFS, ETC.)

; DEFAULT TO BASE 10 NUMBER DESIGNATION

BASE 10D

;Remember: ACTIVE LOW!!!!!!!!!!!!!

RAMPROG: SET 0

; IF SET, ALL (NECESSARY) ROUTINES WILL BE

;ADDRESSED IN RAM INITIALLY;THIS VERSION

; WOULD BE USED AS THE S19 RECORD FILE

; THAT IS DOWNLOADED INTO RAM INMONITOR

; MODE FOR FLASH PROGRAMMING

* SELECT ONLY ONE OF THE FOLLOWING!

GR8: SET 1

;SELECTS GR8 AS THE TARGET DEVICE

KX8: SET 1

;SELECTS KX8 AS THE TARGET DEVICE

JB8: SET 1

;SELECTS JB8 AS THE TARGET DEVICE

JL3: SET 0

;SELECTS JL3 AS THE TARGET DEVICE

* APPLICATION-SPECIFIC MEMORY AND I/O EQUATES

* THE VALUE FOR SPDSET, WHICH IS THE \mathrm{f}_{\mathrm{OP}}*4, normalizes delay routines

* to an absolute time.

SPDSET

EQU

10

;10 => 2.5 MHZ OPER. FREQ.

$00

PTA

EQU

EQU

$01

PTB

CONFIG1

EQU

$1F

;CTRLBYT MASS BIT = 6

MASSBIT

EQU

6

;NOT TO EXCEED SIZE OF RAM ROUTINE

EQU

$50

RAMPRSZ

RAMPRG

EQU

$AC

;START OF RAM ROUTINE

EQU

$F000

;START OF FLASH PROGRAM

PRGSTRT

PRGSTRT+RAMPRG

XFRCODE

EQU

;RESET VECTOR LOCATION

RSTVLOC

EQU

$FFFE

```

| FLCR     | EQU | \$FE08     | ;FLASH CONTROL REGISTER                             |

|----------|-----|------------|-----------------------------------------------------|

| IFEQ GR  | 8   |            |                                                     |

| COMPORT  | EQU | PTA        |                                                     |

| RAM      | EQU | \$40       |                                                     |

| GETBYTE  | EQU | \$1C00     |                                                     |

|          |     | \$FE99     |                                                     |

| GET_PUT  | EQU |            |                                                     |

| GET_BIT  | EQU | \$FED2     |                                                     |

| PUT_BYTE | EQU | \$FEAE     |                                                     |

| ROWSIZ   | EQU | 32         |                                                     |

| FLBPR    | EQU | \$FF7E     |                                                     |

| ENDIF    |     |            |                                                     |

| IFEQ KX  |     |            |                                                     |

| COMPORT  | EQU | PTA        |                                                     |

| RAM      | EQU | \$40       |                                                     |

| GETBYTE  | EQU | \$1000     |                                                     |

| GET_PUT  | EQU | \$FE97     |                                                     |

| GET_BIT  | EQU | \$FECE     |                                                     |

| PUT_BYTE | EQU | \$FEAA     |                                                     |

| ROWSIZ   | EQU | 32         |                                                     |

| FLBPR    | EQU | \$FF7E     |                                                     |

| ENDIF    | ~   |            |                                                     |

| IFEQ JL  | 3   |            |                                                     |

| COMPORT  | EQU | PTB        |                                                     |

| RAM      | EQU | \$80       |                                                     |

| GETBYTE  | EQU | \$FC00     |                                                     |

| GET_PUT  | EQU | \$FEBD     |                                                     |

|          | EQU | \$FF00     |                                                     |

| GET_BIT  |     |            |                                                     |

| PUT_BYTE | EQU | \$FED0     |                                                     |

| ROWSIZ   | EQU | 32         |                                                     |

| FLBPR    | EQU | \$FE09     |                                                     |

| ENDIF    |     |            |                                                     |

| IFEQ JB  |     |            |                                                     |

| COMPORT  | EQU | PTA        |                                                     |

| RAM      | EQU | \$40       |                                                     |

| GETBYTE  | EQU | \$FC00     |                                                     |

| GET_PUT  | EQU | \$FEC0     |                                                     |

| GET_BIT  | EQU | \$FF00     |                                                     |

| PUT_BYTE | EQU | \$FED5     |                                                     |

| ROWSIZ   | EQU | 64         |                                                     |

| FLBPR    | EQU | \$FE09     |                                                     |

| ENDIF    |     |            |                                                     |

|          |     |            |                                                     |

| RDVRRNG  | EQU | GETBYTE+3  |                                                     |

| ERARNGE  | EQU | GETBYTE+6  |                                                     |

| PRGRNGE  | EQU | GETBYTE+9  |                                                     |

| DELNUS   | EQU | GETBYTE+12 |                                                     |

|          |     |            |                                                     |

| DATSTRC  | EQU | RAM+8      | ;Leave 8-bit offset from start of RAM for dev tools |

|          |     |            |                                                     |

\* VARIABLE DEFINITIONS & RAM SPACE USAGE \* DOWNLOADED SET FOR RTNS SIZE \_\_\_\_\_ \_\_\_\_\_ \_\_\_\_\_ \* RAM - RAM+\$07 RES. FOR DEV. TOOLS ( 8 BYTES) \* RAM+\$08 TRANSFER SIZE CTRLBYT ( 1 BYTE) \* RAM+\$09 FIRST ADDRESS CPUSPD (2/1 BYTE) \* RAM+\$0A:RAM+\$0B DATA SIZE LAST ADDRESS (1/2 BYTES)DATA ARRAY \* RAM+\$0C:RAM+\$0D DATA ARRAY ( 32 BYTES) \* \$AC - \$EB RAM PROGRAM ( 64 BYTES) ( 20 BYTES) \* \$EC-\$FF STACK \* TOTAL (128 BYTES) ORG RAM TEMP2B RMB 2 TEMPH RMB 1 TEMPL RMB 1 ORG DATSTRC 1 CTRLBYT RMB CPUSPD RMB 1 LADDR RMR 2 RMB ROWSIZ DATA Program Algorithm (User Mode Programming) \* 1. Initialize all variables and ports. \* 2. Monitor COMM port for input of block of data to be programmed and \* the start address. Load RAM with the data array (up to 64 bytes), the start \* address and length of data array. \* 3. Transfer the following subroutines to \* RAM at address RAMPRG \* A. LDDATA B. MAINPRG Jump to first byte of main RAM program (RAMPRG). \* 4. \* 5. Execute RAM program MAINPRG and then return to comm \* port monitoring loop in RAM. \* \* Program Algorithm - Monitor Mode Programming \* Monitor comm port for input of block of data to be 1. \* programmed and the start address. Load RAM with the data array (up to \* 64 bytes), the start address and length of data array. Execute RAM program MAINPRG and then return to PTA0/PTB0 2. monitoring loop in RAM. \* START OF PROGRAM IFNE RAMPROG ORG PRGSTRT CLR COMPORT ;DISABLE THE COP AND LVI MOV #\$11,CONFIG1

\* NAME: LDRAMPR \* PURPOSE: LOADS MAIN RAM PROGRAM AND ALL NEC. SUBROUTINES \* ENTRY CONDITIONS: NONE \* EXIT CONDITIONS: NONE \* SUBROUTINES CALLED: \* EXTERNAL VARIABLES USED: \* DESCRIPTION: EXECUTED OUT OF FLASH LDRAMPR LDHX #RAMPRG ;STORE THE START LOCATION IN RAM STHX TEMPH ;WHERE CODE IS TO BE TRANSFERRED #XFRCODE ;LOAD 1ST ADDR OF FLASH CODE TO BE T'DHX X+,TEMP2B ;TRANSFER LOCATION IN RAM NXTMOVE MOV PSHH PSHX ; PUSH CURRENT FLASH ADDDR TO STACK TEMPH ;LOAD ADDRESSES THAT HOLD THE DEST. T'DHX MOV TEMP2B,X+ ;TRANSFER DATA FROM TRANSFER LOCATION NEXT STHX TEMPH CPHX #RAMPRG+RAMPRSZ ;TO NEXT LOCATION AT RAM DESTINATION PULX ; POP CURRENT FLASH ADDR FROM STACK PULH BNE NXTMOVE ; IF NOT DONE, CONTINUE JMP RAMPRG ORG XFRCODE ;START OF CODE TO BE TRANSFERRED TO RAM ELSE ORG RAMPRG ;START OF MONITOR PROGRAM WHICH IS ORG'D ; IN RAM ENDIF \* NAME: LDDATA \* PURPOSE: LOAD RAM WITH USER'S DATA AND START ADDRESS VIA THE COMM PORT; PROGRAMS AND THEN DUMPS DATA THAT IS DOWNLOADED; ONLY DUMPS DATA IN ROW SPECIFIED IF NUMBER OF BYTES TO BE PROGRAMMED (DATASIZ) IS 0. \* ENTRY CONDITIONS: \* EXIT CONDITIONS: \* SUBROUTINES CALLED: PRGFLSH, DUMPROW \* EXTERNAL VARIABLES USED: \* DESCRIPTION: EXECUTED OUT OF RAM \* THE STRUCTURE OF THE DATA RECEIVED IS AS FOLLOWS: LOCATION DESCRIPTION RAM LOC. ======== ======== \_\_\_\_\_ COUNT OF THE TOTAL NUMBER OF RAM+\$08 1 \* BYTES TO BE SENT (INCL. THAT BYTE) 2-3 THE FIRST ADDRESS WHERE THE RAM+\$09 thru RAM+\$0A \* FOLLOWING DATA IS TO BE PROGRAMMED \* NUMBER OF BYTES TO BE PROGRAMMED RAM+\$0B 4 \* 5-68 ARRAY SPACE FOR DATA TO BE PROGRAMMED RAM+\$0C thru RAM+\$4B \* IF A COUNT IS USED THAT IS GREATER THAN (PROGRAM LENGTH + 1) \* THEN THE ROUTINE WILL HANG AFTER THE LAST PROGRAM BYTE IS SENT.

| * AFTER<br>* IF A I<br>* THEN I<br>* WAS TH<br>* A COMN<br>*<br>*<br>* RAM+\$(<br>* RAM+\$(<br>* RAM+\$(<br>* RAM+\$( | THE LA<br>DATA AF<br>PROGRAM<br>HE MOST<br>MAND BY<br>08<br>09<br>08<br>09<br>08<br>09 |                                                                                     | MBER OF BYTES TO BE PROD<br>SIGNAL TO ERASE THE ENTI<br>ENT BULK ERASE WITHOUT F<br>PROGRAM<br>==========<br>CTRLBYT<br>CPUSPD<br>LAST ADDRESS (MSB)<br>LAST ADDRESS (LSB) | GRAMMED OF \$FF<br>IRE ARRAY. THIS<br>HAVING TO HAVE<br>SIZE<br>( 1 BYTE)<br>( 1 BYTE)<br>( 1 BYTE)<br>( 1 BYTE) |

|-----------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|

|                                                                                                                       | * * * * * * *                                                                          | * * * * * * * * * * * * * * * * * * * *                                             | * * * * * * * * * * * * * * * * * * * *                                                                                                                                    | * * * * * * * * * * * * * * * *                                                                                  |

| LDDATA:                                                                                                               | GI DII                                                                                 |                                                                                     |                                                                                                                                                                            |                                                                                                                  |

| WAITRX:                                                                                                               | JSR<br>CPX<br>BNE<br>TSTA                                                              | #CTRLBYT<br>GET_PUT<br>#CTRLBYT<br>STORNOW                                          | ;POINT TO LOCATION<br>;CALL TO ROUTINE II<br>;BAD START - KEEP I                                                                                                           | N MONITOR CODE                                                                                                   |

| STORNOW                                                                                                               | ~                                                                                      | WAITRX<br>,X<br>CTRLBYT,WAITRX                                                      | ;STORE THE DATA IN<br>;MOVE TO NEXT RAM :<br>;DEC. PROG SIZE CN<br>;IF ENTIRE PROG NO                                                                                      | LOCATION<br>TR (1st BYTE)                                                                                        |

| CPARSE                                                                                                                | LDHX<br>STHX<br>MOV<br>MOV<br>AIX<br>STHX<br>LDHX                                      | CPUSPD<br>TEMP2B<br>#SPDSET,CPUSPD<br>LADDR+1,TEMPH<br>#ROWSIZ-1<br>LADDR<br>TEMP2B | ;\$89<br>;MAINTAIN FIRST BY<br>;PUT THE CPU SPEED<br>; INTO CPUSPD ADDR<br>;MAINTAIN DATASIZ<br>;DO THIS FOR BOTH .<br>;                                                   | TE IN TEMP2B<br>SELECTED IN EQUATE                                                                               |

|                                                                                                                       | LDA<br>BEQ<br>COMA<br>BEQ                                                              | TEMPH<br>DUMPROW<br>ERASE1                                                          | ;IF SIZE OF DATA T<br>;IS 0 THEN BRANCH ;<br>;IF SIZE IS FFH, T                                                                                                            | TO DUMP                                                                                                          |

| JUSTPRG                                                                                                               | LDA<br>STA<br>JSR<br>BRA                                                               | #\$FF<br>FLBPR<br>PRGRNGE<br>DUMPROW                                                |                                                                                                                                                                            |                                                                                                                  |

| ERASE1                                                                                                                | BSET<br>JSR                                                                            | MASSBIT,CTRLBYT<br>ERARNGE                                                          |                                                                                                                                                                            |                                                                                                                  |

#### **ROM Routines Source Code**

The following five flowcharts provide graphic explanations of the ROM routines source code.

Figure 1. GETBYTE

Figure 2. RDVRRNG

Figure 3. PRGRNGE

$\label{eq:purpose: DELAY FOR N*12 US FOR $f_{OP} >= 1$ MHZ;$ D = (DELAY TIME[US]/12) IN X, C = (f_{OP}[MHZ]*4)$ IN Acc CYCLES = 5+(DELAY/12)* 3(4f_{OP}-3)+9 = 5+DELAY*f_{OP}$ }$

X CONTAINS THE TIME/12 OF DELAY (IN MICROSECONDS.); Acc CONTAINS CPUSPD (CPU SPEED X 4); CPU SPEED MUST BE >= 1 MHZ

Figure 4. DELNUS

Figure 5. ERARNGE

#### **ROM Routines Source Code**

```

FILE NAME: MAINPR.ASM

*

PURPOSE: To provide FLASH erase, program and verify routines

*

to reside in ROM.

TARGET DEVICE: MC68HC908GR8, MC68HC908KX8, MC68HC908JL3/JK3 and the MC68HC908JB8

*

MEMORY USAGE - RAM: 4-36 BYTES, DEPENDING ON DATA PASSED

ROM: 364 BYTES

*

*

ASSEMBLER: MCUEZ

*

VERSION: 1.0.5

*

PROGRAM DESCRIPTION:

* This program contains a structure of routines to facilitate FLASH programming.

* These routines, which are individually callable, are intended to reside in ROM

* for the use of a user program, a test/burn-in program, or for development/programming

* tools. This set of routines is included, along with definition files, by the project

*

file 9GR8ALLROM.ASM.

*

AUTHOR: Grant Whitacre

*

LOCATION: Austin - Oak Hill, Texas

*

* UPDATE HISTORY:

*

REV

AUTHOR

DESCRIPTION OF CHANGE

DATE

*

===

============

=======

0.0 G. WHITACRE

10/05/98

Initial release

0.1

G. WHITACRE

02/17/99

MODIFIED FOR THE SST FLASH

0.2 G. WHITACRE

08/23/99

MODIFIED GETBYTE FOR 9600

BAUD @ 2.4576 MHZ

* GENERAL CODING NOTES:

* Bit names are labeled with <port name><bit number> and are used in the commands that

* operate on individual bits, such as BSET and BCLR. A bit name followed by a dot

indicates a label that will be used to form a bit mask.

* INCLUDED FILES

INCLUDE "E:\MMDS\GR8\SSTROM\H908GR8.FRK"

* EQUATES

* PROGRAMMING TIMES IN μs

* FOLLOWING DEFINED IN .FRK FILE

*TPROG

EQU

40

;FLASH Byte Program Time

*TERASE

EQU

1000

;FLASH Page Erase Time

4000

*TMERASE

EQU

;FLASH Mass Erase Time

```

| *TNVS                                                                                                                                         | EQ                                                                                                                                            | JU               | 10                                      | ;FLASH PGM/ERASE to HVEN Setup Time                    |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------------------------|--------------------------------------------------------|--|

| *TPGS                                                                                                                                         | ΞQ                                                                                                                                            | -                |                                         | ;FLASH Program Hold Time                               |  |

| *TNVH                                                                                                                                         | ΞQ                                                                                                                                            | JU               | 5                                       | ;FLASH High-Voltage Hold Time                          |  |

| *TNVHL                                                                                                                                        |                                                                                                                                               | ~<br>2U          |                                         | ;FLASH High-Voltage Hold Time (Mass Erase)             |  |

| *TRCV                                                                                                                                         | ΞÕ                                                                                                                                            |                  |                                         | ;FLASH Return to Read Time                             |  |

|                                                                                                                                               | ~                                                                                                                                             | ~ -              |                                         |                                                        |  |

|                                                                                                                                               | * TIMES REPRESENT VALUES THAT ARE PASSED TO THE DELAY ROUTINE, WHICH * DELAYS FOR X 12 $\mu s$ FOR VALUES PASSED. FOR TERASE AND TMERASE, THE |                  |                                         |                                                        |  |

|                                                                                                                                               |                                                                                                                                               |                  | AND 20 (12 µs*17*20=4                   |                                                        |  |

|                                                                                                                                               |                                                                                                                                               |                  | BUMP OF THE COP BEFO                    | •                                                      |  |

| ECALLS                                                                                                                                        |                                                                                                                                               |                  | 5                                       |                                                        |  |

| MECALL                                                                                                                                        | ~                                                                                                                                             | -                | 20                                      |                                                        |  |

| TPROGQ                                                                                                                                        | ~                                                                                                                                             |                  |                                         | ;FLASH Program Time                                    |  |

| TERASE                                                                                                                                        | ~                                                                                                                                             |                  | 17                                      | ;FLASH Block Erase Time                                |  |

| TMERAS                                                                                                                                        |                                                                                                                                               |                  |                                         | ;FLASH Mass Erase Time                                 |  |

| TNVSQ                                                                                                                                         |                                                                                                                                               | QU               | 1                                       | ;FLASH PGM/ERASE to HVEN Setup Time                    |  |

| TPGSQ                                                                                                                                         |                                                                                                                                               | ~ -              |                                         | ;FLASH Program Hold Time                               |  |

| TNVHQ                                                                                                                                         |                                                                                                                                               | ~                |                                         | ;FLASH High-Voltage Hold Time                          |  |

| TNVHLQ                                                                                                                                        | ~                                                                                                                                             | ~                |                                         | ;FLASH High-Voltage Hold Time (Mass Erase)             |  |

| TRCVQ                                                                                                                                         | ~                                                                                                                                             | -                |                                         | ;FLASH Return to Read Time                             |  |

| INCVQ                                                                                                                                         |                                                                                                                                               | 20               | 1                                       | TEMON Recard to Read Time                              |  |

| * * * * * *                                                                                                                                   | * * * * * * * * * * *                                                                                                                         | ******           | * * * * * * * * * * * * * * * * * * * * | ***************                                        |  |

| * ROUT                                                                                                                                        | TNES                                                                                                                                          |                  |                                         |                                                        |  |

|                                                                                                                                               |                                                                                                                                               | ******           | * * * * * * * * * * * * * * * * * * * * | *****                                                  |  |

| * * * * * *                                                                                                                                   | * * * * * * * * * * *                                                                                                                         | ******           | * * * * * * * * * * * * * * * * * * * * | ***************                                        |  |

| * NAME:                                                                                                                                       | GETBYTE                                                                                                                                       |                  |                                         |                                                        |  |

|                                                                                                                                               | -                                                                                                                                             | byte of          | data on PTAO                            |                                                        |  |

|                                                                                                                                               |                                                                                                                                               |                  | t A0 configured as an                   | input.                                                 |  |

|                                                                                                                                               |                                                                                                                                               |                  | c=byte received.                        |                                                        |  |

| *                                                                                                                                             | 0011010101                                                                                                                                    |                  | —                                       | esult bad then send break and                          |  |

| *                                                                                                                                             | i                                                                                                                                             |                  | ck to start.                            |                                                        |  |

| *                                                                                                                                             |                                                                                                                                               |                  | ) configured as an inp                  |                                                        |  |

| * SUBR(                                                                                                                                       | -<br>DUTINES CAL                                                                                                                              |                  |                                         |                                                        |  |

|                                                                                                                                               | ABLES READ:                                                                                                                                   |                  |                                         |                                                        |  |

|                                                                                                                                               | ABLES MODIF:                                                                                                                                  |                  |                                         |                                                        |  |

|                                                                                                                                               | USED: 4                                                                                                                                       |                  |                                         |                                                        |  |

|                                                                                                                                               | 20 BYTES                                                                                                                                      |                  |                                         |                                                        |  |

|                                                                                                                                               |                                                                                                                                               | (ECUTED          | OUT OF ROM                              |                                                        |  |

| * DESCRIPTION: EXECUTED OUT OF ROM<br>* Attempts to receive a byte from the external controller via PortA0.                                   |                                                                                                                                               |                  |                                         |                                                        |  |

| * Once called, program will remain in GETBYTE until a byte is received                                                                        |                                                                                                                                               |                  |                                         |                                                        |  |

|                                                                                                                                               |                                                                                                                                               |                  |                                         |                                                        |  |

| * Signal to start receiving a byte is a valid (low) start bit.<br>* NOTE: Cycle path for each bit reception must be kept the same to maintain |                                                                                                                                               |                  |                                         |                                                        |  |

| * a steady baud rate.                                                                                                                         |                                                                                                                                               |                  |                                         |                                                        |  |

| * BITTIMING = 9+(17+10*23) = 256 CYCLES@2.4576 MHZ = 104 µs = 9600 BAUD                                                                       |                                                                                                                                               |                  |                                         |                                                        |  |

| **************************************                                                                                                        |                                                                                                                                               |                  |                                         |                                                        |  |

| GETBYTE:                                                                                                                                      |                                                                                                                                               |                  |                                         |                                                        |  |

|                                                                                                                                               | -                                                                                                                                             |                  | BYTE                                    | ;Waiting for start edge.                               |  |

|                                                                                                                                               | BRSET0 P                                                                                                                                      |                  |                                         |                                                        |  |

|                                                                                                                                               | BRSETO ,P<br>JSR GE                                                                                                                           |                  |                                         |                                                        |  |

|                                                                                                                                               | JSR GE                                                                                                                                        | ET_BIT           |                                         | ;try to receive a full start bit.                      |  |

|                                                                                                                                               | JSR GE<br>BCS GE                                                                                                                              | ET_BIT<br>ETBYTE |                                         | <pre>;try to receive a full start bit. ;Success?</pre> |  |