# Motorola Semiconductor Application Note

# AN1836

# FLASH Programming for Motorola MC68HC912 Microcontrollers

#### By Matt Ruff

Body Electronics and Occupant Safety Systems Engineering Austin, Texas

#### Introduction

This document outlines basic routines that demonstrate how to program and erase FLASH EEPROM on the MC68HC912 Family of microcontrollers (MCU) through the background debug mode (BDM) interface using a Motorola serial debug interface (SDIL) and the SDBUG12 software (version 2.15) from P&E Microcomputer Systems, Inc. SDBUG12 is a software interface tool to the SDIL hardware, which allows for background monitoring of the M68HC12 Family of MCUs.

Information pertaining to the proper conditioning and handling of the external voltage supply used to program the FLASH EEPROM (electrically erasable programmable read-only memory) also is included. Care must be taken to ensure proper programming and to prevent damage to the device or data corruption in the memory array.

This application note provides updated information to the engineering bulletin titled *Erasing and Programming the FLASH EEPROM on the MC68HC912B32*, Motorola document order number EB183/D, in addition to a much greater detailed description of the programming voltage supply considerations needed to design an application.

The 32 Kbytes of embedded FLASH EEPROM are a primary reason why the MC68HC912B32 device is so useful. This module serves as electrically programmable and erasable, non-volatile ROM-like memory, allowing for storage of program code which:

- Must be executed frequently

- Must be executed at high speeds

- Might need to be upgraded in the field later

The programming routines and registers referred to in this document pertain to the MC68HC912B32 device. However, the concepts covered here hold for the entire MC68HC912 FLASH MCU Family and any other Motorola microcontrollers which share this same FLASH technology (also called 1.5T FLASH EEPROM or UDR FLASH technology). Included in this list are the M68HC16 and 683xx Families. Some of the newest M68HC12 Family devices are moving to a new FLASH technology and contain an A at the end of the part number to differentiate the FLASH technology used (for instance, MC68HC912D60A).

#### FLASH EEPROM Control Block

The FLASH EEPROM is controlled by a 4-byte register block, which is located at address \$00F4 upon reset. Within this block are four single-byte registers:

- Lock control register, FEELCK

- Module configuration register, FEEMCR

- Module test register, FEETST

- Module control register, FEECTL

For more detail on these control registers, refer to **Section 8.4 FLASH EEPROM Registers** in the *MC68HC912B32 / MC68HC912BE32 Advance Information,* Motorola document order number MC68HC912B32/D. This section can be found in the appropriate documents for all M68HC12 Family MCUs. The sequence of how to use these registers is covered later in this document.

#### FLASH EEPROM Lock Control Register

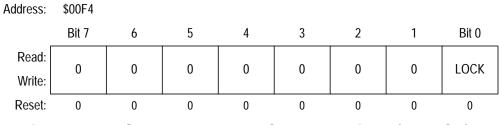

The FEELCK register (located at \$00F4) contains only the LOCK bit (bit 0), which allows or prevents writing to the FEEMCR register. This must be cleared to change the FEEMCR. Note that it is cleared out of reset.

Figure 1. FLASH EEPROM Lock Control Register (FEELCK)

#### FLASH EEPROM Module Configuration Register

The FEEMCR register (located at \$00F5) contains only the BOOTP bit (bit 0), which protects the 2-Kbyte boot block (1 Kbyte in early mask sets G86W or G75R) located at \$7800–\$7FFF. This bit must be cleared, after the FEELCK (LOCK bit) is cleared, to write or erase the boot block.

| Address:        | \$00F5 |   |   |   |   |   |   |       |

|-----------------|--------|---|---|---|---|---|---|-------|

|                 | Bit 7  | 6 | 5 | 4 | 3 | 2 | 1 | Bit 0 |

| Read:<br>Write: | 0      | 0 | 0 | 0 | 0 | 0 | 0 | BOOTP |

| Reset:          | 0      | 0 | 0 | 0 | 0 | 0 | 0 | 1     |

Figure 2. FLASH EEPROM Module Configuration Register (FEEMCR)

#### FLASH EEPROM Module Test Register

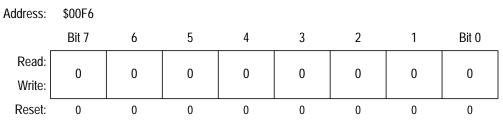

The FEETST register (located at \$00F6) has no effect and always reads 0 in normal modes of operation.

Figure 3. FLASH EEPROM Module Test Register (FEETST)

# FLASH EEPROM Control Register

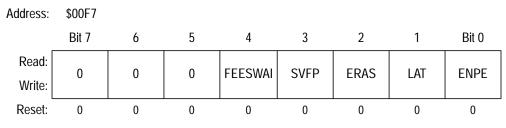

The FEECTL register (located at \$00F7) controls the actual programming and erasing of the FLASH EEPROM. In this register, five bits are used to control the FLASH. All bits are 0 upon reset.

#### Figure 4. FLASH EEPROM Control Register (FEECTL)

#### FEESWAI

FEESWAI (bit 4) controls the behavior of the FLASH EEPROM clock while in wait mode.

#### SVFP

SVFP (bit 3), the V<sub>FP</sub> status bit, is set when V<sub>FP</sub> is near normal programming voltage levels; clear otherwise (read only). This is not a guarantee that V<sub>FP</sub> is within specified tolerances and should be used only as a secondary check.

#### ERAS

ERAS (bit 2), when set, configures the array for erasure.

#### LAT

LAT (bit 1), when set, enables the programming latches.

#### ENPE

ENPE (bit 0), when set, applies the programming/erase voltage to the array.

#### Hardware Configuration

Setting Up the Debugging Hardware Since programming the FLASH EEPROM takes a finite amount of time and is dependent on a reliable programming voltage from an exterior source, it is difficult to tell if the procedure worked immediately. Also, it should be verified by some sort of external signal. To simplify the debugging of the process, try using a few hardware techniques that are listed in this application note.

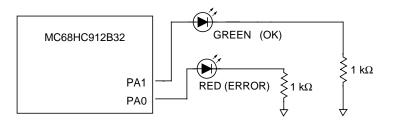

For debugging hardware, simply use light-emitting diodes (LED), connected to port pins on the MC68HC912B32 device to use as error and sequence successfully complete indicators. For use with the code listed here, connect a red LED to PA0, with a 1-k $\Omega$  current limiting resistor to indicate errors. In like manner, connect a green LED to PA1 to indicate that the process has completed successfully. Refer to Figure 5 for connections.

Figure 5. Debugging Hardware Connections

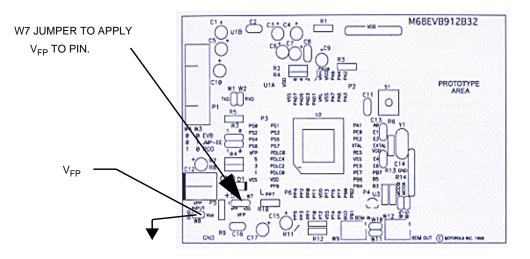

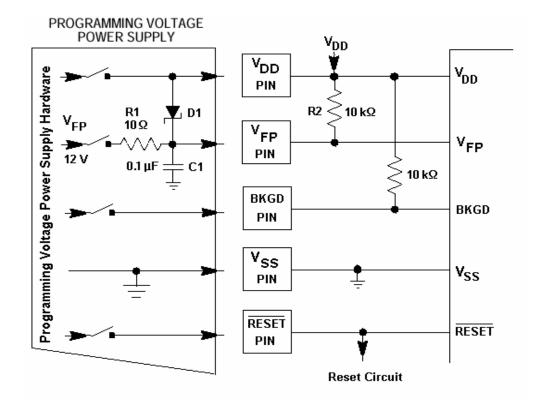

Setting Up the Be sure to connect the programming voltage (V<sub>FP</sub>) source to W8 on the M68HC12B32EVB M68HC12B32EVB with the proper polarity. W8 allows V<sub>FP</sub> to be connected to the board, but the jumper on W7 actually transfers V<sub>FP</sub> to the V<sub>FP</sub> pin (pin 69) on the microcontroller. The default location of W7 applies V<sub>DD</sub> to the V<sub>FP</sub> pin, and a jumper should always be located here to maintain the voltage on the V<sub>FP</sub> pin when programming and erasing are not occurring. See Figure 6 for the locations of W7 and W8.

Refer to the *Evaluation Board User's Manual*, which comes with the M68HC12 evaluation board, Motorola part order number M68EVB912B32, for detailed connection information.

Figure 6. M68EVB912B32 Evaluation Board Connections

The M68HC12B32EVB is designed to be used for evaluation purposes only and does not have sufficient protection against improper  $V_{FP}$ voltage levels for a production level system. Refer to **Example V<sub>FP</sub> Protection Circuitry** in this document for more detailed circuit information for proper circuit design and protection of the V<sub>FP</sub> pin and FLASH EEPROM in the MCU.

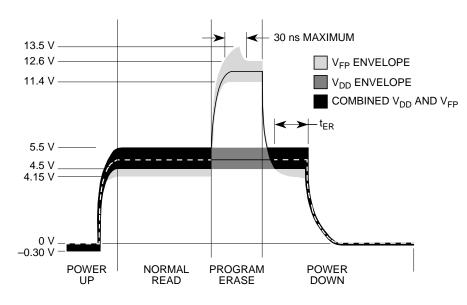

**NOTE:** V<sub>FP</sub> should be 11.4–11.8 volts for mask sets 1H91F and 3H91F. For all other masks, use 11.4–12.6 volts (12 volts ±5%).

#### **Software Considerations**

Using SDBUG12 to manipulate the FLASH EEPROM requires some special considerations. First, a few bugs in some versions of the software can cause confusion when manipulating the FLASH memory array. The memory display windows sometimes do not refresh properly, sometimes showing all of the odd addresses as one value and all the even addresses as another value. To fix this problem, issue a **RESET** command from the SDBUG12 command prompt to force SDBUG12 to refresh all of its display windows from the MCU once the part comes out of reset.

The routines that follow were tested with version 2.15 of SDBUG12 running on a Windows NT<sup>®</sup> workstation in a DOS window. The problem described in the preceding paragraph did not appear when executing these routines. SDBUG12 displayed the proper values for the FLASH array when the routines were allowed to run to completion. Both of the code segments included here can be loaded into the RAM of the part at the same time since they do not overlap. Use the **LOAD** command in SDBUG12 to load each segment into RAM. Notice that the entry point of the program routine is \$80A and the entry point of the erase routine is \$90A. Once loaded into RAM, the command **G 80A** will begin the programming process or **G 90A** will begin the erase process.

For a detailed description of the software commands for SDBUG12, refer to documentation from P&E Microcomputer Systems, Inc.

**NOTE:** Once the FLASH array has been erased or programmed, reloading the DBUG12 monitor code into the FLASH array is necessary if that monitor is to be used, as manipulation of the array will have destroyed this code. This can be accomplished with the bootloader in the boot block of the part or by using a software programming tool, such as Prog12s, which is a product of P&E Microcomputer Systems, Inc.

If using the M68EVB912B32 evaluation board, refer to the *Evaluation Board User's Manual*, which comes with the evaluation board, for further information on how to reload the monitor program into the device using the on-board bootloader.

General Notes<br/>on Coding FLASHThe routines used in this application note are designed for reference<br/>purposes. Programming and erase routines always should be<br/>downloaded to the device at the time of programming through the BDM<br/>or through a CAN, J1850, or other communication link. The code for<br/>these algorithms should not be resident on the device during normal<br/>operations.

One reason for not including these routines in FLASH or EEPROM is to prevent possible activation in a code runaway situation. If the code gets

<sup>&</sup>lt;sup>®</sup> Windows NT is a registered trademark of Microsoft in the U.S. and other countries.

"lost," it is possible that the programming voltage could be applied to the array for a time much longer than the specifications allow, resulting in corruption of data. Obviously, implementing FLASH-modifying code, such as bootloaders stored in FLASH, could result in such a case if the microcontroller were to get lost and start executing code at a random point.

**NOTE:** In cases such as this, great care must be taken to test all of the code to make certain that FLASH modification routines cannot be activated accidentally.

If these routines must be located in non-volatile memory (NVM), other ways to safeguard against code runaway are possible. For instance, if assembly opcodes are interlaced with software interrupt (SWI) instructions, splitting up the instruction which modifies the FEECTL register to apply the programming voltage to the array prevents accidental modification of that register. To actually run the code, that section of code in RAM would need to be reconstructed by copying the bytes from their interlaced location in NVM using a message from the CAN, J1850, SCI, etc., which contains the decryption key for the locations of the scrambled opcodes. The SWI instructions are not essential, but would ensure that the device would execute an SWI if the code were lost in this region, alerting the engineer to a possible dangerous condition. This concept is complicated and is beyond the scope of this application note. It is mentioned here only to offer one possible alternative to avoid accidental activation of program or erase routines.

The other major reason to simply leave the program and erase routines out of the NVM is in the interest of software reuse. As newer devices are developed and newer FLASH technologies emerge, the algorithms for programming and erasing these routines also are being refined. If the algorithms themselves are downloaded dynamically to the target devices at the time of programming, the newest algorithms can be utilized with little impact to the target system. This allows the target system software to remain FLASH technology independent, minimizing engineering time required for code development and testing.

# Programming the FLASH Array

Programming the FLASH EEPROM is accomplished by this step-bystep procedure. The  $V_{FP}$  pin voltage must be at the proper level prior to executing step 4 the first time.

- 1. Apply program/erase voltage to the  $V_{FP}$  pin.

- 2. Clear ERAS and set the LAT bit in the FEECTL register to establish program mode and enable programming address and data latches.

- Write data to a valid address. The address and data are latched. If BOOTP is asserted, an attempt to program an address in the boot block will be ignored.

- 4. Apply programming voltage by setting ENPE.

- 5. Delay for one programming pulse, t<sub>PPULSE</sub>.

- 6. Remove programming voltage by clearing ENPE.

- 7. Delay while high voltage is turning off, t<sub>VPROG</sub>.

- 8. Read the address location to verify that it has been programmed.

- If the location is not programmed, repeat steps 4 through 7 until the location is programmed or until the specified maximum number of program pulses, n<sub>PP</sub>, has been reached.

- 10. If the location is programmed, repeat the same number of pulses as required to program the location. This provides 100 percent program margin.

- 11. Read the address location to verify that it remains programmed.

- 12. Clear LAT.

- 13. If there are more locations to program, repeat steps 2 through 10.

- 14. Turn off  $V_{FP}$ . Reduce voltage on  $V_{FP}$  pin to  $V_{DD}$ .

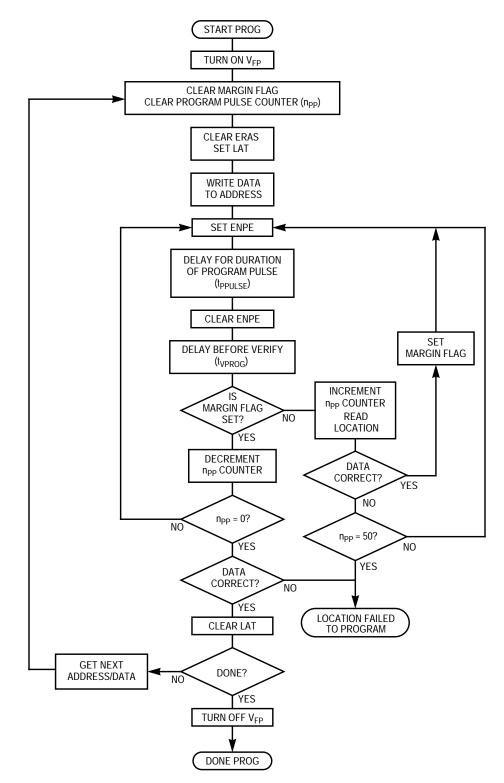

The flowchart in **Figure 7** demonstrates the recommended programming sequence.

Figure 7. Programming Sequence Flowchart

The following code segment adheres to the recommended procedure for programming the FLASH array. The flowchart in **Figure 7** outlines this same procedure. The general idea is to set the programming latches, write the desired byte/word to the location in the array, apply the programming voltage to the FLASH module within the chip (by setting the ENPE bit), then to make sure the location is programmed properly. If the data is correct, then the number of times the programming voltage was applied to get this byte programmed will have been preserved in the N<sub>PP</sub> variable. The programming voltage is then pulsed that many times again to ensure that the byte/word remains programmed. This is a 100 percent programming margin. This whole process is repeated for each byte/word to be programmed. The next code segment simply copies a string of characters from RAM and stores it at the beginning of the FLASH array.

The source code for this application note is available on Motorola's Web site at http://www.motorola.com/sps.

**NOTE:** In the following code, the STEP comments refer to the steps shown at the beginning of this section. Some steps in the code do not correspond directly to the programming algorithm, but are included simply to provide output to the indicator LEDs to show the user the status of the program.

```

;--- Application Note Source Code for AN1836 ---

Erasing and Programming the FLASH ---

;---

;---

EEPROM on the MC68HC912B32

___

; - - -

_ _ _

;--- FLASH EEPROM program routine

___

;--- MC68HC912B32 1.5T FLASH Module

_ _ _

_ _ _

; - - -

;--- Rev. 1.2 February 9, 2000

Created Bit Name Labels for easier reading---

Streamlined Code for efficiency ---

; - - -

; - - -

;--- Rev. 1.0 - April 23,1998

___

;--- Fixed Tppulse = 25us and Tvprog = 10us

___

;--- Written November 6, 1997

___

; - - -

____

ASSEMBLER:

IASM12 v. 3.06

; _ _ _

___

; - - -

P & E Microcomputer Systems---

;---

_ _ _

;--- by Matt Ruff, BE/OS Systems Engineering

_ _ _

; - - -

____

;--- This code is intended for instructional use ---

;--- only. Motorola assumes no liability for use ---

;--- or modification of this code. It is the

___

;--- responsibility of the user to verify all

___

;--- parameters, variables, timings, etc.

_ _ _

; ---

___

```

#### AN1836

# **Application Note**

;-----

\$BASE 10T

;Set assembler default base to base 10

| ;                                                                                                        |            |                                                                                            | Equates -                                                                                                       |                                                                                                                                                                                                                                                                                          |

|----------------------------------------------------------------------------------------------------------|------------|--------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FEEStart:                                                                                                | EQU        | \$8000                                                                                     |                                                                                                                 | ;FLASH Start address                                                                                                                                                                                                                                                                     |

| FEEEnd:                                                                                                  | EQU        | \$FFFF                                                                                     |                                                                                                                 | ;FLASH End address                                                                                                                                                                                                                                                                       |

| FEESize:                                                                                                 | EQU        | \$8000                                                                                     |                                                                                                                 |                                                                                                                                                                                                                                                                                          |

| FEEWords:                                                                                                | EQU        | {FEESi                                                                                     | _ze/2}                                                                                                          | ;Num of words is number of bytes divided by two                                                                                                                                                                                                                                          |

| MaxNpp:                                                                                                  | EQU        | 50                                                                                         | ,                                                                                                               | ;50 pulses maximum                                                                                                                                                                                                                                                                       |

|                                                                                                          |            |                                                                                            |                                                                                                                 | -                                                                                                                                                                                                                                                                                        |

| FEELCK:                                                                                                  | EQU        | \$F4                                                                                       |                                                                                                                 | ;FLASH Lock Control Register                                                                                                                                                                                                                                                             |

| FEEMCR:                                                                                                  | EQU        | \$F5                                                                                       |                                                                                                                 | ;FLASH Module Configuration Register                                                                                                                                                                                                                                                     |

| FEECTL:                                                                                                  | EQU        | \$F7                                                                                       |                                                                                                                 | ;FLASH Control Register                                                                                                                                                                                                                                                                  |

| LOCK:                                                                                                    | EQU        | \$01                                                                                       |                                                                                                                 | ;Lock register Bit in FEELCK                                                                                                                                                                                                                                                             |

| BOOTP:                                                                                                   | EQU        | \$01                                                                                       |                                                                                                                 | ;Boot Protect Bit in FEEMCR                                                                                                                                                                                                                                                              |

| SVFP:                                                                                                    | EQU        | \$08                                                                                       |                                                                                                                 | ;Status Vfp Voltage Bit in FEECTL                                                                                                                                                                                                                                                        |

| ERAS:                                                                                                    | EQU        | \$04                                                                                       |                                                                                                                 | ;Erase Control Bit in FEECTL                                                                                                                                                                                                                                                             |

| LAT:                                                                                                     | EQU        | \$02                                                                                       |                                                                                                                 | ;Programming Latch Control bit in FEECTL                                                                                                                                                                                                                                                 |

| ENPE:                                                                                                    | EQU        | \$01                                                                                       |                                                                                                                 | ;Enable Program/Erase Voltage Bit in FEECTL                                                                                                                                                                                                                                              |

|                                                                                                          | ~          |                                                                                            |                                                                                                                 |                                                                                                                                                                                                                                                                                          |

| PORTA:                                                                                                   | EQU        | \$0000                                                                                     |                                                                                                                 | ;Port A data register                                                                                                                                                                                                                                                                    |

| DDRA:                                                                                                    | EQU        | \$0002                                                                                     |                                                                                                                 | ;Port A data direction register                                                                                                                                                                                                                                                          |

| PA0on:                                                                                                   | EQU        | \$01                                                                                       |                                                                                                                 | -                                                                                                                                                                                                                                                                                        |

| PAlon:                                                                                                   | EQU        | \$02                                                                                       |                                                                                                                 |                                                                                                                                                                                                                                                                                          |

|                                                                                                          |            |                                                                                            |                                                                                                                 |                                                                                                                                                                                                                                                                                          |

| Mult:                                                                                                    | EQU        | 1000                                                                                       |                                                                                                                 | ;Multiplier for EClock, assembler won't do                                                                                                                                                                                                                                               |

|                                                                                                          |            |                                                                                            |                                                                                                                 | ; values over 2^16                                                                                                                                                                                                                                                                       |

| EClock:                                                                                                  | EQU        | {Mult*                                                                                     | 8000}                                                                                                           | ;E-clock frequency in Hz.                                                                                                                                                                                                                                                                |

|                                                                                                          |            | •                                                                                          |                                                                                                                 |                                                                                                                                                                                                                                                                                          |

|                                                                                                          |            |                                                                                            |                                                                                                                 |                                                                                                                                                                                                                                                                                          |

| mS1LoopTime:                                                                                             | EQU        | 4                                                                                          |                                                                                                                 | ;Num of clock cycles per loop.                                                                                                                                                                                                                                                           |

| mS1LoopTime:<br>mS1Delay:                                                                                | EQU<br>EQU |                                                                                            | k/(mS1LoopTime                                                                                                  | ;Num of clock cycles per loop.<br>e*1000)};Must surround expression w/{()}                                                                                                                                                                                                               |

| -                                                                                                        |            |                                                                                            | k/(mS1LoopTime                                                                                                  |                                                                                                                                                                                                                                                                                          |

| -                                                                                                        |            |                                                                                            | k∕(mS1LoopTime                                                                                                  | e*1000)};Must surround expression w/{()}                                                                                                                                                                                                                                                 |

| -                                                                                                        | EQU        | {ECloc                                                                                     |                                                                                                                 | e*1000)};Must surround expression w/{()}<br>; for P&E.                                                                                                                                                                                                                                   |

| mSlDelay:                                                                                                | EQU        | {ECloc                                                                                     |                                                                                                                 | e*1000)};Must surround expression w/{()}<br>; for P&E.<br>;Factor of 1000 used for base time of 1 ms.                                                                                                                                                                                    |

| mSlDelay:                                                                                                | EQU        | {ECloc                                                                                     |                                                                                                                 | e*1000)};Must surround expression w/{()}<br>; for P&E.<br>;Factor of 1000 used for base time of 1 ms.                                                                                                                                                                                    |

| mSlDelay:                                                                                                | EQU        | {ECloc                                                                                     | Equates                                                                                                         | e*1000)};Must surround expression w/{()}<br>; for P&E.<br>;Factor of 1000 used for base time of 1 ms.                                                                                                                                                                                    |

| mS1Delay:                                                                                                | EQU        | {ECloc                                                                                     | Equates                                                                                                         | e*1000)};Must surround expression w/{()}<br>; for P&E.<br>;Factor of 1000 used for base time of 1 ms.                                                                                                                                                                                    |

| mSlDelay:<br>;<br>Npp:                                                                                   | EQU<br>DS  | {ECloc<br><br>ORG<br>1                                                                     | Equates                                                                                                         | <pre>e*1000)};Must surround expression w/{()} ; for P&amp;E. ;Factor of 1000 used for base time of 1 ms</pre>                                                                                                                                                                            |

| mSlDelay:<br>;<br>Npp:                                                                                   | EQU<br>DS  | {ECloc<br><br>ORG<br>1                                                                     | Equates                                                                                                         | <pre>e*1000)};Must surround expression w/{()} ; for P&amp;E. ;Factor of 1000 used for base time of 1 ms</pre>                                                                                                                                                                            |

| mSlDelay:<br>;<br>Npp:                                                                                   | EQU<br>DS  | {ECloc<br>ORG<br>1<br>1                                                                    | Equates<br>\$0800                                                                                               | <pre>e*1000)};Must surround expression w/{()} ; for P&amp;E. ;Factor of 1000 used for base time of 1 ms</pre>                                                                                                                                                                            |

| mSlDelay:<br>;<br>Npp:<br>MarginFlag:                                                                    | EQU<br>DS  | {ECloc<br>ORG<br>1<br>1                                                                    | Equates<br>\$0800                                                                                               | <pre>e*1000)};Must surround expression w/{()} ; for P&amp;E. ;Factor of 1000 used for base time of 1 ms</pre>                                                                                                                                                                            |

| mSlDelay:<br>;<br>Npp:<br>MarginFlag:                                                                    | EQU<br>DS  | {ECloc<br>ORG<br>1<br>1<br>ORG<br>LDS                                                      | Equates<br>\$0800<br>\$80A<br>#\$B00                                                                            | <pre>e*1000)};Must surround expression w/{()} ; for P&amp;E. ;Factor of 1000 used for base time of 1 ms</pre>                                                                                                                                                                            |

| mSlDelay:<br>;<br>Npp:<br>MarginFlag:                                                                    | EQU<br>DS  | {ECloc<br>ORG<br>1<br>1<br>ORG<br>LDS                                                      | Equates<br>\$0800<br>\$80A<br>#\$B00                                                                            | <pre>e*1000)};Must surround expression w/{()} ; for P&amp;E. ;Factor of 1000 used for base time of 1 ms</pre>                                                                                                                                                                            |

| mSlDelay:<br>;<br>Npp:<br>MarginFlag:                                                                    | EQU<br>DS  | {ECloc<br>ORG<br>1<br>1<br>ORG<br>LDS<br>BRCLR                                             | Equates<br>\$0800<br>\$80A<br>#\$B00<br>FEECTL,\$08,Er                                                          | <pre>e*1000)};Must surround expression w/{()} ; for P&amp;E. ;Factor of 1000 used for base time of 1 ms</pre>                                                                                                                                                                            |

| mSlDelay:<br>;<br>Npp:<br>MarginFlag:<br>Start:                                                          | EQU<br>DS  | {ECloc<br>ORG<br>1<br>1<br>ORG<br>LDS<br>BRCLR<br>LDX<br>CLR                               | Equates<br>\$0800<br>\$80A<br>#\$B00<br>FEECTL,\$08,Er<br>#\$0000<br>Npp                                        | <pre>e*1000)};Must surround expression w/{()} ; for P&amp;E. ;Factor of 1000 used for base time of 1 ms. ;Number of programming pulses applied ;Programming margin flag ;(Turn on your Vfp power supply to board) cror;If Vfp not present, output an error ;Clear number of pulses</pre> |

| mSlDelay:<br>;<br>Npp:<br>MarginFlag:<br>Start:<br>Loop:                                                 | EQU<br>DS  | {ECloc<br>ORG<br>1<br>1<br>ORG<br>LDS<br>BRCLR<br>LDX                                      | Equates<br>\$0800<br>\$80A<br>#\$B00<br>FEECTL,\$08,Er<br>#\$0000                                               | <pre>e*1000)};Must surround expression w/{()} ; for P&amp;E. ;Factor of 1000 used for base time of 1 ms</pre>                                                                                                                                                                            |

| mSlDelay:<br>;<br>Npp:<br>MarginFlag:<br>Start:                                                          | EQU<br>DS  | {ECloc<br>ORG<br>1<br>1<br>ORG<br>LDS<br>BRCLR<br>LDX<br>CLR                               | Equates<br>\$0800<br>\$80A<br>#\$B00<br>FEECTL,\$08,Er<br>#\$0000<br>Npp                                        | <pre>e*1000)};Must surround expression w/{()} ; for P&amp;E. ;Factor of 1000 used for base time of 1 ms</pre>                                                                                                                                                                            |

| mSlDelay:<br>;<br>Npp:<br>MarginFlag:<br>Start:<br>Loop:                                                 | EQU<br>DS  | {ECloc<br>ORG<br>1<br>1<br>ORG<br>LDS<br>BRCLR<br>LDX<br>CLR<br>CLR<br>MOVB                | Equates<br>\$0800<br>\$80A<br>#\$B00<br>FEECTL,\$08,Er<br>#\$0000<br>Npp<br>MarginFlag<br>#LAT,FEECTL           | <pre>e*1000)};Must surround expression w/{()} ; for P&amp;E. ;Factor of 1000 used for base time of 1 ms. ;Number of programming pulses applied ;Programming margin flag ;(Turn on your Vfp power supply to board) cror;If Vfp not present, output an error ;Clear number of pulses</pre> |

| mSlDelay:<br>;<br>Npp:<br>MarginFlag:<br>Start:<br>Loop:<br>;- Step 2 -                                  | EQU<br>DS  | {ECloc<br>ORG<br>1<br>1<br>ORG<br>LDS<br>BRCLR<br>LDX<br>CLR<br>CLR                        | Equates<br>\$0800<br>\$80A<br>#\$B00<br>FEECTL,\$08,Er<br>#\$0000<br>Npp<br>MarginFlag                          | <pre>e*1000)};Must surround expression w/{()} ; for P&amp;E. ;Factor of 1000 used for base time of 1 ms</pre>                                                                                                                                                                            |

| mSlDelay:<br>;<br>Npp:<br>MarginFlag:<br>Start:<br>Loop:                                                 | EQU<br>DS  | {ECloc<br>ORG<br>1<br>1<br>ORG<br>LDS<br>BRCLR<br>LDX<br>CLR<br>CLR<br>CLR<br>MOVB<br>LDAB | Equates<br>\$0800<br>\$80A<br>#\$B00<br>FEECTL,\$08,Er<br>#\$0000<br>Npp<br>MarginFlag<br>#LAT,FEECTL<br>DATA,X | <pre>e*1000)};Must surround expression w/{()} ; for P&amp;E. ;Factor of 1000 used for base time of 1 ms</pre>                                                                                                                                                                            |

| <pre>mS1Delay:<br/>;<br/>Npp:<br/>MarginFlag:<br/>Start:<br/>Loop:<br/>;- Step 2 -<br/>;- Step 3 -</pre> | EQU<br>DS  | {ECloc<br>ORG<br>1<br>1<br>ORG<br>LDS<br>BRCLR<br>LDX<br>CLR<br>CLR<br>MOVB                | Equates<br>\$0800<br>\$80A<br>#\$B00<br>FEECTL,\$08,Er<br>#\$0000<br>Npp<br>MarginFlag<br>#LAT,FEECTL           | <pre>e*1000)};Must surround expression w/{()} ; for P&amp;E. ;Factor of 1000 used for base time of 1 ms</pre>                                                                                                                                                                            |

| mSlDelay:<br>;<br>Npp:<br>MarginFlag:<br>Start:<br>Loop:<br>;- Step 2 -                                  | EQU<br>DS  | {ECloc<br>ORG<br>1<br>1<br>ORG<br>LDS<br>BRCLR<br>LDX<br>CLR<br>CLR<br>CLR<br>MOVB<br>LDAB | Equates<br>\$0800<br>\$80A<br>#\$B00<br>FEECTL,\$08,Er<br>#\$0000<br>Npp<br>MarginFlag<br>#LAT,FEECTL<br>DATA,X | <pre>e*1000)};Must surround expression w/{()} ; for P&amp;E. ;Factor of 1000 used for base time of 1 ms</pre>                                                                                                                                                                            |

| <pre>mS1Delay:<br/>;<br/>Npp:<br/>MarginFlag:<br/>Start:<br/>Loop:<br/>;- Step 2 -<br/>;- Step 3 -</pre> | EQU<br>DS  | {ECloc<br>ORG<br>1<br>1<br>ORG<br>LDS<br>BRCLR<br>LDX<br>CLR<br>CLR<br>CLR<br>MOVB<br>LDAB | Equates<br>\$0800<br>\$80A<br>#\$B00<br>FEECTL,\$08,Er<br>#\$0000<br>Npp<br>MarginFlag<br>#LAT,FEECTL<br>DATA,X | <pre>e*1000)};Must surround expression w/{()} ; for P&amp;E. ;Factor of 1000 used for base time of 1 ms</pre>                                                                                                                                                                            |

|                 | BSET  | FEECTL, ENPE      | ;Apply programming voltage (Set ENPE)             |

|-----------------|-------|-------------------|---------------------------------------------------|

| ;- Step 5 -     | JSR   | dly 22us          | ;Delay time for prog pulse (Tppulse)              |

| ;- Step 6 -     | 0 DIC |                   | , being eine for prog puble (ippuble)             |

| · Ohen 7        | BCLR  | FEECTL, ENPE      | ;Remove programming voltage (Clear ENPE)          |

| ;- Step 7 -     | JSR   | dly_10us          | ;Delay for high voltage turn off (Tvprog)         |

|                 | TST   | MarginFlag        | ;Is MarginFlag set??                              |

|                 | BEQ   | NoFlag            | ;If not, go bump counter and check data           |

| YesFlag:        | DEC   | Npp               | ;Decrement Npp                                    |

|                 | TST   | Npp               | ; Is Npp=0?                                       |

|                 | BNE   | STEP4             | ; If not, go to Step 4                            |

| ;- Step 9 -     |       |                   |                                                   |

|                 | LDAA  | FEEStart,X        | Read FEEPROM location to verify programming       |

|                 | CMPA  | DATA,X            | ; Is it the same as the byte to be programmed?    |

| ;- Step 10 -    | BNE   | Error             | ;Programming failed, output an error              |

| , 2005-10       | BCLR  | FEECTL,LAT        | ;Clear LAT in FEECTL                              |

|                 | INX   |                   |                                                   |

|                 | CMPA  | #\$00             | ;Check for \$00 delimiter character               |

|                 | BNE   | Loop              | ;If not, go back to start!                        |

| N-DI            | BRA   | Done              | ;If so, quit.                                     |

| NoFlag:         | INC   | Npp               | ;Increment number of prog pulses applied          |

|                 | LDAA  |                   | Read FEEPROM location to verify programming       |

|                 | CMPA  | DATA,X            | ; Is it the same as the byte to be programmed?    |

|                 | BEQ   |                   | ;If so, set the margin flag                       |

|                 | LDAB  | Npp               |                                                   |

|                 | CMPB  | #MAXNpp           | ;Have we applied max number of pulses?            |

|                 | BLS   | STEP4             | ; If not, continue programming                    |

| SetMarginFlag:  | BSR   | Error             | ; If so, we have a problem                        |

| SecMargini iag. | INC   | MarginFlag        | ;Set MarginFlag                                   |

|                 | BRA   | STEP4             |                                                   |

| Done:           |       |                   |                                                   |

|                 | CLR   | PORTA             | ;Clear Port A                                     |

|                 | MOVB  | #\$FF,DDRA        | ;Set DDRA to outputs                              |

|                 | MOVB  | #PA1on,PORTA<br>* | ;Turn on PA1 to indicate complete                 |

|                 | BRA   |                   | ;(Turn off Vfp supply - programming complete)     |

|                 |       |                   |                                                   |

| ;               |       |                   |                                                   |

| ;               |       | ror Subroutine    |                                                   |

| ;<br>Error:     |       |                   |                                                   |

| EII0I.          | CLR   | PORTA             | ;Clear Port A                                     |

|                 | MOVB  |                   | ;Set DDRA to outputs                              |

| Blink:          |       |                   |                                                   |

|                 | MOVB  |                   | ;Turn PAO on for error output                     |

|                 | BSR   | dly_500ms         | ;Delay so blinking is visible (1/2 second between |

|                 | MOVB  | #\$00,PORTA       | ; flashes)<br>;Turn PAO off                       |

|                 | BSR   | dly_500ms         | TULII FAU ULL                                     |

|                 | BRA   | Blink             | Repeat ad nauseam                                 |

|                 |       |                   | -                                                 |

AN1836

### **Application Note**

;----- Delay Subroutines -----dly\_500ms: LDD #500 ;Delay for 500 ms BSR DelaymS RTS ;-----; - - -Millisecond Delay Routine ; ---\_\_\_ ;---Call with the number of ms to delay in the D accumulator. \_\_\_ The delay is not exact, but close enough when delaying ms. ; - - ----DelaymS: DlyLoop1mS: LDX #mS1Delay ;Load 1ms delay count into X DlyLoop: NOP ;Decrement count DBNE X,DlyLoop ;Loop until done. DBNE D,DlyLoop1mS RTS ; ---Microsecond Delay Routines (8MHz e clock) \_\_\_ ; ---\_\_\_ ;--- To reduce loop overhead, the following routines have been \_\_\_ ;--- optimized by counting cycle time and calculating the delay \_\_\_ ;--- based on an 8MHz system clock. \_\_\_ ; Delay for about 22-23us dly\_22us: ; JSR or BSR is 4 cycles ; Total delay is  $\{4+2+(loopcount*3)+5\}*125ns$ ; For a loopcount of 52 yields 20.875us LDD #52 ; -2 cyclesd\_22u: DBNE D,d\_22u ; -3 cycles-RTS ; -5 cycles-; Delay for about 10us dly\_10us: ; JSR or BSR is 4 cycles ; Total delay is {4+2+(loopcount\*3)+5}\*125ns ; For a loopcount of 24 yields 10.375us #24 LDD ; -2 cyclesd\_10u: DBNE D,d\_10u ; -3 cycles-; -5 cycles-RTS DATA FCB "Motorola Microcontrollers" FCB \$00 END

#### Erasing the FLASH Array

This sequence demonstrates the recommended procedure for erasing the FLASH EEPROM. The  $V_{FP}$  pin voltage must be at the proper level prior to executing step 4 the first time.

- 1. Turn on  $V_{FP}$ . Apply program/erase voltage to the  $V_{FP}$  pin.

- 2. Set the LAT bit and ERAS bit to configure the FLASH EEPROM for erasing.

- 3. Write to any valid address in the FLASH array. This allows the erase voltage to be turned on; the data written and the address written are not important. The boot block will be erased only if the control bit BOOTP is negated.

- 4. Apply erase voltage by setting ENPE.

- 5. Delay for a single erase pulse, t<sub>EPULSE</sub>.

- 6. Remove erase voltage by clearing ENPE.

- 7. Delay while high voltage is turning off, t<sub>VERASE</sub>.

- 8. Read the entire array to ensure that the FLASH EEPROM is erased.

- If all of the FLASH EEPROM locations are not erased, repeat steps 4 through 7 until either the remaining locations are erased or until the maximum erase pulses have been applied, n<sub>EP</sub>.

- 10. If all of the FLASH EEPROM locations are erased, repeat the same number of pulses as required to erase the array. This provides 100 percent erase margin.

- 11. Read the entire array to ensure that the FLASH EEPROM is erased.

- 12. Clear LAT.

- 13. Turn off  $V_{FP}$ . Reduce voltage on  $V_{FP}$  pin to  $V_{DD}$ .

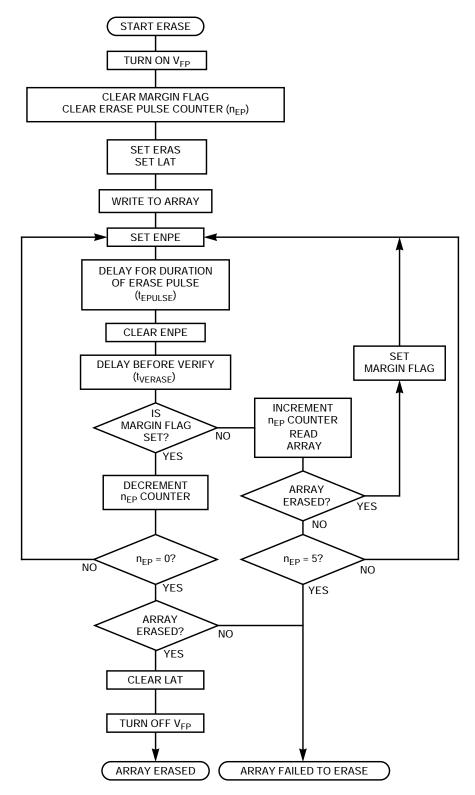

The flowchart in **Figure 8** demonstrates the recommended erase sequence.

Figure 8. Erasing Sequence Flowchart

This code segment follows the recommended procedure for erasing the FLASH array. The flowchart in **Figure 8** outlines this same procedure. The general idea is to set the erase flag, write to any location in the array, apply the erase voltage to the FLASH module within the chip (by setting the ENPE bit), then to make sure the entire array is erased. If the whole array is erased, then the number of times the erase voltage was applied to get this erasure will have been preserved in the Nep variable. The erase voltage is then pulsed that many times again to ensure that the array remains erased. This is a 100 percent erase margin.

The source code for this application note is available on Motorola's Web site at http://www.motorola.com/sps.

**NOTE:** In the following code, the STEP comments refer to the steps shown at the beginning of this section. Some steps in the code do not correspond directly to the erasing algorithm but are included simply to provide output to the indicator LEDs to show the user the status of the program.

```

;______

; - - -

Application Note Source Code for AN1836

Erasing and Programming the FLASH

; - - -

EEPROM on the MC68HC912B32

_ _ _

; - - -

; - - -

_ _ _

;--- FLASH EEPROM erase routine

_ _ _

;--- MC68HC912B32 1.5T FLASH Module

_ _ _

; - - -

;--- Rev. 1.2 February 9, 2000

Fixed bug in ReadArray routine

; - - -

_ _ _

Created Bit Name Labels for easier reading ---

; - - -

Streamlined Code for efficiency

___

;---

;--- Rev. 1.1 January 11, 2000

___

Changed to 10ms delay for tepulse

; - - -

to match specification change

; - - -

;--- Rev. 1.0 April 16, 1998

___

Changed to 100ms delay for tepulse

; - - -

_ _ _

;--- Written November 6, 1997

_ _ _

;---

_ _ _

;--- ASSEMBLER:

IASM12 v. 3.06

; - - -

P & E Microcomputer Systems ---

; - - -

_ _ _

_ _ _

;--- by Matt Ruff, BE/OS Systems Engineering

;---

_ _ _

;--- This code is intended for instructional use

_ _ _

;--- only. Motorola assumes no liability for use

;--- or modification of this code. It is the

;--- responsibility of the user to verify all

_ _ _

;--- parameters, variables, timings, etc.

_ _ _

; - - -

_ _ _

```

#### AN1836

\$BASE 10T

;Set the assembler default base to base 10

| ;                                                                                         |          |                                                                          | Equates                                                                                                |                                                                                                                                                                                                                                                                                                |

|-------------------------------------------------------------------------------------------|----------|--------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FEEStart:                                                                                 | EQU      | \$8000                                                                   | - 1                                                                                                    | ;FLASH Start address                                                                                                                                                                                                                                                                           |

| FEEEnd:                                                                                   | EQU      | \$FFFF                                                                   |                                                                                                        | ;FLASH End address                                                                                                                                                                                                                                                                             |

| FEESize:                                                                                  | EQU      | \$8000                                                                   |                                                                                                        |                                                                                                                                                                                                                                                                                                |

| FEEWords:                                                                                 | EQU      | {FEESi                                                                   | ze/2}                                                                                                  | ;Num of words is number of bytes divided by                                                                                                                                                                                                                                                    |

|                                                                                           | ~ -      | (                                                                        | - , ,                                                                                                  | ; two                                                                                                                                                                                                                                                                                          |

| BootBlkSize:                                                                              | EQU      | 2048                                                                     |                                                                                                        | ;Size of the boot block                                                                                                                                                                                                                                                                        |

| BCFEEWords:                                                                               | EQU      | {(FEES                                                                   | Size-BootBlkSize)/2                                                                                    | 2};Num of words to blank check use {()}for P&E.                                                                                                                                                                                                                                                |

| MaxNep:                                                                                   | EQU      | 5                                                                        |                                                                                                        | ;5 pulses maximum                                                                                                                                                                                                                                                                              |

|                                                                                           | ~ -      |                                                                          |                                                                                                        |                                                                                                                                                                                                                                                                                                |

| FEELCK:                                                                                   | EQU      | \$F4                                                                     |                                                                                                        | ;FLASH Lock Control Register                                                                                                                                                                                                                                                                   |

| FEEMCR:                                                                                   | EQU      | \$F5                                                                     |                                                                                                        | ;FLASH Module Configuration Register                                                                                                                                                                                                                                                           |

| FEECTL:                                                                                   | EQU      | \$F7                                                                     |                                                                                                        | ;FLASH Control Register                                                                                                                                                                                                                                                                        |

| LOCK:                                                                                     | EQU      | \$01                                                                     |                                                                                                        | Lock register Bit in FEELCK                                                                                                                                                                                                                                                                    |

| BOOTP:                                                                                    | EQU      | \$01                                                                     |                                                                                                        | ;Boot Protect Bit in FEEMCR                                                                                                                                                                                                                                                                    |

| SVFP:                                                                                     | EQU      | \$08                                                                     |                                                                                                        | ;Status Vfp Voltage Bit in FEECTL                                                                                                                                                                                                                                                              |

| ERAS:                                                                                     | EQU      | \$04                                                                     |                                                                                                        | ¿Erase Control Bit in FEECTL                                                                                                                                                                                                                                                                   |

| LAT:                                                                                      | EQU      | \$02                                                                     |                                                                                                        | Programming Latch Control bit in FEECTL                                                                                                                                                                                                                                                        |

| ENPE:                                                                                     | EQU      | \$01                                                                     |                                                                                                        | ;Enable Program/Erase Voltage Bit in FEECTL                                                                                                                                                                                                                                                    |

|                                                                                           | -20      | + ° ±                                                                    |                                                                                                        | ,                                                                                                                                                                                                                                                                                              |

| PORTA:                                                                                    | EQU      | \$0000                                                                   |                                                                                                        | ;Port A data register                                                                                                                                                                                                                                                                          |

| DDRA:                                                                                     | EQU      | \$0002                                                                   |                                                                                                        | Port A data direction register                                                                                                                                                                                                                                                                 |

|                                                                                           | -2-      | 4                                                                        |                                                                                                        |                                                                                                                                                                                                                                                                                                |

| Mult:                                                                                     | EQU      | 1000                                                                     |                                                                                                        | ;Multiplier for EClock, assembler won't do                                                                                                                                                                                                                                                     |

|                                                                                           | 200      | 2000                                                                     |                                                                                                        | ; values over 2^16                                                                                                                                                                                                                                                                             |

| EClock:                                                                                   | EQU      | {Mult*                                                                   | 8000}                                                                                                  | ;E-clock frequency in Hz.                                                                                                                                                                                                                                                                      |

|                                                                                           | -2-      | (                                                                        | ,                                                                                                      |                                                                                                                                                                                                                                                                                                |

| mS1LoopTime:                                                                              | EQU      | 4                                                                        |                                                                                                        | ;Num of clock cycles per loop.                                                                                                                                                                                                                                                                 |

| mS1Delay:                                                                                 | EQU      |                                                                          | k/(mS1LoopTime*10)                                                                                     | 00)};Must surround expression $w/{()}$ for P&E.                                                                                                                                                                                                                                                |

|                                                                                           | ~ -      | ι                                                                        |                                                                                                        | ;Factor of 1000 used for base time of 1 ms.                                                                                                                                                                                                                                                    |

|                                                                                           |          |                                                                          | Equates                                                                                                |                                                                                                                                                                                                                                                                                                |

| ,                                                                                         |          |                                                                          |                                                                                                        |                                                                                                                                                                                                                                                                                                |

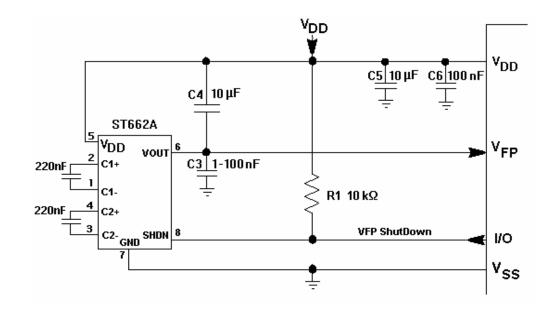

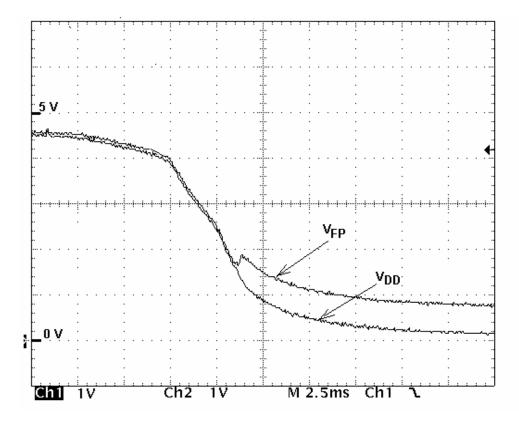

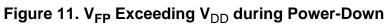

| ,                                                                                         |          |                                                                          |                                                                                                        |                                                                                                                                                                                                                                                                                                |