# Motorola Digital Signal Processors

# DSP96002 Interface Techniques and Examples

- by R. Robles

- Z. Rozenshein

- O. Rubinstein

- A. Vainberg

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters can and do vary in different applications. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application. Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and (A) are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

| 1.1 | Introduction                                                          | 1-1  |

|-----|-----------------------------------------------------------------------|------|

| 1.2 | Full Handshake DMA Transfer                                           | 1-2  |

|     | 1.2.1 Description                                                     | 1-2  |

|     | 1.2.2 Interconnection Model                                           | 1-5  |

|     | 1.2.3 Programming Consideration for<br>Full Handshake DMA Transfer    | 1-6  |

|     | 1.2.3.1 Master Processor<br>DMA Programming                           | 1-6  |

|     | 1.2.3.2 Master Processor<br>Port Programming                          | 1-8  |

|     | 1.2.3.3 Slave Processor Host<br>Interface Programming                 | 1-8  |

|     | 1.2.3.4 Slave Processor DMA<br>Channel Programming                    | 1-8  |

|     | 1.2.4 Timing Diagram of Full                                          |      |

|     | Handshake DMA Transfer                                                | 1-9  |

| 1.3 | Partial Handshake DMA Transfer                                        | 1-12 |

|     | 1.3.1 Description                                                     | 1-12 |

|     | 1.3.2 Interconnection Model                                           | 1-13 |

|     | 1.3.3 Programming Consideration for<br>Partial Handshake DMA Transfer | 1-15 |

|     | 1.3.3.1 Master Processor<br>DMA Programming                           | 1-15 |

|     | 1.3.3.2 Master Processor<br>Port Programming                          | 1-15 |

|     | 1.3.3.3 Slave Processor Host<br>Interface Programming                 | 1-15 |

SECTION 1 DSP96002 Data Transfer Techniques

|     |       | 1.3.3.4  | Slave Processor DMA                         |       |

|-----|-------|----------|---------------------------------------------|-------|

|     |       |          | Channel Programming                         | 1-15  |

|     | 1.3.4 | Timing   | Diagram of Partial                          |       |

|     |       | Handsh   | ake DMA Transfer                            | 1-16  |

| 1.4 | No Ha | andshak  | e DMA Transfer                              | 1-18  |

|     | 1.4.1 | Descrip  | tion                                        | 1-18  |

|     | 1.4.2 | Intercor | nnection Model                              | 1-19  |

|     | 1.4.3 | Program  | nming Considerations for                    |       |

|     |       | No Han   | dshake DMA Transfer                         | 1-20  |

|     |       | 1.4.3.1  | Master Processor DMA                        |       |

|     |       |          | Programming                                 | 1-20  |

|     |       | 1.4.3.2  | Master Processor Port                       |       |

|     |       |          | Programming                                 | 1-20  |

|     |       | 1.4.3.3  | Slave Processor Host                        | 4 04  |

|     |       |          | Interface Programming                       | 1-21  |

|     |       | 1.4.3.4  | Slave Processor DMA                         | 1-21  |

|     |       | 1 1 2 5  | Channel Programming<br>Slave Processor Port | 1-21  |

|     |       | 1.4.3.3  | Programming                                 | 1-21  |

|     | 1 4 4 | Timina   | Diagram of No Handshake                     | 1 2 1 |

|     | 1.4.4 | DMA Tr   | -                                           | 1-21  |

| 1.5 | Proar | ammina   | Examples                                    | 1-24  |

|     | -     | -        | nming Model of the Full                     |       |

|     | -     |          | ake DMA Transfer                            | 1-24  |

|     | 1.5.2 | Program  | nming Model for Partial                     |       |

|     |       | -        | ake DMA Transfer                            | 1-26  |

|     | 1.5.3 |          | nming Model for No                          |       |

|     |       | Handsh   | ake DMA Transfer                            | 1-28  |

SECTION 2 Connecting the DSP96002 as an Attached Processor to the ISA Bus Turns PC/AT into a Fast and Powerful IEEE Compatible Floating Point Computer

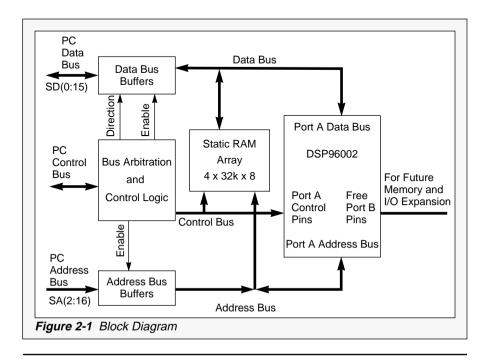

| 2.1 | Introduction                                    | 2-1  |

|-----|-------------------------------------------------|------|

| 2.2 | ISA (Industry Standard Architecture)            |      |

|     | Bus Details                                     | 2-2  |

| 2.3 | DSP96002 Features                               | 2-4  |

| 2.4 | Application Board Detailed Description          | 2-7  |

|     | 2.4.1 CPU                                       | 2-8  |

|     | 2.4.2 Memory                                    | 2-8  |

|     | 2.4.3 Data Bus and Address                      |      |

|     | Bus Buffers                                     | 2-8  |

|     | 2.4.4 Bus Arbitration Logic                     | 2-9  |

| 2.5 | CPU Sub-Block Detailed Description              | 2-9  |

| 2.6 | Memory Sub-Block Detailed Description           | 2-13 |

| 2.7 | Data and Address Bus Buffers                    |      |

|     | Detailed Description                            | 2-17 |

|     | 2.7.1 Bus Arbitration and Control Logic         |      |

|     | Detailed Description                            | 2-19 |

|     | 2.7.2 Host Interface Detailed                   | 0.40 |

|     | Description                                     | 2-19 |

|     | 2.7.3 Address Decoder Detailed                  | 2-21 |

|     | Description<br>2.7.4 Buffer Controller Detailed | 2-21 |

|     | Description                                     | 2-23 |

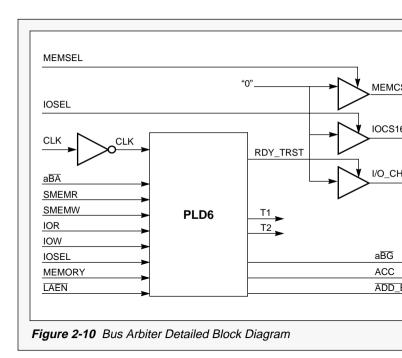

| 2.8 | Bus Arbiter Detailed Description                | 2-23 |

| 2.0 | Sample Software Applications                    | 2-24 |

| 2.9 | 2.9.1 Sample Application: Download              | 2-20 |

|     | Through the Host Interface                      | 2-29 |

|     | 2.9.2 Sample Application: Download              | 2 20 |

|     | Through Common Memory                           | 2-30 |

|     |                                                 |      |

|                                | 2.10 | Benchmarks                                     | 2-31 |

|--------------------------------|------|------------------------------------------------|------|

|                                | 2.11 | Acceleration Factor                            | 2-31 |

| SECTION 3                      | 3.1  | Introduction                                   | 3-1  |

| Connecting the                 | 3.2  | The VMEbus                                     | 3-1  |

| DSP96002 to                    | 3.3  | The DSP96002                                   | 3-2  |

| the VMEbus                     | 3.4  | Design Description                             | 3-2  |

|                                | 3.5  | Signals Between the Interface and the VMEbus   | 3-3  |

|                                | 3.6  | Signals Between the Interface and the ADS96002 | 3-4  |

|                                | 3.7  | Address and Modifier Decoding                  | 3-5  |

|                                |      | 3.7.1 Address Decoder PLD Equations            | 3-6  |

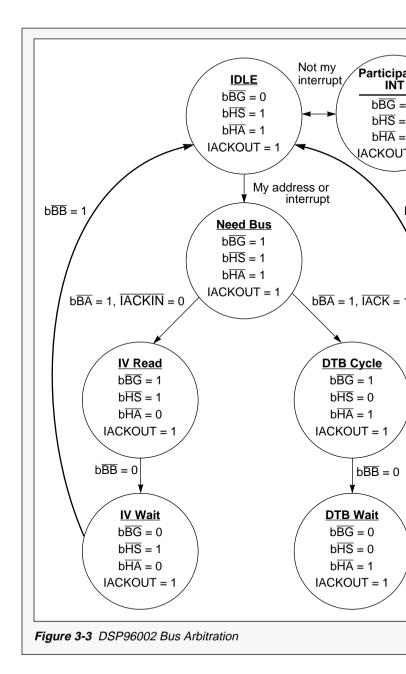

|                                | 3.8  | Description—Bus Arbiter                        | 3-6  |

|                                |      | 3.8.1 Bus Arbiter PLD Equations                | 3-8  |

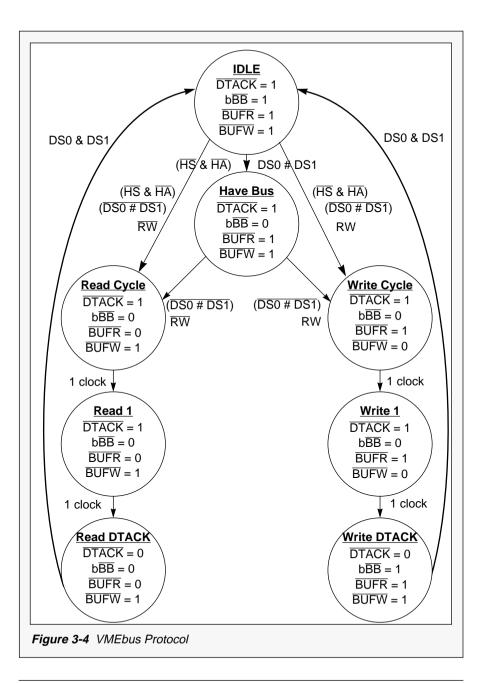

|                                | 3.9  | Description—VMEbus Protocol Handler            | 3-9  |

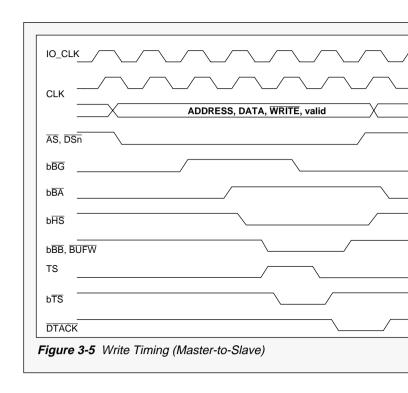

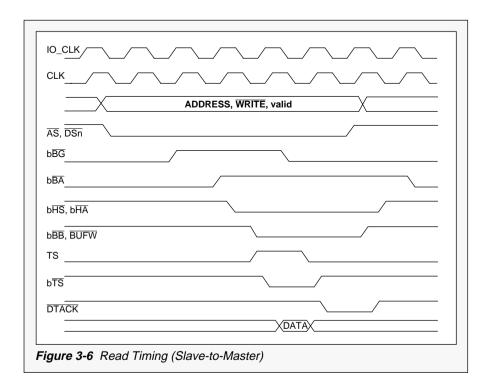

|                                | 3.10 | Timing Considerations                          | 3-12 |

| SECTION 4                      | 4.1  | Introduction                                   | 4-1  |

| Interfacing the DSP96002 Media | 4.2  | The DSP56ADC16 Analog-to-Digital<br>Converter  | 4-2  |

| Engine <sup>™</sup>            | 4.3  | The DSP96002 Media Engine™                     |      |

| Processor                      |      | Processor                                      | 4-3  |

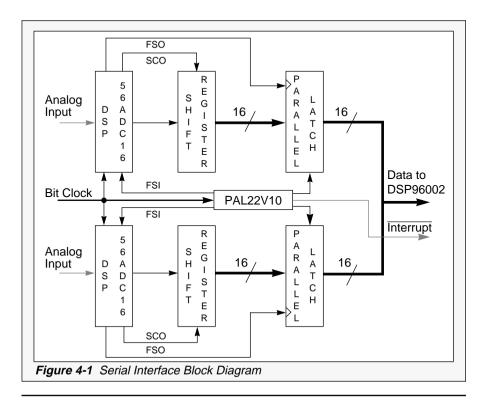

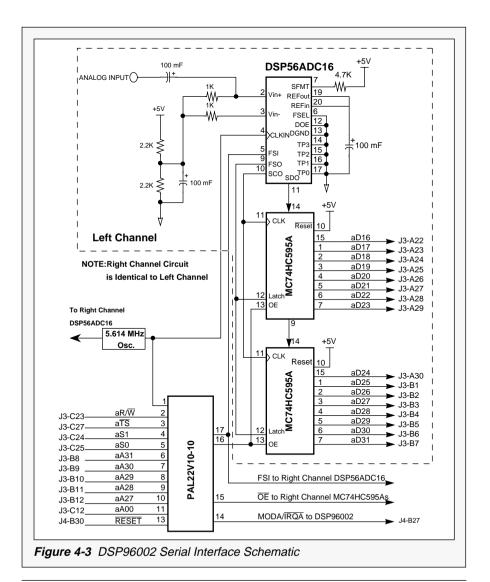

| to 56ADC16                     | 4.4  | Interface Hardware Description                 | 4-4  |

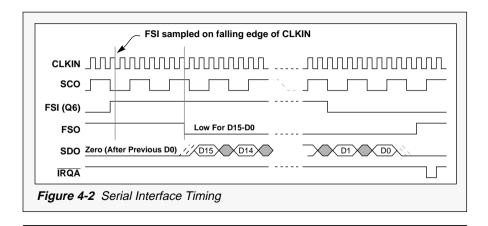

| Sigma-Delta A/D                |      | 4.3.1 Timing                                   | 4-7  |

| Converters                     |      |                                                |      |

| SECTION 5       | 5.1 | Introduction        | 5-1 |

|-----------------|-----|---------------------|-----|

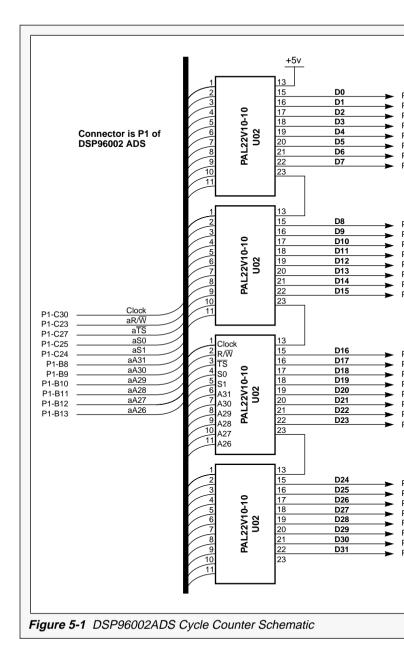

| A Non-Intrusive | 5.2 | Circuit description | 5-1 |

| Cycle Counter   |     |                     |     |

| for the         |     |                     |     |

| DSP96002 ADS    |     |                     |     |

REFERENCES

References-1

# Illustrations

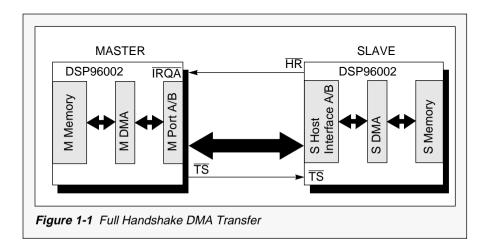

| Figure 1-1  | Full Handshake DMA Transfer                                                        | 1-3  |

|-------------|------------------------------------------------------------------------------------|------|

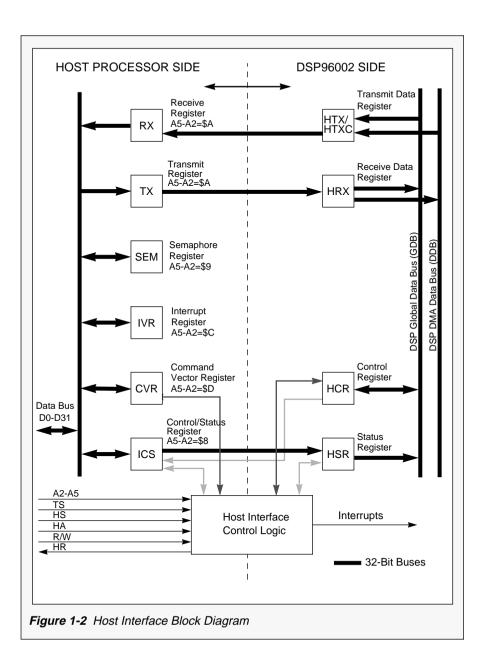

| Figure 1-2  | Host Interface Block Diagram                                                       | 1-4  |

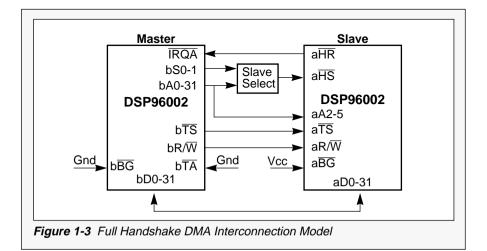

| Figure 1-3  | Full Handshake DMA Interconnection Model                                           | 1-5  |

| Figure 1-4  | Timing Diagram of Full Handshake DMA Transfer                                      | 1-11 |

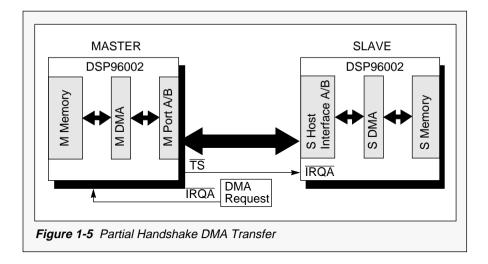

| Figure 1-5  | Partial Handshake DMA Transfer                                                     | 1-13 |

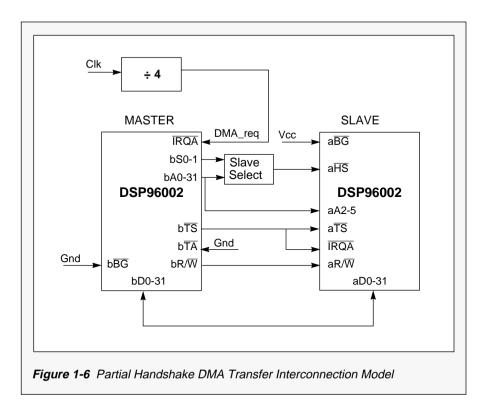

| Figure 1-6  | Partial Handshake DMA Transfer Interconnection Model                               | 1-14 |

| Figure 1-7  | Timing Diagram for Partial Handshake DMA Transfer                                  | 1-17 |

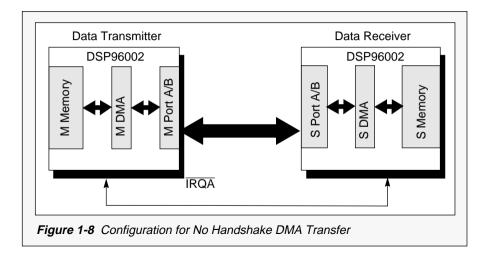

| Figure 1-8  | Configuration for No Handshake DMA Transfer                                        | 1-18 |

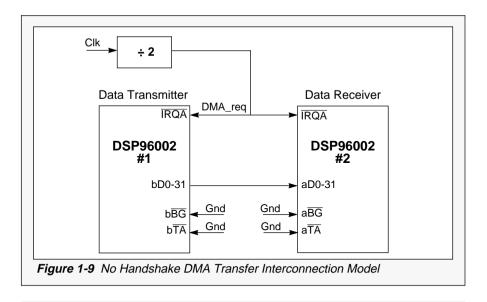

| Figure 1-9  | No Handshake DMA Transfer Interconnection Model                                    | 1-20 |

| Figure 1-10 | No Handshake DMA Transfer                                                          | 1-23 |

| Figure 1-11 | DMA Programming Procedure for the Master Processor<br>in the Full Handshake        | 1-24 |

| Figure 1-12 | DMA Programming Procedure for the Slave Processor<br>in the Full Handshake         | 1-25 |

| Figure 1-13 | DMA Programming Procedure for the Master Processor<br>in the Partial handshake     | 1-26 |

| Figure 1-14 | DMA Programming Procedure for the Slave Processor<br>in the Partial Handshake      | 1-27 |

| Figure 1-15 | DMA Programming Procedure for the Master Processor<br>in the No Handshake Transfer | 1-28 |

| Figure 1-16 | DMA Programming Procedure for the Slave Processor<br>in the No Handshake Transfer  | 1-29 |

| Figure 2-1  | Block Diagram                                                                      | 2-2  |

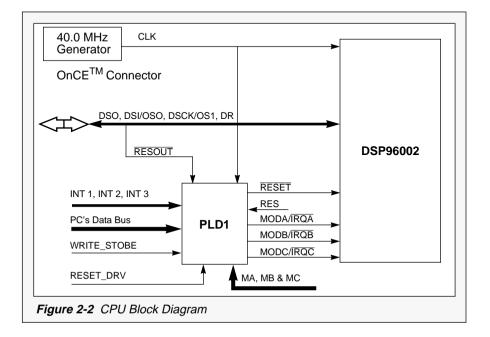

| Figure 2-2  | CPU Block Diagram                                                                  | 2-10 |

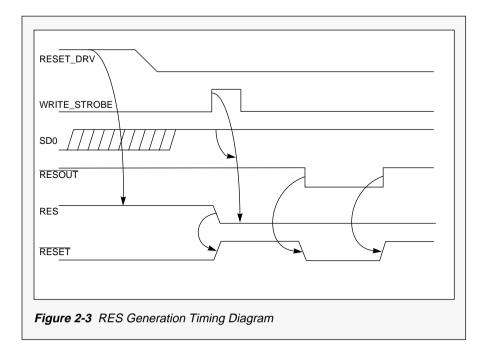

| Figure 2-3  | RES Generation Timing Diagram                                                      | 2-11 |

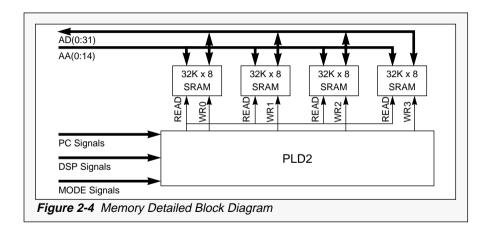

| Figure 2-4  | Memory Detailed Block Diagram                                                      | 2-13 |

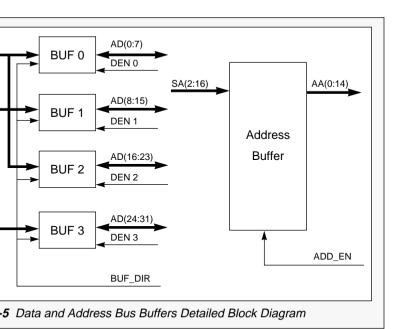

| Figure 2-5  | Data and Address Bus Buffers Detailed Block Diagram                                | 2-18 |

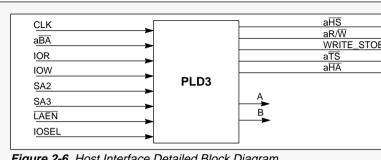

| Figure 2-6  | Host Interface Detailed Block Diagram                                              | 2-19 |

# Illustrations

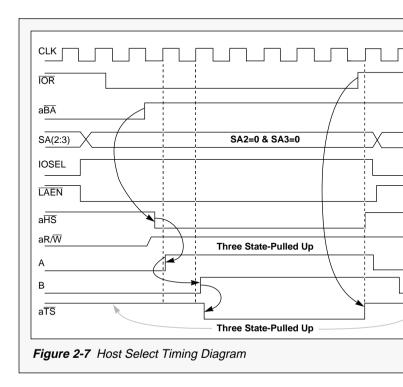

| Figure 2-7  | Host Select Timing Diagram                              | 2-21 |

|-------------|---------------------------------------------------------|------|

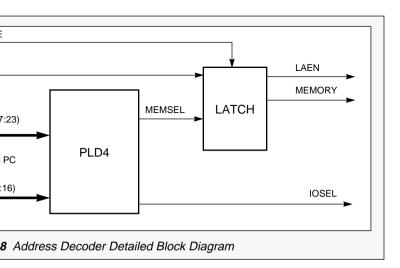

| Figure 2-8  | Address Decoder Detailed Block Diagram                  | 2-22 |

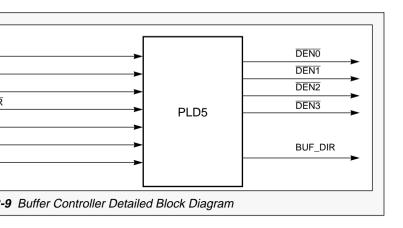

| Figure 2-9  | Buffer Controller Detailed Block Diagram                | 2-24 |

| Figure 2-10 | Bus Arbiter Detailed Block Diagram                      | 2-25 |

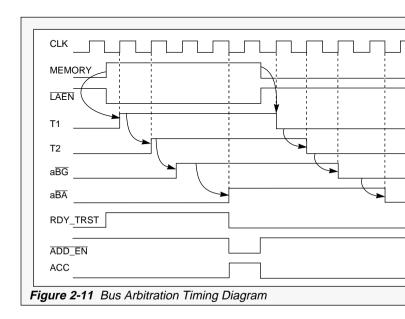

| Figure 2-11 | Bus Arbitration Timing Diagram                          | 2-27 |

| Figure 2-12 | 'C' Language Program Listing                            | 2-29 |

| Figure 2-13 | DSP96002 Assembly Language Listing                      | 2-29 |

| Figure 2-14 | 'C' Language Program Listing                            | 2-30 |

| Figure 2-15 | DSP96002 Assembly Language Listing                      | 2-30 |

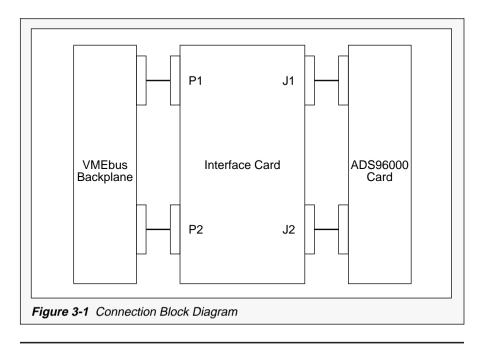

| Figure 3-1  | Connection Block Diagram                                | 3-4  |

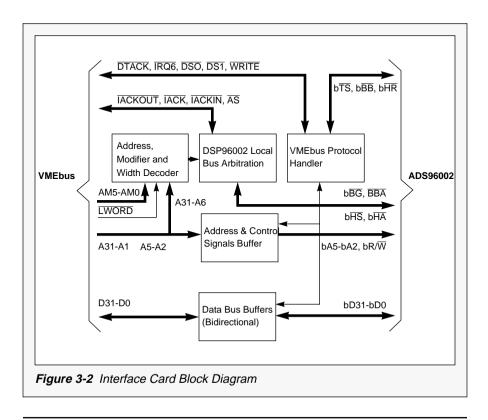

| Figure 3-2  | Interface Card Block Diagram                            | 3-5  |

| Figure 3-3  | DSP96002 Bus Arbitration                                | 3-7  |

| Figure 3-4  | VMEbus Protocol                                         | 3-10 |

| Figure 3-5  | VMEbus Protocol handler PLD Equations                   | 3-11 |

| Figure 3-6  | Write Timing (Master-to-Slave)                          | 3-13 |

| Figure 3-7  | Read Timing (Slave-to-Master)                           | 3-14 |

| Figure 4-1  | Serial Interface Block Diagram                          | 4-4  |

| Figure 4-2  | Serial Interface Timing                                 | 4-7  |

| Figure 4-3  | DSP96002 Serial Interface Schematic                     | 4-8  |

| Figure 4-4  | DSP96002 Serial Interface — PLD Definition              | 4-10 |

| Figure 5-1  | DSP96002ADS Cycle Counter Schematic                     | 5-2  |

| Figure 5-2  | PLD Source for the DSP96002 ADS Cycle Counter           | 5-3  |

| Figure 5-3  | Sample Program to Test the DSP96002ADS<br>Cycle Counter | 5-4  |

# List of Tables

Table 2-1

Generation of Read and Write Signals

2-16

## **SECTION 1**

# DSP96002 Data Transfer Techniques

by A. Vainberg

"The three transfer techniques presented in this section are Full Handshake DMA transfer..., Partial Handshake DMA transfer..., and No Handshake DMA transfer..."

# 1.1 Introduction

This section presents three high performance interconnection techniques with several DSP96002s. Transfer procedures are designed in such a manner that minimum DSP96002 CPU intervention is required. For this purpose, one of the two on-chip DMA channels is used and CPU intervention is required only in the initial phase for programming the DMA channels.

Unidirectional data transfer is assumed for simplicity; however, bidirectional data transfer can be implemented in the same manner. The model is composed of two processors, one is the Master Processor and the other is the Slave Processor. The model can be easily expanded for configurations with more than two processors. The data transfer direction is from Master to Slave. The particular implementation in this section is based on data transfer from the Master Processor internal memory, to Slave Processor internal memory. One of the Master Processor's two DMA channels is used to transfer data from Master internal memory to the Slave Processor's Host Interface. One of the Slave Processor DMA channels is used to transfer the received data from the Host Interface to internal memory.

The three transfer techniques presented in this section are:

- Full Handshake DMA transfer: one 4 byte transfer every 4 instruction cycles

- Partial Handshake DMA transfer: one 4 byte transfer every 2 instruction cycles

- No Handshake DMA transfer: one 4 byte transfer every 1 instruction cycle

# 1.2 Full Handshake DMA Transfer

## 1.2.1 Description

A full handshake DMA transfer provides data transfer from the internal memory of the Master Processor to the internal memory of the Slave Processor. For this purpose, one DMA channel is allocated to each processor. One of the Master Processor DMA channels is programmed to read data from internal memory and then to write this data to the Slave Processor Host Transmit Register. The Slave Processor DMA channel is programmed to read data from the Host Receive Register and to write this data in its internal memory. The Slave Processor DMA channel is programmed as "Single Block, Word Transfer, Triggered by the DMA Request" where the DMA request is the Host Receive Data Full (HRDF=1) flag. After the Slave Processor DMA channel is enabled, Transmit Data Register Empty (TXDE) status asserts the HR line of the Host Interface. The Slave Processor HR line connects to the Master Processor IRQA line.

The Master Processor DMA channel is programmed as "Single Block, Word Transfer, Triggered by DMA Request", where the DMA request is IRQA. A DMA request is generated when the Master Processor DMA channel is enabled and IRQA is asserted. In response to this DMA request, the Master Processor DMA channel reads data from internal memory and starts a bus write cycle. New data is written into the Slave Host Interface Transmit Data Register with the deassertion of TS. The TXDE bit is cleared, the HR line is deasserted, and a new data transfer to the HRX register is initiated.

A DMA request is generated after the status of Host Receive Data Full (HRDF) is updated and data is transferred to HRX register. This DMA request enables the DMA channel to read the HRX register and to write the received data into internal memory. The HRDF status is then cleared and the  $\overline{\text{HR}}$  line is asserted. After the  $\overline{\text{HR}}$  line is asserted, a new data transfer cycle is performed. If the DMA channel interrupt enable line has been set, an interrupt is generated at the end of DMA transfer.

### **1.2.2 Interconnection Model**

The data bus is common to both processors. The Master Processor is configured in master mode, i.e., Bus Grant ( $\overline{BG}$ ) is connected to "0". Also, Transfer Acknowledge ( $\overline{TA}$ ) is connected to "0" which means that the Master Processor will always receive an automatic data acknowledge so that no wait states will be inserted.

MOTOROLA

The Master Processor address bus (A5-A31) and Space Select (S0-S1) lines are decoded to generate  $\overline{HS}$  to select the Slave Processor Host Interface. The A2-A5 lines are used to select the Slave Processor Host Interface Register. The Master Processor R/ $\overline{W}$  line is connected to the Slave Processor R/ $\overline{W}$  line and is used to signal a Read or Write transfer. The Master processor Transfer Strobe ( $\overline{TS}$ ) is connected to the Slave Processor Tris;  $\overline{TS}$  is asserted when a bus write or a bus read is taking place. The Slave Processor Bus Grant ( $\overline{BG}$ ) signal is connected to "1", placing the Slave Processor in the Bus Slave mode. A common clock is *not* necessary in this configuration and no special timing precautions need to be considered.

### 1.2.3 Programming Consideration for Full Handshake DMA Transfer

#### 1.2.3.1 Master Processor DMA Programming

One of the Master Processor's two DMA channels is programmed to read data from internal memory and to write this data to the Slave Processor Host Interface Transmit Data Register.

The DMA Source Address Register receives the beginning address of the internal memory data block. The DMA Source Modifier Register and the DMA Source Offset Register are programmed according to the data organization.

The DMA Destination Address Register is programmed with the Slave Processor Host Interface Transmit Data Register address which is the Slave Select Address + \$28. The DMA Destination Modifier Register is programmed for linear increment, the DMA Destination Offset is programmed with "0", and the destination pointer is not incremented. The DMA destination counter register is programmed with the data block length.

The DMA Control Status Register is programmed as follows:

- DMA Enable is set to start the DMA transfer

- DMA Source Space Control (DSS) is set for transfer from internal X or Y memory

- DMA Destination Space Control (DDS) will be set for transfer to external X or Y memory

- If an interrupt is requested at the end of transfer, the DIE bit should be set and the Interrupt Priority Register must be initialized to receive Interrupt Requests from the DMA channel

- The DMA request source is the IRQA line so the DMA Request Mask bits should be configured as M1-M6=0 and M0=1

- The DMA Transfer Mode must be programmed as "Single Block, Word Transfer Triggered by DMA Request", where the DMA Request in this case is the TRQA line

- No special caution needs to be taken regarding the DMA/Core Priority bit, DMAP

- Also, it is not necessary for this DMA channel to have a higher priority than the second internal DMA channel

#### 1.2.3.2 Master Processor Port Programming

The Port Select Register allocates the address range for each port. The port allocated address must permit selection of the Slave Processor Host Interface.

No special precautions need to be considered when programming the Bus Control Register; however, introducing wait states slows data transfer.

#### 1.2.3.3 Slave Processor Host Interface Programming

If the Host Interface is used only for DMA, no special programming is necessary after reset. The Master Processor only needs to write data to the Host Interface TX register.

#### 1.2.3.4 Slave Processor DMA Channel Programming

One of the Slave Processor's two DMA channels is programmed to read data from the Host Interface HRX register and to write data to internal memory.

The DMA Source Address Register is programmed with the Host Interface RX register address. The DMA Source Modifier Register and the DMA Source Offset Register are programmed so that the DMA Source Address Register remains constant, which means the DMA Source Offset Register is cleared.

The DMA Destination Address Register receives the internal memory data block beginning address. The DMA Destination Modifier Register and the DMA Destination Offset Register is programmed according to the data organization. The DMA destination counter register is programmed with the data block length.

The DMA Control Status Register is programmed as follows:

- DMA Enable is set to start the DMA transfer.

- DMA Destination Space Control (DDS) is set for transfer to internal X or Y memory.

- DMA Source Space Control (DDS) is set for transfer from the Host Interface HRX register. If an interrupt is requested at the end of the transfer, the DIE bit should be set and the Interrupt Priority Register must be initialized to receive Interrupt Requests from the DMA channel.

- The DMA request source is the HRDF status so the DMA Request Mask bits are M0-M6=\$8.

- The DMA Transfer Mode needs to be programmed as "Single Block, Word Transfer, Triggered by DMA Request", where DMA Request, in this case, is the HRDF status.

## 1.2.4 Timing Diagram of Full Handshake DMA Transfer

We assume that both DSP96002 processors work with the same clock although this is not essential. Each DSP96002 system clock is composed of four phases, or two clock periods. If the two processors work with different clocks then, generally, the transfers are longer due to synchronization delays. The  $\overline{\text{HR}}$  line is asserted on phase T1 of the clock *after* the Slave Processor DMA is initialized and HRX is empty (therefore the Host Interface TX Register is empty).  $\overline{\text{IRQA}}$ , which is connected to  $\overline{\text{HR}}$ , is asserted at the same time.

The DMA request is sampled on T1 and a Master DMA transfer is then started. The DMA controller generates a valid DMA address on the first T0 after  $\overline{IRQA}$  is asserted and new data is read from internal memory. After four more phases (i.e., on the next T0), the DMA data bus receives valid data from internal memory, and starts an external memory write cycle. The TS line is asserted on phase T1, and when TS is deasserted, the data is written to the Slave Processor Host Interface TX register on T3.

The TXDE bit is cleared on the first T0 after the Slave Processor TX register is written. This deasserts the  $\overline{HR}$  signal. On phase T3 of that cycle, the internal Host Interface signal HldHRX is asserted for one phase, and data is transferred from the TX register to the Host Interface HRX register. After this transfer, the TXDE status is set and  $\overline{HR}$  is asserted, initiating the next full handshake transfer. When  $\overline{HR}$  is asserted, a valid DMA address is written to the DMA address bus following T0. During the next T0, the new data is read from the HRX register to the DMA bus. The HRDF Status is cleared after data is transferred to the DMA data bus from the HRX. The minimum cycle data transfer length is 8 clocks or 4 instruction cycles.

A listing of the programming model for the full handshake DMA transfer is provided in **SECTION 1.5**.

|                                                                            | T2 T3 T0 T1 T2 T3 T0 T1 T2 T3 T0 T1 T2 T | T3 T0 T1 T2 T3 T0 T1 T2 T3 |

|----------------------------------------------------------------------------|------------------------------------------|----------------------------|

|                                                                            |                                          |                            |

|                                                                            |                                          |                            |

| aster Processor                                                            |                                          |                            |

| IRQA                                                                       |                                          | /                          |

| ХАВ                                                                        |                                          |                            |

|                                                                            |                                          | Source                     |

| YAB                                                                        |                                          |                            |

| Dest                                                                       | X                                        | Dest                       |

| DMA Data                                                                   |                                          |                            |

|                                                                            | Valid DMA Data                           | Valid DMA Data             |

| TS                                                                         |                                          |                            |

|                                                                            |                                          |                            |

| Data Out                                                                   |                                          |                            |

|                                                                            |                                          |                            |

|                                                                            |                                          |                            |

|                                                                            |                                          |                            |

|                                                                            |                                          | /\/\                       |

| ave Processor                                                              |                                          | /N/N                       |

| ave Processor                                                              |                                          | /N/N                       |

| HS                                                                         |                                          |                            |

|                                                                            |                                          |                            |

| HS                                                                         |                                          | Data                       |

| HS                                                                         | Valid C                                  | Data                       |

| HS<br>TX Register                                                          |                                          | Data                       |

| HS<br>TX Register<br><br>HIdHRX<br>TXDE                                    |                                          | Data                       |

| HS<br>TX Register<br><br>HIdHRX                                            |                                          | Data                       |

| HS<br>TX Register<br><br>HIdHRX<br>TXDE                                    |                                          | Valid Data                 |

| HS<br>TX Register<br>HIdHRX<br>TXDE<br>HRX Register<br>XAB                 |                                          | Valid Data                 |

| HS<br>TX Register<br>HIdHRX<br>TXDE<br>HRX Register                        |                                          | Valid Data                 |

| HS<br>TX Register<br>HIdHRX<br>TXDE<br>HRX Register<br>ZAB<br><br>DMA Data |                                          | Valid Data                 |

| HS<br>TX Register<br>HIdHRX<br>TXDE<br>HRX Register<br>XAB                 |                                          | Valid Data                 |

MOTOROLA

# 1.3 Partial Handshake DMA Transfer

## 1.3.1 Description

The purpose of this implementation is to provide a faster transfer between two DSP96002 processors. One of the processors is configured as the Master and the other one as the Slave, with the data transfer from the Master to the Slave. The advantage of this implementation is the high transfer rate, one 32-bit transfer every four clocks.

The substantial speed improvement is achieved through a pipeline-type transfer. The Master Processor receives a DMA request through IRQA: the DMA channel is programmed as "Single Block, Word Transfer, Triggered by DMA request", The Master Processor DMA channel initiates a data transfer from Master Processor internal memory to the Slave Processor Host Interface TX register. Data is placed in the Slave Processor TX register and from there, in the HRX register. The Slave Processor DMA channel is programmed as "Single Block, Word Transfer, Triggered by DMA request", where the DMA request is  $\overline{IROA}$ . Because the Master Processor  $\overline{TS}$  line is connected to the Slave Processor IRQA line, a DMA transfer is initiated from the HRX register to internal memory. Meanwhile, the Master Processor can start a new DMA transfer cycle. Before new data is placed in the Slave TX register, the Slave DMA channel transfers the contents of the HRX register into internal memory.

### **1.3.2 Interconnection Model**

The data bus is common to both processors. The Master Processor is configured in the master mode – i.e., Bus Grant ( $\overline{BG}$ ) signal is connected to "0". Also, Transfer Acknowledge ( $\overline{TA}$ ) is connected to "0" which means that the Master Processor always receives automatic data acknowledge so that no wait states are inserted. The Master Processor address bus (A5-A31) and Space Select (S0-S1) lines are decoded to generate the  $\overline{HS}$  signal to select the Slave Processor Host Interface. The A2-A5 lines are used to select the TX register from Slave Processor Host Interface. The Master Processor R/ $\overline{W}$  line is connected to Slave Processor R/ $\overline{W}$  line and is used to signal a Read or Write action.

The Master processor Transfer Strobe (TS) is con-

nected to the Slave Processor  $\overline{TS}$ ; a bus write or a bus read takes place when  $\overline{TS}$  is asserted. The Slave Processor Bus Grant ( $\overline{BG}$ ) signal is connected to "1", placing it in the Slave mode. The Master Processor IRQA is connected to an external DMA request source which can generate a maximum of one request every 2 instruction cycles.

The Slave Processor  $\overline{IRQA}$  is connected to  $\overline{TS}$  of Master Processor.

A common clock *is* necessary in this configuration, and no wait states are permitted.

## 1.3.3 Programming Consideration for Partial Handshake DMA Transfer

#### 1.3.3.1 Master Processor DMA Programming

The same rules as for the Full Handshake Programming model must be followed. It is recommended that this DMA channel be given a higher interrupt priority level than the core processor.

#### 1.3.3.2 Master Processor Port Programming

The Port Select Register allocates the address range for each port. The port allocated address must permit selection of the Slave Processor Host Interface. No Wait States are permitted for this configuration.

### 1.3.3.3 Slave Processor Host Interface Programming

If the Host Interface is used only for this DMA transfer, no special programming is necessary after reset. The Master Processor only needs to write data to the Host Interface TX register.

#### 1.3.3.4 Slave Processor DMA Channel Programming

The same rules as for the Full Handshake Programming model must be followed.

- The DMA request source is the IRQA line so the DMA Request Mask bits are M0-M6=1.

- The DMA Transfer Mode must be programmed as "Single Block, Word Transfer, Triggered by DMA Request", where the DMA Request, in this case, is the IRQA line.

## 1.3.4 Timing Diagram of Partial Handshake DMA Transfer

Both DSP96002s have to work with the same clock for this configuration. After both processors have been initialized, the Master Processor receives a DMA request through the IRQA line. The DMA request is recognized on T1, and a new Master Processor DMA cycle starts. On the first T0 phase after the DMA request has been recognized, the DMA source address is placed on the XAB and the DMA destination address is placed on the YAB because the transfer type is from internal memory to external memory. The new data is read from internal memory. placed on the DMA data bus, and then transferred to the Slave Processor (TS deasserted) on the next T3 phase. A new DMA request can be recognized and a new DMA transfer can be performed on the next T1 after  $\overline{TS}$  is deasserted

The deassertion of  $\overline{TS}$  writes new data in the Slave Processor TX register on the Slave Processor side. The Slave Processor DMA channel is programmed to transfer data from the HRX register to the X internal memory. The DMA channel request is recognized on the first T1 after IRQA deassertion. On the first T0 after the request, the DMA controller places the source address on the XAB bus, and the destination address on the following T0. Data is transferred from the TX register to the HRX register on phase T3. Data from the HRX register is then transferred to the DMA data bus on the next T0. During this T0, the Slave Processor DMA channel is also ready for a new transfer. The minimum cycle data transfer length in this implementation is 4 clocks. A listing of the programming model for the partial handshake DMA transfer is shown in **SECTION 5.2**.

|                                                                | TO T1 T2 T3 T0 T1 T2 T3                              |

|----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|

| laster Process                                                 | sor                                                                                                              |

|                                                                |                                                                                                                  |

| XAB                                                            | rceX XSourceX XSourceX                                                                                           |

|                                                                | st X Dest X Dest X Dest X                                                                                        |

| DMA Data                                                       |                                                                                                                  |

| ===                                                            | 🛛 DMA Data 🕅 DMA Data 🕅 DMA Data                                                                                 |

| TS                                                             |                                                                                                                  |

| Data Out                                                       |                                                                                                                  |

|                                                                | Data Data Data                                                                                                   |

|                                                                |                                                                                                                  |

|                                                                |                                                                                                                  |

| lave Processo                                                  |                                                                                                                  |

|                                                                |                                                                                                                  |

| lave Processo                                                  | or                                                                                                               |

|                                                                | or                                                                                                               |

| IRQ <u>A</u>                                                   | or                                                                                                               |

| IRQA<br>TX Register                                            | DMA Request Recognized                                                                                           |

| IRQA<br>TX Register<br>HIdHRX                                  | DMA Request Recognized                                                                                           |

| IRQA<br>TX Register                                            | DMA Request Recognized                                                                                           |

| IRQA<br>TX Register<br>HIdHRX<br>HRX Register                  | DMA Request Recognized                                                                                           |

| IRQA<br>TX Register<br>HIdHRX                                  | DMA Request Recognized                                                                                           |

| IRQA<br>TX Register<br>HIdHRX<br>HRX Register<br>XAB Slave     | DMA Request Recognized                                                                                           |

| TX Register<br>HIdHRX<br>HRX Register                          | DMA Request Recognized<br>Data Data Data A<br>Data Data Data A<br>Data Data Data Data<br>Src MDest Src MDest Src |

| IRQA     TX Register     HIdHRX     HRX Register     XAB Slave | DMA Request Recognized<br>Data Data Data<br>Data Data Data<br>Data Data Data<br>Data Data Data                   |

MOTOROLA

# 1.4 No Handshake DMA Transfer

## 1.4.1 Description

This technique is a pipelined type of transfer as in the partial handshake DMA transfer; however, in this case, both processors are configured in Master Mode. One processor transmits data and the second processor receives the data.

Two DMA channels are used in Figure 1-8, one on each processor. Both processors are configured as Bus Masters and the only interconnection between them is through the data bus. The Data Transmitter DMA is configured as "Single Block, Word Transfer, Triggered by DMA request", with the transfer direction from internal X memory to external Y memory. The Data Receiver DMA is also configured as "Single Block, Word Transfer, Triggered by DMA request", but with the transfer direction from external Y memory to internal X memory. Both DMAs use the same trigger and both interfaces are programmed with zero wait states.

### **1.4.2 Interconnection Model**

The data bus is common to both processors. The Master Processor is configured in master mode – i.e., the Bus Grant ( $\overline{BG}$ ) signal is connected to "0". Also, the Transfer Acknowledge ( $\overline{TA}$ ) signal is connected to "0" which means that the Master Processor always receives an automatic data acknowledge so that no wait states will be inserted. The Master Processor and Slave Processor do not have the address lines,  $R/\overline{W}$  lines, or  $\overline{TS}$  lines connected. The Slave Processor and Master Processor Bus Grant ( $\overline{BG}$ ) lines are connected to "0".

The Master Processor IRQA is connected to an external DMA request source which can generate a maximum of one request every instruction cycle.The Slave Processor IRQA is connected to the same DMA request source.

It is recommended that the Slave Processor  $\overline{\text{DE}}$  line not be asserted to avoid potential data bus contention.

A common clock *is* necessary in this configuration and no wait states are permitted.

## 1.4.3 Programming Considerations for No Handshake DMA Transfer

#### 1.4.3.1 Master Processor DMA Programming

The same rules as for the Full Handshake Programming model must be followed. It is recommended that this DMA channel be given a higher interrupt priority level than the core processor or the second on-chip DMA channel.

#### 1.4.3.2 Master Processor Port Programming

The Port Select Register allocates the address range for each port. The port allocated address must permit selection of the Slave Processor Host Interface. No Wait States are permitted for this configuration.

### 1.4.3.3 Slave Processor Host Interface Programming

The Slave Processor Host Interface is not used for this type of transfer.

#### 1.4.3.4 Slave Processor DMA Channel Programming

The same rules as for Full Handshake Programming model must be followed.

- The Source Address must be external X or Y memory and the destination address must be Y or X memory.

- The DMA request source is the IRQA line so the DMA Request Mask bits are M0-M6=1.

- The DMA Transfer Mode has to be programmed as "Single Block, Word Transfer, Triggered by DMA Request", where DMA Request in this case is the IRQA line.

#### 1.4.3.5 Slave Processor Port Programming

The Port Select Register allocates the address range for each port. The port selected allows the DMA channel to read data from the connected data bus. No Wait States are permitted for this configuration.

## 1.4.4 Timing Diagram of No Handshake DMA Transfer

Both DSP96002s work with the same clock in this configuration. After the DMA channels of both processors have been initialized, a DMA request is

applied simultaneously to all DMA channels. On the first T1 phase after IRQA is asserted, the DMA request is recognized and a DMA transfer cycle is started. On the next T0 phase after IRQA is recognized, the DMA source address is placed on the XAB internal bus and the DMA destination address. is placed on the YAB internal bus. Data is read from internal memory and placed on the DMA data bus on the next T3 phase after the source and destination addresses are placed on XAB and YAB. The valid data is written on the output data pins on phase T2 after data becomes valid. A pipeline type transfer starts if a new DMA request is placed four phases after the first request. If the second processor receives the DMA request with the same timing as the first processor, the data is transferred to the second processor. The Slave processor recognizes the DMA request on the first T1. The source and destination addresses are placed on XAB and YAB on the next T0. Subsequently, the appropriate address is placed on the external address bus on the following T0. The data on the data bus is sampled at the transition from T2 to T3, and the new read data is valid on the internal DMA data bus beginning on T3.

If the DMA request signals are identical for Processor #1 and Processor #2, data written by Processor #1 is valid on the third T2 phase after the DMA request is recognized. Processor #2 reads valid data on the third T3 phase after IRQA is recognized.

This pipelined type of transfer offers the possibility of a transfer every 4 phases (i.e., every two clock periods or each instruction cycle). A listing of the programming model for the no handshake DMA transfer is provided in **SECTION 1.5.3**.

|                                         |         | T1 T2 T3 1              |            |            |                |               |     |               |          | 2 T3          |   |

|-----------------------------------------|---------|-------------------------|------------|------------|----------------|---------------|-----|---------------|----------|---------------|---|

| laster Pro                              | ocesso  | or                      |            |            |                |               |     |               |          |               |   |

|                                         | 2       |                         | 3          |            | 4              | 5             |     | 6             |          | 7             |   |

| ХАВ                                     | X1      | N_N                     | 2 X        | X 3        | M              | X 4 X         | X 5 |               | X 6      | M             | M |

| YAB                                     | X 1     | N_N                     | 2 🕅        | X 3        | X              | X 4 X         | X 5 |               | X 6      |               | M |

| Address O                               | ut      | N                       | 1          |            | 2              | X <u>3</u>    |     | 4             |          | 5             | M |

| Da <u>ta Out</u>                        |         |                         | - <b>1</b> | ۰ <b>.</b> |                |               |     |               | <i>л</i> |               |   |

|                                         |         |                         | <u>N_1</u> | M/         |                | <u> </u>      |     | 4             | <u> </u> | ( <u>5</u> )X |   |

|                                         |         | 2                       | <u>X</u> 1 | MP         | 4              | X 3           |     | <u> </u>      |          | <u>_</u> 5_X  |   |

|                                         |         | 2                       |            |            |                |               |     |               |          |               |   |

| IRQA 1_<br>Data in on                   | Externa | 2<br>al Bus             | 3          |            | 4              | 5             |     |               |          | 7             |   |

| Slave Proc                              | Externa | 2<br>al Bus             | 3_<br>     |            | 4<br>(2)(<br>2 | 5<br>73       |     | 6<br>(4_)     |          | 7_<br>(5)X    |   |

| IRQA 1_<br>Data in on<br><br>Address or | Externa | 2<br>al Bus<br>hal Pins | 3<br>      |            | 4<br>(2)(<br>2 | 5<br>(3<br>M3 |     | 6<br>(4)<br>4 |          | _7            |   |

# 1.5 Programming Examples

### 1.5.1 Programming Model of the Full Handshake DMA Transfer

| IPR                                                                              | equ                                                                                             | \$fffffff                                                                   | ; Interrupt Priority Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BCRB                                                                             | equ                                                                                             | \$ffffffd                                                                   | ; Bus Control Register port B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| PSR                                                                              | equ                                                                                             | \$ffffffc                                                                   | ; Port Select Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| D1SMR                                                                            | equ                                                                                             | \$fffffd7                                                                   | ; DMA1 Source Modifier Register<br>; DMA1 Source Address Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| D1SAR                                                                            | equ                                                                                             | \$fffffd6                                                                   | ; DMA1 Source Address Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                  | equ                                                                                             | \$fffffd5                                                                   | ; DMA1 Source Offset Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| D1DMR                                                                            |                                                                                                 | \$fffffd3                                                                   | ; DMA1 Source Offset Register<br>; DMA1 Destination Modifier Reg                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| D1DAR                                                                            |                                                                                                 | \$fffffd2                                                                   | ; DMA1 Destination Address Reg<br>; DMA1 Destination Offset Reg                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| D1DOR                                                                            |                                                                                                 | \$fffffd1                                                                   | ; DMA1 Destination Offset Reg                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| D1CT                                                                             |                                                                                                 |                                                                             | ; DMA1 Counter Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| D1CSR                                                                            |                                                                                                 | \$fffffd0                                                                   | ; DMA1 Control Status Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                  |                                                                                                 |                                                                             | ost Interface Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                  | equ                                                                                             | \$4000000                                                                   | ; Tx register address on the Slave                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| TX                                                                               | 1 · · ·                                                                                         | Slave+\$28                                                                  | ; DMA1 Control Status Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                  |                                                                                                 | re for Master Pr                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| movep                                                                            | #\$000C                                                                                         | 0000,X:IPR                                                                  | ; Enable interrupts from DMA1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                  |                                                                                                 |                                                                             | ; The DMA1 channel will generate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                  |                                                                                                 |                                                                             | ; interrupts on level 2 for DMA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                  |                                                                                                 |                                                                             | ; transfer completed, if DIE=1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| movep                                                                            | #\$0000                                                                                         | 0000,x:BCRB                                                                 | ; Port B Bus has no wait states                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                  | "+                                                                                              |                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| movep                                                                            | #\$000F                                                                                         | OF00,x:PSR                                                                  | ; All X addresses 0\$80000000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| movep                                                                            | #\$000F                                                                                         | OFOO,x:PSR                                                                  | ; All Y addresses 0\$80000000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| -                                                                                |                                                                                                 | ·                                                                           | ; All Y addresses 0\$80000000<br>; will be through port B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| ; Init                                                                           | ialize t                                                                                        | he DMA Procedure                                                            | ; All Y addresses 0\$80000000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| ; Init; Prog                                                                     | ialize t<br>ram DMA1                                                                            | he DMA Procedure<br>source                                                  | ; All Y addresses 0\$80000000<br>; will be through port B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| ; Init; Prog                                                                     | ialize t                                                                                        | he DMA Procedure<br>source                                                  | <pre>; All Y addresses 0\$80000000<br/>; will be through port B<br/>e for the Master Processor<br/>; DMA1 source modifier is</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| ; Init; Prog                                                                     | ialize t<br>ram DMA1                                                                            | he DMA Procedure<br>source                                                  | ; All Y addresses 0\$80000000<br>; will be through port B<br>e for the Master Processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| ; Init<br>; Prog<br>movep                                                        | ialize t<br>ram DMA1                                                                            | the DMA Procedure<br>source<br>DISMR                                        | <pre>; All Y addresses 0\$80000000<br/>; will be through port B<br/>e for the Master Processor<br/>; DMA1 source modifier is<br/>; programmed in linear modulo</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| ; Init<br>; Prog<br>movep<br>movep                                               | ialize t<br>ram DMA1<br>#\$1ff,]                                                                | the DMA Procedure<br>source<br>DISMR<br>SOR                                 | <pre>; All Y addresses 0\$80000000<br/>; will be through port B<br/>a for the Master Processor<br/>; DMA1 source modifier is<br/>; programmed in linear modulo<br/>; addressing mode</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                             |