APR20/D

## Application Optimization for the DSP56300/DSP56600 Family of Digital Signal Processors

by Uri Dayan, Zvi Rozenshein, Elkana Korem, Yoram Salant, Philippe Sixou, George Agasandian, and Victor Kaplansky Motorola Semiconductor Israel Ltd.

Motorola, Incorporated Semiconductor Products Sector DSP Division 6501 William Cannon Drive West Austin, TX 78735-8598

Mfax and OnCE are trademarks of Motorola, Inc.

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Motorola data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and M are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

#### How to reach us:

## USA/Europe/Locations Not Listed:

Motorola Literature Distribution P.O. Box 5405 Denver, Colorado 80217 303-675-2140 1 (800) 441-2447

#### Mfax™: RMEAX0@em

RMFAX0@email.sps.mot.com TOUCHTONE (602) 244-6609

#### Asia/Pacific:

Motorola Semiconductors H.K. Ltd. 8B Tai Ping Industrial Park 51 Ting Kok Road Tai Po, N.T., Hong Kong 852-2662928

**Technical Resource Center:** 1 (800) 521-6274

DSP Helpline dsphelp@dsp.sps.mot.com

#### Japan:

Nippon Motorola Ltd. Tatsumi-SPD-JLDC 6F Seibu-Butsuryu-Center 3-14-2 Tatsumi Koto-Ku Tokyo 135, Japan 81-3-3521-8315

Internet: http://www.motorola-dsp.com

## TABLE OF CONTENTS

| SECTIO | N 1 INTRODUCTION                                       |

|--------|--------------------------------------------------------|

| 1.1    | OVERVIEW                                               |

| 1.2    | DSP56300 CORE FAMILY1-3                                |

| 1.3    | DSP56600 CORE FAMILY1-4                                |

| 1.4    | ENHANCEMENTS OVER THE DSP56000                         |

| 1.4.1  | Instruction Set Enhancements                           |

| 1.4.2  | Architectural Enhancements                             |

| 1.5    | APPLICATION NOTE STRUCTURE                             |

| 1.5.1  | DSP56300 and DSP56600 Features Description and Use 1-8 |

| 1.5.2  | Optimizing the Code for Best Performance               |

| 1.5.3  | Appendixes                                             |

| SECTIO | N 2 DATA OPERATIONS                                    |

| 2.1    | USING THE DUAL DATA PATHS                              |

| 2.2    | 16-BIT ARITHMETIC MODE (DSP56300 ONLY)2-7              |

| 2.3    | THE MAX INSTRUCTION                                    |

| 2.4    | USING THE BARREL SHIFTER2-9                            |

| 2.5    | BIT MANIPULATION INSTRUCTIONS                          |

| 2.6    | DOUBLE PRECISION ARITHMETIC2-12                        |

| 2.7    | USING LESS STRAIGHT-FORWARD INSTRUCTIONS 2-14          |

| SECTIO | N 3 PROGRAM CONTROL                                    |

| 3.1    | HARDWARE LOOPS                                         |

| 3.2    | THE HARDWARE STACK                                     |

| 3.3    | USING THE STACK EXTENSION                              |

| 3.4    | TASK SWITCHING WITH THE STACK EXTENSION 3-11           |

| 3.5    | CONDITIONAL DATA ALU INSTRUCTIONS                      |

| 3.6    | PC RELATIVE INSTRUCTIONS                               |

| 3.7    | USING FAST INTERRUPTS                                  |

| SECTIO | N 4 USING THE DMA                                      |

|        | INTRODUCTION                                           |

| 4.2       | CONSERVING CORE MIPS BY WORKING IN PARALLEL4-3              |

|-----------|-------------------------------------------------------------|

| 4.3       | USING SLOW, LOW-COST MEMORIES                               |

| 4.4       | SERVICING A PERIPHERAL                                      |

| 4.5       | DATA TRANSFER OPTIMIZATION HINTS4-13                        |

| SECTIO    | N 5 INSTRUCTION CACHE AND MEMORY FEATURES .<br>5-1          |

| 5.1       | INTRODUCTION                                                |

| 5.2       | THE INSTRUCTION CACHE                                       |

| 5.2.1     | Cache Sectors                                               |

| 5.2.2     | Control of Sector Allocation                                |

| 5.2.3     | Cache Burst Mode                                            |

| 5.3       | MEMORY SWITCH                                               |

| 5.4       | USING THE BOOTSTRAP ROM                                     |

| SECTIO    | N 6 PIPELINE INTERLOCKS                                     |

| 6.1       | INTRODUCTION                                                |

| 6.2       | DATA ALU PIPELINE INTERLOCKS                                |

| 6.2.1     | What are the Data ALU Pipeline Interlocks?                  |

| 6.2.2     | Avoiding Data ALU Pipeline Interlocks                       |

| 6.2.2.1   | Code Reorder                                                |

| 6.2.2.2   | Loop Unrolling                                              |

| 6.2.2.2.1 |                                                             |

| 6.2.2.2.2 | 2 Unrolling in Memory Array Copy routine                    |

| 6.2.2.3   | Saving Interlocks by Using the TFR Instruction6-8           |

| 6.3       | ADDRESS GENERATION PIPELINE INTERLOCKS                      |

| 6.3.1     | What are the Address Generation Pipeline Interlocks6-9      |

| 6.3.2     | Avoiding Address Generation Pipeline Interlocks6-10         |

| 6.4       | STACK EXTENSION DELAYS                                      |

| 6.4.1     | Stack Extension Full/Empty Cases                            |

| 6.4.2     | Avoiding Stack Extension Delays                             |

| 6.5       | PROGRAM FLOW-CONTROL PIPELINE INTERLOCKS6-11                |

| 6.5.1     | What are the Program Flow-Control Pipeline Interlocks? 6-11 |

| 6.5.1.1   | MOVE to the Status Register (SR)                            |

| 6.5.1.2   | MOVE to the System Stack High/Low (SSH/SSL)6-12             |

| 6.5.1.3   | JMP to Last Addresses of a Do-Loop (LA or LA-1)6-12         |

| <ul> <li>6.5.1.4 RTI to Last Addresses of a Do-Loop (LA or L</li> <li>6.5.1.5 MOVE from the System Stack High (SSH)</li> <li>6.5.1.6 Conditional Instructions</li> </ul> |        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| 6.5.2 Avoiding Program Flow-Control Pipeline Interloc                                                                                                                    |        |

| 0.5.2 Avoiding Program Flow-Control Pipeline Interior                                                                                                                    | KS0-13 |

| SECTION 7 COMPACT OPCODE USE                                                                                                                                             |        |

| 7.1 INTRODUCTION                                                                                                                                                         |        |

| 7.2 CYCLE COUNT OF AN INSTRUCTION                                                                                                                                        |        |

| 7.2.1 Opening Small REP and DO Loops                                                                                                                                     |        |

| 7.2.2 Replacing Jumps with Conditional Execution Ins                                                                                                                     |        |

| 7.2.3 Inverting Condition in Conditional Jump Instructi                                                                                                                  |        |

| 7.3 ADDRESSING MODES                                                                                                                                                     |        |

| 7.3.1 Single Cycle Addressing Modes                                                                                                                                      |        |

| 7.3.2 Short Addressing Mode                                                                                                                                              |        |

| 7.3.3 Short Immediate Mode                                                                                                                                               |        |

| 7.3.4 Short Immediate Operands                                                                                                                                           |        |

| 7.3.5 Register Addressing                                                                                                                                                |        |

| 7.3.6 Word Count                                                                                                                                                         |        |

| 7.4 PERIPHERAL ADDRESSING                                                                                                                                                |        |

| 7.5 SPECIAL INSTRUCTIONS                                                                                                                                                 |        |

| 7.5.1 Dual Data Spaces                                                                                                                                                   |        |

| 7.5.2 Using the TFR instructions                                                                                                                                         |        |

| 7.5.3 Clearing Registers                                                                                                                                                 |        |

| APPENDIX A SAVING POWER                                                                                                                                                  | A-1    |

| A.1 INTRODUCTION                                                                                                                                                         | A-3    |

| A.2 LOW POWER MODES                                                                                                                                                      | A-3    |

| A.2.1 Wait Standby Mode                                                                                                                                                  | A-3    |

| A.2.2 Stop Standby Mode                                                                                                                                                  |        |

| A.2.3 Low-Power Clock Divider.                                                                                                                                           |        |

| A.3 DISABLING FUNCTIONAL BLOCKS                                                                                                                                          |        |

| APPENDIX B DEBUG AND TEST SUPPORT                                                                                                                                        | B-1    |

| B.1 INTRODUCTION                                                                                                                                                         |        |

| B.2 OnCE PORT FEATURES                                                                                                                                                   |        |

| B.3 JTAG PORT FEATURES                                                                                                                                                   |        |

| B.4   | ADDRESS TRACING B-5              |

|-------|----------------------------------|

| APPEN | DIX C USING THE PROFILER         |

| C.1   | SCOPE C-3                        |

| C.2   | CREATING A PROFILER C-3          |

| C.3   | THE PROFILING REPORT             |

| C.3.1 | Basic Report C-4                 |

| C.3.2 | Symbol Report C-4                |

| C.3.3 | Instruction Set Usage Report C-5 |

| C.3.4 | Code Coverage Report C-6         |

| C.3.5 | Basic Subroutine Report C-7      |

| C.3.6 | Subroutine Call Graph Report     |

| C.3.7 | Subroutine Dependency Report     |

| C.3.8 | Subroutine Call Report           |

| C.4   | USING THE PROFILE REPORT C-10    |

# LIST OF FIGURES

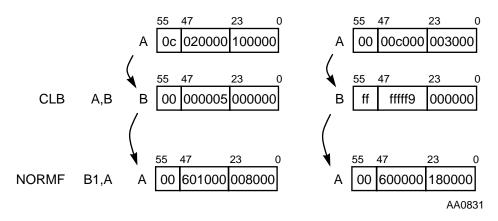

| Figure 2-1 | The Fast Normalization Operation for the DSP56300: 2-10                 |

|------------|-------------------------------------------------------------------------|

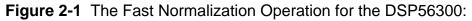

| Figure 2-2 | $48 \times 48$ -bit Multiplication with 48 Bits of the Result Kept 2-13 |

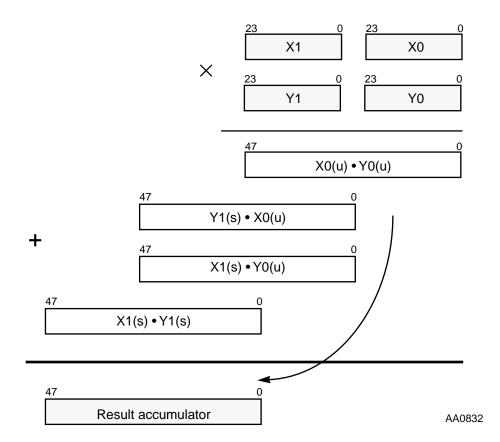

| Figure 3-1 | State of the Stack When IRQA Is Serviced                                |

| Figure 4-1 | DMA Addressing Modes for SCI Transmitters 4-11                          |

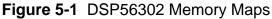

| Figure 5-1 | DSP56302 Memory Maps 5-11                                               |

# LIST OF TABLES

| Table 1-1 | New Instructions in DSP56300 and DSP566001-5                    |

|-----------|-----------------------------------------------------------------|

| Table 2-1 | Parallel Move Instructions                                      |

| Table 2-2 | Registers Used in Parallel XY Moves                             |

| Table 2-3 | Registers used in Long Addressing2-6                            |

| Table 2-4 | Data Operations Using Multi-shift                               |

| Table 2-5 | Bit Manipulation Instructions2-11                               |

| Table 3-1 | Implicit Stack Activity                                         |

| Table 3-2 | Registers Involved in Stack Extension Operation                 |

| Table 3-3 | Stack Status Information                                        |

| Table 3-4 | Options for Parallel Moves and Conditional Execution            |

| Table 3-5 | Instructions with Program Memory Arguments                      |

| Table 5-1 | Example for Cycle Count with Cache Enabled Versus Disabled .5-4 |

| Table 5-2 | Cycle Count Example With and Without Burst Mode                 |

# SECTION 1 INTRODUCTION

This application note describes how to optimize an application for the DSP56300 and DSP56600 DSP cores.

| 1.1 | OVERVIEW                       | .1-3 |

|-----|--------------------------------|------|

| 1.2 | DSP56300 CORE FAMILY           | .1-3 |

| 1.3 | DSP56600 CORE FAMILY           | .1-4 |

| 1.4 | ENHANCEMENTS OVER THE DSP56000 | .1-5 |

| 1.5 | APPLICATION NOTE STRUCTURE     | .1-7 |

## 1.1 OVERVIEW

The DSP56300 and DSP56600 are the new high-performance 24-bit and 16-bit cores in Motorola's family of Digital Signal Processors. They are based on the same pipeline structure. This structure is capable of executing an instruction on every clock cycle. At the same time these cores maintain a Harvard architecture and programming model similar to the older 24-bit DSP56000 core.

Code written for the DSP56300 or the DSP56600 may be based on previously developed code written for the DSP56000, or it may be new code that was developed initially for these new DSP cores. The intent of this document is to describe the new and the DSP56000-based features of the DSP56300 and DSP56600 cores in order to help the DSP software engineer to fully utilize the processor resources and generate an optimized application.

The document is a supplement to the detailed DSP56300 and DSP56600 Family Manuals.

## 1.2 DSP56300 CORE FAMILY

The DSP56300 core consists of the Expansion Port and DRAM Controller, Data ALU, Address Generation Unit, Instruction Cache Controller, Program Control Unit, DMA Controller, PLL Clock Oscillator, On-Chip Emulation (OnCE<sup>™</sup>) module, JTAG Test Access Port (TAP), and the Peripheral and Memory Expansion Busses. The main features of this high performance CPU include:

- Object code compatibility with the DSP56000 core

- Harvard Architecture with 24-bit instruction width and 24-bit data width

- Fully pipelined 24 × 24-bit parallel Multiplier-Accumulator (MAC)

- 56-bit parallel barrel shifter

- 16-bit Arithmetic mode of operation

- Highly parallel instruction set

- Position Independent Code (PIC) instruction-set support

- Unique DSP addressing modes

- On-chip memory-expandable hardware stack

- Nested hardware DO loops

#### **DSP56600 Core Family**

- Fast auto-return interrupts

- On-chip instruction cache

- On-chip concurrent six-channel DMA controller

- On-chip Phase Lock Loop (PLL)

- On-Chip Emulation (OnCE) module

- Program address tracing support

- JTAG port compatible with the IEEE 1149.1 Standard

The first members of DSP chips that use the DSP56300 core are the DSP56301, DSP56302, DSP56303, and DSP56305. The main differences between these derivatives are the size of the on-chip memory and the types of on-chip peripherals and hardware accelerators.

## 1.3 DSP56600 CORE FAMILY

The DSP56600 core consists of the External Memory Interface port, Data ALU, Address Generation Unit, Program Control Unit, PLL Clock Oscillator, On-Chip Emulation module, and the Peripheral and Memory Expansion Busses. The main differences between the DSP56300 and the DSP56600 cores are:

- The DSP56600 uses a 16-bit data bus, while the DSP56300 uses a 24-bit data bus.

- The Multiplier-Accumulator in the DSP56600 is  $16\times 16$  bit while the DSP56300 is  $24\times 24$  bit.

- The DSP56600's barrel shifter is 40 bits wide, while the DSP56300's barrel shifter is 56 bits wide.

- The DSP56600 does not include an instruction cache controller.

- The DSP56600 does not include a six-channel DMA controller.

The first members of DSP chips that use the DSP56600 core are the DSP56602 and the DSP56603. The main differences between these derivatives are the size of the on-chip memory and the types of on-chip peripherals.

## 1.4 ENHANCEMENTS OVER THE DSP56000

The DSP56300 and the DSP56600 include many architectural enhancements over the older generation 24-bit DSP family, the DSP56000. The following tables shortly describe these enhancements.

## 1.4.1 Instruction Set Enhancements

Many instructions were added in order to support the target applications of the new DSP cores:

| Opcodes         | Opcodes                       | Exist in<br>DSP56300? | Exist in<br>DSP56600? |

|-----------------|-------------------------------|-----------------------|-----------------------|

| MAX             | Transfer by Signed Value      |                       |                       |

| MAXM            | Transfer by Magnitude         |                       |                       |

| INSERT          | INSERT Bit Field              | $\checkmark$          |                       |

| EXTRACT         | Extract Bit Field             | $\checkmark$          |                       |

| EXTRACTU        | Extract Unsigned Bit Field    | $\checkmark$          |                       |

| MERGE           | Merge Two Half Words          | $\checkmark$          |                       |

| CLB             | Count Leading Bits            | $\checkmark$          |                       |

| NORMF           | Fast Accumulator Normalize    | $\checkmark$          |                       |

| CMPU            | Compare Unsigned              | $\checkmark$          |                       |

| Multibit Shifts | Arithmetic and Logical Shifts | $\checkmark$          |                       |

| MAC (uu)        | Unsigned MAC                  | $\checkmark$          |                       |

| DMAC            | Double-Precision MAC          | $\checkmark$          |                       |

| PLOCK           | Lock Cache Sector             |                       |                       |

| PUNLOCK         | Unlock Cache Sector           |                       |                       |

| PFLUSH          | Flush Cache Sectors           |                       |                       |

**Table 1-1**New Instructions in DSP56300 and DSP56600

#### Enhancements over the DSP56000

| Opcodes       | Opcodes                                   | Exist in<br>DSP56300? | Exist in<br>DSP56600? |

|---------------|-------------------------------------------|-----------------------|-----------------------|

| PFLUSHUN      | Flush Unlocked Cache Sectors              |                       |                       |

| PFREE         | free all locked sectors                   |                       |                       |

| LRA           | Load Relative Address                     |                       |                       |

| BSR / BScc    | Branch Subroutine<br>always/conditionally | $\checkmark$          | $\checkmark$          |

| BRA / Bcc     | Branch Target<br>always/conditionally     | $\checkmark$          | $\checkmark$          |

| BSset / BSclr | Branch Subroutine on Bit<br>Set/Clear     | $\checkmark$          |                       |

| BRset / BRclr | Branch Target on Bit Set/Clear            |                       |                       |

| DO Forever    | DO-Loop Forever                           |                       |                       |

| DOR Forever   | DO-Loop Forever Relative                  |                       |                       |

| BRKcc         | Break Loop Conditionally                  |                       |                       |

| TRAPcc        | TRAP Conditionally                        |                       |                       |

| IFcc          | Execute Instruction Conditionally         |                       |                       |

| VSL           | Viterbi Shift Left                        |                       |                       |

| Table 1-1         New Instructions in DSP56300 and DSP56600 (Continue) |

|------------------------------------------------------------------------|

|------------------------------------------------------------------------|

## 1.4.2 Architectural Enhancements

The programmer's model of the new DSP cores were also enhanced by the following:

- An instruction cache controller was added to the DSP56300. A Burst mode can be used to lower the off-chip traffic if external DRAMs are used.

- A six-channel DMA controller was added to the DSP56300.

- A true barrel shifter (56-bit in DSP56300 and 40-bit in DSP56600) was added to support multibit operations.

- The address and offset registers of the DSP56300 (R0–R7, N0–N7) were extended to 24-bit wide to support larger memory sizes.

- The DSP56300 has a 16-bit Arithmetic operating mode such that 16-bit exact algorithms can be implemented without any overhead.

- The DSP56300 and the DSP56600 have an on-chip Hardware Stack Extension mechanism that makes the Stack depth practically unlimited.

- Rounding and Saturation modes were added to the Arithmetic Unit of the DSP56300 and DSP56600.

- New addressing modes were added to the DSP56300 and DSP56600:

- Short/Long address displacement

- PC-Relative for Position Independent Code

- Short/Long Immediate operands to Arithmetic and Logical operations

## 1.5 APPLICATION NOTE STRUCTURE

This document has three main component parts:

- DSP56300 and DSP56600 features description and use

- Optimizing the code for best performance

- Appendices

#### **Application Note Structure**

## 1.5.1 DSP56300 and DSP56600 Features Description and Use

The first five sections in this application note describe all the architectural and instruction set enhancements in the new DSP cores and how they can be used to optimize applications.

- Section 1—Introduction

- DSP56300 core family

- DSP56600 core family

- Enhancements over the DSP56000

- Section 2—Data Operations

- How to organize data in memory to use parallel moves

- How to use the barrel shifter in various applications

- The benefit and use of the 16-bit Arithmetic support

- Some examples that show the benefit of few of the new arithmetic and logical instructions

- Section 3—Program Control

- How to use the on-chip hardware stack

- Benefit and usage of the Stack Extension

- Usage of the conditional arithmetic and logical instructions

- How to use the PC relative instructions for code relocation and saving of program words

- Using fast interrupts

- Section 4—Using the DMA

- How to reduce core MIPS by using the DMA

- How to service peripherals using the DMA

- How to use slow, inexpensive memory chips without loosing performance

- How to handle complex data structures by using the DMA

- Section 5—Instruction Cache and Other Memory Features

- Basic instruction cache tutorial

- Data organization for efficient sector allocation

#### **Application Note Structure**

- Sector locking for critical loops

- Flushing the cache after task switching.

- Burst mode for DRAMs

- Memory banks between program and data

- Using the bootstrap ROM

### 1.5.2 Optimizing the Code for Best Performance

The next two sections include general explanation of the various pipeline stall conditions and how they can be avoided in order to get faster execution times. In addition, some observations on the instruction set are included along with recommended usage for optimization purposes.

- Section 6—Pipeline Interlocks

- Description of the various types of interlocks

- Ways to avoid each type of interlock

- Program flow and control

- Understanding timing of conditional change of flow

- How to reorder code at the end of DO loops

- When to use the repeat instruction

- Section 7—Compact Opcode Use

- Cycle count of an instruction

- Addressing modes

- Word count of an instruction

- Peripheral addressing

#### **Application Note Structure**

### 1.5.3 Appendixes

There are three appendices providing supplementary information about application design guidelines:

- Appendix A—Saving Power

- Appendix B—Debug and Test Support

- Appendix C—Using the Profiler

<del>dsp</del>

# SECTION 2 DATA OPERATIONS

This section discusses important features and new additions to the DSP56000 core Data Arithmetic Unit.

| 2.1 | USING THE DUAL DATA PATHS               | 2-3   |

|-----|-----------------------------------------|-------|

| 2.2 | 16-BIT ARITHMETIC MODE (DSP56300 ONLY)  | 2-7   |

| 2.3 | THE MAX INSTRUCTION.                    | 2-8   |

| 2.4 | USING THE BARREL SHIFTER                | 2-9   |

| 2.5 | BIT MANIPULATION INSTRUCTIONS           | 2-11  |

| 2.6 | DOUBLE PRECISION ARITHMETIC             | 2-12  |

| 2.7 | USING LESS STRAIGHT-FORWARD INSTRUCTION | S2-14 |

## 2.1 USING THE DUAL DATA PATHS

The DSP56300/DSP56600 core can execute a new instruction every clock cycle. This performance can be used efficiently only if data can be fed to the core and its results moved out of it at a sufficient rate. The DSP56300/DSP56600 core's highly parallel architecture was designed to allow performing the following operations in parallel:

- Data ALU instruction execution

- Up to two parallel moves of data operands or results to/from the Data ALU

- Up to two address calculations for the next instruction

- Fetch of next instruction

The two data paths (the X bus and Y bus) connect two data memory sections (the X memory and the Y memory) with the Data ALU. This parallelism allows the DSP56300/DSP56600 core to execute more effectively, for example, executing a FIR tap in one clock cycle:

| Opcod | e + operands | Data for next<br>iteration via the X<br>data bus +<br>increment pointer | Data for next<br>iteration via the Y<br>data bus +<br>increment pointer |

|-------|--------------|-------------------------------------------------------------------------|-------------------------------------------------------------------------|

| mac   | x0,y0,a      | x:(r0)+,x0                                                              | y:(r4)+,y0                                                              |

Data that is moved in parallel *into* a register is ready for use in the next instruction, and does not interfere with the current value of the operands in execution. In the above example, the values of X0 and Y0 are updated only after the "MAC" instruction uses its operands. Similarly, data moved *from* a register will hold the data before it was updated as a result of execution. For example:

mac x0,y0,a a,x:(r0)+

The value of the accumulator A that is moved to the memory is the value before its update by the "MAC" instruction.

There are two ways to generate the operand addresses for parallel moves:

• **XY addressing**—Two address registers are used independently, one generating an operand address for the X memory and the other for the Y memory. The FIR example above is of this kind. The address registers must be of different "banks", meaning that if an address register R0–3 is used for one data field, an address register R4–7 should be used for the other data field. No absolute addresses are allowed in this mode.

#### **Using the Dual Data Paths**

• **Long addressing**—One address register or absolute address is used to generate the address for both the X memory and the Y memory. For example:

mac x0,x1,a l:(r0)+,X

The syntax L:(R0)+,X is equivalent to moving X:(R0) to X0 and Y:(R0) to X1, then incrementing R0. The name "long addressing" refers to the fact that such addressing enables to access two data registers as if they were one 48-bit long register.

**Note:** Not all the DSP56300/DSP56600 instructions support parallel moves. In general, the instructions that do are a subset of the arithmetic instructions. The full list of these instructions appears in **Table 2-1**.

| Instruction                              | Mnemonic | Relevant Opcode<br>variants  |

|------------------------------------------|----------|------------------------------|

| Absolute Value                           | ABS      |                              |

| Add Long with Carry                      | ADC      |                              |

| Add                                      | ADD      | Non-immediate                |

| Shift Left and Add Accumulators          | ADDL     |                              |

| Shift Right and Add Accumulators         | ADDR     |                              |

| Logical AND                              | AND      | Non-immediate                |

| Arithmetic Shift Accumulator Left        | ASL      | Single bit,<br>non-immediate |

| Arithmetic Shift Accumulator Right       | ASR      | Single bit,<br>non-immediate |

| Clear Accumulator                        | CLR      |                              |

| Compare                                  | СМР      | Non-immediate                |

| Compare Magnitude                        | СМРМ     |                              |

| Logical Exclusive OR                     | EOR      | Non-immediate                |

| Logical Shift Left                       | LSR      |                              |

| Logical Shift Right                      | LSR      |                              |

| Multiply and Accumulate                  | MAC      | Signed operands              |

| Signed Multiply and Accumulate and Round | MACR     |                              |

Table 2-1

Parallel Move Instructions

| Instruction                           | Mnemonic | Relevant Opcode<br>variants |

|---------------------------------------|----------|-----------------------------|

| Transfer by Signed Value              | MAX      |                             |

| Transfer by Magnitude                 | MAXM     |                             |

| Signed Multiply                       | MPY      |                             |

| Signed Multiply and Round             | MPYR     |                             |

| Negate Accumulator                    | NEG      |                             |

| Logical Complement                    | NOT      |                             |

| Logical Inclusive OR                  | OR       | Non-immediate               |

| Round Accumulator                     | RND      |                             |

| Rotate Left                           | ROL      |                             |

| Rotate Right                          | ROR      |                             |

| Subtract Long with Carry              | SBC      |                             |

| Subtract                              | SUB      | Non-immediate               |

| Shift Right and Subtract Accumulators | SUBR     |                             |

| Shift Left and Subtract Accumulators  | SUBL     |                             |

| Transfer Data ALU Register            | TFR      |                             |

| Test Accumulators                     | TST      |                             |

Table 2-1

Parallel Move Instructions (Continued)

Parallel moves are also restricted in their use of registers as source and destination to a part of the Data ALU registers. The register options available for XY Addressing are listed in **Table 2-2** on page 2-6. Any register in the X field column can appear with any register in the Y column, with the obvious exception of updating the same accumulator from both the X and Y fields.

#### **Using the Dual Data Paths**

| X Field | Y Field | Comments                                                                                                |

|---------|---------|---------------------------------------------------------------------------------------------------------|

| X0      | Y0      |                                                                                                         |

| X1      | Y1      |                                                                                                         |

| A       | A       | As source: undergoes shifting and limiting<br>As destination: A2/B2 sign extended, A0/B0<br>zero filled |

| В       | В       | - Zero imeu                                                                                             |

**Table 2-2**Registers Used in Parallel XY Moves

The register options available for long addressing are listed in Table 2-3.

**Note:** Some syntax combinations of the accumulators differ only in shifting/limiting (if the register is the source) or implicit register updates (if they are destination). For example, compare "A10" with "A". In the "AB" and "BA" combinations, each accumulator has same behavior as a regular move, such as:

move a, x:(r0)+.

| Table 2-3 | Registers used in | n Long Addressing |

|-----------|-------------------|-------------------|

|-----------|-------------------|-------------------|

| Assembler<br>Syntax | X Field | Y Field | Shifting/<br>Limiting if<br>source | Sign<br>extension if<br>destination | Zero fill if destination |

|---------------------|---------|---------|------------------------------------|-------------------------------------|--------------------------|

| A10                 | A1      | A0      | no                                 | no                                  | no                       |

| B10                 | B1      | B0      | no                                 | no                                  | no                       |

| X                   | X1      | X0      | no                                 | no                                  | no                       |

| Y                   | Y1      | Y0      | no                                 | no                                  | no                       |

| А                   | A1      | A0      | yes                                | A2                                  | no                       |

| В                   | B1      | B0      | yes                                | B2                                  | no                       |

| AB                  | A1      | B1      | yes                                | A2,B2                               | A0,B0                    |

| BA                  | B1      | A1      | yes                                | A2,B2                               | A0,B0                    |

Keeping those restrictions in mind, writing a critical data processing loop efficiently should be done after careful planning of register use and the data allocations in the memory space according to the parallelism possible in the calculation at hand. For example, in the FIR tap calculation given above, the coefficients occupy the X memory with pointer R0, and the data buffer occupies the Y memory with pointer R4 (or vice versa). In other cases, the division may not be so straight forward. For example, in many algorithms involving complex numbers, the efficient solution uses one memory space for the real part of the numbers, while the other memory space is

used for the imaginary part. In those examples, there is a logical separating criterion between the data placed in the X and Y memories. In many applications, however, variables may be split up between the X and Y memories based on no other criterion than the ability to transfer them in parallel to the core at the time they are called for by the algorithm.

## 2.2 16-BIT ARITHMETIC MODE (DSP56300 ONLY)

The 16-bit Arithmetic mode causes the Data ALU to use only 16 bits of the 24-bit data in transfers and calculations, allowing use of the DSP56300 as a 16-bit data processor. The 16-bit data is right aligned in the memory, but left aligned in data registers (in order to comply with the fractional numerical representation convention). The hardware makes the proper alignments and shifts in data transfers and operations, so the user does not have any overhead when using this mode. This includes the accumulators, which in the 16-bit mode are 40-bits wide (in accumulator A, for example, A0 and A1 are 16 bits each, and the extension A2 remains 8 bits wide). All data operations are properly defined to give correct 16-bit arithmetic results. For more information on the 16-bit Arithmetic mode, see **Section 3.4** in the *DSP56300 Family Manual* for a general description, and **Appendix A** in the same manual (Instruction set) for a detailed description on the functionality of each instruction affected by this mode.

Using the 16-bit Arithmetic mode may give many advantages from a general system point of view:

- Ability to implement a 16-bit exact algorithms. The DSP56300 also supports saturation arithmetic and flexible rounding modes required by some standards.

- 16-bit exact algorithms exact algorithms could be integrated easily into a software system that also includes 24-bit exact routines. Changing of the arithmetic mode can be done "on the fly".

The 16-bit Arithmetic mode is activated by setting the SA bit in the Status Register (SR).

**Note:** This is not the same as the 16-bit Compatibility mode (activated by setting the SC bit in the Status Register). The 16-bit Compatibility mode affects address registers and address calculations and enables object code compatibility with the DSP56000 family (which uses 16-bit wide addresses).

**The MAX Instruction**

## 2.3 THE MAX INSTRUCTION

MAX is a new instruction in the DSP56300 and DSP56600 instruction set that can used to enhance performance in critical data operation loops. For example,

max a,b

compares the two accumulators, and places the bigger value in the destination accumulator (accumulator B). The MAXM instruction does the same thing, only it transfers the bigger absolute value to the destination .

Like other data operations, this instruction is effectively executed in one clock cycle. Previously such functionality was achieved in two cycles, for example:

> cmp a,b tlt a,b

**Note:** This example differs from the MAX functionality only in the status update.

The MAXM instruction can be used to find the largest number in an array of values, in  $N\,+\,10$  clock cycles:

|      |            |           | <u>cycles</u> |

|------|------------|-----------|---------------|

| move | #DATA_POIN | TER,r0    | 1             |

| clr  | b          | x:(r0)+,a | 1+3 interlock |

| rep  | #n         |           | 5             |

| maxm | a,b        | x:(r0)+,a | N             |

The initialization of R0 takes 4 cycles due to an address register interlock. The three cycle stall could be used for other useful instructions (see **Section 6.3.1** on page 6-9).

**Note:** The MAX and MAXM instructions can only be used with fixed operands (A as first source, B as destination). There is no opcode for MAX B,A.

## 2.4 USING THE BARREL SHIFTER

The DSP56300/DSP56600 includes a true barrel shifter that can be used for multi-bit data shifts. The instructions that use the barrel shifter are listed in **Table 2-4**.

| Mnemonic | Function                  | Operands                                     |                                           |

|----------|---------------------------|----------------------------------------------|-------------------------------------------|

| ASL      | Arithmetic<br>Shift Left  | C,S,D<br>C: number of shift bits             | 6-bit immediate, or                       |

| ASR      | Arithmetic<br>Shift Right | S: source of shift<br>D: destination         | X0,X1,Y0,Y1,A1,B1<br>A,B<br>A,B           |

| LSL      | Logical<br>Shift Left     | C,D<br>S: number of shift bits               | 5 -bit immediate, or<br>X0,X1,Y0,Y1,A1,B1 |

| LSR      | Logical<br>Shift Right    | D: source & destination                      | A,B                                       |

| NORMF    | Fast<br>Normalizat<br>ion | C,D<br>C: control of shift<br>D: destination | X0,X1,Y0,Y1,A1,B1<br>A,B                  |

Table 2-4

Data Operations Using Multi-shift

The logical shifts operate on the most significant register (A1/B1) of the accumulator destination (the accumulator extension and LS register are not affected). The arithmetic shifts operate on the full length of the source and destination accumulators, sign extending when applicable. In addition to the multi-bit shifts, there are also four respective single bit shift instructions that allow parallel moves (the multi-bit shifts do not allow them).

The NORMF instruction deserves special attention, as it can effectively replace several instructions in many common algorithms. The NORMF instruction arithmetically shifts the data from the destination accumulator (D) in the direction and amount specified by the first operand (C). If C > 0, then D is arithmetically shifted to the left by C bits. If C < 0, then D is arithmetically shifted to the right by C bits. The operand C should normally be prepared by the CLB instruction (Count Leading Bits). The instruction pair:

will normalize A, so that in the DSP56300 it's leading one or zero will be shifted to Bit 46 in the accumulator. If |A| > 1 (meaning that it spilled to the extension A2), then CLB returns a positive number (between 1 and 8). If |A| < 1, CLB returns a zero or a negative number (between -47 and 0). The two cases in **Figure 2-1** exemplify the normalization operation for the DSP56300. The NORMF at the 56600 core operates similarly, with adjustments to the different accumulator length.

#### **Using the Barrel Shifter**

The NORMF instruction can be used to keep data dynamically bounded (maximizing calculation accuracy), implement floating point routines, normalizing data blocks, and more. For example, consider the following routine for efficiently normalizing a data block. The first pass finds the normalization factor (using MAXM and CLB) and the second pass performed the normalization itself.

```

;NORMALIZING A DATA BLOCK

;X:base - base address of un-normalized data.

;Y:base - base address of normalized data.

;N: data block size

;cycle count

; 1

#base,r0

move

#base,r1

; 1

move

x:(r0)+,a

; 1 + 2 pointer interlock

clr b

#Ν

; 5

rep

x:(r0)+,a ; 1 x N

maxm

a,b

rl,r0

; 1

move

; 1

clb

b,a

move

#base-1,r4

; 1

move

al,xl

; 1

move

x:(r0)+,a

; 1

do

#N/2,_ENDLOOP

; 5

x:(r0)+,b b,y:(r4)+ ; 1 x N/2

move

normf

xl,a

; 1 \ge N/2

normf

x1,b

; 1 \ge N/2

x:(r0)+,a a,y:(r4)+ ; 1 x N/2

move

ENDLOOP

b,y:(r4)+

; 1

move

;Total: 3N + 22

```

## 2.5 BIT MANIPULATION INSTRUCTIONS

The data ALU has a special Bit Field Unit (BFU) that supports powerful bit-manipulation instructions that enable an application to insert/ extract a bit field of varying width and position to/from an accumulator. These instructions are summarized in **Table 2-5**.

| Mnemonic | Function                                       | Operands                                                                                   |                                                                       |

|----------|------------------------------------------------|--------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|

| EXTRACT  | Extract a bit<br>field                         | C,S,D<br>C: Source field position &<br>width                                               | 6-bit immediate, or:<br>X0,X1,Y0,Y1,A1,B1                             |

| EXTRACTU | Extract an<br>unsigned bit<br>field            | S: Data source<br>D: Data Destination                                                      | A,B<br>A,B                                                            |

| INSERT   | Insert a bit<br>field                          | C,S,D<br>C: Destination field position &<br>width<br>S: Data source<br>D: Data Destination | 6-bit immediate, or:<br>X0,X1,Y0,Y1,A1,B1<br>X0,X1,Y0,Y1,A1,B1<br>A,B |

| MERGE    | Merge field &<br>width data to<br>one register | S,D<br>S: Width Data Source.<br>D: Position data source &<br>merging destination           | X0,X1,Y0,Y1,A1,B1<br>A,B                                              |

**Table 2-5** Bit Manipulation Instructions

The EXTRACT(U) and INSERT instruction use a control operand (C) that specifies the bit field to be extracted or inserted. The bit field is specified by its width (in bits) and its starting position (in bits, relative to the LSB of the accumulator). The width and position values could be prepared using the MERGE instruction, which merges data from two data registers in the appropriate positions for future use as a control operand for EXTRACT and INSERT.

The EXTRACT instruction extracts the specified field, right-aligns it, and sign-extends it in the destination accumulator. The EXTRACTU instruction does the same, but does not sign-extend the result. The INSERT instruction takes a right-aligned field of the specified width from the source register and places it in the specified position in the destination accumulator.

Detailed examples of the use of these instructions for parsing and creating a data stream, and parsing Hoffman code data stream can be found in **Appendix C** of the *DSP56300* and *DSP56600 Family Manuals*.

#### **Double Precision Arithmetic**

## 2.6 DOUBLE PRECISION ARITHMETIC

The DSP56300/DSP56600 has instructions to help the programmer implement arithmetic operations if the operands are longer than standard accumulator size. Using these instructions can help achieve enhanced precision with minimum software overhead. The examples below relate to the DSP56300 core register size (24 bits for data registers, 56 bits for an accumulator), but can be adapted for the DSP56600 core by changing the register size accordingly.

The normal ADD and SUB instructions can add a 48-bit operand (X1:X0, for example) to an accumulator, and, of course, can add a 56-bit accumulator to another. Furthermore, the user may use ADC (Add long with Carry) or SBC (Subtract long with Carry), which adds (subtracts) a 48-bit operand to (from) an accumulator with a carry (borrow) bit from a previous calculation.

The normal MPY (multiply) or MAC (multiply-accumulate) instructions multiply two 24-bit operands to give a 48-bit result. Implementing  $32 \times 32$ -bit or  $48 \times 48$ -bit multiplication requires four  $24 \times 24$  multiplications, and some shifting and addition operations. The DSP56300 and DSP56600 specialized instructions can help reducing these extra operations to a minimum. Consider for example  $48 \times 48$  multiplication, where only the forty-eight Most Significant Bits are needed, and the forty-eight Least Significant Bits discarded. **Figure 2-2** on page 2-13 illustrates the required operations.

#### **Double Precision Arithmetic**

Figure 2-2  $48 \times 48$ -bit Multiplication with 48 Bits of the Result Kept.

The (U) means an unsigned operand, and the (S) a signed operand. The following four instructions perform the operation in full:

;48x48 bit multiplication with 48 bit result. ;first operand - X1:X0 ;second operand -Y1:y0 ;result is in accumulator A. x0,y0,a x0(u) \* y0 (u) -> a mpyuu ; y1,x0,a yl(s) \* x0 (u) -> a dmacsu ;a>>24 + x1,y0,a x1(s) \* y0 (u) -> a macsu ;a + dmacss x1,y1,a ;a>>24 + x1(s) \* y1 (s) -> a

#### **Using Less Straight-Forward Instructions**

The features that help in this case are:

- · The ability to specify combinations of signed and unsigned operands

- The 24-bit right arithmetic shifting inherent in the DMAC instruction

Using these instruction combinations, and others, enables the programmer to build other multi-register arithmetic operations. The user is referred to **Appendix A** of the *DSP56300* and *DSP56600 Family Manuals* for the full documentation of the various instruction options.

### 2.7 USING LESS STRAIGHT-FORWARD INSTRUCTIONS

The rich instruction set includes many instructions that are in fact combinations of smaller atomic operations. Among these instructions are ADDL, ADDR, MAX, EXTRACT, INSERT, MACR, and MPYR.

A good example of using some of these less straight-forward instructions is the SQROOT routine. The following is a straight forward implementation of that routine:

```

sqroot

;determine 2nd term and add contribution

asr

а

sub

#$4000,a

move

a1,x0

sub

#$8000,a

;a = L Templ

;x0 = swTemp

;a = L_Templ

;determine 3rd term and add contribution

mpy -x0,x0,b

ib = swTemp ^ 2

move

bl,xl

;x1 = swTemp2

asr

b

;a = L_Temp0

add b,a

;determine 4th term and add contribution

mpy -x0,x1,b

ib = swTemp x swTemp2

b1,y0

;y0 = swTemp3

move

asr

b

add

b,a

;a = L_Templ

;determine partial 5th term

mpyr x0,y0,b

b,yl

;y1=swTemp4

move

;determine partial 6th term

mpy -x1,y0,b

rnd

b

move b,xl

; determine 5th term and add its contribution

-#$5000,y1,b ; b = 0 - (swTemp4 x

mpy

;TERMS MULTIPLIER)

add

b,a

; determine 6th term and add its contribution

macr #$7000,x1,a ;swSqrtOut is contained in a

rts

```

#### **Using Less Straight-Forward Instructions**

In this example, the ADDR and MPYR instructions replace a few instructions in the original code causing some reduction in total cycle count:

|                                          | sqroot                   |                                                                                        |                                                                               |                                                           |                                                       |

|------------------------------------------|--------------------------|----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-----------------------------------------------------------|-------------------------------------------------------|

| ;determine 2nd term and add contribution |                          |                                                                                        |                                                                               |                                                           |                                                       |

|                                          |                          | asr                                                                                    | a                                                                             | #<\$40,yl                                                 |                                                       |

|                                          |                          | sub                                                                                    | yl,a                                                                          | #<\$80,x1                                                 | ;a = L_Temp1                                          |

|                                          |                          | sub                                                                                    | xl,a                                                                          | al,x0                                                     | ;a = L_Temp1,x0 = swTemp                              |

|                                          |                          | 2 . 1                                                                                  | J . JJ                                                                        | 1                                                         |                                                       |

|                                          | determine                | 3rd term an                                                                            |                                                                               |                                                           |                                                       |

|                                          |                          | mpy                                                                                    | -x0,x0,b                                                                      |                                                           | ;b = swTemp ^ 2                                       |

|                                          |                          | addr                                                                                   | a,b                                                                           | b1,x1                                                     | $x1 = swTemp2, b = L_Temp0$                           |

|                                          | ;determine               | 4th term an                                                                            | d add contr                                                                   | ibution                                                   |                                                       |

|                                          |                          | mpy                                                                                    | -x0,x1,a                                                                      | #<\$70,yl                                                 | ;a = swTemp x swTemp2                                 |

|                                          |                          |                                                                                        | -                                                                             |                                                           |                                                       |

|                                          |                          | addr                                                                                   | b,a                                                                           | a1,y0                                                     | ;y0 = swTemp3, a = L_Temp1                            |

|                                          | ;determine               | addr<br>partial 5th                                                                    | -                                                                             | al,y0                                                     | ; $y0 = swTemp3$ , $a = L_Temp1$                      |

|                                          | ;determine               | partial 5th                                                                            | -                                                                             |                                                           | ;y0 = swTemp3, a = L_Temp1                            |

|                                          |                          | partial 5th                                                                            | term<br>x0,y0,b                                                               |                                                           | ;y0 = swTemp3, a = L_Temp1                            |

|                                          |                          | partial 5th<br>mpyr<br>partial 6th                                                     | x0,y0,b<br>term                                                               |                                                           |                                                       |

|                                          | ;determine               | partial 5th<br>mpyr<br>partial 6th<br><b>mpyr</b>                                      | term<br>x0,y0,b<br>term<br><b>-x1,y0,b</b>                                    | #<\$50,x0                                                 |                                                       |

|                                          | ;determine               | partial 5th<br>mpyr<br>partial 6th<br><b>mpyr</b><br>5th term an                       | term<br>x0,y0,b<br>term<br>-x1,y0,b<br>d add its c                            | #<\$50,x0<br><b>b,x1</b><br>ontribution                   |                                                       |

|                                          | ;determine               | partial 5th<br>mpyr<br>partial 6th<br><b>mpyr</b><br>5th term an                       | term<br>x0,y0,b<br>term<br>-x1,y0,b<br>d add its c                            | #<\$50,x0<br><b>b,x1</b><br>ontribution                   | ;yl=swTemp4                                           |

|                                          | ;determine<br>;determine | partial 5th<br>mpyr<br>partial 6th<br><b>mpyr</b><br>5th term an<br>mac                | term<br>x0,y0,b<br>term<br>-x1,y0,b<br>d add its c<br>-x0,x1,a                | #<\$50,x0<br><b>b,x1</b><br>ontribution                   | ;yl=swTemp4<br>;b = -(swTemp4 x                       |

|                                          | ;determine<br>;determine | partial 5th<br>mpyr<br>partial 6th<br><b>mpyr</b><br>5th term an<br>mac                | term<br>x0,y0,b<br>term<br>-x1,y0,b<br>d add its c<br>-x0,x1,a<br>d add its c | <pre>#&lt;\$50,x0 b,x1 ontribution b,x1 ontribution</pre> | ;yl=swTemp4<br>;b = -(swTemp4 x                       |

|                                          | ;determine<br>;determine | partial 5th<br>mpyr<br>partial 6th<br><b>mpyr</b><br>5th term an<br>mac<br>6th term an | term<br>x0,y0,b<br>term<br>-x1,y0,b<br>d add its c<br>-x0,x1,a<br>d add its c | <pre>#&lt;\$50,x0 b,x1 ontribution b,x1 ontribution</pre> | ;yl=swTemp4<br>;b = -(swTemp4 x<br>;TERMS_MULTIPLIER) |

<del>dsp</del>

## Using Less Straight-Forward Instructions

# SECTION 3 PROGRAM CONTROL

This section discusses important program control features and new additions.

| 3.1 | HARDWARE LOOPS                            | 3-3 |

|-----|-------------------------------------------|-----|

| 3.2 | THE HARDWARE STACK                        | 3-5 |

| 3.3 | USING THE STACK EXTENSION                 | 3-8 |

| 3.4 | TASK SWITCHING WITH THE STACK EXTENSION3- | 11  |

| 3.5 | CONDITIONAL DATA ALU INSTRUCTIONS         | 12  |

| 3.6 | PC RELATIVE INSTRUCTIONS                  | 14  |

| 3.7 | USING FAST INTERRUPTS                     | 17  |

## 3.1 HARDWARE LOOPS

Hardware looping is one of the strongest features of the DSP56300/DSP56600 core families. Loop counter management and end-of-loop testing is done by hardware in parallel to instruction execution, thus saving execution time of otherwise needed control software. This enables the user to muster more performance in critical loops, and also makes program writing more close to high-level languages. Consider the following C code example:

A straight forward assembly implementation of the main loop of the code may look like this:

|           | move | #MEMORY_AREA,r0 |            |

|-----------|------|-----------------|------------|

|           | clr  | a               | #100,b     |

|           | move | x:(r0)+,x0      |            |

| _LOOP_TOP |      |                 |            |

|           | add  | x0,a            | x:(r0)+,x0 |

|           | sub  | #1,b            |            |

|           | tst  | b               |            |

|           | jne  | _LOOP_TOP       |            |

Using hardware looping, this code looks like:

|          | move | #MEMORY_AREA,r0 |            |

|----------|------|-----------------|------------|

|          | clr  | a               | x:(r0)+,x0 |

|          |      |                 |            |

|          | do   | #100,_LOOI      | P_END      |

|          | add  | x0,a            | x:(r0)+,x0 |

| LOOP END |      |                 |            |

There is more to hardware loops than easy programming. The loop control hardware is optimized for maximum pipeline efficiency. There is no stall between loop iterations; all comparisons and loop counter arithmetic are done in parallel to instruction execution. It is important to know that after the loop is initialized (execution of the DO instruction), the instructions in the loop are fetched and executed in sequence. From the pipeline's point of view, there is no difference between the code in the last example and the "ADD" instruction written 100 times in sequence.

A common programming technique is known as "loop unrolling", in which a high-level loop is replaced by the inner loop code, repeated N times, thus saving the time needed to decrement the counter, test for the end of the loop, and jumping back to the top. From the above explanation, it follows that this technique is less efficient in the DSP56300/DSP56600 family—the hardware executes loops normally at the same speed as unrolled code (except for the initializing DO instruction itself, which

### **Program Control**

### Hardware Loops

takes 5 cycles). Loops should be unrolled only when the 5-cycle initialization is meaningful in comparison to the total loop length, especially if this loop is nested in another loop and the 5-cycle delay is multiplied. See the example in **Section 7.2.1** on page 7-3.

High-level "*for*" loops are normally implemented in assembly with the DO instruction. The instructions DO FOREVER and BRKcc (break on condition) may be used to implement high-level "*while*" or "*repeat*" loops efficiently. The following example is a wave generator that sends data to a peripheral (Host Interface HI08 in this example) until a hardware interrupt (IRQA) sets a flag, signalling the end of the loop. The core drives the HI08 transmitter by polling the HTDE (Host Transmitter Data Empty) bit in the HI08 status register. The C high-level code may look like:

while (!flag){

```

al = next_wave_value();

wait_until_transmitter_empty();

send_data(al);

```

```

}

```

and in Assembler:

|          | org        | p:I_IRQA                                              | ;IRQA_ interrupt vector       |

|----------|------------|-------------------------------------------------------|-------------------------------|

|          | bset       | #0,x: <flag< td=""><td>;occupies 2 words</td></flag<> | ;occupies 2 words             |

|          | org        | p:MAIN_PROGRAM                                        |                               |

|          |            |                                                       |                               |

|          | move       | #0,x0                                                 |                               |

|          | move       | x0,x:FLAG                                             | ;clear FLAG register          |

|          | bclr       | #0,sr                                                 | ;clear carry bit              |

|          |            |                                                       |                               |

|          | do forever | ,_END_LOOP                                            |                               |

|          | brkcs      |                                                       | ;break loop if carry bit set  |

|          | jsr        | NEXT_WAVE_VALUE                                       | ;new value returned in al     |

| _WAIT    |            |                                                       |                               |

|          | jclr       | #0,x:M_SSR ,_WAIT                                     | ;wait until transmitter empty |

|          | btst       | #0,x:FLAG                                             | ;set carry by flag value      |

|          | movep      | al,x:M_HTX                                            | ;transmit data to host.       |

| END LOOP |            |                                                       |                               |

**Note:** The BRKcc instruction has the same functionality as the C language "break", (i.e., terminating the loop and resuming execution after the end of the loop). A similar instruction is the ENDDO instruction, which exits the loop after finishing the current loop iteration. ENDDO is not a conditional instruction, therefore normal use generally includes testing a condition and skipping the ENDDO instruction accordingly.

The following example counts the number of bits in A1, terminating if the register turns 0 before the full 24 iterations.

```

clr

b

#0,x0

#24,_END_LOOP

do

tst

а

_CONT

ine

enddo

CONT

lsr

а

x0,b

addc

END LOOP

```

Bit 0 of the result (B1) could be used as the parity of the original operand (A1).

**Note:** Both ENDDO and BRKcc have sequence restrictions, as shown in the *DSP56300* and *DSP56600 Family Manuals*, **Appendix B**.

## 3.2 THE HARDWARE STACK

The DSP56300/DSP56600 hardware stack enables the user to nest DO loops and subroutines (called by software or interrupts) with no software overhead. With the Stack Extension enabled, the hardware stack can accommodate an unlimited nesting level of DO loops, JSRs, or a combination of them. The only overhead of a very deep nesting level is some additional cycles required to copy data to or from the stack extension memory. Examples of stack extension use are given in **Section 3.3** on page 3-8.

The hardware stack mechanism works in parallel to opcode execution, thus saving execution time, as well as software overhead compared to conventional software stacks. These advantages make the DSP56300/DSP56600 especially suitable for multi-tasking, and running real-time operating systems and program code generated from high-level languages.

The current stack location is pointed by the SP register. A single stack location can store two words, referred to as occupying the "high" and "low" halves of the stack location. The current stack locations pointed by SP (top of stack) are named SSH and SSL, respectively. A single "*push*" or "*pop*" activity can access the SSH and SSL concurrently. Stack activities are triggered implicitly at execution of specialized instruction or fulfillment of certain conditions. These activities are summarized in **Table 3-1**.

**Note:** The table only summarizes the effect of those instructions on the stack. Some instructions update other registers as well. For complete information on an instruction, refer to **Appendix A** in the *DSP56300* and *DSP56600 Family Manuals*.

### The Hardware Stack

| Activity                        | Triggered by Instruction or Condition                                                                     | Implicit Stack Actions<br>Taken                                                    |

|---------------------------------|-----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| jump to subroutine              | JSR, BSR<br>JScc, BScc (condition true)<br>JSCLR, BSCLR (condition true)<br>JSSET, BSSET (condition true) | SP: = SP + 1;<br>SSH: = PC; SSL: = SR.                                             |

| return from<br>subroutine       | RTS                                                                                                       | PC: = SSH<br>SP: = SP - 1                                                          |

| return from long<br>interrupt   | RTI                                                                                                       | PC: = SSH; SR: = SSL<br>SP: = SP - 1                                               |

| move to SSH                     | MOVEC <source/> ,SSH                                                                                      | SP: = SP + 1<br>SSH: = <source/>                                                   |

| move from SSH                   | MOVEC SSH, <destination></destination>                                                                    | <destination>: = SSH<br/>SP: = SP - 1</destination>                                |

| enter DO loop                   | DO<br>DOR<br>DO FOREVER<br>DOR FOREVER                                                                    | SP: = SP + 1<br>SSH: = LA, SSL: = LC<br>SP: = SP + 1<br>SSH: = PC, SSL: = SR       |

| exit DO loop at last<br>address | (LF bit set and FV bit clear<br>and fetched address = LA<br>and LC = 0).<br>ENDDO                         | SR: = SSL<br>SP: = SP - 1<br>LA: = SSH, LC: = SSL<br>SP: = SP - 1                  |

| exit DO loop<br>immediately     | BRKcc (condition true)                                                                                    | PC: = LA + 1;<br>SR: = SSL<br>SP: = SP - 1<br>LA: = SSH, LC: = SSL<br>SP: = SP - 1 |

**Table 3-1** Implicit Stack Activity

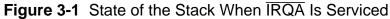

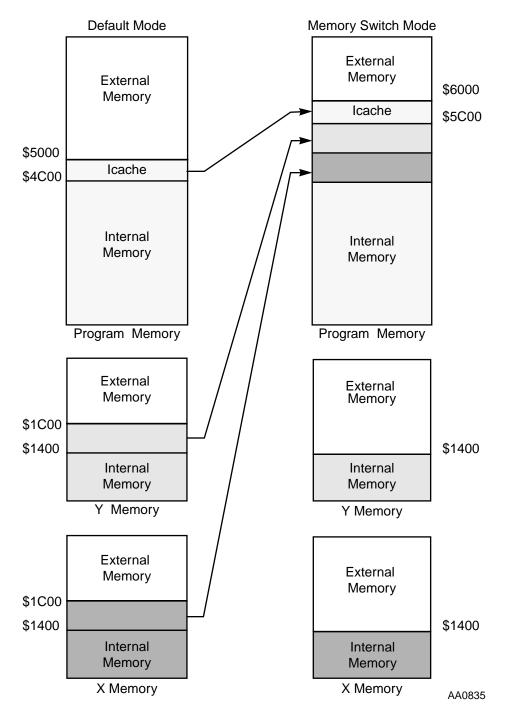

The next example shows loop and subroutine nesting. **Figure 3-1** shows the state of the stack at the time the fast interrupt is executing (label I\_IRQA, that enters execution when PC =\$000529). The first DO instruction pushes the existing data on LA and LC (0 and \$FFFFFF, respectively, in this example).

**Note:** A fast interrupt does not effect the stack. Only long interrupts (that have a subroutine call) push data into the stack. Had IRQA been a long interrupt, another push would have been done, the saved values being SSH:\$529 (PC) and SSL: \$C18300 (SR). The different values of the LF and FV bits in SR are saved as the nesting proceeds (no loop, finite loop, infinite loop).

#### The Hardware Stack

```

;example of loop and subroutine nesting.

```

```

; interrupt definitions: fast interrupt from IRQA_

org

p:I_IRQA

bset

#5,x:(r0)

nop

. . .

;program area

;after jsr execution, sp == 1,

; execution continues at _SUB1

_SUB1

jsr

. . .

. . .

. . .

_SUB1

do

#6,_LOOP1

; after instruction, sp == 3

. . .

forever,_LOOP2

;after instruction, sp == 5

do

btst

#0,x:(r0)

brkcs

; if condition true, resume at

; LOOP2, and sp == 3.

move

a0,x:(r1)+

;<---- irqA occurs here.

al,x:(r1)+

move

move

a2,x:(r1)+

_LOOP2

;after loop is braked, sp == 3

nop

. . .

nop

```

### **Using the Stack Extension**

| _LOOP1 |     |                               |

|--------|-----|-------------------------------|

|        | nop | ;after normal loop            |

|        |     | ;termination, sp == 1         |

|        | rts | ;after execution, SP == $0$ , |

|        |     | ; execution returns to main   |

|        |     |                               |

Direct user access with the MOVEC instruction is possible to SSL,SSH. Note that MOVEC to/from SSH implicitly increments or decrements SP, while the same instruction on SSL has no effect on SP. A manual "pop" operation will usually have the format:

```

movec ssl,<destination 1>

movec ssh,<destination 2> ;implicit sp decrement

```

Explicit access to the stack registers is not recommended for the general user. Such accesses have severe restrictions on them (see **Appendix B** in the *DSP56300* and *DSP56600 Family Manuals*). A user who wishes to manually access the stack must take into account pipeline effects that are usually transparent, and that long interrupts may enter.

## 3.3 USING THE STACK EXTENSION

The hardware stack could be extended to the data memory (X or Y), and it's depth could be set by the user according to need. After initialization, the stack extension works automatically without any user overhead, giving the same functionality as the hardware stack. The registers participating in stack extension operation are listed in **Table 3-2**.

| Register | Name                       | Function                                                                                    |

|----------|----------------------------|---------------------------------------------------------------------------------------------|

| OMR      | operating mode<br>register | stack extension initialization (bits:SEN,XYS)<br>stack extension status (bits: WRP,EOV,EUN) |

| SZ       | stack extension size       | maximum stack depth, in word pairs.                                                         |

| SP       | stack pointer              | current total stack depth, in word pairs                                                    |

| SC       | stack counter              | current hardware stack depth.                                                               |

| EP       | stack extension<br>pointer | pointer to the last address written in the memory extension.                                |

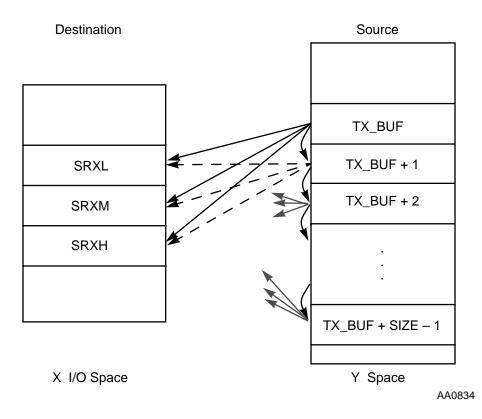

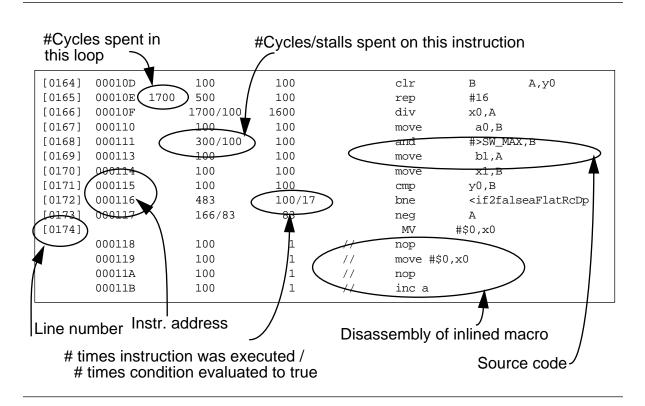

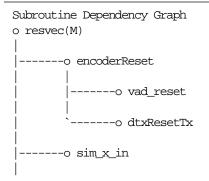

**Table 3-2** Registers Involved in Stack Extension Operation