## Motorola Semiconductor Engineering Bulletin

EB349

# RAM Data Retention Considerations for Motorola Microcontrollers

#### By Bill Lucas

Motorola Microcontroller Division Consumer and Industrial Operations Austin, Texas

### Introduction

This engineering bulletin discusses some of the design considerations and techniques for implementing a non-battery RAM (random-access memory) data retention scheme for Motorola microcontrollers (MCU) that do not have separate RAM standby power pins, such as some of the devices in the 68HC(7)05 and 68HC11 MCU Families.

### Background

Some MCU-based system designs require RAM data retention for transient power outages, possibly during the changing of batteries, or for brownout conditions.

The simple solution to the challenge is to detect the occurrence of the power failure, write RAM data into an external EEPROM (electrically erasable programmable read-only memory), and read the saved RAM data from the EEPROM when power is restored.

However, cost-sensitive systems may not be able to afford the luxury of an EEPROM. Applying creative design techniques to the system may be an inexpensive solution to the issue.

### From a Hardware Point of View

The hardware design for RAM data retention is likely the most difficult part of the challenge. When using Motorola MCUs, some basic issues need to be considered when saving RAM data during a power outage.

For example, the user must make provisions in hardware for these functions:

- Power failure detection circuitry

- Power restoration RESET circuitry

- An energy storage device, for instance, a capacitor

- Power supply isolation (MCU power isolated from the rest of analog and digital circuitry)

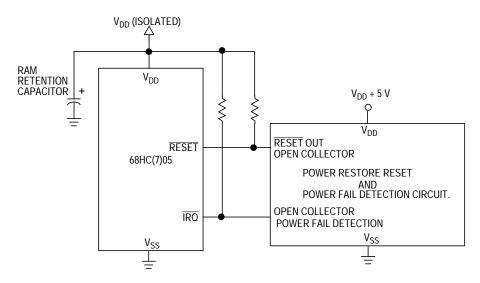

**Figure 1** shows a possible hardware configuration to accomplish RAM retention during a power outage. The circuit provides two basic functions:

- 1. First, it must momentarily assert the RESET input to the MCU when system power is restored or powered-up the first time.

- 2. Second, the circuit must interrupt the MCU when the power fails so immediate action can be taken.

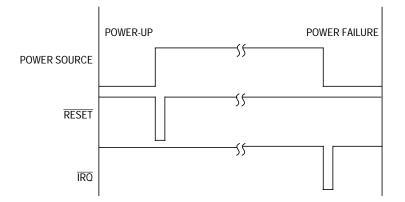

**Figure 2** shows a timing sequence for the assertion of  $\overrightarrow{RESET}$  at the initiation or resumption of power and the assertion of  $\overrightarrow{IRQ}$  upon the detection of a power failure.

**NOTE:** The power restoration RESET circuit must be designed such that it resets the MCU as power is restored, but does not assert the RESET input to the MCU during the power outage. Asserting the MCU's RESET during the duration of a power outage allows its oscillator to run, consuming valuable power from the RAM retention capacitor.

Figure 1. Power Fail and Power Restore Detection Block Diagram

#### Figure 2. Power Restore Detection and Power Fail Timing Diagram

The power failure circuit will inform the MCU via its IRQ input that a power failure is imminent and some action will be required. Most likely, the action will be to calculate a RAM checksum, set up some of the input/output (I/O) ports, and finally place the MCU in stop mode.

Stop mode will place the MCU in its lowest possible power mode. It will remain in that state until one of two events occurs.

An external interrupt is asserted or the RESET input is asserted. Never leave inputs to the MCU floating because they can cause excessive current consumption. If any of the MCU's bidirectional I/O ports are not

### **Engineering Bulletin**

terminated, make sure the data direction register bits for the I/O port are set as outputs. If the port is an input-only port, make sure its input is terminated. Set the output ports to ensure that they do not drive or sink current during the power outage.

An energy storage device will be needed to power the MCU during the power outage. In this case, it will be a capacitor.

It is important to segregate the microcontroller's power source from that of other logic and analog circuitry in the system. Power supply isolation is necessary to ensure that the RAM retention capacitor will power only the microcontroller and other minimal circuitry.

The circuitry powered by the RAM retention capacitor must be designed with minimum leakage in mind.

Some of the not-so-obvious sources of printed circuit board leakage are:

- High leakage decoupling capacitors

- Forward-biased junctions through non-powered devices connected to the MCU's I/O

- PC boards that have flux remaining from the soldering process

- PC boards that reside in high humidity environments and are not conformally coated.

#### Sizing the Capacitor

To size the capacitor, some basic information about the system must be known, specifically:

- 1. What is the minimum time RAM data must be retained during the power failure?

- 2. What is the minimum RAM retention voltage specification of the MCU of choice?

- 3. What is the nominal MCU's power supply voltage?

4. What is the STOP current of the MCU plus the current requirements of any other circuitry powered by the RAM retention capacitor?

The formula for sizing a capacitor to retain RAM data is

(

$$C_{Retention} = (I_{Micro} / V_{Delta}) * t_{Retention}$$

Where:

C<sub>Retention</sub> is the RAM retention capacitor in microfarads.

- I<sub>Micro</sub> is the average STOP current, in microamperes, of the MCU plus any additional circuits powered from the RAM retention capacitor.

- V<sub>Delta</sub> is the nominal power supply voltage minus the minimum RAM retention specification of the MCU.

t<sub>Retention</sub> is the RAM retention in seconds.

As an example, consider a system with these specifications:

- RAM data must be retained for five minutes. (t<sub>Retention</sub> = 300 seconds)

- 2. The minimum RAM retention voltage specification from the MCU's documentation is 2 volts.

- The nominal system power supply voltage is 5 volts. (V<sub>Delta</sub> = 3 volts = (5 volts - 2 volts))

- The average STOP current of the MCU is 1 μA plus 2 μA for additional circuitry, etc. (I<sub>Micro</sub> = 3 μA)

$C_{Retention} = (3 \times 10^{-6} / 3) \times 300 = 300 \ \mu F$

The  $I_{Micro}$  is the average current draw over the RAM retention time. This is because the current of most semiconductor devices is linear with respect to its applied voltage.

When choosing the RAM retention capacitor, an aluminum electrolytic with low dielectric leakage will be the best choice. Choosing an aluminum electrolytic capacitor for a 5-volt system of 16 Vdc working voltage or greater generally will provide the lowest leakage.

#### From a Software Point of View

A number of issues need to be addressed when power is lost and then once it has been restored.

The design of the system power supply will dictate how the power failure detection is handled. In any event, circuitry that will detect an impending power failure is necessary. It may be a comparator circuit, monitoring some dc voltage in the system, or possibly a circuit that detects lost ac cycles.

The job of the software, upon the occurrence of the power failure, is:

- Calculate and save a checksum of the RAM area being saved

- Set I/O ports to ensure that ports do not drive or sink current or are left floating during the power outage

- Then execute a STOP instruction

Upon restoration of power, the software will:

- Check the current RAM checksum against the previously calculated checksum

- If the checksums match, normal system activity can be resumed with the saved data.

- If the checksums do not agree, the software must assume power had been lost for an excessive length of time, resulting in corrupted RAM data, and restart the system with default values.

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Motorola data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death masociated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and ( $\widehat{A}$ ) are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

#### How to reach us:

USA/EUROPE/Locations Not Listed: Motorola Literature Distribution; P.O. Box 5405, Denver, Colorado 80217. 1-303-675-2140 or 1-800-441-2447

JAPAN: Motorola Japan Ltd.; SPS, Technical Information Center, 3-20-1, Minami-Azabu, Minato-ku, Tokyo 106-8573 Japan. 81-3-3440-3569

ASIA/PACIFIC: Motorola Semiconductors H.K. Ltd.; Silicon Harbour Centre, 2 Dai King Street, Tai Po Industrial Estate, Tai Po, N.T., Hong Kong. 852-26668334

Technical Information Center: 1-800-521-6274

HOME PAGE: http://www.motorola.com/semiconductors/

© Motorola, Inc., 2000