# M68MPB916Y3 MCU PERSONALITY BOARD USER'S MANUAL

### **CONTENTS**

## **CHAPTER 1 GENERAL INFORMATION**

| 1.1 | INTRODUCTION                                    | 1-1      |

|-----|-------------------------------------------------|----------|

| 1.2 | SPECIFICATIONS                                  | 1-2      |

| 1.3 | EQUIPMENT REQUIRED                              | 1-2      |

| 1.4 | CUSTOMER SUPPORT                                | 1-3      |

|     |                                                 |          |

|     | CHAPTER 2 HARDWARE PREPARATION AND INSTA        | ALLATION |

| 2.1 | INTRODUCTION                                    | 2-1      |

| 2.2 | HARDWARE PREPARATION                            | 2-1      |

|     | 2.2.1 Clock Select Header (W1)                  | 2-4      |

|     | 2.2.2 VDDA Select Header (W2)                   | 2-5      |

|     | 2.2.3 Voltage Reference High Select Header (W3) | 2-6      |

|     | 2.2.4 Voltage Reference Low Select Header (W4)  | 2-7      |

|     | 2.2.5 MCU Clock Source Select Header (W5)       | 2-8      |

|     | 2.2.6 Using a 32 KHz Clock                      | 2-9      |

|     | 2.2.7 MCU ID Code Select Header (W6)            | 2-10     |

|     | 2.2.8 VSSA Insertion Point (E1)                 | 2-10     |

| 2.3 | MEVB CONFIGURATION                              | 2-11     |

| 2.4 | MPB – MMDS INSTALLATION                         | 2-13     |

|     | CHAPTER 3 MEVB QUICK START GUIDE                |          |

|     | CHAFTER 5 WEVB QUICK START GUIDE                |          |

| 3.1 |                                                 |          |

| 3.2 | CONFIGURING THE MPB                             | 3-1      |

| 3.3 | CONFIGURING THE MPFB                            | 3-1      |

|     | 3.3.1 MPFB Memory Devices                       | 3-1      |

|     | 3.3.2 MPFB Jumper Headers                       | 3-2      |

| 3.4 | MEVB INSTALLATION INSTRUCTIONS                  | 3-3      |

|     | 3.4.1 Power Supply – MPFB Connection            | 3-4      |

|     | 3.4.2 Personal Computer – BDM Connection        | 3-5      |

| 3.5 | SOFTWARE INSTALLATION                           | 3-5      |

|      | CHAPTER 4 MEVB SUPPORT INFORMATION                                 |     |

|------|--------------------------------------------------------------------|-----|

| 4.1  | INTRODUCTION                                                       | 4-1 |

|      | CHAPTER 5 MAPI SUPPORT INFORMATION                                 |     |

| 5.1  | INTRODUCTION                                                       | 5-1 |

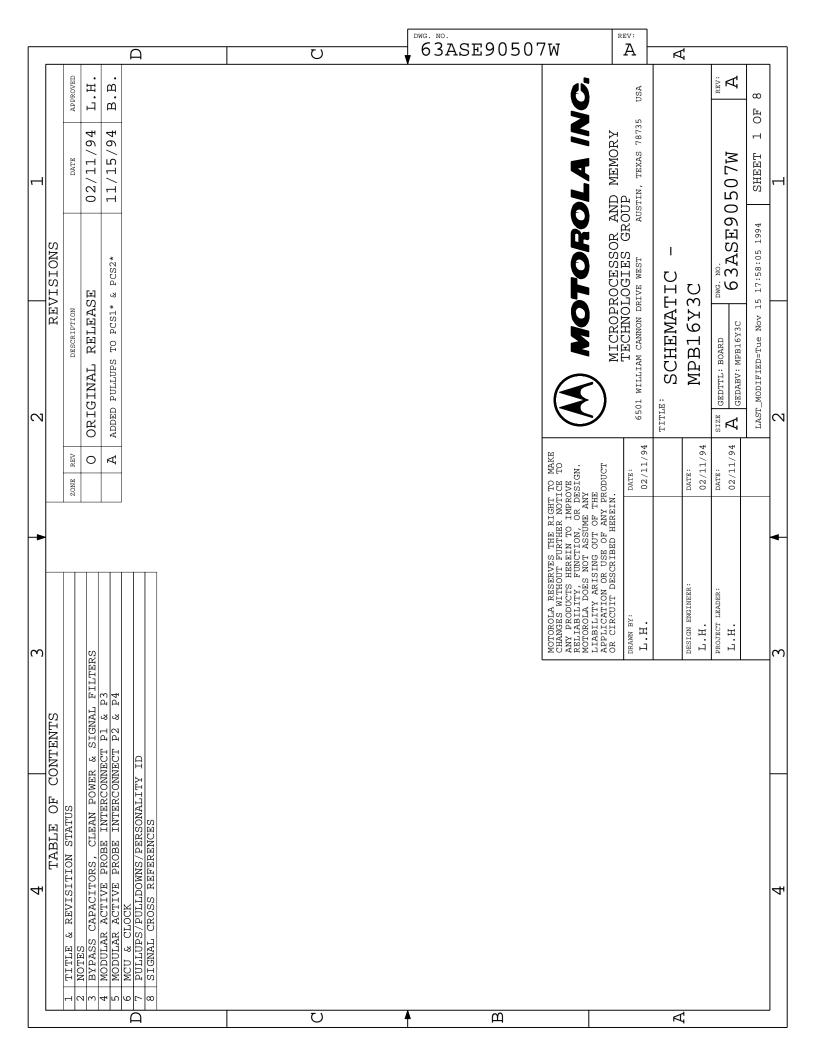

|      | CHAPTER 6 SCHEMATIC DIAGRAMS                                       |     |

| 6.1  | INTRODUCTION                                                       | 6-1 |

|      | FIGURES                                                            |     |

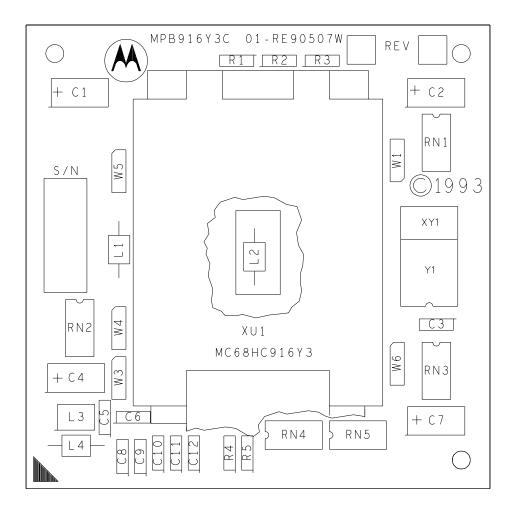

| 2-1. | MPB Jumper Headers and Insertion Point Location Diagram (top view) | 2-2 |

| 5-1. | MAPI Interface Connector Layout                                    | 5-1 |

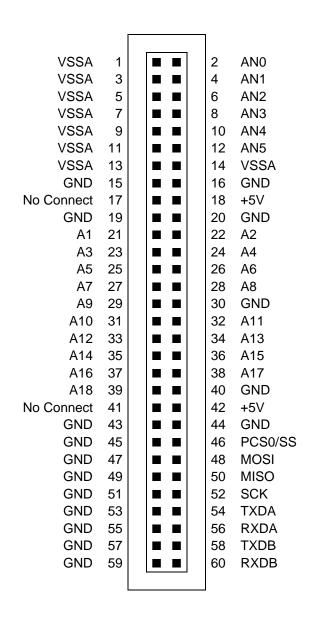

| 5-2. | MAPI Interface Connector P1 Pin Assignments                        | 5-2 |

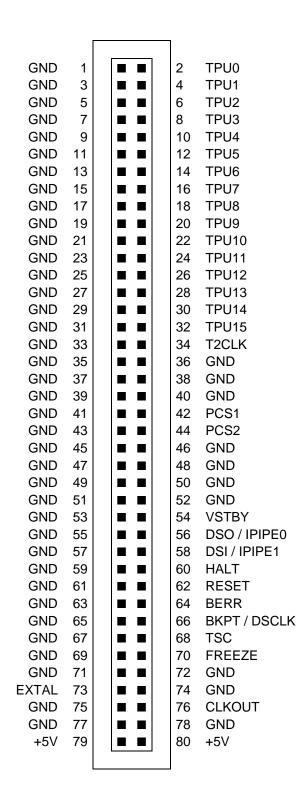

| 5-3. | MAPI Interface Connector P2 Pin Assignments                        | 5-3 |

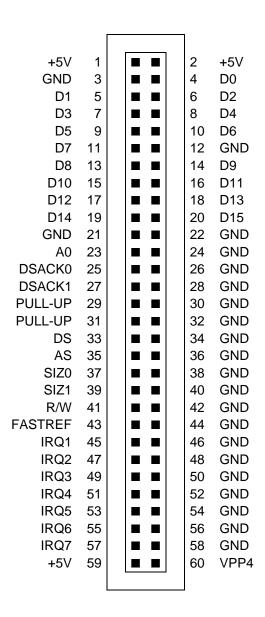

| 5-4. | MAPI Interface Connector P3 Pin Assignments                        | 5-4 |

| 5-5. | MAPI Interface Connector P4 Pin Assignments                        | 5-5 |

|      | TABLES                                                             |     |

| 1-1. | MPB Specifications                                                 | 1-2 |

| 2-1. | Jumper Header Types                                                | 2-3 |

| 2-2. | MPB Jumper Header Descriptions                                     | 2-3 |

| 3-1. | MPFB Quick Start Jumper Header Configuration                       | 3-2 |

|      | Logic Analyzer Connector J7 Pin Assignments                        |     |

| 4-2. | Logic Analyzer Connector J8 Pin Assignments                        | 4-2 |

| 4-3. | Logic Analyzer Connector J9 Pin Assignments                        | 4-3 |

|      | Logic Analyzer Connector J10 Pin Assignments                       |     |

| 4-5. | Logic Analyzer Connector J11 Pin Assignments                       | 4-4 |

|      | Logic Analyzer Connector J12 Pin Assignments                       |     |

|      | Logic Analyzer Connector J13 Pin Assignments                       |     |

| 4-8. | Logic Analyzer Connector J14 Pin Assignments                       | 4-8 |

# **TABLES** (continued)

| 4-9. Logic Analyzer Connector J15 Pin Assignments  | 4-9  |

|----------------------------------------------------|------|

| 4-10. Logic Analyzer Connector J16 Pin Assignments | 4-9  |

| 4-11. Logic Analyzer Connector J17 Pin Assignments | 4-10 |

| 4-12. Logic Analyzer Connector J18 Pin Assignments | 4-11 |

| 4-13. Logic Analyzer Connector J19 Pin Assignments | 4-12 |

| 4-14. Logic Analyzer Connector J20 Pin Assignments | 4-12 |

vi M68MPB16Y3UM/D

# CHAPTER 1 GENERAL INFORMATION

#### 1.1 INTRODUCTION

This manual provides general information, hardware preparation, installation instructions, a quick start guide, and support information for the M68MPB916Y3 MCU Personality Board (MPB). The MPB is one component of Motorola's modular approach to MC68HC16Y3 and MC68HC916Y3 Microcontroller Unit-based product development. This modular approach lets you easily configure our development systems to fit your requirements.

The MPB may be used in either the M68MMDS1632 Motorola Modular Development System (MMDS) or the M68MEVB1632 Modular Evaluation Board (MEVB). Alternately, you may install the MPB directly in your target system if the target system includes an modular active probe interconnect (MAPI) interface. The MCU device on the MPB defines which MCU is emulated/evaluated by the MMDS or MEVB. Both systems are invaluable tools for designing, debugging, and evaluating MCU operation of the M68HC16 and M68300 MCU Families. By providing the essential MCU timing and I/O circuitry, these systems simplify user evaluation of prototype hardware/software products.

#### MPB product includes:

- M68MPB916Y3 MCU Personality Board (MPB)

- Plastic overlay for use with the MEVB pin outs for the logic analyzer connectors on the MPFB (specifically for the MC68HC916Y3 MCU)

- Documentation

#### 1.2 SPECIFICATIONS

Table 1-1 lists MPB specifications.

**Table 1-1. MPB Specifications**

| Characteristic                      | Specifications                                                                          |

|-------------------------------------|-----------------------------------------------------------------------------------------|

| On-Board Clock                      | Case style: 14 or 8-pin hybrid crystal clock oscillator (frequency as required by MCU). |

| External Clock                      | dc – 20.97 MHz (or maximum MCU allows).                                                 |

| MCU I/O ports                       | HCMOS compatible                                                                        |

| Temperature Operating Storage       | 0° to +40° C<br>-40° to +85° C                                                          |

| Relative humidity                   | 0 to 90% (non-condensing)                                                               |

| Power requirements                  | +5 Vdc ± 5% @ 500 mA (max.)                                                             |

| Dimensions<br>MCU Personality Board | 3.25 x 3.25 in. (82.6 x 82.6 mm)                                                        |

## 1.3 EQUIPMENT REQUIRED

The external requirements for MPB operation are either an MEVB or MMDS system. MMDS operation requirements are described in the M68MMDS1632 Motorola Modular Development System User's Manual, M68MMDS1632/D. Operation requirements for the MEVB are described in this manual and the M68MPFB1632 Modular Platform Board User's Manual, M68MPFB1632/D.

1-2 M68MPB16Y3UM/D

#### 1.4 CUSTOMER SUPPORT

For information about a Motorola distributor or sales office near you call:

AUSTRALIA, Melbourne – (61-3)887-0711 Sydney – 61(2)906-3855

BRAZIL, Sao Paulo – 55(11)815-4200

CANADA, B. C., Vancouver – (604)606-8502 ONTARIO, Toronto – (416)497-8181 ONTARIO, Ottawa – (613)226-3491 QUEBEC, Montreal – (514)333-3300

CHINA, Beijing – 86-10-68437222

DENMARK - (45)43488393

FINLAND, Helsinki - 358-9-6824-400

FRANCE, Paris – 33134 635900

GERMANY,

Langenhagen/Hannover – 49(511)786880 Munich – 49 89 92103-0 Nuremberg – 49 911 96-3190 Sindelfingen – 49 7031 79 710 Wiesbaden – 49 611 973050

HONG KONG, Kwai Fong – 852-6106888 Tai Po – 852-6668333

INDIA, Bangalore – (91-80)5598615

ISRAEL, Herzlia – 972-9-590222

ITALY, Milan - 39(2)82201

JAPAN, Fukuoka – 81-92-725-7583

Gotanda - 81-3-5487-8311

Nagoya – 81-52-232-3500

Osaka - 81-6-305-1802

Sendai – 81-22-268-4333

Takamatsu - 81-878-37-9972

Tokyo – 81-3-3440-3311

KOREA, Pusan - 82(51)4635-035

Seoul – 82(2)554-5118

MALAYSIA, Penang – 60(4)2282514

MEXICO, Mexico City – 52(5)282-0230 Guadalajara – 52(36)21-8977

PUERTO RICO, San Juan - (809)282-2300

SINGAPORE - (65)4818188

SPAIN, Madrid - 34(1)457-8204

SWEDEN, Solna – 46(8)734-8800

SWITZERLAND, Geneva – 41(22)799 11 11 Zurich – 41(1)730-4074

TAIWAN, Taipei – 886(2)717-7089

THAILAND, Bangkok - 66(2)254-4910

UNITED KINGDOM, Aylesbury – 441(296)395-252

UNITED STATES, Phoenix, AZ – 1-800-441-2447

For a list of the Motorola sales offices and distributors:

http://www.mcu.motsps.com/sale off.html

1-4 M68MPB16Y3UM/D

#### **CHAPTER 2**

#### HARDWARE PREPARATION AND INSTALLATION

#### 2.1 INTRODUCTION

This chapter provides unpacking instructions, hardware preparation information, and installation instructions for the MPB.

When you unpack the MPB from its shipping carton, verify that all items are in good condition. Save packing material for storing and shipping the MPB.

#### **NOTE**

Should the MPB arrive damaged, save all packing material, and contact the carrier's agent.

#### 2.2 HARDWARE PREPARATION

This portion of the manual explains how to prepare the MPB before use, as well as how to configure the MPB for system operation. MPB installation in the MMDS and MEVB are also described.

The MPB has been factory tested and is shipped with installed jumpers. A jumper installed on a jumper header provides a connection between two points in the MPB circuit. There are two types of jumper headers on the MPB: three-pin and two-pin with a cut-trace short. A cut-trace short has a copper trace between the feed-through holes (bottom or solder side of the MPB). Table 2-1 describes each type of jumper header.

There are five jumper headers on the MPB (Table 2-2 is a quick reference guide for the jumper headers). These jumper headers may be re-configured to customize MPB functionality. The following paragraphs are a detailed description of each jumper header function. There is also an insertion point (E1) for connecting an external ground. Figure 2-1 shows the location of the MPB jumper headers and the insertion point.

#### **NOTE**

Verify that all socketed parts are seated in their sockets.

#### **CAUTION**

Depending on the application, it may be necessary to cut the wiring trace short (cut-trace short) on W2. Be careful not to cut adjacent PCB wiring traces or too deep on the multi-layer circuit board.

#### **NOTE**

If the cut-trace short on a jumper header is cut, a user-supplied fabricated jumper must be installed on the jumper header to return the MPB to its default setting.

Figure 2-1. MPB Jumper Headers and Insertion Point Location Diagram (top view)

2-2 M68MPB16Y3UM/D

**Table 2-1. Jumper Header Types**

| Jumper Header<br>Type        | Symbol | Description                                                                                                                                                                                                        |

|------------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| two-pin with cut-trace short | •      | Two-pin jumper header with cut-trace short, designated as WX (X = the jumper header number). After removing the cut-trace short, use a fabricated jumper to return the jumper header to its factory default state. |

| three-pin                    | •      | Three-pin jumper header, designated as WX (X = the jumper header number). Use a fabricated jumper to create a short between two of the three pins of the jumper header.                                            |

**Table 2-2. MPB Jumper Header Descriptions**

| Jumper<br>Header | Туре | Description                                                                                                                                        |

|------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| W1 1 2 1         |      | Jumper between pins 1 and 2 (factory default); selects the MPB on-board crystal clock source.                                                      |

|                  | 3 ●  | Jumper between pins 2 and 3; selects an external clock source as the MCU EXTAL input signal.                                                       |

| W2               | 1 2  | Jumper installed or cut-trace short intact (factory default); selects the on-board VDDA power source.                                              |

|                  |      | No jumper or cut-trace short; use an external power source by connecting an external power source to W2 pin 2.                                     |

|                  |      | NOTE                                                                                                                                               |

|                  |      | Jumper header W2 is not populated by the factory.                                                                                                  |

| W3               | 1 2  | Jumper installed on pins 1 and 2 (factory default); selects the MPB on-board VRH power source.                                                     |

| 3 •              |      | Jumper installed on pins 2 and 3; selects external VRH power source.                                                                               |

| W4 1 1 2         |      | Jumper installed on pins 1 and 2 (factory default); selects the MPB on-board VRL power source.                                                     |

|                  | 3 ●  | Jumper installed on pins 2 and 3; selects external VRL power source.                                                                               |

| W5               | 1 2  | Jumper installed on pins 1 and 2 (factory default); selects the MCU-internal phase-lock-loop frequency synthesizer as the system clock.            |

|                  | 3 ●  | Jumper installed on pins 2 and 3; selects the EXTAL input as the system clock. The MCU-internal phase-lock-loop frequency synthesizer is disabled. |

| W6               | 1 2  | Jumper installed on pins 1 and 2 (factory default); selects an MC68HC916Y3 MCU as the MCU type for this MPB.                                       |

|                  | 3 •  | Jumper installed on pins 2 and 3; selects an MC68HC16Y3 MCU as the MCU type for this MPB.                                                          |

#### 2.2.1 Clock Select Header (W1)

Jumper header W1 connects the MCU external clock (EXTAL) pin to either an on-board or external (target system) clock source. The drawing below shows the factory configuration: fabricated jumper on pins 1 and 2. This configuration selects the MPB on-board clock source; crystal oscillator in socket at located Y1. (This crystal provides for operation at the maximum rate the MCU allows via the internal phase-locked loop or direct clock input.) When the MPB is installed in the active probe or directly on a target system and the target system clock is used as the MPB clock, move the fabricated jumper to W1 pins 2 and 3. This connects the MCU EXTAL pin to the MAPI bus input pin. The frequency of the external clock signal can be from dc to 20.97 MHz (or to the maximum the MCU allows).

#### **NOTE**

You can not drive the MPB clock circuit from an external source (target system) with a discrete crystal. If a target system clock source is used to drive the MPB clock circuit, always use a logic driven clock such as a hybrid oscillator.

2-4 M68MPB16Y3UM/D

#### 2.2.2 VDDA Select Header (W2)

Jumper header W2 selects the MPB VDDA power source; either MPB power (VDDI) or an external source. The drawing below shows the factory configuration: cut-trace short on pins 1 and 2. This configuration connects filtered VDDI to VDDA. To use an external power source, remove the cut-trace short from W2 pins 1 and 2. Then connect the external power source to W2 pin 2. Removal of the cut-trace short isolates the MCU VDDA pin from the other MPB circuitry. Isolation lets you connect a precision VDDA source for accurate 10-bit analog/digital (A/D) generation. When connecting an external VDDA power supply to the MPB connect the power supply ground to insertion point E1. For more information on A/D generation refer to the Analog-To-Digital Converter Reference Manual, ADCRM/AD.

W2

#### **NOTES**

If the cut-trace short has been cut, a fabricated jumper must be installed on W2 to return it to the factory configuration.

Jumper header W2 is not populated by the factory.

#### 2.2.3 Voltage Reference High Select Header (W3)

Jumper header W3 selects the voltage reference high (VRH) source; either MPB power (VDDA) or an external VRH source. The drawing below shows the factory configuration: fabricated jumper on pins 1 and 2. This configuration selects VDDA as the VRH source. To use an external VRH source, first place the fabricated jumper on W3 pins 2 and 3. Then connect the MCU VRH pin to the external VRH source. Each configuration defines which method is best when connecting the MCU VRH pin to the external VRH source:

- • MPB/MPFB connect via the MPFB logic analyzer connector (refer to Chapter 4 for the appropriate logic analyzer pin)

- • MPB/MMDS1632 connect via the VRH pin of the target MCU socket

- •MPB/Target System connect via the VRH pin of the target system MAPI bus

Alternately, you may remove the jumper and wire-wrap directly to W3 pin 2. Connecting directly to pin 2 is an option regardless of the configuration.

W3

2-6 M68MPB16Y3UM/D

#### 2.2.4 Voltage Reference Low Select Header (W4)

Jumper header W4 selects the voltage reference low (VRL) source; either MPB power (VSSA) or an external VRL source. The drawing below shows the factory configuration: fabricated jumper on pins 1 and 2. This configuration selects VSSA as the VRL source. To use an external VRL source, first place the fabricated jumper on W4 pins 2 and 3. Then connect the MCU VRL pin to the external VRL source. Each configuration defines which method is best when connecting the MCU VRL pin to the external VRL source:

- •MPB/MPFB connect via the MPFB logic analyzer connector (refer to Chapter 4 for the appropriate logic analyzer pin)

- •MPB/MMDS1632 connect via the VRL pin of the target MCU socket

- •MPB/Target System connect via the VRL pin of the target system MAPI bus

Alternately, you may remove the jumper and wire-wrap directly to W4 pin 2. Connecting directly to pin 2 is an option regardless of the configuration.

W4

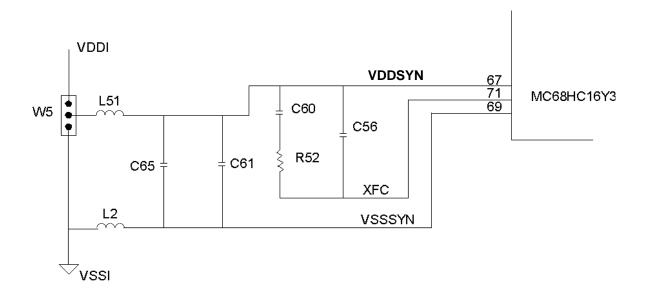

#### 2.2.5 MCU Clock Source Select Header (W5)

Jumper header W5 selects the MCU clock; either the MCU-internal phase-lock-loop frequency synthesizer or the EXTAL input. The drawing below shows the factory configuration: fabricated jumper on pins 1 and 2. This configuration selects the MCU-internal phase-lock-loop frequency synthesizer as the clock. To use the EXTAL input as the clock, place the fabricated jumper on 2 and 3.

#### **NOTE**

J14 pin-4 and W16 on the MPFB are marked MODCLK, but this signal, when using an M68HC916Y3, is FASTREF. The M68HC916Y3 MEVB overlay is correct and marked FASTREF. Use W16 on the MPFB to select the MCU PLL clock input speed.

2-8 M68MPB16Y3UM/D

#### 2.2.6 Using a 32 KHz Clock

The factory installed crystal oscillator in location Y1 is rated at 4.194 megahertz. You may change Y1 to change the clock speed of the MPB. The only other oscillator you may install is 32 kilohertz. If you change Y1 to the slower value (32 KHz) you must replace the following capacitors and resistor (see diagram below):

$C60 \ - \ 1 \ \mu f$

C56 – 1 µf

$R52 \quad - \quad 18 \ k\Omega$

#### 2.2.7 MCU ID Code Select Header (W6)

Jumper header W6 selects the MCU ID code; either the M68HC16Y3 MCU or M68HC916Y3 MCU. The drawing below shows the factory configuration: fabricated jumper on pins 1 and 2. Use this configuration when an M68HC16Y3 MCU is installed on the MPB. To use the MPB with an M68HC916Y3 MCU installed, place the fabricated jumper on 2 and 3.

#### **NOTE**

These jumper settings only apply to when using the M68HC916Y3 MPB in an MMDS1632.

#### 2.2.8 VSSA Insertion Point (E1)

Insertion point E1 is a plate through hole that lets you connect an external ground to the MPB VSSA pin (refer to paragraph 2.2.2). Insert an external ground wire in E1 and solder it into the plate through hole.

#### **NOTE**

Insertion point E1 is not populated by the factory.

2-10 M68MPB16Y3UM/D

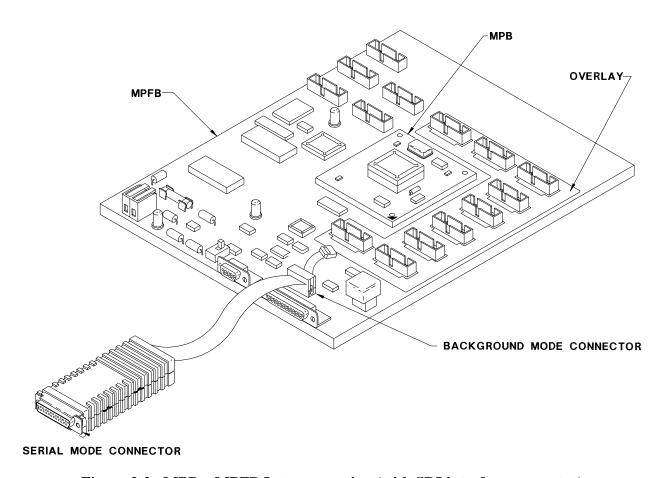

#### 2.3 MEVB CONFIGURATION

The MEVB contains:

- MPB MCU-device-specific board that defines the MCU to be evaluated.

- M68MPFB1632 Modular Platform Board (MPFB) which provides the interface connections to the host computer, logic analyzer connections, and the platform for installing the MPB. For more information about the MPFB and MEVB system connections refer to the M68MPFB1632 Modular Platform Board User's Manual, M68MPFB1632/D. Chapter 3 of this manual contains information to help you get started using your MEVB.

#### **CAUTION**

Turn OFF MPFB power when installing the MPB on the MPFB or removing the MPB from the MPFB. Sudden power surges could damage MEVB integrated circuits.

To install the MPB on the MPFB (refer to Figure 2-2):

- 1. Inspect all connectors for bent or damaged pins.

- 2. Align the MPB reference mark with the MPFB reference mark.

- 3. Rotate the MPB until the four MAPI bus connectors on its bottom mate with the MAPI bus connectors on the top of the MPFB. (There is only one way to connect the MPB and the MPFB.)

- 4. Firmly press the MPB onto the MPFB.

#### **CAUTION**

Support the bottom side of MPFB when installing the MPB on the MPFB. Excessive flexing of the MPFB could damage the printed circuit.

Figure 2-2. MPB – MPFB Interconnection (with SDI interface connector)

After you have installed the MPB, install the plastic overlay on the MPFB: place the overlay over logic analyzer connectors J12 through J20 and press down. Holes in the overlay slide down over plastic clips on the MPFB. These clips hold the overlay in place.

2-12 M68MPB16Y3UM/D

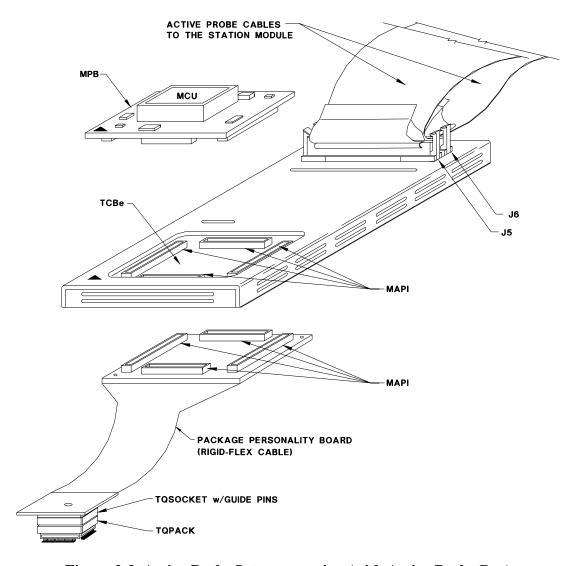

#### 2.4 MPB – MMDS INSTALLATION

The M68MMDS1632 Motorola Modular Development System (MMDS) consists of the station module and an active probe. The active probe consists of a three board set, two cables, and a box:

- MPB MCU-device-specific board that defines the MCU to be evaluated.

- Enhanced Target Control Board (TCB) the interface between the MPB, target system, and the station module. The TCB must be purchased separately. For more information about the TCB refer to the MMDS1632 Motorola Modular Development System User's Manual, MMDS1632UM/D.

- Package Personality Board (PPB) the board that connects the active probe to the target system. The PPB must be purchased separately. For more information about the PPB refer to the appropriate PPB configuration guide.

- Active probe cables (2) the interface between the active probe and the station module. 01-RE90340W01 REV 0 and 01-RE90341W01 REV 0 are printed on the active probe cables. The active probe cables come with the TCB. For more information about the active probe cables refer to the MMDS1632 Motorola Modular Development System User's Manual, MMDS1632UM/D.

- Active probe box the protective enclosure for the TCB.

#### **CAUTION**

Turn off MMDS and target system power when installing or removing MMDS components. Sudden power surges could damage MMDS and target system integrated circuits.

To configure an active probe (refer to Figure 2-3):

- 1. Inspect all connectors for bent or damaged pins.

- 2. Rotate the MPB until the four MAPI bus connectors on its bottom mate with the MAPI bus connectors on the top of the TCB. (There is only one way to connect the MPB and the TCB.) Firmly press the MPB and the TCB together.

- 3. Rotate the PPB until the four MAPI bus connectors on its top mate with the MAPI bus connectors on the bottom of the TCB. (There is only one way to connect the PPB and the TCB.) Firmly press the PPB and the TCB together.

4. Connect one end of the 01-RE90341W01 REV 0 active probe cable to connector P6 on the MMDS control board; connect the other end to connector J6 on the TCB. Connect one end of the 01-RE90340W01 REV 0 active probe cable to connector P5 on the MMDS control board; connect the other end to connector J5 on the TCB. Secure the connector clamps on TCB connectors J5 and J6.

The active probe is now ready to connect to the target system (refer to the PPB configuration guide for information on connecting the active probe to the target system.)

Figure 2-3. Active Probe Interconnection (with Active Probe Box)

2-14 M68MPB16Y3UM/D

# CHAPTER 3 MEVB QUICK START GUIDE

#### 3.1 INTRODUCTION

This quick start guide is intended for the user who may not be familiar with Motorola's development tools. This chapter explains the MEVB hardware and software set-up for M68MEVB916Y3 operation. Hardware set-up consists of configuring the MPB and MPFB jumper headers. While software set-up consists of installing and running the appropriate macro script file within the debugger.

For the purpose of this quick start guide the MPB jumper headers should be configured in their default positions. Chapter 2 of this manual contains the default jumper header settings for the MPB.

#### 3.2 CONFIGURING THE MPFB

The MPFB includes jumper-selectable options such as chip select usage, memory type selection and memory size selection for the pseudo ROM sockets, and reset data control.

#### 3.2.1 MPFB Memory Devices

Pseudo ROM refers to memory locations U2 & U4. The two pseudo ROM sockets provide a generic memory socket, and accepts a variety of RAM, EPROM, or EEPROM devices. The pseudo ROM sockets, as shipped from the factory, contain two 32K x 8 RAM devices. These memory are 28-pin package devices.

#### 3.2.2 MPFB Jumper Headers

Configure your MPFB jumper headers per the instructions in Table 3-1. Table 3-1 contains information exclusively intended for quick start and ignores the other jumper headers.

**Table 3-1. MPFB Quick Start Jumper Header Configuration**

| Jumper<br>Header | Туре                     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| W2               | 123                      | Install a jumper on pins 1 and 2 to configure pin 1 of the memory devices in the pseudo ROM sockets (U2 & U4) as a standard address line.                                                                                                                                                                                                                                                                                                           |  |

| W3               | 123                      | Install a jumper on pins 1 and 2 to indicate that the memory devices in the pseudo ROM sockets (U2 & U4) have 28-pins.                                                                                                                                                                                                                                                                                                                              |  |

| W4               | 123                      | Install a jumper on pins 1 and 2 to set the pseudo ROM port size (memory data width) as word.                                                                                                                                                                                                                                                                                                                                                       |  |

| W5               | 1 2 3<br>••••            | Install a jumper on pins 2 and 3 to enable the PRU.                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| W6               | 123                      | W6 selects the MCU operation mode. Each 3-pin jumper header set corresponds to an MCU data line. While the reset pin is low, the reset data values are driven on the data bus (D0 – D15). (The MEVB reset data circuit is open drain; a high state is provided via a pull-up resistor.) Each reset data line may be set high (H) or low (L). Consult the appropriate MCU user's manual, data book, or technical summary for reset data information. |  |

| W10              | 1<br>3<br>0 0 4<br>5 0 6 | Install a jumper on pins 1 and 2 to indicate that RAM is installed in the pseudo ROM sockets (U2 & U4).                                                                                                                                                                                                                                                                                                                                             |  |

| W12              | 1 2 4 5 6 8 10           | Install a jumper on pins 3 and 4 to indicate that the two devices installed in the pseudo ROM sockets (U2 & U4) are 32K x 8.                                                                                                                                                                                                                                                                                                                        |  |

3-2 M68MPB16Y3UM/D

**Table 3-1. MPFB Quick Start Jumper Header Configuration (continued)**

| Jumper<br>Header | Туре       | Description                                                                                                                                                                                                                                                                                                                                   |  |

|------------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| W14              | 123        | Jumper header W14 selects the MCU signal for the memory devices in the fast RAM sockets (U9 & U10) and pseudo ROM sockets (U2 & U4). Pins 1 and 2 select the MCU chip select for the memory devices in the fast RAM sockets. While pins 2 and 3 of jumper header W14 select the chip select for the memory devices in the pseudo ROM sockets. |  |

|                  |            | Jumper installed on CSBOOT pins 2 and 3 (factory default); use CSBOOT as the memory device chip enable for memory devices in the pseudo ROM sockets.                                                                                                                                                                                          |  |

| W16              | 1 2<br>• • | No jumper installed; the MCU FASTREF signal is pulled high (logic 1) via a resistor during reset.                                                                                                                                                                                                                                             |  |

|                  |            | NOTE                                                                                                                                                                                                                                                                                                                                          |  |

|                  |            | J14 pin-4 and W16 on the MPFB are marked MODCLK, but this signal, when using an M68HC16Y3, is FASTREF. The M68HC16Y3 MEVB overlay is correct and marked FASTREF. Use W16 on the MPFB to select the MCU PLL clock input speed.                                                                                                                 |  |

| W17              | 1 2<br>• • | No jumper installed; the BERR signal is pulled high (logic 1) via a resistor during reset.                                                                                                                                                                                                                                                    |  |

| W18              | 123        | Install a jumper on pins 1 and 2 for unrestricted writes to the memory devices in the pseudo ROM sockets (U2 & U4).                                                                                                                                                                                                                           |  |

| W19              | 123        | Install a jumper on pins 1 and 2 to ground the A19 signal to the MPFB memory arrays.                                                                                                                                                                                                                                                          |  |

| W22              | 123        | Install a jumper on pins 2 and 3 to select the evaluation MCU (on the MPB) as an M68HC16 MCU device.                                                                                                                                                                                                                                          |  |

#### 3.3 MEVB INSTALLATION INSTRUCTIONS

MEVB installation requires a user-supplied power supply and host computer. The host computer must have a parallel port and must run MS-DOS, as required by ICD16. The following paragraphs explain MPFB connections. Refer to Chapter 2 for instructions to interconnect the MPB and MPFB.

#### 3.3.1 Power Supply – MPFB Connection

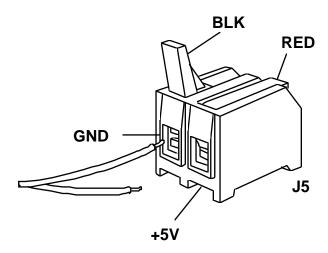

Use MPFB connector J5 to connect a user-supplied power supply to the MEVB. Contact 1 is ground; black lever. Contact 2 is VDD (+5 volts); red lever. Use 20 or 22 AWG wire for power connections. For each wire, trim back the insulation 1/4 in. (.635 cm), lift the appropriate lever of J5 to release tension on the contacts, then insert the bare wire into J5 and close the lever. The MEVB requires a +5Vdc @ 1.0 amp power supply for operation. A 1.5 amp fuse is installed on the MPFB +5Vdc power supply input line.

#### **CAUTIONS**

Do not use wire larger than 20 AWG in connector J5. Such wire could damage the connector.

Turn off MEVB power when installing or removing the MPB from the MPFB. Sudden power surges could damage MEVB integrated circuits.

3-4 M68MPB16Y3UM/D

#### 3.3.2 Personal Computer – BDM Connection

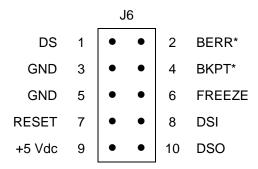

Personal computer communication with the MEVB requires background debug mode (BDM) hardware. Connect your BDM hardware between your computer's I/O port and the BDM header on the MPFB (MPFB connector J6). The drawing below shows signal assignments for connector J6. For additional information about your BDM software/hardware, including debugging and assembly information, see the appropriate user's manual.

#### 3.4 SOFTWARE INSTALLATION

After you have set up the MEVB hardware you must install the software on your computer. Follow the installation procedure in the appropriate software operations manual.

The MCU must be initialized before the MEVB will function. The following is one possible initialization for the MPB16Y3. You may adapt this example to your debugger. This initialization enables the maximum system clock frequency and disables the software watchdog while enabling the bus monitor. CSBOOT is set to zero-wait state and the block size set to 64K starting at \$00000. The SRAM is enabled to reside at \$10000 with the stack pointer initialized at \$103FE and the instruction pointer (IP) initialized to \$00200 (PK=0, IP=200).

Load your program at address \$00200.

## Below is the MPBY3.ICD initialization macro program listing.

| symbol SCIMCR FFA00 symbol SYNCR FFA04 symbol CSBARBT FFA48 symbol CSORBT FFA4A symbol START 00200 dmmw SCIMCR 40CF dmmw SYNCR B000 watchdog dmmw CSBARBT 0003 dmmw CSORBT 7830 mdf6 START pk=0 a=AA b=BB e=0000 ix=0000 iy=0000 ir=0000 hr=0000 k=0000 k=0000                                                                                                  | Set module mapping to \$FFF000-\$FFFFFF<br>Set system clock frequency to 16.78 MHz<br>Disable the watcdog timer<br>Change CSBOOT block size to 64K<br>Change wait state to zero<br>Display program in PMM window<br>Initialize CPU registers |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| sp=03fe<br>sk=1                                                                                                                                                                                                                                                                                                                                                 | Initialize the stack pointer                                                                                                                                                                                                                 |

| symbol RAMBAH FFB04<br>symbol RAMMCR FFB00                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                              |

| dmmw RAMBAH 0001<br>dmmb RAMMCR 00                                                                                                                                                                                                                                                                                                                              | Set SRAM base address Enable SRAM array Chaols SRAM write Meterala 681 1616 advanced MCUla                                                                                                                                                   |

| dmml       10000       4D6F746F         dmml       10004       726F6C61         dmml       10008       20363848         dmml       1000C       43313620         dmml       10010       41647661         dmml       10014       6E636564         dmml       10018       20204D43         dmml       1001C       55732020         dmml       10020       36384843 | Check SRAM: write Motorola 68HC16 advanced MCUs                                                                                                                                                                                              |

| mdf3 10000<br>ip=START                                                                                                                                                                                                                                                                                                                                          | Display SRAM in DMM window<br>Start entering your program here                                                                                                                                                                               |

3-6 M68MPB16Y3UM/D

# CHAPTER 4 MEVB SUPPORT INFORMATION

#### 4.1 INTRODUCTION

The information in this chapter is relevant when the MPB is used in an MEVB (the MPB installed on a MPFB). Signals on the MPFB logic analyzer connectors are defined by the MPB type. The tables of this chapter describe MPFB logic analyzer connector signals when an M68MPB9916Y3 is installed on the MPFB. The signal descriptions on J12 – J20 are the logic analyzer pin-outs on the plastic overlay supplied with the MPB.

#### **NOTE**

The signal descriptions in the following tables are for quick reference only. The MC68HC916Y3 User's Manual, MC68HC916Y3UM/AD, contains a complete description of the MC68HC916Y3 MCU signals.

Also contained in this chapter are MAPI bus interface layout and pin assignments information for MPB connectors P1, P2, P3, and P4.

Tables 4-1 through 4-14 list pin assignments for MPFB connectors J7 through J20.

| Table 4-1. | Logic analyzer connector J7  |  |

|------------|------------------------------|--|

| Table 4-2. | Logic analyzer connector J8  |  |

| Table 4-3. | Logic analyzer connector J9  |  |

| Table 4-4. | Logic analyzer connector J10 |  |

| Table 4-5. | Logic analyzer connector J11 |  |

| Table 4-6. | Logic analyzer connector J12 |  |

| Table 4-7. | Logic analyzer connector J13 |  |

| Table 4-8.  | Logic analyzer connector J14 |  |

|-------------|------------------------------|--|

| Table 4-9.  | Logic analyzer connector J15 |  |

| Table 4-10. | Logic analyzer connector J16 |  |

| Table 4-11. | Logic analyzer connector J17 |  |

| Table 4-12. | Logic analyzer connector J18 |  |

| Table 4-13. | Logic analyzer connector J19 |  |

| Table 4-14. | Logic analyzer connector J20 |  |

Table 4-1. Logic Analyzer Connector J7 Pin Assignments

| Pin     | Mnemonic           | Signal                                                                                            |

|---------|--------------------|---------------------------------------------------------------------------------------------------|

| 1, 2    | SPARE              | No connection                                                                                     |

| 3       | OE(ALL)            | I/O PRU OUTPUT ENABLE – Input, active high; when low disables all PRU outputs.                    |

| 4 – 11  | PEPAR7 –<br>PEPAR0 | PEPAR OUTPUTS – Output signals that show the complement (negated contents) of the PEPAR register. |

| 12 – 19 | PE7 – PE0          | PORT E I/O SIGNALS – PRU replacement of the Port E function.                                      |

| 20      | GND                | GROUND                                                                                            |

Table 4-2. Logic Analyzer Connector J8 Pin Assignments

| Pin     | Mnemonic  | Signal                                                                                            |

|---------|-----------|---------------------------------------------------------------------------------------------------|

| 1, 2    | SPARE     | No connection                                                                                     |

| 3       | OE(ABG)   | I/O PRU OUTPUT ENABLE – Input, active high; when low disables port A, port B, and port G outputs. |

| 4 – 11  | PA7 – PA0 | PORT A I/O SIGNALS – PRU replacement of the Port A function.                                      |

| 12 – 19 | PB7 – PB0 | PORT B I/O SIGNALS – PRU replacement of the Port B function.                                      |

| 20      | GND       | GROUND                                                                                            |

4-2 M68MPB16Y3UM/D

Table 4-3. Logic Analyzer Connector J9 Pin Assignments

| Pin     | Mnemonic  | Signal                                                                            |

|---------|-----------|-----------------------------------------------------------------------------------|

| 1, 2    | SPARE     | No connection                                                                     |

| 3       | OE(H)     | I/O PRU OUTPUT ENABLE – Input, active high; when low disables the port H outputs. |

| 4 – 11  | PH7 – PH0 | PORT H I/O SIGNALS – PRU replacement of the Port H function.                      |

| 12 – 19 | PG7 – PG0 | PORT G I/O SIGNALS – PRU replacement of the Port G function.                      |

| 20      | GND       | GROUND                                                                            |

Table 4-4. Logic Analyzer Connector J10 Pin Assignments

| Pin    | Mnemonic | Signal                                                                                                                                                      |

|--------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | +5V      | +5 VDC POWER – Input voltage (+5 Vdc @ 1.0 A) used by the MEVB logic circuits. (To make this pin no connection, remove the jumper from header on the MPFB.) |

| 2      | SPARE    | No connection                                                                                                                                               |

| 3      | AS       | ADDRESS STROBE – Active-low output signal that indicates whether a valid address is on the address bus.                                                     |

| 4 – 19 | A15 – A0 | ADDRESS BUS BITS 15 – 0 – Sixteen bits of the 24-bit address bus.                                                                                           |

| 20     | GND      | GROUND                                                                                                                                                      |

Table 4-5. Logic Analyzer Connector J11 Pin Assignments

| Pin    | Mnemonic | Signal                                                                                                                                                                                                      |

|--------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | +5V      | +5 VDC POWER – Input voltage (+5 Vdc @ 1.0 A) used by the MEVB logic circuits. (To make this pin no connection, remove the jumper from header on the MPFB.)                                                 |

| 2      | SPARE    | No connection                                                                                                                                                                                               |

| 3      | DS       | DATA STROBE – Active-low output signal. During a read cycle, indicates that an external device should place valid data on the data bus. During a write cycle, indicates that valid data is on the data bus. |

| 4 – 19 | D15 – D0 | DATA BUS 15 – 0 – 16 bits of the MCU bi-directional data bus lines.                                                                                                                                         |

| 20     | GND      | GROUND                                                                                                                                                                                                      |

Table 4-6. Logic Analyzer Connector J12 Pin Assignments

| Pin  | Mnemonic                         | Signal                                                                                                                                         |

|------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 2 | SPARE                            | No connection                                                                                                                                  |

| 3    | CLKOUT                           | SYSTEM CLOCK OUT – Output signal that is the MCU internal system clock.                                                                        |

| 4    | BERR                             | BUS ERROR – Active-low signal that indicates that a memory access error has occurred.                                                          |

| 5    | BKPT /                           | BREAKPOINT – Active-low input signal that signals a hardware breakpoint to the CPU.                                                            |

|      | DSCLK                            | Development Serial Clock – Clock input signal for the background debug mode.                                                                   |

| 6    | FREEZE                           | FREEZE – Output signal that indicates the CPU has acknowledged a breakpoint.                                                                   |

|      | QUOT                             | QUOTIENT OUT – Output signal that furnishes the quotient bit of the polynomial divider for test purposes.                                      |

| 7    | LAT-DSO /<br>(Latched<br>IPIPE0) | LATCHED INSTRUCTION PIPE 0 – Latched output signal of the first state of IPIPE0 for CPU16-based MCUs; indicates instruction pipeline activity. |

4-4 M68MPB16Y3UM/D

Table 4-6. Logic Analyzer Connector J12 Pin Assignments (continued)

| Pin | Mnemonic                    | Signal                                                                                                                                                     |

|-----|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8   | LAT-DSI<br>(Latched IPIPE1) | LATCHED INSTRUCTION PIPE 1 – Latched output signal of the first state of IPIPE1 for CPU16-based MCUs; indicates instruction pipeline activity.             |

| 9   | DSO/                        | DEVELOPMENT SERIAL OUT – Serial data output signal for background debug mode.                                                                              |

|     | (IPIPE0)                    | INSTRUCTION PIPE 0 for CPU16-based MCUs.                                                                                                                   |

| 10  | DSI/                        | DEVELOPMENT SERIAL IN – Serial data input signal for background debug mode.                                                                                |

|     | (IPIPE1)                    | INSTRUCTION PIPE 1 for CPU16-based MCUs.                                                                                                                   |

| 11  | DSACK1                      | DATA AND SIZE ACKNOWLEDGE 1 – Active-low input signal that allows asynchronous data transfers and dynamic bus sizing between the MCU and external devices. |

| 12  | DSACK0                      | DATA AND SIZE ACKNOWLEDGE 0 – Active-low input signal that allows asynchronous data transfers and dynamic bus sizing between the MCU and external devices. |

| 13  | FC2/                        | FUNCTION CODE 2 – Output signal that identifies the processor state and address space of the current bus cycle.                                            |

|     | CS5                         | CHIP SELECT 5 – Output signal that selects peripheral or memory devices at programmed addresses.                                                           |

| 14  | FC1                         | FUNCTION CODE 1 – Output signal that identifies the processor state and address space of the current bus cycle.                                            |

| 15  | FC0/                        | FUNCTION CODE 0 – Output signal that identifies the processor state and address space of the current bus cycle.                                            |

|     | CS3                         | CHIP SELECT 3 – Output signal that selects peripheral or memory devices at programmed addresses.                                                           |

| 16  | SIZ1                        | TRANSFER SIZE – Active-high output signals that Indicates the number of bytes to be transferred during a bus cycle.                                        |

| 17  | SIZ0                        | TRANSFER SIZE 0 – Active-high output signals that Indicates the number of bytes to be transferred during a bus cycle.                                      |

Table 4-6. Logic Analyzer Connector J12 Pin Assignments (continued)

| Pin | Mnemonic | Signal                                                                                                                                         |

|-----|----------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 18  | R/W      | READ/WRITE – Active-high output signal that indicates the direction of data transfer on the bus.                                               |

| 19  | BGACK /  | BUS GRANT ACKNOWLEDGE – Active-low input signal that indicates that an external device has assumed bus mastership.                             |

|     | CSE      | EMULATOR CHIP SELECT – Output signal that selects external emulation devices at internally-mapped addresses. CSE is used to emulate I/O ports. |

| 20  | GND      | GROUND                                                                                                                                         |

Table 4-7. Logic Analyzer Connector J13 Pin Assignments

| Pin | Mnemonic | Signal                                                                                                                                                                                                      |

|-----|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | +5V      | +5 VDC POWER – Input voltage (+5 Vdc @ 1.0 A) used by the MEVB logic circuits. (To make this pin no connection, remove the jumper from header on the MPFB.)                                                 |

| 2   | SPARE    | No connection                                                                                                                                                                                               |

| 3   | DSACK1   | DATA AND SIZE ACKNOWLEDGE 1 – Active-low input signal that allows asynchronous data transfers and dynamic bus sizing between the MCU and external devices.                                                  |

| 4   | PULL-UP  | Not connected; pulled high through a resistor on the MPB.                                                                                                                                                   |

| 5   | HALT     | HALT – Active-low input/output signal that suspends external bus activity, to request a retry when used with BERR, or for single-step operation.                                                            |

| 6   | AS       | ADDRESS STROBE – Active-low output signal that indicates that a valid address is on the address bus.                                                                                                        |

| 7   | DS       | DATA STROBE – Active-low output signal. During a read cycle, indicates that an external device should place valid data on the data bus. During a write cycle, indicates that valid data is on the data bus. |

4-6 M68MPB16Y3UM/D

Table 4-7. Logic Analyzer Connector J13 Pin Assignments (continued)

| Pin     | Mnemonic  | Signal                                                                                                                                                        |

|---------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8       | BR /      | BUS REQUEST – Active-low input signal that indicates that an external device requires bus mastership.                                                         |

|         | CS0       | CHIP SELECT 0 – Output signal that selects peripheral or memory devices at programmed addresses.                                                              |

| 9       | BG /      | BUS GRANT – Active-low output signal that indicates that the MCU has relinquished the bus.                                                                    |

|         | CSM       | INTERNAL MODULE CHIP SELECT – Active-low output signal that selects external emulation devices at internally-mapped addresses. CSM is used to emulate memory. |

| 10      | CSBOOT    | BOOT CHIP SELECT – An active-low output chip select for external boot startup ROM                                                                             |

| 11      | CLKOUT    | SYSTEM CLOCK OUTPUT – MCU internal clock output signal.                                                                                                       |

| 12      | A23 /     | ADDRESS BUS BIT 23 – One bit of the 24-bit address bus.                                                                                                       |

|         | CS10      | CHIP SELECT 10 – Output signal that selects peripheral or memory devices at programmed addresses.                                                             |

| 13      | A22 /     | ADDRESS BUS BIT 22 – One bit of the 24-bit address bus.                                                                                                       |

|         | CS9       | CHIP SELECT 9 – Output signal that selects peripheral or memory devices at programmed addresses.                                                              |

| 14      | A21 /     | ADDRESS BUS BIT 21 – One bit of the 24-bit address bus.                                                                                                       |

|         | CS8       | CHIP SELECT 8 – Output signal that selects peripheral or memory devices at programmed addresses.                                                              |

| 15      | A20 /     | ADDRESS BUS BIT 20 – One bit of the 24-bit address bus.                                                                                                       |

|         | CS7       | CHIP SELECT 7 – Output signal that selects peripheral or memory devices at programmed addresses.                                                              |

| 16      | A19 /     | ADDRESS BUS BIT 19 – One bit of the 24-bit address bus.                                                                                                       |

|         | CS6       | CHIP SELECT 6 – Output signal that selects peripheral or memory devices at programmed addresses.                                                              |

| 17 – 19 | A18 – A16 | ADDRESS BUS 18 – 16 – Three bits of the 24-bit address bus.                                                                                                   |

| 20      | GND       | GROUND                                                                                                                                                        |

M68MPB16Y3UM/D 4-7

Table 4-8. Logic Analyzer Connector J14 Pin Assignments

| Pin     | Mnemonic    | Signal                                                                                                                                                                                             |

|---------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 2    | SPARE       | No connection                                                                                                                                                                                      |

| 3       | DSACK0      | DATA AND SIZE ACKNOWLEDGE 0 – Active-low input signal that allows asynchronous data transfers and dynamic bus sizing between the MCU and external devices.                                         |

| 4       | FASTREF     | FASTREF – Selection of crystal or clock input frequency driven into the VCO for generation of the MCU system clock. 1=fast reference, 0=slow reference                                             |

| 5       | TSC         | THREE STATE CONTROL – When TSC is logic high, this input signal forces all output drivers to a high-impedance state.                                                                               |

| 6       | RESET       | RESET – Active-low, bi-directional signal to start a system reset.                                                                                                                                 |

| 7       | PULL-UP     | Not connected; pulled high through a resistor on the MPB.                                                                                                                                          |

| 8       | SPARE       | No connection                                                                                                                                                                                      |

| 9 – 15  | IRQ1 – IRQ7 | TARGET INTERRUPT REQUEST 1 – 7 - Active-low input signals from the target that asynchronously provides an interrupt priority level to the CPU. IRQ1 has the lowest priority, IRQ7 has the highest. |

| 16 – 19 | SPARE       | No connection                                                                                                                                                                                      |

| 20      | GND         | GROUND                                                                                                                                                                                             |

4-8 M68MPB16Y3UM/D

Table 4-9. Logic Analyzer Connector J15 Pin Assignments

| Pin    | Mnemonic | Signal                                                                                                               |

|--------|----------|----------------------------------------------------------------------------------------------------------------------|

| 1 – 3  | SPARE    | No connection                                                                                                        |

| 4 – 13 | GND      | GROUND                                                                                                               |

| 14     | PCLK     | AUXILIARY TIMER CLOCK INPUT – External input clock source for the GPT.                                               |

| 15     | PWMB     | PULSE WIDTH MODULATION B – Repetitive output signals whose high time to low time ratio can be controlled by the CPU. |

| 16     | PWMA     | PULSE WIDTH MODULATION A – Repetitive output signals whose high time to low time ratio can be controlled by the CPU. |

| 17     | PAI      | PULSE ACCUMULATOR INPUT – Input signal that increments an 8-bit counter.                                             |

| 18, 19 | SPARE    | No connection                                                                                                        |

| 20     | GND      | GROUND                                                                                                               |

Table 4-10. Logic Analyzer Connector J16 Pin Assignments

| Pin   | Mnemonic | Signal                                                                                                                                                                |

|-------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 – 4 | SPARE    | No connection                                                                                                                                                         |

| 5     | IC1      | INPUT CAPTURE 1 – Input signal that latches the contents of the GPT timer counter (TCNT) into the input capture register TIC1 when a selected edge occurs at the pin. |

| 6     | IC2      | INPUT CAPTURE 2 – Input signal that latches the contents of the GPT timer counter (TCNT) into the input capture register TIC2 when a selected edge occurs at the pin. |

| 7     | IC3      | INPUT CAPTURE 3 – Input signal that latches the contents of the GPT timer counter (TCNT) into the input capture register TIC3 when a selected edge occurs at the pin. |

| 8     | OC1      | OUTPUT COMPARE 1 – Output signal that is generated when the GPT timer counter (TCNT) and TOC1 comparator register contain the same value.                             |

M68MPB16Y3UM/D 4-9

Table 4-10. Logic Analyzer Connector J16 Pin Assignments (continued)

| Pin     | Mnemonic | Signal                                                                                                                                                                |

|---------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9       | OC2      | OUTPUT COMPARE 2 – Output signal that is generated when the GPT timer counter (TCNT) and TOC2 comparator register contain the same value.                             |

| 10      | OC3      | OUTPUT COMPARE 3 – Output signal that is generated when the GPT timer counter (TCNT) and TOC3 comparator register contain the same value.                             |

| 11      | OC4      | OUTPUT COMPARE 4 – Output signal that is generated when the GPT timer counter (TCNT) and TOC4 comparator register contain the same value.                             |

| 12      | IC4/     | INPUT CAPTURE 4 – Input signal that latches the contents of the GPT timer counter (TCNT) into the input capture register TIC4 when a selected edge occurs at the pin. |

|         | OC5      | OUTPUT COMPARE 5 – Output signal that is generated when the GPT timer counter (TCNT) and TOC5 comparator register contain the same value.                             |

| 13 – 19 | SPARE    | No connection                                                                                                                                                         |

| 20      | GND      | GROUND                                                                                                                                                                |

**Table 4-11. Logic Analyzer Connector J17 Pin Assignments**

| Pin    | Mnemonic  | Signal                                                                                            |

|--------|-----------|---------------------------------------------------------------------------------------------------|

| 1 – 4  | SPARE     | No connection                                                                                     |

| 5      | VSSA      | A/D GROUND – A/D ground reference.                                                                |

| 6 – 11 | AN5 – AN0 | ANALOG TO DIGITAL CONVERSION 5 -0 – Analog input lines to the MCU device.                         |

| 12     | VRH       | VOLTAGE REFERENCE HIGH – Input reference supply voltage (high) line (must set jumper on the MPB). |

| 13     | VRL       | VOLTAGE REFERENCE LOW – Input reference supply voltage (low) line (must set jumper on the MPB).   |

| 14, 15 | AN6, AN7  | ANALOG TO DIGITAL CONVERSION 6 and 7 – Analog input lines to the MCU device.                      |

4-10 M68MPB16Y3UM/D

Table 4-11. Logic Analyzer Connector J17 Pin Assignments (continued)

| Pin     | Mnemonic | Signal                             |

|---------|----------|------------------------------------|

| 16      | VSSA     | A/D GROUND – A/D ground reference. |

| 17 – 19 | SPARE    | No connection                      |

| 20      | VSSA     | A/D GROUND – A/D ground reference. |

Table 4-12. Logic Analyzer Connector J18 Pin Assignments

| Pin     | Mnemonic    | Signal                                                                                                                                           |

|---------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 – 4   | SPARE       | No connection                                                                                                                                    |

| 5       | PCS0/       | PERIPHERAL CHIP SELECT 0 – Active-low output SPI peripheral chip select signal.                                                                  |

|         | SS          | SLAVE SELECT – Bi-directional, active-low signal that initiates serial transmission when SPI is in slave mode; causes mode fault in master mode. |

| 6       | MOSI        | MASTER-IN, SLAVE-OUT – Serial input to SPI in master mode; serial output from SPI in slave mode.                                                 |

| 7       | MISO        | MASTER-OUT, SLAVE-IN – Serial output from SPI in master mode; serial input to SPI in slave mode.                                                 |

| 8       | SCK         | SPI SERIAL CLOCK – In master mode, the clock signal from the SPI; in slave mode the clock signal to the SPI.                                     |

| 9       | TXDA        | TRANSMIT DATA A – Serial data output line to serial communication interface A.                                                                   |

| 10      | RXDA        | RECEIVE DATA A – Serial data input line to serial communication interface A.                                                                     |

| 11      | TXDB        | TRANSMIT DATA B– Serial data output line to serial communication interface B.                                                                    |

| 12      | RXDB        | RECEIVE DATA B – Serial data input line to serial communication interface B.                                                                     |

| 13 – 16 | TPU0 – TPU3 | TIME PROCESSOR UNIT CHANNELS – TPU input/output channels.                                                                                        |

| 17 – 19 | SPARE       | No connection                                                                                                                                    |

| 20      | GND         | GROUND                                                                                                                                           |

M68MPB16Y3UM/D 4-11

Table 4-13. Logic Analyzer Connector J19 Pin Assignments

| Pin     | Mnemonic     | Signal                                                   |

|---------|--------------|----------------------------------------------------------|

| 1 – 4   | SPARE        | No connection                                            |

| 5 – 12  | TPU4 – TPU11 | TIME PROCESSOR UNIT CHANNELS – TPU input/output channels |

| 13 – 19 | SPARE        | No connection                                            |

| 20      | GND          | GROUND                                                   |

Table 4-14. Logic Analyzer Connector J20 Pin Assignments

| Pin     | Mnemonic      | Signal                                                                          |

|---------|---------------|---------------------------------------------------------------------------------|

| 1 – 4   | SPARE         | No connection                                                                   |

| 5 – 8   | GND           | GROUND                                                                          |

| 9       | PCS2          | PERIPHERAL CHIP SELECT 2 – Active-low output SPI peripheral chip select signal. |

| 10      | PCS1          | PERIPHERAL CHIP SELECT 1 – Active-low output SPI peripheral chip select signal. |

| 11 – 13 | GND           | GROUND                                                                          |

| 14      | T2CLK         | TPU CLOCK – External input clock source to the TPU.                             |

| 15 – 18 | TPU15 – TPU12 | TIME PROCESSOR UNIT CHANNELS – TPU input/output channels.                       |

| 19      | SPARE         | No connection                                                                   |

| 20      | GND           | GROUND                                                                          |

4-12 M68MPB16Y3UM/D

## CHAPTER 5 MAPI SUPPORT INFORMATION

## 5.1 INTRODUCTION

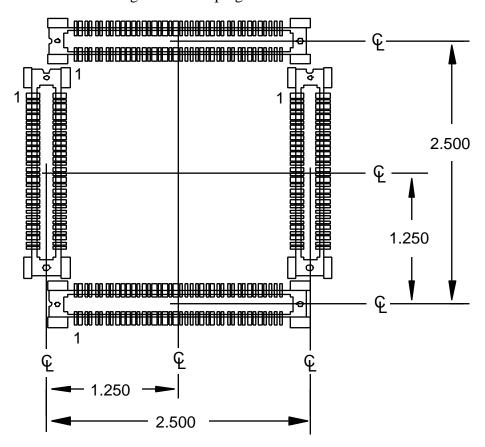

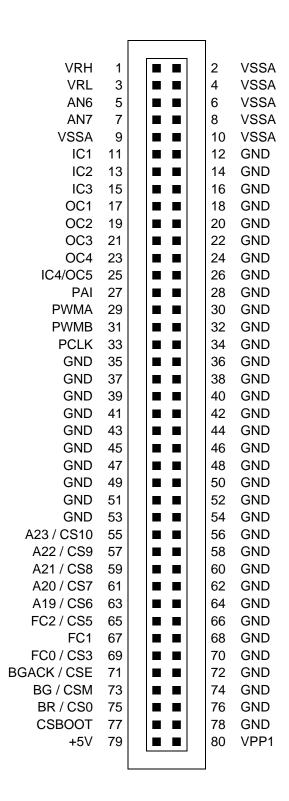

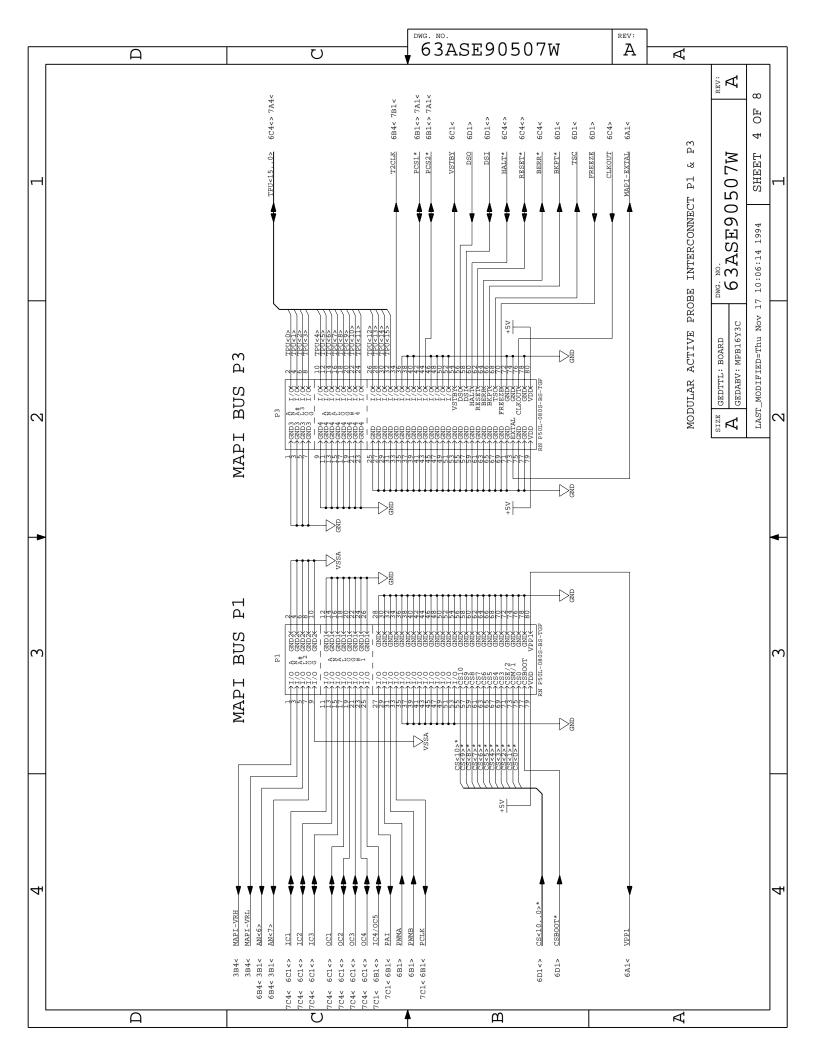

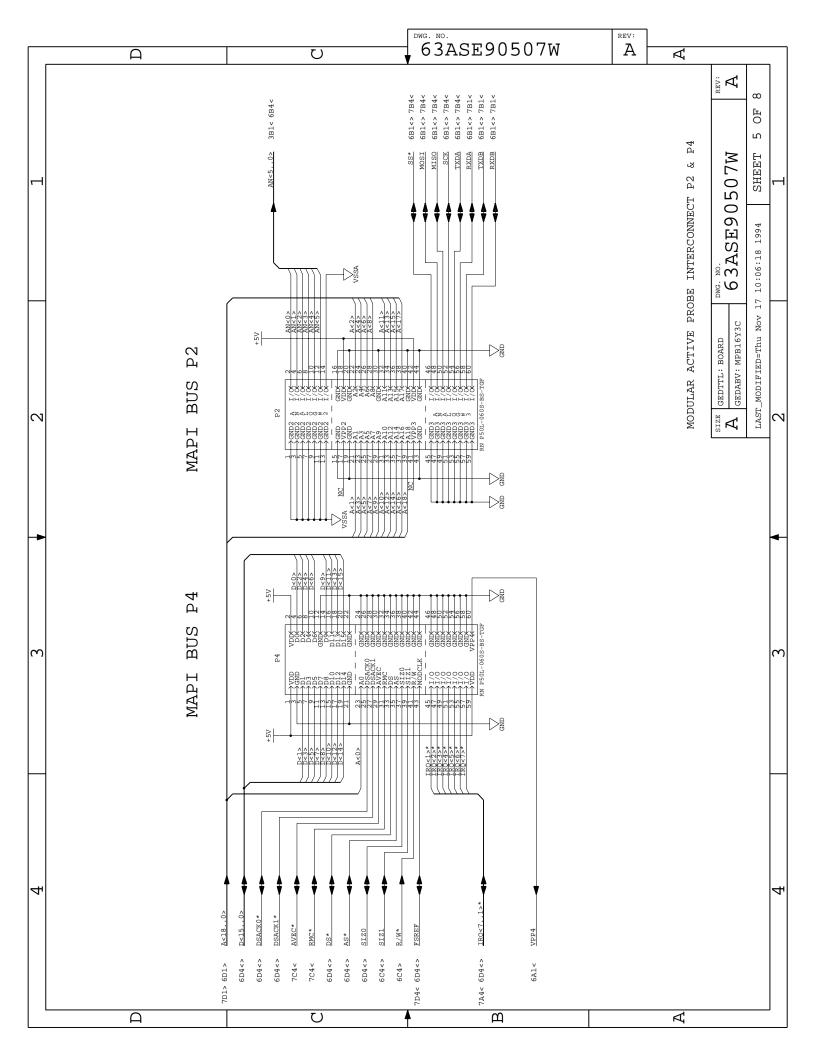

The information in this chapter is relevant when the MPB is to be installed on a target system. The figures in this chapter show the MAPI interface connector layout and pin assignments for MPB connectors P1, P2, P3, and P4.

The connectors required to interface to the MAPI bus are:

- 2 Robinson Nugent 2 X30 plugs P50L-060P-AS-TGF

- 2 Robinson Nugent 2 X40 plugs P50L-080P-AS-TGF

Figure 5-1. MAPI Interface Connector Layout

M68MPB16Y3UM/D 5-1

Figure 5-2. MAPI Interface Connector P1 Pin Assignments

5-2 M68MPB16Y3UM/D

Figure 5-3. MAPI Interface Connector P2 Pin Assignments

M68MPB16Y3UM/D 5-3

Figure 5-4. MAPI Interface Connector P3 Pin Assignments

5-4 M68MPB16Y3UM/D

Figure 5-5. MAPI Interface Connector P4 Pin Assignments

M68MPB16Y3UM/D 5-5

5-6 M68MPB16Y3UM/D

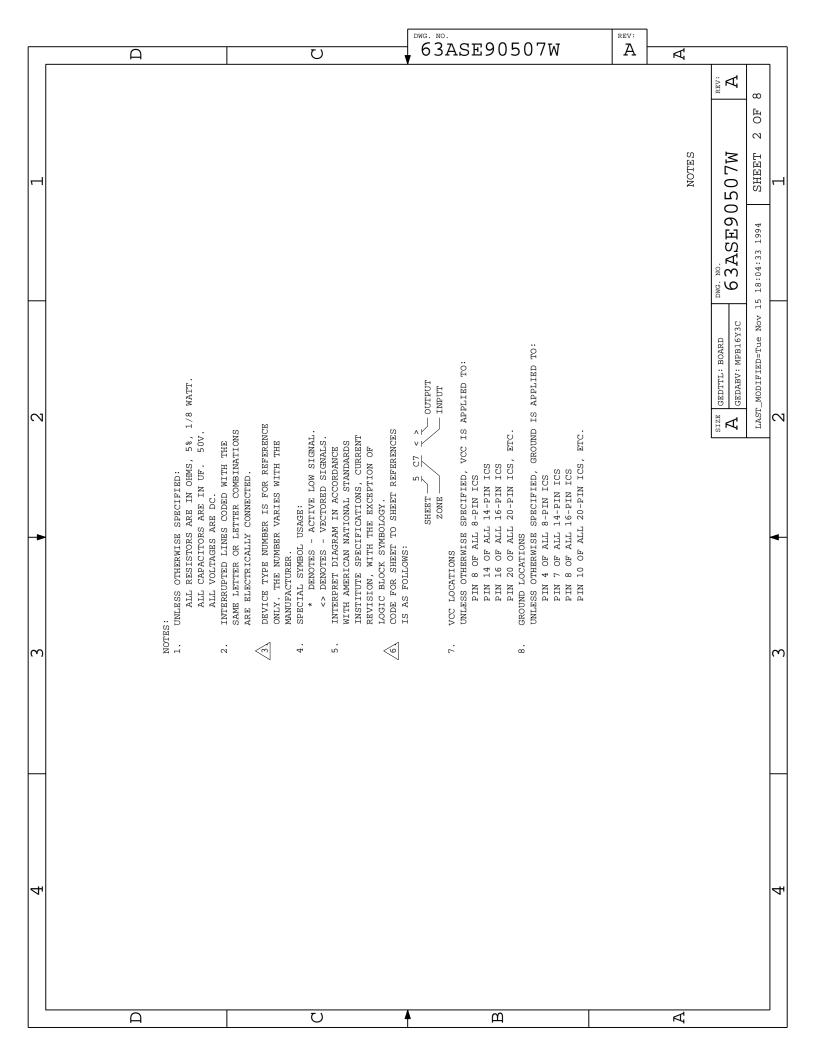

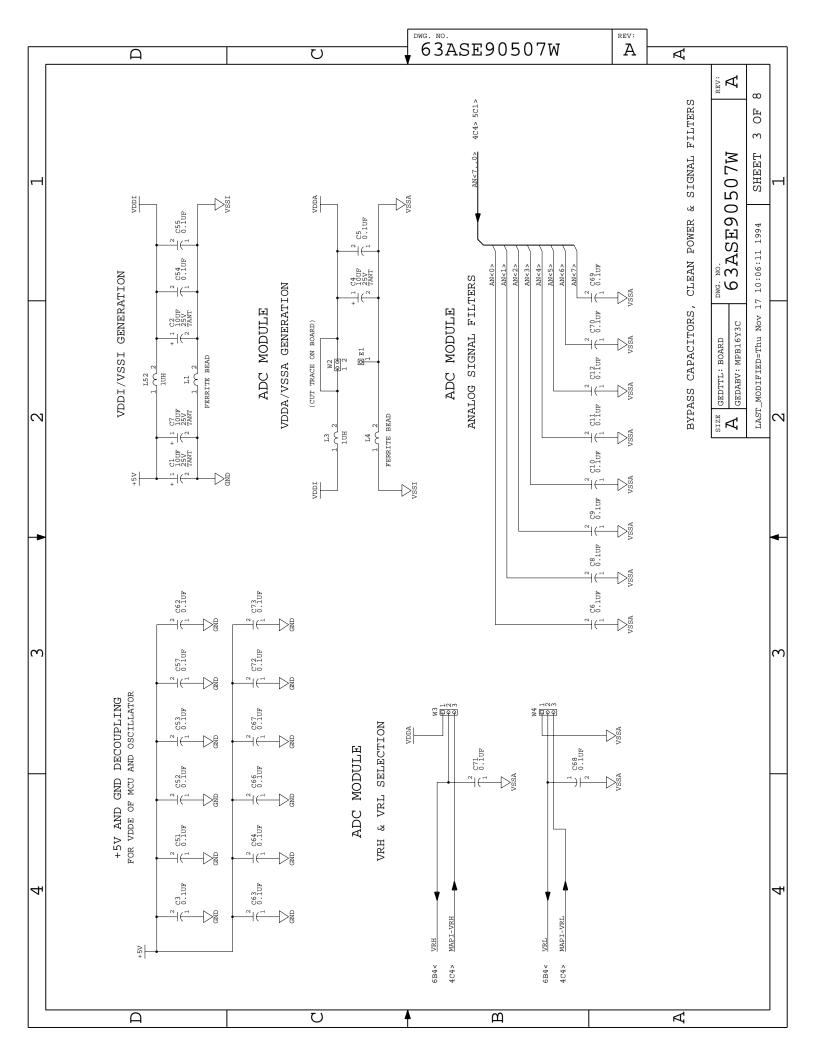

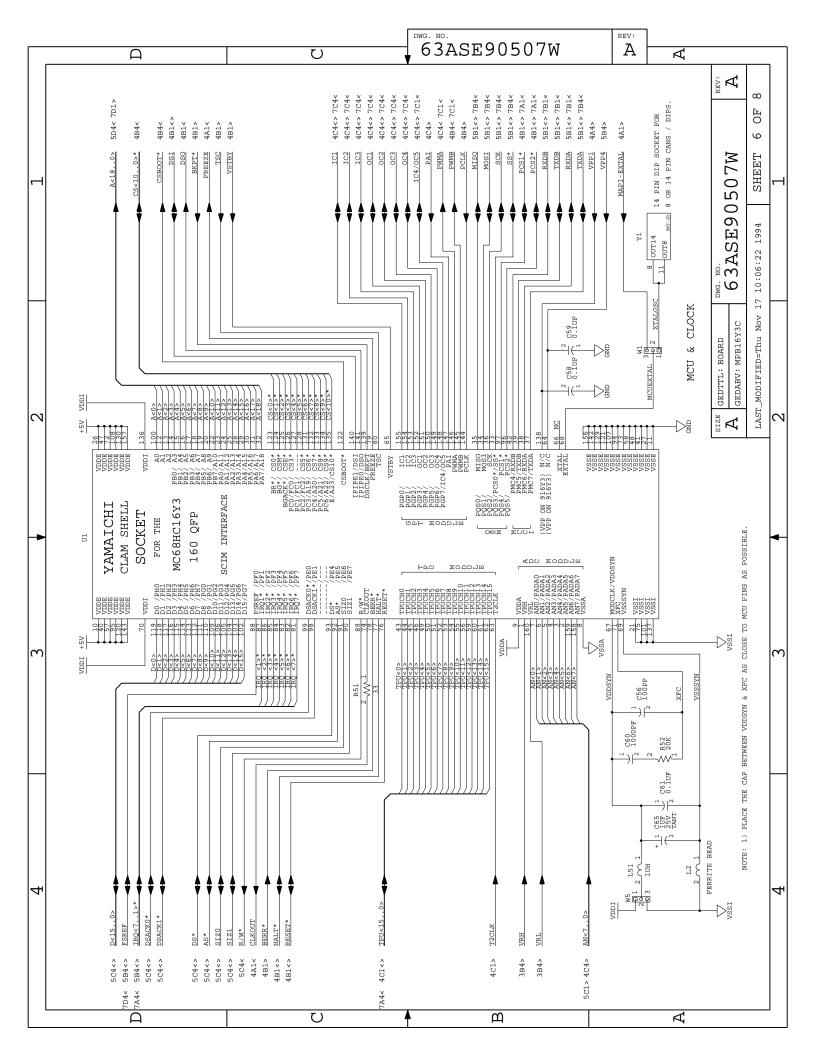

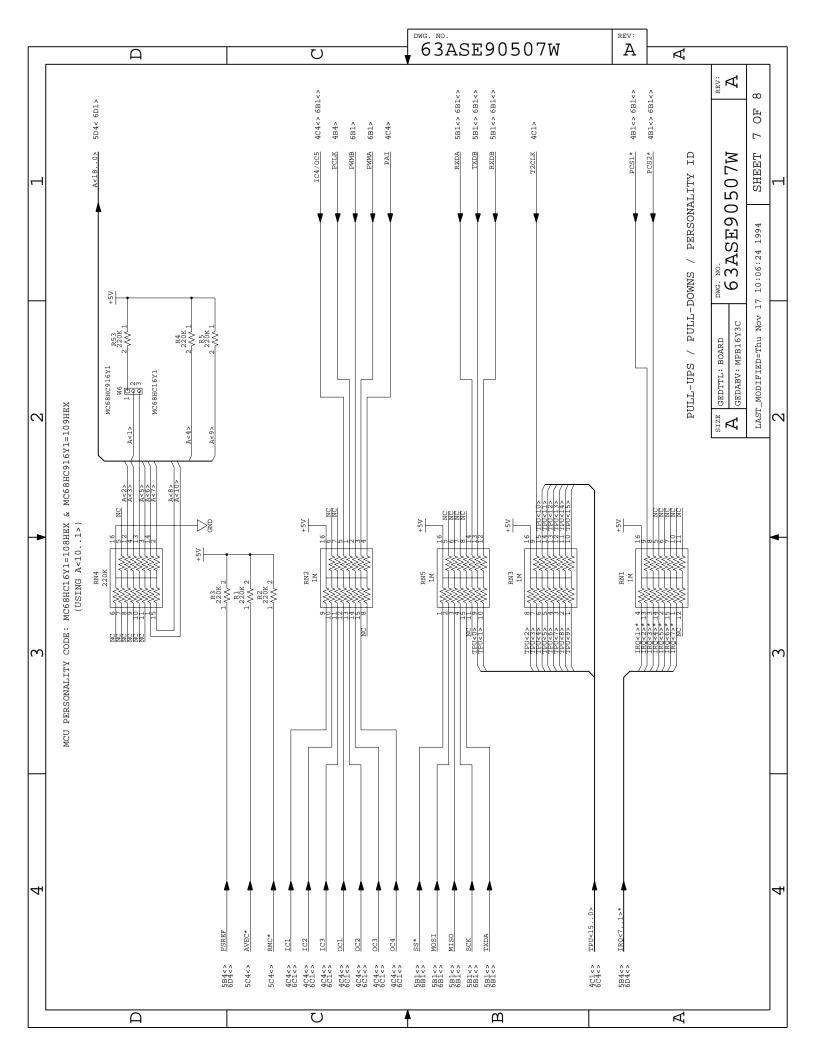

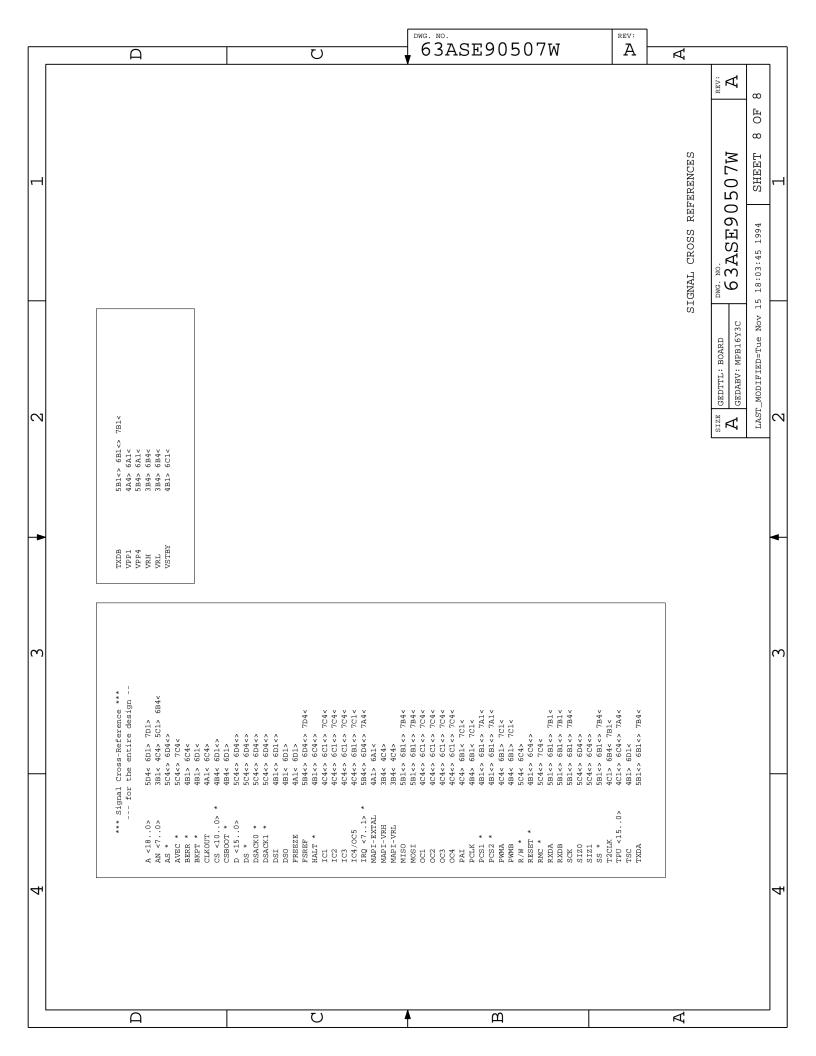

## CHAPTER 6 SCHEMATIC DIAGRAMS

## **6.1 INTRODUCTION**

This chapter contains the M68MPB916Y3 MCU Personality Board (MPB) schematic diagrams. These schematic diagrams are for reference only and may deviate slightly from the circuits on your MPB.

M68MPB16Y3UM/D 6-1

6-10 M68MPB16Y3UM/D