#### AN1770

### In-Circuit Programming of FLASH Memory in the MC68HC908GP20

By Grant Whitacre Microcontroller Division Austin, Texas

#### Introduction

This application note describes two methods of programming FLASH memory in the Motorola MC68HC908GP20 (GP20) microcontroller, a general-purpose device based on the 68HC08 architecture that has 20 Kbytes of on-board FLASH.

Programming the FLASH array can be done either in user mode or monitor mode. The information given here details:

- How the FLASH is programmed and erased in-circuit in each of these two modes

- · How the control and protection registers are programmed

- Additional considerations when dealing with this type of memory

To illustrate the GP20's in-circuit programming capabilities, a sample program is included which executes programming routines from RAM.

These RAM routines are loaded in one of two ways:

- When programming in user mode, the routines would be part of and transferred into RAM by a bigger program residing in FLASH. This program could be initiated by the user's main program, perhaps through the monitoring of an input port, or it could be loaded into FLASH as a stand-alone seed program which would later enable re-programming of the entire FLASH array with the actual user program.

- Alternatively, the RAM routines could be loaded directly into RAM by an external host with the device in monitor mode.

The main routine of this dual mode program monitors the SCI (serial communications interface) port when user mode programming, or port A bit 0 when monitor mode programming, for the input of data and the address range in FLASH where the data is to be programmed. It then makes necessary calls to other RAM-loaded routines to do necessary erasing, programming, and verifying.

A host program's necessary functionality is also described in this application note. The one specifically used in the generation of this document is a Windows® application and accommodates both modes of programming. It is available as a free download from the Motorola web site, http://mot-sps.com/csic/techhelp/appsw/appsw.htm.

The user will be able to in-circuit program the GP20 in either monitor mode or user mode with:

- This host program

- Two MC68HC908GP20 RAM programs in S19 format

- A target system that is configured to communicate with a PC host

- A basic understanding of the device and its FLASH memory

Windows is a registered trademark of Mircrosoft in the U.S. and other countries.

#### Description of FLASH Memory in the MC68HC908GP20

#### Memory Map FLASH Location

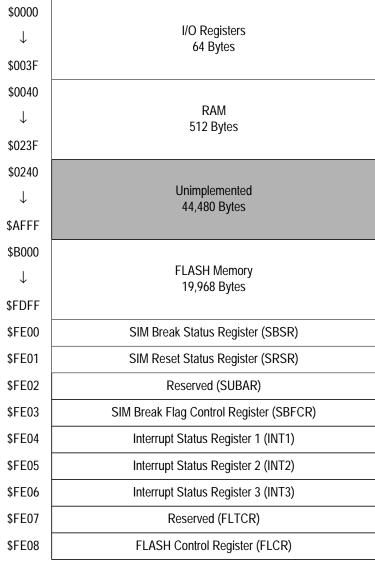

The memory map for the MC68HC908GP20 is shown in **Figure 1**. Note that the FLASH memory occupies addresses from \$B000 to \$FDFF, a single byte for the block protection register at \$FF80, and a block for the user vectors from \$FFDC to \$FFFF. The total addressable FLASH capacity is 20,005 bytes.

Figure 1. Memory Map (Sheet 1 of 2)

#### **Application Note**

|                     | \$FE09       | Break Address Register High (BRKH)                       |

|---------------------|--------------|----------------------------------------------------------|

|                     | \$FE0A       | Break Address Register Low (BRKL)                        |

|                     | \$FE0B       | Break Status and Control Register (BRKSCR)               |

|                     | \$FE0C       | LVI Status Register (LVISR)                              |

|                     | \$FE0D       |                                                          |

|                     | $\downarrow$ | Unimplemented<br>3 Bytes                                 |

|                     | \$FE0F       |                                                          |

|                     | \$FE10       | Unimplemented                                            |

|                     | $\downarrow$ | 16 Bytes<br>Reserved for Compatibility with Monitor Code |

|                     | \$FE1F       | for A-Family Parts                                       |

|                     | \$FE20       | Monitor ROM                                              |

|                     | $\downarrow$ | 307 Bytes                                                |

|                     | \$FF52       |                                                          |

|                     | \$FF53       |                                                          |

|                     | $\downarrow$ | Unimplemented<br>45 Bytes                                |

|                     | \$FF7F       |                                                          |

|                     | \$FF80       | FLASH Block Protect Register (FLBPR)                     |

|                     | \$FF81       |                                                          |

|                     | $\downarrow$ | Unimplemented<br>91 Bytes                                |

|                     | \$FFDB       |                                                          |

| Note: \$FFF6-\$FFFD | \$FFDC       |                                                          |

| Also Used for       | $\downarrow$ | FLASH Vectors<br>36 Bytes                                |

| 8 Security Bytes    | \$FFFF       |                                                          |

Figure 1. Memory Map (Sheet 2 of 2)

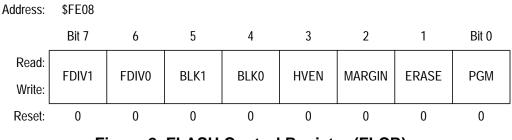

## FLASH ControlThe FLASH control register is located at \$FE08 in the user memory map.RegisterThis register provides the means to erase, program, and verify the<br/>FLASH. All bits in this register can be read or written at any time. The<br/>register structure is shown in Figure 2.

Figure 2. FLASH Control Register (FLCR)

The FDIV bits are frequency divide control bits and are set to ensure proper operation for the charge pump. Its optimum frequency is about 2 MHz and is derived by dividing the internal bus frequency by a value stored in FDIV1 and FDIV0. Setting of these two bits should be made according to bus frequency as shown in **Table 1**.

Table 1. Charge Pump Clock Frequencyas a Function of Bus Frequency

| FDIV1 | FDIV0 | Use When Bus<br>Frequency Is |              |

|-------|-------|------------------------------|--------------|

| 0     | 0     | Bus frequency ÷ 1            | 1.8–2.5 MHz  |

| 0     | 1     | Bus frequency ÷ 2            | 3.6–5.0 MHz  |

| 1     | 0     | Bus frequency ÷ 2            | 3.6–5.0 MHz  |

| 1     | 1     | Bus frequency ÷ 4            | 7.2–10.0 MHz |

**NOTE:** There is no mechanism to step up the pump clock frequency from a bus frequency lower than 1.8 MHz to attain a charge pump frequency of about 2 MHz. Also, programming and erasing the FLASH cannot be done if the charge pump frequency is lower than 1.8 MHz.

BLK1 and BLK0 are block erase control bits and are used to specify the size and location of a block of FLASH to be erased. Erasing can take place in chunks of a single row (64 bytes), eight rows (512 bytes), 4 Kbytes, 16 Kbytes, or the entire array. The procedure for erasing any

of these blocks of FLASH is discussed in **Procedure for Erasing the FLASH**. The setting of the BLK bits corresponds to the erase block as shown in **Table 2**.

| BLK1 | BLK0 | Block Size                     |

|------|------|--------------------------------|

| 0    | 0    | Full array: 20 Kbytes          |

| 0    | 1    | Partial array*: 4 or 16 Kbytes |

| 1    | 0    | Eight rows: 512 bytes          |

| 1    | 1    | Single row: 64 bytes           |

Table 2. Size of Erase Blocks

\* \$B000-\$BFFF or \$C000-\$FFFF, depending on bit A14 of address written to

HVEN is the high-voltage enable bit and provides the control to apply the charge pump voltage to the cells to be erased or programmed.

The MARGIN bit is used during programming to verify that the page attempting to be programmed gets programmed adequately. It can only be set for verification after the HVEN bit is turned off. If it is high when HVEN is turned on, it will clear automatically. Setting the MARGIN bit puts the FLASH in a "hard read" state, which ensures that if the FLASH is verified in this state then it guarantees a good read during normal operation.

The ERASE and PGM (program) control bits are required to be set when erasing and programming, respectively. Both cannot be set at the same time.

Block Protection The block protection register provides a way of preventing a block of FLASH from being erased or programmed. This register, itself a FLASH address, has four bits with each bit protecting a progressively larger block of FLASH starting at \$FFFF. Figure 3 shows the register contents and the FLASH range that is protected by setting each bit.

Erasing this register clears all bits and removes protection from all blocks.

**NOTE:** Setting more than one bit is redundant, and three of the bits provide protection of a FLASH range some of whose locations are not available in the GP20. Setting bits 0, 1, or 2 protects all of FLASH, and setting only bit 3 protects all but the lower 1000H bytes.

|        | Bit 7 | 6     | 5     | 4     | 3      | 2      | 1      | Bit 0  |

|--------|-------|-------|-------|-------|--------|--------|--------|--------|

| Read:  | Bit 7 | Bit 6 | Bit 5 | Bit 4 | BPR3   | BPR2   | BPR1   | BPR0   |

| Write: | Bit / | Ditto | Dir o | Dit 1 | DI Ito | DI ILZ | Britti | DI III |

| Reset: | U     | U     | U     | U     | U      | U      | U      | U      |

U = Unaffected by reset. Initial value from factory is 0.

#### Figure 3. FLASH Block Protect Register (FLBPR)

| Bit Location | Bit Name | Address Block Protected |

|--------------|----------|-------------------------|

| 0            | BPR0     | \$B000-\$FFFF           |

| 1            | BPR1     | \$B000-\$FFFF           |

| 2            | BPR2     | \$B000-\$FFFF           |

| 3            | BPR3     | \$C000-\$FFFF           |

#### Table 3. Block Protection Register and Size<br/>and Location of Block Protected

Protection of any block protects the block protection register because it is located at address FF80. The only way to circumvent block protection to modify FLASH is to enter monitor mode with V<sub>TST</sub> applied to the IRQ line upon reset. (See the monitor mode entry in **Circuit Requirements**.) When this occurs, all of FLASH, including the block protection register, can be erased or programmed regardless of block protection.

**NOTE:** Since the block protection register is located at \$FF80, it is the first byte in a row whose range is \$FF80–\$FFBF. There are no other implemented FLASH locations within this row, so this register can be erased with no impact to other locations by specifying row erasing with the BLK bits in the FLASH control register (BLK1 = BLK0 = 1).

> To program FLASH in user mode, make sure that the FLASH to be modified is not block protected; otherwise, turn block protection off as in the example described here.

#### Procedure for Erasing the FLASH

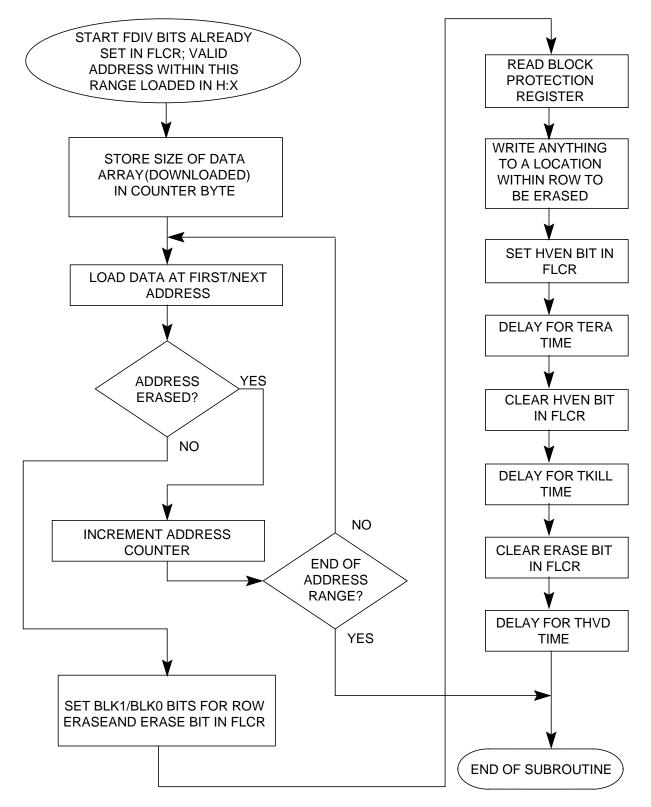

The FLASH array is erased as a block, the size of which is determined by the BLK bits of the FLASH control register, as shown in **Table 2**. Follow this step-by-step procedure to erase a block of FLASH reliably.

- Make sure that the block to be erased is not protected by the settings in the block protection register. See Block Protection for a description of clearing protection for a block.

- 2. Write to the FLASH control register with a bit pattern that sets the appropriate FDIV bits and BLK bits. Set the ERASE bit at the same time.

- 3. Read the block protect register so that the FLASH control logic can latch its content.

- 4. Write any data to any FLASH address within the block to be erased.

- 5. Set the HVEN bit in the FLASH control register to apply the programming (charge pump) voltage.

- Delay for a time, t<sub>Erase</sub> (FLASH erase time), while the programming voltage is applied. Consult the memory characteristics information in the electrical specifications section of *MC68HC908GP20 Advance Information*, Motorola document order number MC68HC908GP20/D, for this value and other times referenced in this application note.

- 7. Clear the HVEN bit to turn off the programming voltage.

- 8. Delay for a time, t<sub>Kill</sub> (high voltage kill time), to allow the high voltage of the charge pump to dissipate.

- 9. Clear the ERASE bit.

- Delay for a time, t<sub>HVD</sub> (FLASH return to read time), before trying to read from this block of FLASH.

Optionally, an erase verification may be performed after step 10. This verification would be done with a normal read of each location of FLASH, and a location would be verified as erased if a value of 0 is read.

**NOTE:** It is recommended that a row be erased after eight programs of any page/pages of the row.

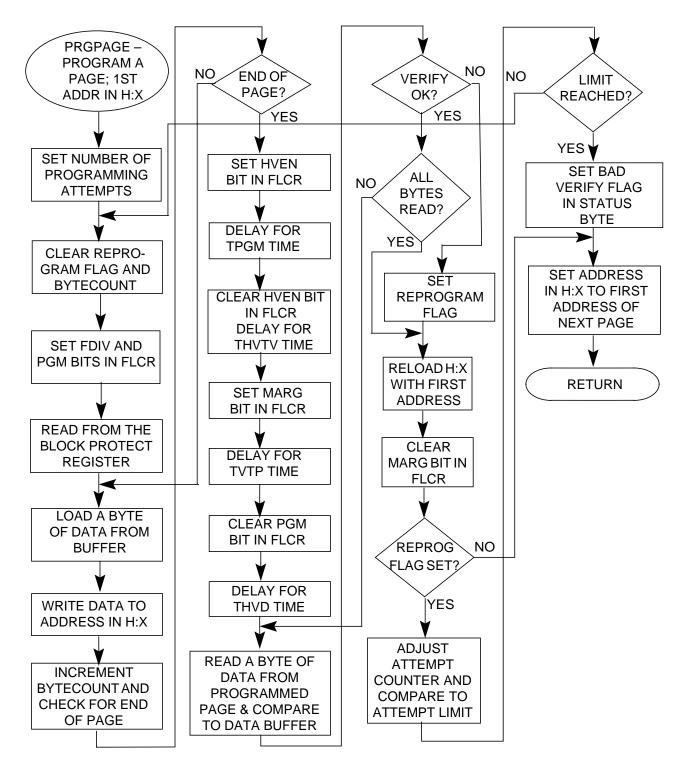

#### Procedure for Programming the FLASH

The FLASH array is programmed a page at a time, where a page is defined as eight contiguous bytes whose first byte is on an 8-byte boundary. The normal programming sequence includes a verification step during which the FLASH is put in a "margin read" verification mode. In this mode, the control gates are held at a lower voltage than in a normal read. To allow sensing of the lower cell current, reads in this mode last eight machine cycles longer than a normal read.

Follow this procedure to reliably program and verify a page of FLASH.

- 1. Make sure that the page to be programmed is not within a protected block. See the block protection section for a description of clearing protection for a block.

- 2. Write to the FLASH control register with a bit pattern that sets the appropriate FDIV bits. Set the PGM bit at the same time.

- 3. Read the block protect register so that the FLASH control logic can latch its content.

- 4. Write individual data to each of the eight bytes of the page to be programmed.

- 5. Set the HVEN bit in the FLASH control register to apply the programming (charge pump) voltage.

- Delay for a time, t<sub>PROG</sub> (FLASH program time), while the programming voltage is applied.

- 7. Clear the HVEN bit to turn off the programming voltage.

- Delay for a time, t<sub>HVTV</sub> (FLASH HVEN low to MARGIN high time), to allow enough time between applying high voltage and doing a verification.

- 9. Set the MARGIN bit to initiate verification mode.

- 10. Delay for a time,  $t_{VTP}$  (FLASH MARGIN high to PGM low time).

- 11. Clear the PGM bit.

- Delay for a time, t<sub>HVD</sub> (FLASH return to read time), before trying to read from this block of FLASH.

- 13. Read the individual data in each of the eight byte locations to compare to what was intended to be programmed.

- 14. Clear the MARGIN bit.

- 15. Repeat steps 2 through 14 for each page until the data matches.

#### Practical Considerations for Programming, Verifying, and Erasing

| Life Expectancy<br>in Terms<br>of Program/Erase<br>Cycling | The FLASH in the MC68HC908GP20 has an endurance specification of 100 erase/program cycles. Therefore, it is not suited for short-term or temporary non-volatile parameter storage. This limitation could be alleviated somewhat by devising a scheme to move the parameter storage area when it approaches the 100-cycle limit.                                                                                                                                                              |

|------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                            | For example, if a row (64 bytes) of parameter data is to be stored and<br>updated on a frequent basis and the program is short enough to occupy<br>less than two-thirds of the 20-Kbyte capacity, then a method of moving<br>the location of the parameter block when the number of erase/program<br>cycles approach 100 (cycle count could be stored in this block) could be<br>implemented. In this example, this would effectively increase the number<br>of parameter updates to 10,400. |

|                                                            | Unused FLASH: 1/3 x 19,968 bytes = 6656 bytes = 104 rows                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                            | 100 cycles/row x 104 rows in the unused FLASH space = 10,400<br>erase/program cycles                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                            | Since the smallest block erased is an entire row, whenever one byte is<br>changed, the entire row would need to be erased and reprogrammed.<br>Because of this limitation with FLASH, using it to store non-volatile<br>temporary values is of limited usefulness.                                                                                                                                                                                                                           |

MarginMargin, or bump, programming is a method of FLASH programmingProgrammingwhich is done in successive periods of relatively short duration, such as<br/>1 millisecond. After each "bump," the page that is attempted to be<br/>programmed is checked in margin mode, and if verification of any byte<br/>in the page fails, the entire page is re-programmed, without erasing, for<br/>another bump period. This process is repeated until all bytes in the page<br/>pass verification.

Bump programming minimizes the programming time, not only for the user's benefit but also for the endurance of the FLASH. By minimizing the amount of time that a FLASH cell is exposed to the programming voltage, the life of the cell is maximized and the possibility of disturbing (inadvertently programming) neighboring cells by an excessively long programming time is minimized. The RAM program contained in this application note utilizes this method of programming, as does the information in **Procedure for Programming the FLASH**.

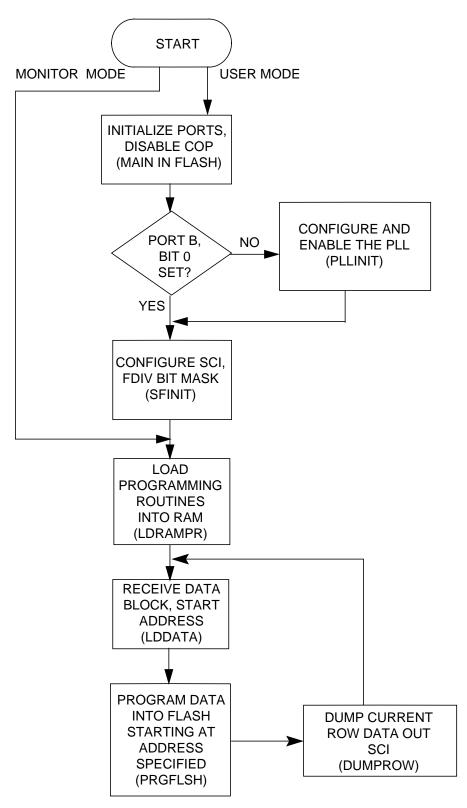

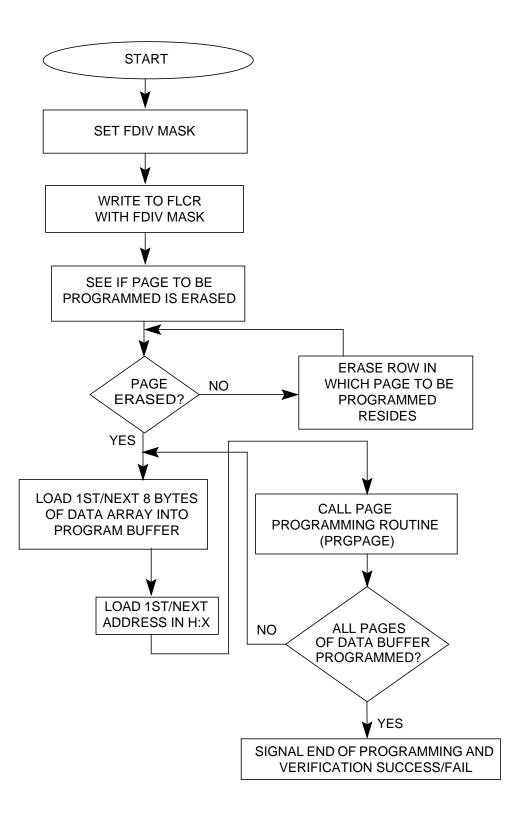

#### Programming the MC68HC908GP20 in User Mode

Program Algorithm Included in this application note is a program that demonstrates the capability to perform in-circuit programming. By setting assembler directives, this program can be loaded into FLASH and run in user mode, so no special mode entry hardware is required. After an initialization and loading of the RAM routine executed from FLASH, initiated either upon reset or subroutine call from the user's existing main program, the program branches to a place in RAM where program execution resumes.

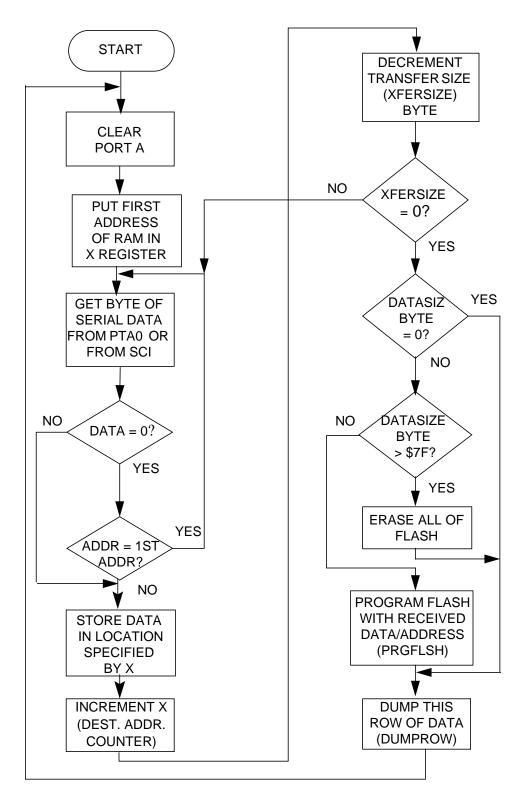

From RAM, the SCI serial communication port is monitored for the download of data to be programmed into FLASH and the starting address to place this data. After this data is received, the main RAM routine calls necessary subroutines, also located in RAM, to perform necessary FLASH erasing, programming, verification, and memory dumping. Up to a row (64 bytes) of data can be downloaded at a time, although there are a few stipulations when downloading data to be programmed.

They are:

- All data downloaded must be intended to reside within a single row boundary. This means that the start address must be divisible by 64 when an entire row is to be programmed.

- If data forming less than an entire row is downloaded, the previous rule still applies. All intended addresses must be within a single row boundary. Additionally, since programming takes place eight bytes at a time, a multiple of eight bytes should be downloaded and the starting address must be on a page (8-byte) boundary.

- The program checks to see if all intended addresses are erased before attempting to program. If any cell is not erased, then the entire row is erased. So, if programming less than an entire row, remember that the entire row will be erased if the block designated for reprogramming is not completely erased.

- At the completion of each block programming, the data is read from the current row and all 64 bytes of the row are sent out the SCI port, even if less than the entire row was reprogrammed.

This main RAM routine executes a continuous loop so that multiple data downloads can take place without the program ever leaving RAM. In fact, the entire FLASH array can be (re)programmed in this manner. At the completion of programming, the device will need to be reset to take it out of the SCI monitoring routine and to execute the new code in FLASH.

After receiving data to be programmed and loading RAM with necessary programming code, program execution jumps to RAM to do the actual FLASH programming.

The program consists of the functions listed here:

- Initialize all variables, ports, PLL (if selected), and SCI.

- Transfer these subroutines to RAM:

- LOADDATA Polls the SCI for data to be programmed, the start address, and length of data array (see Message Structure to Communicate between Host and GP20). This routine also calls the other RAM routines as needed.

- DUMPROW Dumps the contents of the current row (64 bytes) out the SCI

- PRGFLSH Controls the routine to program a row of FLASH

- ERACHK Checks to see if FLASH needs to be erased and does so, if necessary

- DELNUS Delays for n microseconds (n preloaded into H:X)

- PRGPAGE Programs a page (eight bytes) of FLASH

- Execute code to program FLASH out of RAM, making necessary calls to other RAM routines to perform actual programming/erasing.

- Return to SCI port monitoring loop in RAM

RAM Utilization and Program Execution Since program execution cannot occur out of a FLASH block at the same time it is being modified, and since this device has only one block of nonvolatile memory, execution of code to modify the FLASH must be from RAM (or from monitor ROM which will be discussed later).

The program which resides in FLASH loads the necessary programming and erasing modules to RAM and then jumps to the main RAM routine which, when appropriate, makes calls to other RAM modules. Since RAM capacity in the GP20 is 512 bytes, the code executed in RAM is kept to that size.

Therefore, only the programming, erasing and dumping routines, the array of data to be programmed, necessary variables, and the stack fit into RAM. Almost all of RAM is used by the program, variables, message buffer, and stack.

The RAM utilization map is found in **Table 4**.

| Function                          | Allocated Space | Address Range |  |

|-----------------------------------|-----------------|---------------|--|

| Unused                            | 16 bytes        | \$40-\$4F     |  |

| Download size                     | 1 byte          | \$50          |  |

| Start address of block to program | 2 bytes         | \$51–\$52     |  |

| Number of bytes to program        | 1 byte          | \$53          |  |

| Data array                        | 64 bytes        | \$54–\$93     |  |

| Variables                         | 20 bytes        | \$94–\$A7     |  |

| RAM routines                      | 56 bytes        | \$A8-\$DF     |  |

| Stack                             | 32 bytes        | \$E0\$FF      |  |

| RAM routines                      | 320 bytes       | \$100–\$23F   |  |

#### Table 4. RAM Utilization Map

## AssemblerA few switches in the program are implemented through assemblerDirectivesdirectives. They were left in the program for mode configuration and<br/>ease of user testing, especially in an emulation environment.

The directive constant and its use and meaning are outlined in Table 5.

| Assembler<br>Constant | Use                                                                                                                                                                                             |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MONPROG               | If set, all (necessary) routines will be addressed in RAM initially.<br>This version would be used as the S19 record file that is<br>downloaded into RAM in monitor mode for FLASH programming. |

| TESTMOD               | When set, changes all STA to LDA in programming/erase routines.<br>Done to prevent an illegal write error when emulating.<br>Programming is not attempted so any verification step will fail.   |

| ERSDTST               | When set, always causes erase verification to be true. Done to exercise good loop logic.                                                                                                        |

#### Table 5. Assembler Directives

#### Other Application-Specific Memory and I/O Equates

Several other constants are used in the program which can be modified as desired by the user. This may be necessary if the user wishes to incorporate this program into an existing program which is already fixed in memory.

| Constant                                               | Default<br>Value                         | Other Possible Settings                                                                    | Description                                                                                                                                                                   |

|--------------------------------------------------------|------------------------------------------|--------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CPUSPD                                                 | 2                                        | 4, 8                                                                                       | Specifies the bus frequencies:<br>2 = 2.45 MHz, 4 = 4.92 MHz, 8 = 8.0 MHz                                                                                                     |

| RAM                                                    | \$50                                     | \$40-\$4F                                                                                  | Specifies the start address of RAM. All RAM locations are offset from this value.                                                                                             |

| STCKSIZ                                                | \$23                                     | Dependent on location of<br>branch to page 2                                               | Specifies the amount of RAM reserved for the stack                                                                                                                            |

| PRGSTRT                                                | \$B000                                   | Anywhere in FLASH                                                                          | Start of the FLASH program that launches the RAM program                                                                                                                      |

| RAMPRG                                                 | \$A8                                     | Anywhere after the variable space                                                          | Start of RAM program. Set here, just after the variable space                                                                                                                 |

| RAMPRSZ                                                | \$1A7                                    | Any value larger than the RAM<br>program size plus the stack<br>size, up to the end of RAM | Length of the RAM program plus the stack area                                                                                                                                 |

| TESTDAT                                                | \$C0                                     | Any byte value                                                                             | Value of all bytes, except size bytes, used in<br>test mode instead of downloaded value. Set<br>at this value so that the first address used<br>(\$C0C0) is on a row boundary |

| PRGTRIES                                               | 20                                       | Any value greater than 0                                                                   | Number of attempts to program a page<br>of FLASH before giving up                                                                                                             |

| VTPGM<br>VHLFTER<br>VTKILL<br>VTHVD<br>VTHVTV<br>VTVTP | 1000<br>50,000<br>200<br>50<br>50<br>150 | See programming timing specification in data book                                          | Programming times                                                                                                                                                             |

| PLLCHK                                                 | 0                                        | 1                                                                                          | Input port used to check if PLL is to be initiated; initiated when port is high                                                                                               |

| P, E, NHI,<br>NLO, L, R                                | 0, 1, 1,<br>\$2C,<br>\$80, 1             | See PLL setup procedure<br>in data book                                                    | PLL setup parameters; values used allow<br>external clock of 32.768 kHz to be stepped up<br>to 2.45-MHz bus frequency                                                         |

#### Table 6. Program Constants

#### **Application Note**

Proper ClockA constant called CPUSPD is set in the application-specific memory and<br/>I/O (input/output) equates section of the program. Its purpose is to allow<br/>the programmer to select one of three bus frequencies for this constant,<br/>which directly affects how the SCI, the FLASH control register, and<br/>timing constants are set up.

In particular, based on a CPUSPD setting of 2, 4, or 8, corresponding to an internal frequency of 2.4576, 4.9152, or 8.0 MHz, the SCI is set to communicate at 9600 baud (assuming the selection of the internal bus clock as the SCI clock source (see **SCI Setup**) and the FDIV bit in the FLASH control register is set to cause the closest to the optimum setting of the charge pump frequency of 2 MHz.

If the external clock frequency is such that it causes a bus frequency lower than required for proper charge pump operation, the PLL can be enabled. The PLL is turned on upon initial program execution if port B, bit 0 is set. In this event, the program assumes an external clock of 32.768 kHz and steps this up to 2.4576-MHz bus frequency. An initialization routine sets the baud rate for the SCI to 9600 and the FDIV divider to divide-by-1 for a charge pump frequency of 2.4576 MHz.

Make sure that the CPUSPD constant described earlier is set to 2 if the PLL is enabled. Also, if an external clock frequency other than 32.768 kHz exists that would necessitate the use of the PLL (external clock less than 8 MHz), then the PLL setup and this SCI/FDIV initialization routine (SFINIT) will have to be modified for proper communication and charge pump frequency requirements. (See note in **FLASH Control Register**.)

#### **PLL Setup**

Since this is not an application note on the use and control of the PLL, the description here is brief. The settings used are justified with calculations, and the means of making these settings are shown. The significance of each bit in each register is not covered. Refer to the clock generator module section in the GP20 data manual for details about proper setup.

The six control and status registers for the GP20's PLL are shown in **Figure 4**.

Application Note Programming the MC68HC908GP20 in User Mode

| Register Name                                        |                                                                                                                                                          | Bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4                                                      | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2                                                      | 1                                                       | Bit 0                                                   |

|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|---------------------------------------------------------|---------------------------------------------------------|

|                                                      | Read:                                                                                                                                                    | DULE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | PLLF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | PCS                                                    | PRE1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | PRE0                                                   | VPR1                                                    | VPR0                                                    |

| PLL Control Register<br>(PCTL)                       | Write:                                                                                                                                                   | F LLIL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | FLLON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 005                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                        |                                                         |                                                         |

|                                                      | Reset:                                                                                                                                                   | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0                                                      | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0                                                      | 0                                                       | 0                                                       |

|                                                      | Read:                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | LOCK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0                                                      | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0                                                      | 0                                                       | R                                                       |