M68HC11EVBU2/D

April 1998

# M68HC11EVBU UNIVERSAL EVALUATION BOARD USER'S MANUAL ADDENDUM

© MOTOROLA Inc. 1990, 1998; All Rights Reserved

Motorola reserves the right to make changes without further notice to any products herein to improve reliability, function, or design. Motorola does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part.

The computer program stored in the Read Only Memory of the device contains material copyrighted by Motorola Inc., first published 1990, and may be used only under a license such as the License For Computer Programs (Article 14) contained in Motorola's Terms and Conditions of Sale, Rev. 1/79.

Motorola Inc. is an Equal Opportunity/Affirmative Action Employer.

Motorola and the Motorola logo are registered trademarks of Motorola Inc.

#### Introduction

M68HC11EVBU2 is a promotional version of the standard M68HC11EVBU. This document describes the upgrade modifications that have been made to the original.

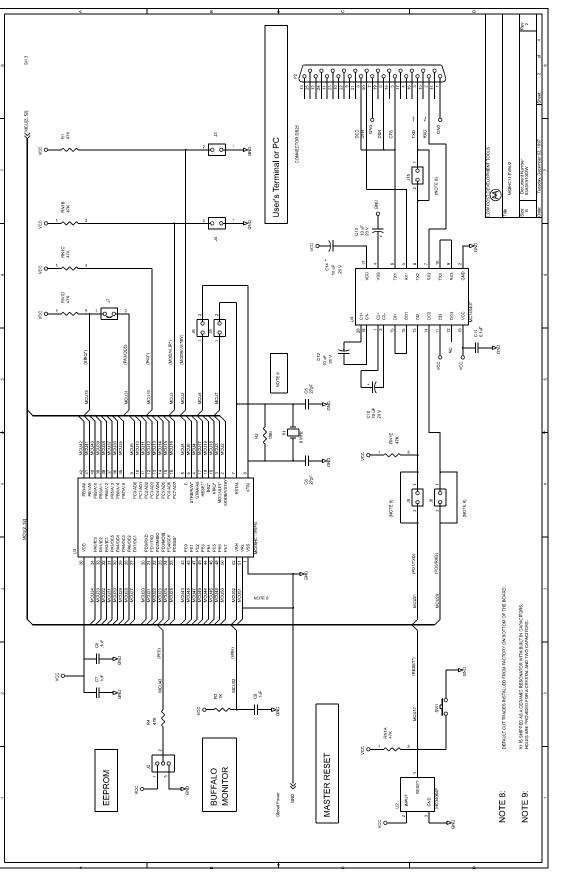

A 32K byte RAM was added in the wire-wrap area to provide more user memory. This RAM is accessible from address location \$8000 through \$FFFF except where an on-chip resource has higher priority. The board defaults to normal-expanded mode rather than single-chip mode so this additional RAM can be used.

For the M68HC11EVBU2 normal configuration, the MC68HC11E9 MCU on-chip ROM occupies the address space from \$D000 through \$FFFF. A factory ROM test pattern uses the 4K from \$D000 through \$DFFF and the BUFFALO monitor program uses the space from \$E000 through \$FFFF. The on-chip EEPROM occupies the space from \$B600 through \$B7FF. The BUFFALO monitor does not use any of this new RAM so the spaces from \$8000 through \$B5FF and \$B800 through \$CFFF are available to the user.

On the original M68HC11EVBU board a cut-trace short across jumper header J4 holds the MCU's MODA pin low and forces the board to restart in normal single chip mode. This short has been removed from the M68HC11EVBU2 board so the board normally resets into normal expanded mode. While the EVBU2 is in expanded mode, Ports B and C are defined as a multiplexed address/data bus so these port pins are not available as general purpose I/O pins as they were in the original M68HC11EVBU.

In addition to the 32K x 8 RAM (U7 - MCM60L256), the EVBU2 has a 74HC373 latch (U6) and a 74HC00 quad NAND (U8). The latch de-multiplexes the low order addresses from port C of the MCU. The 74HC00 decodes the select signal for the RAM to map it to the \$8000 through \$FFFF area of the memory map. Even though the external 32K RAM is selected when the internal ROM is accessed, there is no conflict because the MC68HC11E9 ignores the external data bus during those cycles.

Do not operate the M68HC11EVBU2 board in special expanded test mode with the IRVNE control bit in the HPRIO register set to 1. This mode is requested when the EVBU2 is reset with a shorting jumper installed on J3 and no jumper installed on J4. This could cause a data bus fight between the external RAM data bus drivers and port C during visible internal access cycles. This conflict could interfere with normal operation.

A new cut-trace jumper header (J16) was also added to the EVBU2. A PC board trace normally shorts pins 1 to 2 of this jumper. In the unlikely event that you want to replace the 32K byte RAM (U7) with an 8K byte device, cut the shorting trace between pins 1 and 2 of J16 and short pin 2 to 3 of J16. Pin 1 of an 8K byte RAM is a no-connect and J16 connects a logic 1 to a high-true enable input of an 8K byte RAM. The resulting address decode for the 8K byte RAM would cause it to be mapped at \$8000-9FFF, \$A000-BFFF, \$C000-DFFF, and \$E000-FFFF. Although this looks like the same mapping as the 32K device, you could not store different values at

\$8000, \$A000, \$C000, and \$E000 because all of these addresses select the same physical byte in the 8K RAM. If you leave the cut-trace short intact on J16 and install an 8K device, it would be mapped at \$A000-BFFF and \$E000-FFFF (only where A13 and A15 equal 1).

## Using Ports B and C as general purpose I/O pins

Remove the RAM (U7) from its socket, and place a jumper across jumper header J4. This makes the EVBU2 look just like an unmodified M68HC11EVBU. The jumper on J4 cause the board to reset into single chip mode so ports B and C are general purpose I/O pins rather than being used as the multiplexed address/data bus.

## Using PCbug11

PCbug11 expects the board to be reset in special bootstrap mode, so place jumpers across J3 and J4. When you reset the board, bootstrap mode is selected as PCbug11 expects.

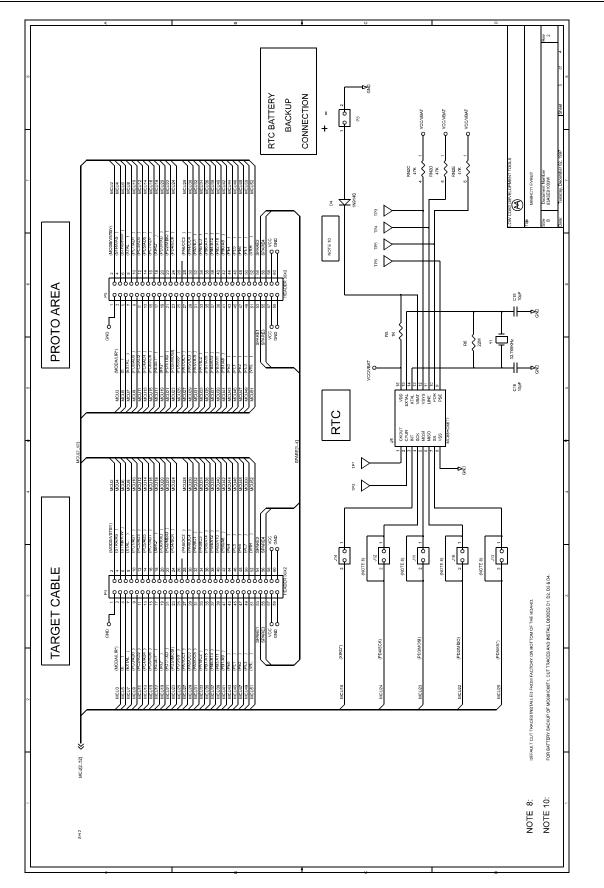

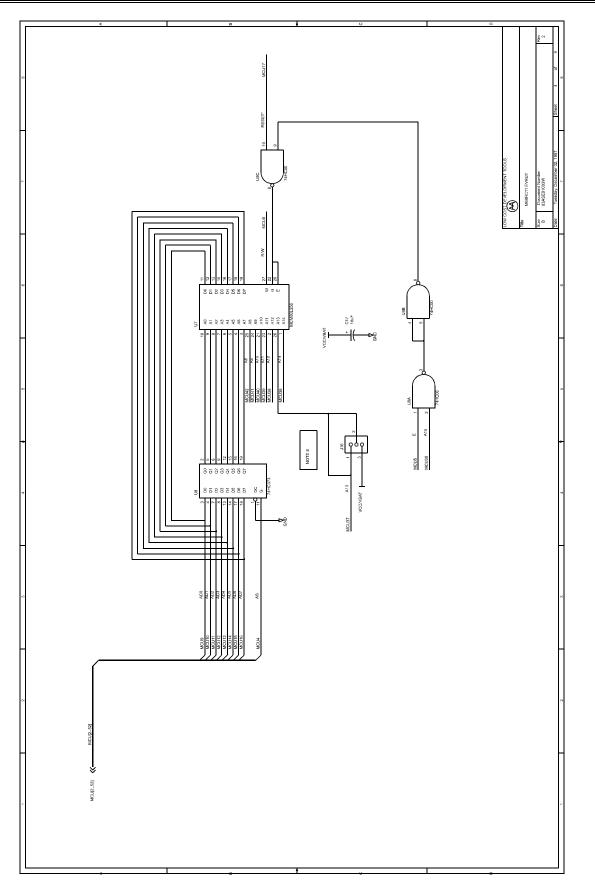

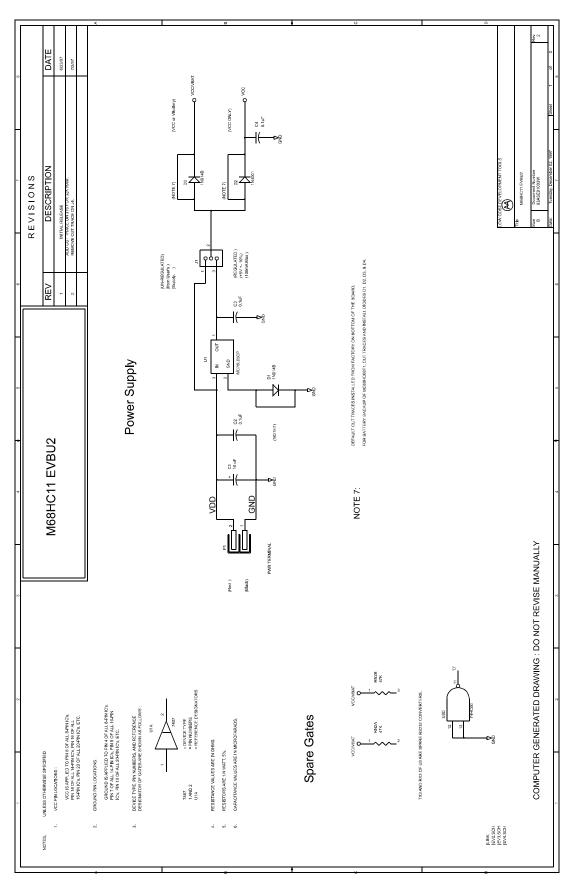

#### Schematic

A new schematic is provided in the next four pages. The first three pages are identical to the original M68HC11EVBU except the default cut-trace shorting J4 has been removed. Sheet 4 shows the new 32K byte RAM and associated circuitry.

M68HC11EVBU2/D

MOTOROLA