## This version was produced for on-line distribution and is not available at the Motorola Literature Distribution Center

## **Technical Supplement**MC68HC912B32 Electrical Characteristics

The MC68HC912B32 microcontroller unit (MCU) is a16-bit device composed of standard on-chip peripherals including a 16-bit central processing unit (CPU12), 32-Kbyte flash EEPROM, 1-Kbyte RAM, 768-byte EEPROM, an asynchronous serial communications interface (SCI), a serial peripheral interface (SPI), an 8-channel timer and 16-bit pulse accumulator, an 8-bit analog-to-digital converter (ADC), a four-channel pulse-width modulator (PWM), and a J1850-compatible byte data link communications module (BDLC). The chip is the first 16-bit microcontroller to include both byte-erasable EEPROM and flash EEPROM on the same device. System resource mapping, clock generation, interrupt control and bus interfacing are managed by the Lite integration module (LIM). The MC68HC912B32 has full 16-bit data paths throughout, however, the multiplexed external bus can operate in an 8-bit narrow mode so single 8-bit wide memory can be interfaced for lower cost systems.

This supplement contains the most accurate electrical information for the MC68HC912B32 microcontroller available at the time of publication. The information should be considered preliminary and is subject to change. The following characteristics are contained in this document:

**Table 1 Maximum Ratings**

**Table 2 Thermal Characteristics**

**Table 3 DC Electrical Characteristics**

**Table 4 Supply Current**

**Table 5 ATD DC Electrical Characteristics**

**Table 6 Analog Converter Characteristics (Operating)**

Table 7 ATD AC Characteristics (Operating)

**Table 8 ATD Maximum Ratings**

**Table 9 EEPROM Characteristics**

**Table 10 Flash EEPROM Characteristics**

**Table 11 Pulse Width Modulator Characteristics**

**Table 12 Control Timing**

**Table 13 Peripheral Port Timing**

**Table 14 Multiplexed Expansion Bus Timing**

**Table 15 SPI Timing**

## **PRELIMINARY**

## Table 1 Maximum Ratings<sup>1</sup>

| Rating                                                                                                  | Symbol                                                  | Value                                                                        | Unit |

|---------------------------------------------------------------------------------------------------------|---------------------------------------------------------|------------------------------------------------------------------------------|------|

| Supply voltage                                                                                          | $V_{\mathrm{DD}}, V_{\mathrm{DDA}}, \ V_{\mathrm{DDX}}$ | -0.3 to +6.5                                                                 | V    |

| Input voltage                                                                                           | V <sub>IN</sub>                                         | -0.3 to +6.5                                                                 | V    |

| Operating temperature range <sup>2</sup> MC68HC912B32FU MC68HC912B32CFU MC68HC912B32VFU MC68HC912B32MFU | T <sub>A</sub>                                          | T <sub>L</sub> to T <sub>H</sub> 0 to +70 -40 to +85 -40 to +105 -40 to +125 | °C   |

| Storage temperature range                                                                               | T <sub>stg</sub>                                        | -55 to +150                                                                  | °C   |

| Current drain per pin <sup>3</sup> Excluding V <sub>DD</sub> and V <sub>SS</sub>                        | I <sub>IN</sub>                                         | ±25                                                                          | mA   |

| V <sub>DD</sub> differential voltage                                                                    | $V_{DD}-V_{DDX}$                                        | 6.5                                                                          | V    |

## NOTES:

- Permanent damage can occur if maximum ratings are exceeded. Exposures to voltages or currents in excess of recommended values affects device reliability. Device modules may not operate normally while being exposed to electrical extremes.

- 2. Refer to MC68HC912B32TS/D Technical Summary for complete part numbers.

- 3. One pin at a time, observing maximum power dissipation limits. Internal circuitry protects the inputs against damage caused by high static voltages or electric fields; however, normal precautions are necessary to avoid application of any voltage higher than maximum-rated voltages to this high-impedance circuit. Extended operation at the maximum ratings can adversely affect device reliability. Tying unused inputs to an appropriate logic voltage level (either GND or V<sub>DD</sub>) enhances reliability of operation.

**Table 2 Thermal Characteristics**

| Characteristic                                                               | Symbol           | Value                                                                           | Unit |

|------------------------------------------------------------------------------|------------------|---------------------------------------------------------------------------------|------|

| Average junction temperature                                                 | TJ               | $T_A + (P_D \times \Theta_{JA})$                                                | °C   |

| Ambient temperature                                                          | T <sub>A</sub>   | User-determined                                                                 | °C   |

| Package thermal resistance (junction-to-ambient) 80-pin quad flat pack (QFP) | $\Theta_{JA}$    | 85                                                                              | °C/W |

| Total power dissipation <sup>1</sup>                                         | P <sub>D</sub>   | P <sub>INT</sub> + P <sub>I/O</sub><br>or<br><u>K</u><br>T <sub>J</sub> + 273°C | W    |

| Device internal power dissipation                                            | P <sub>INT</sub> | $I_{DD} \times V_{DD}$                                                          | W    |

| I/O pin power dissipation <sup>2</sup>                                       | P <sub>I/O</sub> | User-determined                                                                 | W    |

| A constant <sup>3</sup>                                                      | К                | $P_{D} \times (T_{A} + 273^{\circ}C) + \Theta_{JA} \times P_{D}^{2}$            | W·°C |

## NOTES:

- 1. This is an approximate value, neglecting  $P_{I/O}$ .

- 2. For most applications  $P_{I/O}$  «  $P_{INT}$  and can be neglected.

- 3. K is a constant pertaining to the device. Solve for K with a known  $T_A$  and a measured  $P_D$  (at equilibrium). Use this value of K to solve for  $P_D$  and  $T_J$  iteratively for any value of  $T_A$ .

## PRELIMINARY

## **Table 3 DC Electrical Characteristics**

$V_{DD} = 5.0 \ Vdc \ \pm 10\%, \ V_{SS} = 0 \ Vdc, \ T_A = T_L \ to \ T_H, \ unless \ otherwise \ noted$

| Characteristic                                                                                                                                     | Symbol           | Min                                            | Max                                          | Unit           |

|----------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------------------------------------|----------------------------------------------|----------------|

| Input high voltage, all inputs                                                                                                                     | V <sub>IH</sub>  | $0.7 \times V_{DD}$                            | V <sub>DD</sub> + 0.3                        | V              |

| Input low voltage, all inputs                                                                                                                      | V <sub>IL</sub>  | V <sub>SS</sub> -0.3                           | $0.2 \times V_{DD}$                          | V              |

| Output high voltage, all I/O and output pins except XTAL Normal drive strength $I_{OH} = -10.0 \; \mu A$ $I_{OH} = -0.8 \; mA$                     | V <sub>OH</sub>  | V <sub>DD</sub> - 0.2<br>V <sub>DD</sub> - 0.8 | _                                            | V<br>V         |

| Reduced drive strength $I_{OH} = -4.0  \mu A$ $I_{OH} = -0.3  \text{mA}$                                                                           |                  | V <sub>DD</sub> - 0.2<br>V <sub>DD</sub> - 0.8 |                                              | V<br>V         |

| Output low voltage, all I/O and output pins except XTAL Normal drive strength $I_{OL} = 10.0 \ \mu A$ $I_{OL} = 1.6 \ mA$                          | V <sub>OL</sub>  |                                                | V <sub>SS</sub> +0.2<br>V <sub>SS</sub> +0.4 | V<br>V         |

| Reduced drive strength $I_{OL} = 3.6 \ \mu A$ $I_{OL} = 0.6 \ mA$                                                                                  |                  | _                                              | V <sub>SS</sub> +0.2<br>V <sub>SS</sub> +0.4 | V<br>V         |

|                                                                                                                                                    | I <sub>in</sub>  | _<br>_                                         | ±2.5<br>±10                                  | μΑ<br>μΑ       |

| Three-state leakage, I/O ports, BKGD, and RESET                                                                                                    | I <sub>OZ</sub>  | _                                              | ±2.5                                         | μΑ             |

| Input capacitance All input pins and ATD pins (non-sampling) ATD pins (sampling) All I/O pins                                                      | C <sub>in</sub>  | _<br>_<br>_                                    | 10<br>15<br>20                               | pF<br>pF<br>pF |

| Output load capacitance All outputs except PS[7:4] PS[7:4] when configured as SPI                                                                  | CL               |                                                | 90<br>200                                    | pF<br>pF       |

| Programmable active pull-up current  XIRQ, DBE, LSTRB, R/W, ports A, B, DLC, P,S, T  MODA, MODB active pull down during reset BKGD passive pull up | I <sub>APU</sub> | 50<br>50<br>50                                 | 500<br>500<br>500                            | μΑ<br>μΑ<br>μΑ |

| Resistive pull-up current, $\overline{IRQ}/V_{PP}^3$<br>Pin voltage = 0V<br>Pin voltage = 18V                                                      | I <sub>RPU</sub> | 50<br>250                                      | 500<br>1000                                  | μΑ<br>μΑ       |

## NOTES:

- 1. Specification is for parts in the -40 to +85°C range. Higher temperature ranges will result in increased current leakage.

- 2. See Table 5 ATD DC Electrical Characteristics.

- 3.  $\ensuremath{\text{V}_{\text{PP}}}$  function of this pin is used for factory test purposes only.

## **Table 4 Supply Current**

$V_{DD} = 5.0 \ Vdc \pm 10\%, \ V_{SS} = 0 \ Vdc, \ T_A = T_L \ to \ T_H, \ unless \ otherwise \ noted$

| Characteristic                                                            | Symbol           | 2 MHz          | 4 MHz          | 8 MHz          | Unit           |

|---------------------------------------------------------------------------|------------------|----------------|----------------|----------------|----------------|

| Maximum total supply current  RUN:  Single-chip mode  Expanded mode       | I <sub>DD</sub>  | TBD<br>TBD     | TBD<br>TBD     | TBD<br>TBD     | mA<br>mA       |

| WAIT: (All peripheral functions shut down) Single-chip mode Expanded mode | W <sub>IDD</sub> | TBD<br>TBD     | TBD<br>TBD     | TBD<br>TBD     | mA<br>mA       |

| STOP: Single-chip mode, no clocks -40 to +85 +85 to +105 +105 to +125     | S <sub>IDD</sub> | 10<br>25<br>50 | 10<br>25<br>50 | 10<br>25<br>50 | μΑ<br>μΑ<br>μΑ |

| Maximum power dissipation <sup>1</sup> Single-chip mode Expanded mode     | P <sub>D</sub>   | TBD<br>TBD     | TBD<br>TBD     | TBD<br>TBD     | mW<br>mW       |

## NOTES:

1. Includes  $I_{DD}$  and  $I_{DDA}$ .

## **Table 5 ATD DC Electrical Characteristics**

$V_{DD} = 5.0 \text{ Vdc} \pm 10\%$ ,  $V_{SS} = 0 \text{ Vdc}$ ,  $T_A = T_L$  to  $T_H$ , ATD Clock = 2 MHz, unless otherwise noted

| Characteristic                                               | Symbol                               | Min                 | Max                 | Unit     |

|--------------------------------------------------------------|--------------------------------------|---------------------|---------------------|----------|

| Analog supply voltage                                        | $V_{DDA}$                            | 4.5                 | 5.5                 | V        |

| Analog supply currentNormal operation STOP                   | I <sub>DDA</sub>                     |                     | 1.0<br>10           | mA<br>μA |

| Reference voltage, low                                       | V <sub>RL</sub>                      | V <sub>SSA</sub>    | V <sub>DDA</sub> /2 | V        |

| Reference voltage, high                                      | V <sub>RH</sub>                      | V <sub>DDA</sub> /2 | $V_{DDA}$           | V        |

| V <sub>REF</sub> differential reference voltage <sup>1</sup> | V <sub>RH</sub> -V <sub>RL</sub>     | 4.5                 | 5.5                 | V        |

| Input voltage <sup>2</sup>                                   | V <sub>INDC</sub>                    | V <sub>SSA</sub>    | $V_{DDA}$           | V        |

| Input current, off channel <sup>3</sup>                      | l <sub>OFF</sub>                     |                     | 100                 | nA       |

| Reference supply current                                     | I <sub>REF</sub>                     |                     | 250                 | μΑ       |

| Input capacitance Not Sampling Sampling                      | C <sub>INN</sub><br>C <sub>INS</sub> |                     | 10<br>15            | pF<br>pF |

### NOTES:

- 1. Accuracy is guaranteed at  $V_{RH} V_{RL} = 5.0V \pm 10\%$ .

- 2. To obtain full-scale, full-range results,  $V_{SSA} \le V_{RL} \le V_{INDC} \le V_{RH} \le V_{DDA}$ .

- 3. Maximum leakage occurs at maximum operating temperature. Current decreases by approximately one-half for each 10°C decrease from maximum temperature.

## Table 6 Analog Converter Characteristics (Operating)

$V_{DD} = 5.0 \text{ Vdc} \pm 10\%$ ,  $V_{SS} = 0 \text{ Vdc}$ ,  $T_A = T_L$  to  $T_H$ , ATD Clock = 2 MHz, unless otherwise noted

| Characteristic                                                  | Symbol         | Min  | Typical | Max                   | Unit  |

|-----------------------------------------------------------------|----------------|------|---------|-----------------------|-------|

| 8-bit resolution <sup>1</sup>                                   | 1 count        |      | 20      |                       | mV    |

| Differential non-linearity <sup>2</sup>                         | DNL            | -0.5 |         | +0.5                  | count |

| Integral non-linearity <sup>2</sup>                             | INL            | -1   |         | +1                    | count |

| Absolute error <sup>2,3</sup> 2, 4, 8, and 16 ATD sample clocks | AE             | -1   |         | +1                    | count |

| Maximum source impedance                                        | R <sub>S</sub> |      | 20      | See note <sup>4</sup> | ΚΩ    |

### NOTES:

- 1.  $V_{RH} V_{RL} \ge 5.12V$ ;  $V_{DDA} V_{SSA} = 5.12V$

- 2. At  $V_{REF} = 5.12V$ , one 8-bit count = 20 mV.

- 3. Eight-bit absolute error of 1 count (20 mV) includes 1/2 count (10 mV) inherent quantization error and 1/2 count (10 mV) circuit (differential, integral, and offset) error.

- 4. Maximum source impedance is application-dependent. Error resulting from pin leakage depends on junction leakage into the pin and on leakage due to charge-sharing with internal capacitance.

Error from junction leakage is a function of external source impedance and input leakage current. Expected error in result value due to junction leakage is expressed in voltage (V<sub>ERRJ</sub>):

$$V_{ERRJ} = R_S \times I_{OFF}$$

where I<sub>OFF</sub> is a function of operating temperature. Charge-sharing effects with internal capacitors are a function of ATD clock speed, the number of channels being scanned, and source impedance. For 8-bit conversions, charge pump leakage is computed as follows:

$$V_{ERRJ} = .25pF \times V_{DDA} \times R_S \times ATDCLK/(8 \times number of channels)$$

## **Table 7 ATD AC Characteristics (Operating)**

$V_{DD} = 5.0 \text{ Vdc} \pm 10\%$ ,  $V_{SS} = 0 \text{ Vdc}$ ,  $T_A = T_L$  to  $T_H$ , ATD Clock = 2 MHz, unless otherwise noted

| Characteristic                                                                                | Symbol              | Min         | Max          | Unit     |

|-----------------------------------------------------------------------------------------------|---------------------|-------------|--------------|----------|

| ATD operating clock frequency                                                                 | f <sub>ATDCLK</sub> | 0.5         | 2.0          | MHz      |

| Conversion time per channel 0.5 MHz ≤ f <sub>ATDCLK</sub> ≤ 2 MHz 16 ATD clocks 30 ATD clocks | <sup>t</sup> CONV   | 8.0<br>15.0 | 32.0<br>60.0 | μs<br>μs |

| Stop and ATD power up recovery time $^{1}$ $V_{DDA} = 5.0V$                                   | t <sub>SR</sub>     |             | 10           | μs       |

## NOTES:

1. From the time ADPU is asserted until the time an ATD conversion can begin.

# **PRELIMINARY**

## **Table 8 ATD Maximum Ratings**

| Characteristic                                                       | Symbol                                                                 | Value                        | Units  |

|----------------------------------------------------------------------|------------------------------------------------------------------------|------------------------------|--------|

| ATD reference voltage $ V_{RH} \leq V_{DDA} $ $V_{RL} \geq V_{SSA} $ | V <sub>RH</sub><br>V <sub>RL</sub>                                     | -0.3 to +6.5<br>-0.3 to +6.5 | V<br>V |

| V <sub>SS</sub> differential voltage                                 | V <sub>SS</sub> -V <sub>SSA</sub>                                      | 0.1                          | V      |

| V <sub>DD</sub> differential voltage                                 | V <sub>DD</sub> -V <sub>DDA</sub><br>V <sub>DDA</sub> -V <sub>DD</sub> | 6.5<br>0.3                   | V<br>V |

| V <sub>REF</sub> differential voltage                                | V <sub>RH</sub> -V <sub>RL</sub>                                       | 6.5                          | V      |

| Reference to supply differential voltage                             | IV <sub>RH</sub> -V <sub>DDA</sub> I                                   | 6.5                          | V      |

## **Table 9 EEPROM Characteristics**

$V_{DD} = 5.0 \ Vdc \ \pm 10\%, \ V_{SS} = 0 \ Vdc, \ T_A = T_L \ to \ T_H, \ unless \ otherwise \ noted$

| Characteristic                                               | Symbol              | Min    | Typical             | Max                   | Unit   |

|--------------------------------------------------------------|---------------------|--------|---------------------|-----------------------|--------|

| Minimum programming clock frequency <sup>1</sup>             | f <sub>PROG</sub>   | 1.0    |                     |                       | MHz    |

| Programming time                                             | t <sub>PROG</sub>   |        |                     | 10                    | ms     |

| Clock recovery time, following STOP, to continue programming | t <sub>CRSTOP</sub> |        |                     | t <sub>PROG</sub> + 1 | ms     |

| Erase time                                                   | t <sub>ERASE</sub>  |        |                     | 10                    | ms     |

| Write/erase endurance                                        |                     | 10,000 | 30,000 <sup>2</sup> |                       | cycles |

| Data retention                                               |                     | 10     |                     |                       | years  |

## NOTES:

- 1. RC oscillator must be enabled if programming is desired and  $f_{\mbox{\scriptsize SYS}}$  <  $f_{\mbox{\scriptsize PROG}}$ .

- 2. If average  $T_{H}$  is below  $85^{\circ}$  C.

## **Table 10 Flash EEPROM Characteristics**

$V_{DD} = 5.0 \ Vdc \ \pm 10\%, \ V_{SS} = 0 \ Vdc, \ T_A = T_L \ to \ T_H, \ unless \ otherwise \ noted$

| Characteristic                                                                                  | Symbol              | Min                          | Typical               | Max                          | Units    |

|-------------------------------------------------------------------------------------------------|---------------------|------------------------------|-----------------------|------------------------------|----------|

| Program/erase supply voltage:  Read only  Program / erase / verify                              | V <sub>FP</sub>     | V <sub>DD</sub> -0.5<br>11.4 | V <sub>DD</sub><br>12 | V <sub>DD</sub> +0.5<br>12.6 | V<br>V   |

| Program/erase supply current  Word program(V <sub>FP</sub> = 12V)  Erase(V <sub>FP</sub> = 12V) | I <sub>FP</sub>     |                              |                       | 30<br>4                      | mA<br>mA |

| Number of programming pulses                                                                    | n <sub>PP</sub>     |                              |                       | 50                           | pulses   |

| Programming pulse                                                                               | t <sub>PPULSE</sub> | 20                           |                       | 25                           | μs       |

| Program to verify time                                                                          | t <sub>VPROG</sub>  | 10                           |                       |                              | μs       |

| Program margin                                                                                  | p <sub>m</sub>      | 100 <sup>1</sup>             |                       |                              | %        |

| Number of erase pulses                                                                          | n <sub>EP</sub>     |                              |                       | 5                            | pulses   |

| Erase pulse                                                                                     | t <sub>EPULSE</sub> | 90                           | 100                   | 110                          | ms       |

| Erase to verify time                                                                            | t <sub>VERASE</sub> | 1                            |                       |                              | ms       |

| Erase margin                                                                                    | e <sub>m</sub>      | 100 <sup>1</sup>             |                       |                              | %        |

| Program/erase endurance                                                                         |                     | 100                          |                       |                              | cycles   |

| Data retention                                                                                  |                     | 10                           |                       |                              | years    |

## NOTES:

1. The number of margin pulses required is the same as the number of pulses used to program or erase.

## **Table 11 Pulse Width Modulator Characteristics**

$V_{DD} = 5.0 \ Vdc \ \pm 10\%, \ V_{SS} = 0 \ Vdc, \ T_A = T_L \ to \ T_H, \ unless \ otherwise \ noted$

| Characteristic                                  | Symbol            | Min                                              | Max                                          | Unit     |

|-------------------------------------------------|-------------------|--------------------------------------------------|----------------------------------------------|----------|

| E-clock frequency                               | f <sub>eclk</sub> |                                                  | 8.0                                          | MHz      |

| A-clock frequency<br>Selectable                 | f <sub>aclk</sub> | f <sub>eclk</sub> /128                           | f <sub>eclk</sub>                            | Hz       |

| B-clock frequency<br>Selectable                 | f <sub>bclk</sub> | f <sub>eclk</sub> /128                           | f <sub>eclk</sub>                            | Hz       |

| Left-aligned PWM frequency<br>8-bit<br>16-bit   | f <sub>lpwm</sub> | f <sub>eclk</sub> /1M<br>f <sub>eclk</sub> /256M | f <sub>eclk</sub> /2<br>f <sub>eclk</sub> /2 | Hz<br>Hz |

| Left-aligned PWM resolution                     | r <sub>lpwm</sub> | f <sub>eclk</sub> /4K                            | f <sub>eclk</sub>                            | Hz       |

| Center-aligned PWM frequency<br>8-bit<br>16-bit | f <sub>cpwm</sub> | f <sub>eclk</sub> /2M<br>f <sub>eclk</sub> /512M | f <sub>eclk</sub><br>f <sub>eclk</sub>       | Hz<br>Hz |

| Center-aligned PWM resolution                   | r <sub>cpwm</sub> | f <sub>eclk</sub> /4K                            | f <sub>eclk</sub>                            | Hz       |

**Table 12 Control Timing**

| Characteristic                                                                                                     | Symbol             | 8.0     | MHz  | Unit             |

|--------------------------------------------------------------------------------------------------------------------|--------------------|---------|------|------------------|

|                                                                                                                    |                    | Min     | Max  |                  |

| Frequency of operation                                                                                             | f <sub>o</sub>     | dc      | 8.0  | MHz              |

| E-clock period                                                                                                     | t <sub>cyc</sub>   | 125     | _    | ns               |

| Crystal frequency                                                                                                  | f <sub>XTAL</sub>  | _       | 16.0 | MHz              |

| External oscillator frequency                                                                                      | 2f <sub>o</sub>    | dc      | 16.0 | MHz              |

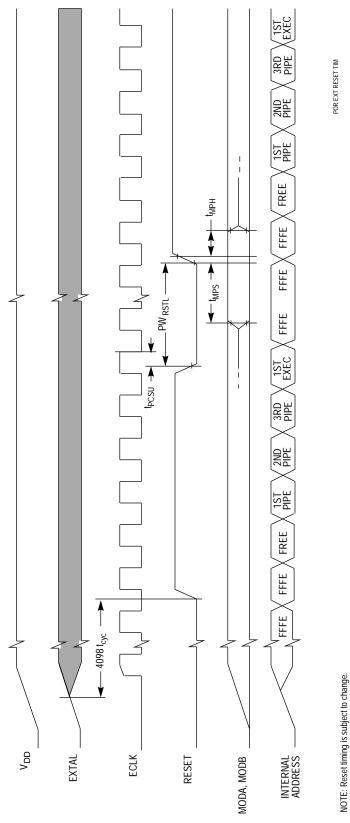

| Processor control setup time<br>t <sub>PCSU</sub> = t <sub>cyc</sub> /4 + 20                                       | t <sub>PCSU</sub>  | 51      | _    | ns               |

| Reset input pulse width To guarantee external reset vector Minimum input time (can be preempted by internal reset) | PW <sub>RSTL</sub> | 32<br>2 | _    | t <sub>cyc</sub> |

| Mode programming setup time                                                                                        | t <sub>MPS</sub>   | 4       | _    | t <sub>cyc</sub> |

| Mode programming hold time                                                                                         | t <sub>MPH</sub>   | 10      | _    | ns               |

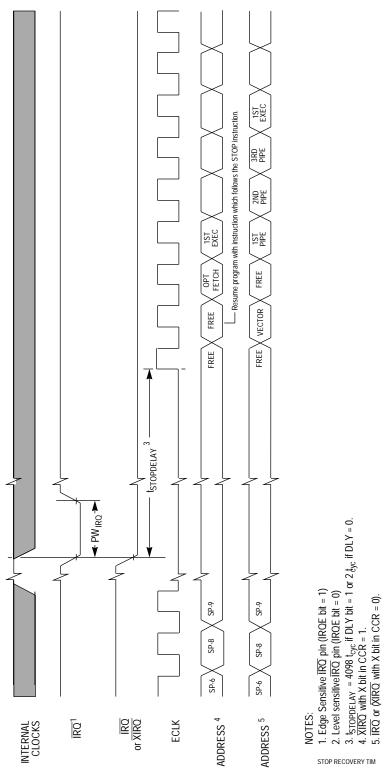

| Interrupt pulse width, $\overline{IRQ}$ edge-sensitive mode $PW_{IRQ} = 2t_{cyc} + 20$                             | PW <sub>IRQ</sub>  | 270     | _    | ns               |

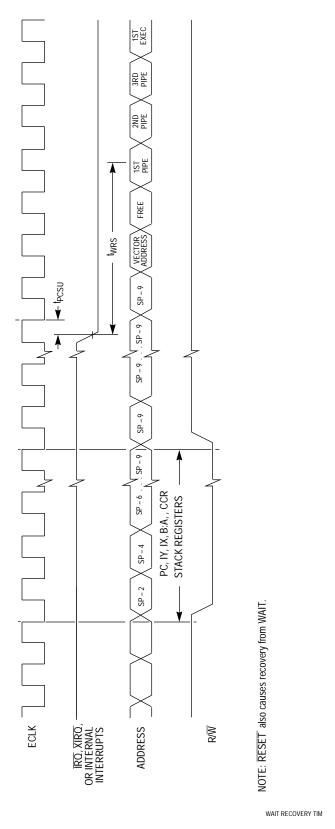

| Wait recovery startup time                                                                                         | t <sub>WRS</sub>   | _       | TBD  | t <sub>cyc</sub> |

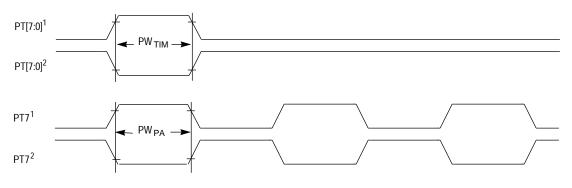

| Timer input capture pulse width PW <sub>TIM</sub> = 2t <sub>cyc</sub> + 20                                         | PW <sub>TIM</sub>  | 270     | _    | ns               |

| Pulse accumulator pulse width                                                                                      | PW <sub>PA</sub>   | TBD     | _    | ns               |

## NOTES:

1. RESET is recognized during the first clock cycle it is held low. Internal circuitry then drives the pin low for 16 clock cycles, releases the pin, and samples the pin level 8 cycles later to determine the source of the interrupt.

## NOTES:

- 1. Rising edge sensitive input

- 2. Falling edge sensitive input

TIMER INPUT TIMING

**Figure 1 Timer Inputs**

Figure 2 POR and External Reset Timing Diagram

**Figure 3 STOP Recovery Timing Diagram**

**Figure 4 WAIT Recovery Timing Diagram**

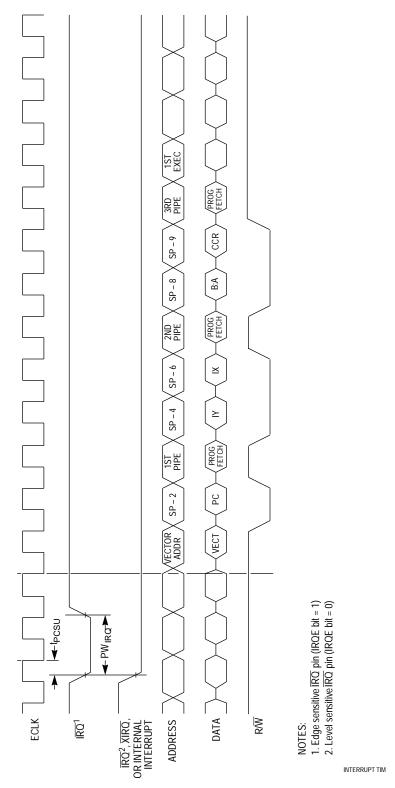

**Figure 5 Interrupt Timing Diagram**

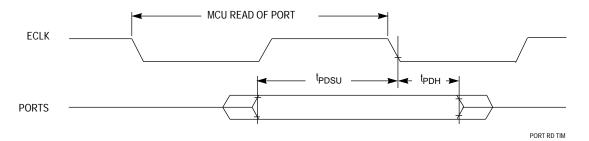

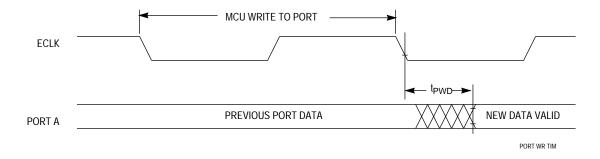

| Table 13 | Peripheral | <b>Port Timing</b> |

|----------|------------|--------------------|

|----------|------------|--------------------|

| Characteristic                                                           | Symbol            | 8.0 | 8.0 MHz Min Max |     |

|--------------------------------------------------------------------------|-------------------|-----|-----------------|-----|

|                                                                          |                   | Min | Max             |     |

| Frequency of operation (E-clock frequency)                               | f <sub>o</sub>    | dc  | 8.0             | MHz |

| E-clock period                                                           | t <sub>cyc</sub>  | 125 | _               | ns  |

| Peripheral data setup time MCU read of ports $t_{PDSU} = t_{cyc}/2 + 40$ | t <sub>PDSU</sub> | 102 | _               | ns  |

| Peripheral data hold time<br>MCU read of ports                           | t <sub>PDH</sub>  | 0   | _               | ns  |

| Delay time, peripheral data write<br>MCU write to ports                  | t <sub>PWD</sub>  | _   | 40              | ns  |

**Figure 6 Port Read Timing Diagram**

**Figure 7 Port Write Timing Diagram**

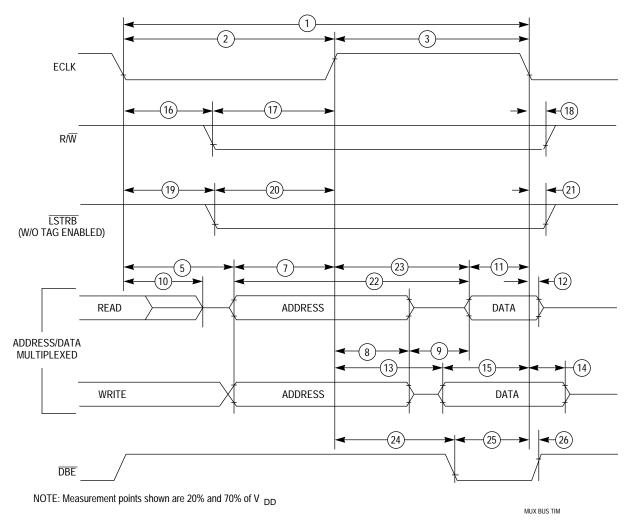

## **Table 14 Multiplexed Expansion Bus Timing**

$V_{DD}$  = 5.0 Vdc  $\pm$  10%,  $V_{SS}$  = 0 Vdc,  $T_{A}$  =  $T_{L}$  to  $T_{H},$  unless otherwise noted

| Num | Characteristic <sup>1, 2, 3, 4</sup>                                                                          |     | Symbol            | 8 MHz |     | Unit |

|-----|---------------------------------------------------------------------------------------------------------------|-----|-------------------|-------|-----|------|

|     |                                                                                                               |     |                   | Min   | Max |      |

|     | Frequency of operation (E-clock frequency)                                                                    |     | f <sub>o</sub>    | dc    | 8.0 | MHz  |

| 1   | Cycle time $t_{cyc} = 1/f_o$                                                                                  | _   | t <sub>cyc</sub>  | 125   | _   | ns   |

| 2   | Pulse width, E low $PW_{EL} = t_{cyc}/2 + delay$                                                              | -2  | PW <sub>EL</sub>  | 60    |     | ns   |

| 3   | Pulse width, E high <sup>5</sup> PW <sub>EH</sub> = t <sub>cyc</sub> /2 + delay                               | -2  | PW <sub>EH</sub>  | 60    |     | ns   |

| 5   | Address delay time $t_{AD} = t_{cyc}/4 + delay$                                                               | 9   | t <sub>AD</sub>   |       | 40  | ns   |

| 7   | Address valid time to ECLK rise $t_{AV} = PW_{EL} - t_{AD}$                                                   | _   | t <sub>AV</sub>   | 20    |     | ns   |

| 8   | Multiplexed address hold time $t_{MAH} = t_{cyc}/4 + delay$                                                   | -10 | t <sub>MAH</sub>  | 21    |     | ns   |

| 9   | Address Hold to Data Valid                                                                                    | _   | t <sub>AHDS</sub> | 5     |     |      |

| 10  | Data Hold to High Z $t_{DHZ} = t_{AD} - 20$                                                                   | _   | t <sub>DHZ</sub>  |       | 20  |      |

| 11  | Read data setup time                                                                                          | _   | t <sub>DSR</sub>  | 18    |     | ns   |

| 12  | Read data hold time                                                                                           | _   | t <sub>DHR</sub>  | 0     |     | ns   |

| 13  | Write data delay time $t_{DDW} = t_{cyc}/4 + delay$                                                           | 14  | t <sub>DDW</sub>  |       | 45  | ns   |

| 14  | Write data hold time $t_{DHW} = t_{cyc}/4 + delay$                                                            | -6  | t <sub>DHW</sub>  | 25    |     | ns   |

| 15  | Write data setup time <sup>5</sup> $t_{DSW} = PW_{EH} - t_{DDW}$                                              | _   | t <sub>DSW</sub>  | 15    |     | ns   |

| 16  | Read/write delay time $t_{RWD} = t_{cyc}/4 + delay$                                                           | 9   | t <sub>RWD</sub>  |       | 40  | ns   |

| 17  | Read/write valid time to E rise $t_{RWV} = PW_{EL} - t_{RWD}$                                                 | _   | t <sub>RWV</sub>  | 20    |     | ns   |

| 18  | Read/write hold time $t_{RWH} = t_{cyc}/4 + delay$                                                            | -6  | t <sub>RWH</sub>  | 25    |     | ns   |

| 19  | Low strobe <sup>6</sup> delay time $t_{LSD} = t_{cyc}/4 + delay$                                              | 9   | t <sub>LSD</sub>  |       | 40  | ns   |

| 20  | Low strobe <sup>6</sup> valid time to E rise $t_{LSV} = PW_{EL} - t_{LSD}$                                    | _   | t <sub>LSV</sub>  | 20    |     | ns   |

| 21  | Low strobe <sup>6</sup> hold time $t_{LSH} = t_{cyc}/4 + delay$                                               | -6  | t <sub>LSH</sub>  | 25    |     | ns   |

| 22  | Address access time <sup>5</sup> $t_{ACCA} = t_{cyc} - t_{AD} - t_{DSR}$                                      | _   | t <sub>ACCA</sub> |       | 67  | ns   |

| 23  | Access time from E rise <sup>5</sup> $t_{ACCE} = PW_{EH} - t_{DSR}$                                           | _   | t <sub>ACCE</sub> |       | 42  | ns   |

| 24  | $\overline{\text{DBE}}$ delay from ECLK rise <sup>5</sup> $t_{\text{DBED}} = t_{\text{cyc}}/4 + \text{delay}$ | 6   | t <sub>DBED</sub> |       | 37  | ns   |

| 25  | $\overline{\text{DBE}}$ valid time $t_{\text{DBE}} = PW_{\text{EH}} - t_{\text{DBED}}$                        | _   | t <sub>DBE</sub>  | 23    |     | ns   |

| 26  | DBE hold time from ECLK fall                                                                                  |     | t <sub>DBEH</sub> | 0     | 10  | ns   |

## NOTES:

- 1. All timings are calculated for normal port drives.

- 2. Crystal input is required to be within 45% to 55% duty.

- 3. Reduced drive must be off to meet these timings.

- 4. Unequalled loading of pins will affect relative timing numbers.

- 5. This characteristic is affected by clock stretch. Add N  $\times$  t<sub>cyc</sub> where N = 0, 1, 2, or 3, depending on the number of clock stretches.

- 6. Without TAG enabled.

Figure 8 Multiplexed Expansion Bus Timing Diagram

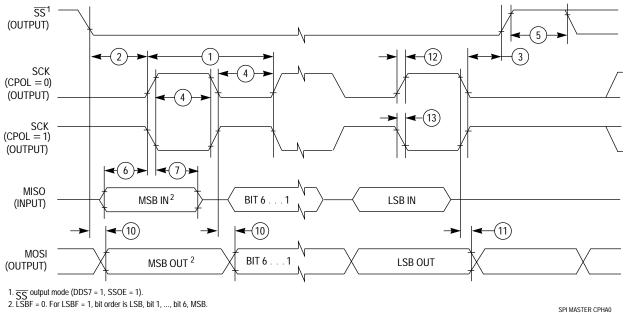

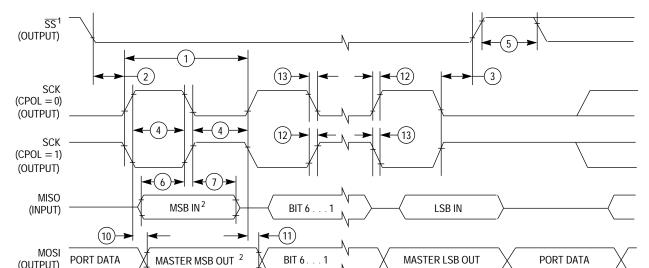

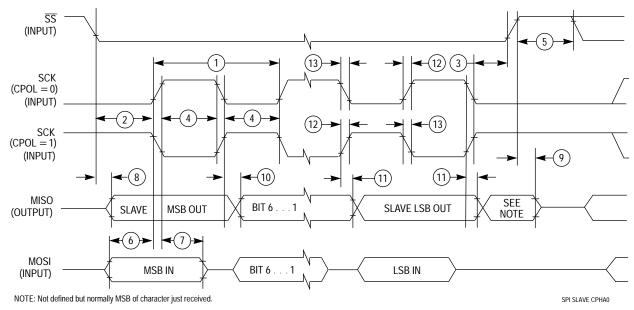

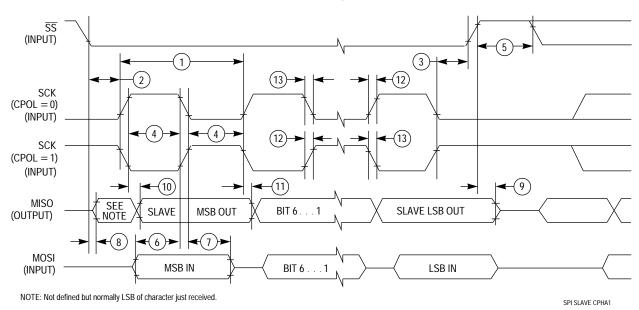

## **Table 15 SPI Timing**

$(V_{DD} = 5.0 \ \text{Vdc} \pm 10\%, \ V_{SS} = 0 \ \text{Vdc}, \ T_A = T_L \ \text{to} \ T_H$  , 200 pF load on all SPI pins)  $^1$

| Num | Function                                        | Symbol                             | Min                                            | Max                   | Unit                                 |

|-----|-------------------------------------------------|------------------------------------|------------------------------------------------|-----------------------|--------------------------------------|

|     | Operating Frequency<br>Master<br>Slave          | f <sub>op</sub>                    | DC<br>DC                                       | 1/2<br>1/2            | E-clock<br>frequency                 |

| 1   | SCK Period<br>Master<br>Slave                   | t <sub>sck</sub>                   | 2<br>2                                         | 256<br>—              | t <sub>cyc</sub>                     |

| 2   | Enable Lead Time<br>Master<br>Slave             | t <sub>lead</sub>                  | 1/2<br>1                                       | _                     | t <sub>sck</sub><br>t <sub>cyc</sub> |

| 3   | Enable Lag Time<br>Master<br>Slave              | t <sub>lag</sub>                   | 1/2<br>1                                       | _                     | t <sub>sck</sub><br>t <sub>cyc</sub> |

| 4   | Clock (SCK) High or Low Time<br>Master<br>Slave | t <sub>wsck</sub>                  | t <sub>cyc</sub> - 60<br>t <sub>cyc</sub> - 30 | 128 t <sub>cyc</sub>  | ns<br>ns                             |

| 5   | Sequential Transfer Delay<br>Master<br>Slave    | t <sub>td</sub>                    | 1/2<br>1                                       | _                     | t <sub>sck</sub><br>t <sub>cyc</sub> |

| 6   | Data Setup Time (Inputs) Master Slave           | t <sub>su</sub>                    | 30<br>30                                       | _                     | ns<br>ns                             |

| 7   | Data Hold Time (Inputs) Master Slave            | t <sub>hi</sub>                    | 0<br>30                                        | _                     | ns<br>ns                             |

| 8   | Slave Access Time                               | t <sub>a</sub>                     | _                                              | 1                     | t <sub>cyc</sub>                     |

| 9   | Slave MISO Disable Time                         | t <sub>dis</sub>                   | _                                              | 1                     | t <sub>cyc</sub>                     |

| 10  | Data Valid (after SCK Edge)<br>Master<br>Slave  | t <sub>v</sub>                     |                                                | 50<br>50              | ns<br>ns                             |

| 11  | Data Hold Time (Outputs) Master Slave           | t <sub>ho</sub>                    | 0<br>0                                         | _                     | ns<br>ns                             |

| 12  | Rise Time<br>Input<br>Output                    | t <sub>ri</sub><br>t <sub>ro</sub> |                                                | t <sub>cyc</sub> – 30 | ns<br>ns                             |

| 13  | Fall Time<br>Input<br>Output                    | t <sub>fi</sub>                    | _                                              | t <sub>cyc</sub> – 30 | ns<br>ns                             |

### NOTES:

1. All AC timing is shown with respect to 20%  $\rm V_{DD}$  and 70%  $\rm V_{DD}$  levels unless otherwise noted.

A) SPI Master Timing (CPHA = 0)

PORT DATA

(OUTPUT)

1.  $\overline{SS}$  output mode (DDS7 = 1, SSOE = 1). 2. LSBF = 0. For LSBF = 1, bit order is LSB, bit 1, ..., bit 6, MSB.

SPI MASTER CPHA1

PORT DATA

B) SPI Master Timing (CPHA = 1)

MASTER LSB OUT

BIT 6 . . . 1

Figure 9 SPI Timing Diagram (1 of 2)

A) SPI Slave Timing (CPHA = 0)

B) SPI Slave Timing (CPHA = 1)

Figure 10 SPI Timing Diagram (2 of 2)

# **PRELIMINARY**

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Motorola data sheets and/or specifications can and do vary in different applications. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part.

MCUinit, MCUasm, MCUdebug, and RTEK are trademarks of Motorola, Inc. The Motorola logos are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

## How to reach us:

USA/EUROPE/Locations Not Listed: Motorola Literature Distribution; P.O. Box 5405, Denver Colorado 80217. 1-800-441-2447, (303) 675-2140 Mfax™: RMFAX0@email.sps.mot.com - TOUCHTONE (602) 244-6609 INTERNET: http://Design-NET.com

JAPAN: Nippon Motorola Ltd.; Tatsumi-SPD-JLDC,

6F Seibu-Butsuryu-Center, 3-14-2 Tatsumi Koto-Ku, Tokyo 135, Japan. 81-3-3521-8315

ASIA PACIFIC: Motorola Semiconductors H.K. Ltd.; 8B Tai Ping Industrial Park,

51 Ting Kok Road, Tai Po, N.T., Hong Kong. 852-26629298

Mfax is a trademark of Motorola, Inc.