# Motorola Semiconductor Application Note

# AN1218

# HC05 to HC08 Optimization

By Mark Glenewinkel CSIC Applications Austin, Texas

## Introduction

Motorola's HC05 Family of microcontrollers contains the world's most popular 8-bit microcontroller units (MCUs). In keeping pace with technology and the changing needs of the customer, Motorola has designed the HC08 Family of MCUs. The HC08 Family CPU is a performance extension to the HC05 Family of low cost MCUs. This application note will describe the differences and advantages of the HC08 Family CPU: the CPU08.

CPU08 is fully opcode and object code compatible with the HC05 CPU. Any HC05 code will execute directly on the HC08 without instruction set differences. As this application note will show, there are many improvements to the speed and capability in the CPU08.

CPU08 is a faster processor. The basic execution speed of the CPU08 has been increased with advanced high performance CMOS technology. Execution cycles of most instructions have been improved with an advanced computer architecture.

CPU08 has more programming capability. It has more addressing modes, better math support, and much improved data manipulation, accessing, and moving capabilities. Looping and branching instructions have also been optimized. This application note will help inform and educate the reader concerning the differences between the HC05 and HC08 CPUs. Detailed examples illustrating the added features found with the CPU08 are given to help optimize software design with the CPU08.

## Scope of this Application Note

This note assumes the reader has a background in MCU software and hardware design and is also familiar with the HC05. It was written for the engineering manager and the design engineer. As a reference, the application note overviews the basic differences between the two CPUs so that one can fit the right CPU for a specific application. As a tutorial, the application note gives the designer the means to understand and utilize the HC08 enhancements. Software is given to illustrate and compare the performance of the CPUs.

## **HC08** Features

The following is a list of major features of the HC08 CPU (CPU08) that differentiate it from the HC05 CPU (CPU05).

- Fully upward object code compatible with the MC6805, MC146805, and the MC68HC05 Family

- 64 KByte program/data memory space

- Enhanced HC05 programming model

- 8 MHz CPU bus frequency

- 16 addressing modes, 5 more than the HC05

- Expandable internal bus definition for addressing range extension beyond 64 KBytes

- 16-bit index register with manipulation instructions

- 16-bit stack pointer with manipulation instructions

- Memory to memory data moves without using the accumulator

- Fast 8-bit multiply and integer/fractional divide instructions

- Binary coded decimal (BCD) instruction enhancements

- Internal bus flexibility to accommodate CPU enhancing peripherals such as a DMA controller

- Fully static low voltage/low power design

## CPU05/CPU08 Programmer's Model Comparison

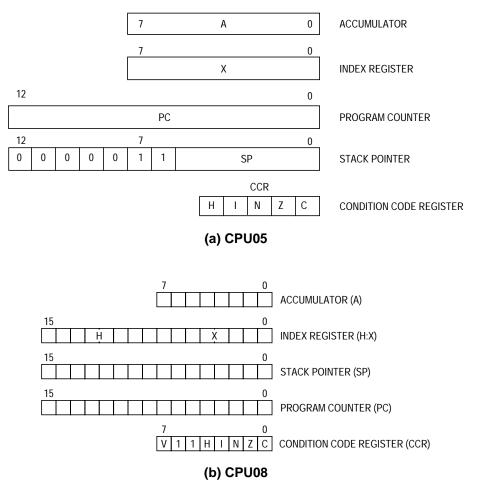

The CPU05 and the CPU08 programmer's model differences are illustrated in **Figure 1**.

- H Index Register The index register of the CPU08 has been extended to 16 bits, allowing the user to index or address a 64 KByte memory space without any offset. The upper byte of the index register is called the H index register. The concatenated 16-bit register is called the H:X register. Source code written for CPU05 will not affect the H register and it will remain in its reset state of \$00. There are seven new instructions that allow the user to manipulate the H:X index register. These instructions are covered in detail later.

- Stack PointerThe stack pointer (SP) has been extended from its 6-bit CPU05 version<br/>to a full 16-bit SP on the CPU08. SPH:SPL refers to the 16-bit stack<br/>pointer by naming the high byte, SPH, and the low byte, SPL. To<br/>maintain HC05 compatibility, the reset state is \$00FF.

New instructions and new addressing modes greatly increase the utility of the CPU08 stack pointer over the CPU05 stack pointer. Nine new CPU08 instructions allow the user to easily manipulate the SP and the stack.

CPU08 also has relative addressing modes that allow the SP to be used as an index register to access temporary variables on the stack. These addressing modes and new instructions are discussed later in this application note.

Figure 1. CPU05 and CPU08 Comparison

Program CounterThe CPU08 program counter (PC) has been expanded to 16 bits which<br/>allows the CPU08 to address 64 KBytes of memory. Not all HC05<br/>devices have a 16-bit program counter.

New AddressingCPU08 has 16 addressing modes, 8 more than the HC05. Table 1 listsModes,these addressing modes and the CPUs that use them. A briefComparisondiscussion of these modes is given below.

| Addressing Mode                         | HC05 | HC08 |

|-----------------------------------------|------|------|

| Inherent                                | X    | X    |

| Immediate                               | X    | Х    |

| Direct                                  | X    | Х    |

| Extended                                | X    | X    |

| Indexed, no offset                      | X    | Х    |

| Indexed, 8-bit offset                   | X    | Х    |

| Indexed, 16-bit offset                  | X    | Х    |

| Relative                                | X    | Х    |

| Stack Pointer, 8-bit offset             |      | Х    |

| Stack Pointer, 16-bit offset            |      | Х    |

| Memory to memory (4 modes)              |      | Х    |

| Indexed w/post increment                |      | X    |

| Indexed, 8-bit offset, w/post increment |      | X    |

Table 1. Addressing Mode Comparison Table

## HC05 and HC08 Addressing Modes

Inherent instructions such as reset stack pointer (RSP) and multiply (MUL) have no operand. Inherent instructions require no memory address and are one byte long.

Immediate instructions contain a value that is used in an operation with the index register or accumulator. Immediate instructions require no memory address and are two bytes long. The operand is found in the byte immediately following the opcode.

Direct instructions can access any of the first 256 memory addresses with only two bytes. The first byte contains the opcode followed by the low byte of the operand address. The CPU automatically uses \$00 for the high byte of the operand address. Most direct instructions are two bytes long.

## **Application Note**

Extended instructions can access any address in the memory map. Extended instructions are three bytes long and contain the opcode and the two-byte operand address.

Indexed instructions with no offset are one-byte instructions that utilize the index register of the CPU. CPU08 also uses the H:X register containing the high byte of the address operand.

Indexed, 8-bit offset instructions are two-byte instructions that utilize the index register of the CPU to access data at any location in memory. The 8-bit unsigned offset following the opcode is added to the 16-bit unsigned index register (H:X). The sum is the address used to access data.

Indexed, 16-bit offset instructions are like the 8-bit offset instructions except that they are three bytes long and add a 16-bit unsigned number to the 16-bit index register (H:X).

Relative addressing is only used for branch instructions. If the branching condition is true, the CPU finds the branch destination by adding the offset operand to the PC counter. The offset is a two's complement byte that gives a branching range of -128 to +127 bytes. This instruction is two bytes long.

# New HC08Stack pointer, 8-bit offset instructions operate like indexed, 8-bit offsetAddressing Modesinstructions except that they add the offset to the 16-bit SP. This modeis available only on the CPU08. If interrupts are disabled, thisaddressing mode allows the SP to be used as a second index register.This instruction is three bytes long.

Stack pointer, 16-bit offset instructions are only available on the CPU08. They are like the stack pointer, 8-bit offset instructions except that they add a 16-bit value to the SP. This instruction is four bytes long. Memory to memory instructions utilize four different modes available only to the CPU08.

- 1. The move, immediate to direct, is a three-byte mode generally used to initialize RAM and register values in page 0 of the memory map. The operand in the second byte is immediately stored to the direct page location found in the third byte.

- 2. The move, direct to direct, is a three-byte instruction. The operand following the opcode is the direct page location that is stored to the second operand direct page location.

- The move, indexed to direct, post increment, is a two-byte instruction. The operand addressed by the 16-bit index register (H:X) is stored to direct page location address by the byte following the opcode. The index register is then incremented.

- 4. The move, direct to indexed, post increment, is a two-byte instruction. The operand in the direct page location addressed by the byte following the opcode is stored in the location addressed by the 16-bit index register (H:X). The index register is then incremented.

In the CPU08, four instructions address operands with the index register and then increment the index register afterwards. This is called indexed with post increment mode. These instructions include CBEQ indexed, CBEQ indexed with offset, MOV IX+Dir, and MOV Dirlx+.

Table 2 gives examples to illustrate these different addressing modes.

| Addressing Mode                                              | Example                  |                                               |  |

|--------------------------------------------------------------|--------------------------|-----------------------------------------------|--|

| Inherent                                                     | RSP                      |                                               |  |

| Immediate                                                    | LDA                      | #\$FF                                         |  |

| Direct                                                       | LDA                      | \$50                                          |  |

| Extended                                                     | LDA                      | \$1000                                        |  |

| Indexed, no offset                                           | LDA                      | ,Х                                            |  |

| Indexed, 8-bit offset                                        | LDA                      | \$50,X                                        |  |

| Indexed, 16-bit offset                                       | LDA                      | \$0150,X                                      |  |

| Relative                                                     | BRA                      | \$20                                          |  |

| Stack Pointer, 8-bit offset*                                 | LDA                      | \$50,SP                                       |  |

| Stack Pointer, 16-bit offset*                                | LDA                      | \$0150,SP                                     |  |

| Memory to memory<br>ImmDir*<br>DirDir*<br>Ix+Dir*<br>Dirlx+* | MOV<br>MOV<br>MOV<br>MOV | #\$30,\$80<br>\$80,\$90<br>X+,\$90<br>\$80,X+ |  |

| Indexed w/post increment*                                    | CBEQ                     | X+,LOOP                                       |  |

| Indexed, 8-bit offset, w/post increment*                     | CBEQ                     | \$20,X+,LOOP                                  |  |

\* New CPU08 addressing modes

## Condition Code Register with Overflow Bit V

A summary of the condition code register (CCR) is given below. Unless otherwise stated, all bits correspond to both CPUs.

Overflow Bit V

This bit is set when a two's-complement overflow has occurred as the result of an operation. The V bit has been added to the CPU08 condition code register to support two's-complement arithmetic.

#### Half-Carry Bit H

The half-carry bit is set when a carry has occurred between bits 3 and 4 of the accumulator because of the last ADD or ADC operation. This bit is required for BCD operations.

Interrupt Mask Bit I

All timer and external interrupts are disabled when this bit is set. Interrupts are enabled when the bit is cleared. This bit is automatically set after any CPU reset.

## Negative Bit N

This bit is set after any arithmetic, logical, or data manipulation operation was negative. In other words, bit 7 of the result of the operation was a logical one.

## Zero Bit Z

The zero bit is set after any arithmetic, logical, or data manipulation operation was zero.

## Carry/Borrow Bit C

The carry/borrow bit is set when a carry out of bit 7 of the accumulator occurred during the last arithmetic, logical, or data manipulation operation. The bit is also set or cleared during bit test and branch instructions and shifts and rotates.

## **Description of the Clock**

In the CPU08, the CPU clock rate is twice that of the address/data bus rates. The internal CPU08 clock rate is 16 MHz for an 8 MHz HC08. To maintain a 50% duty cycle CPU clock, the oscillator clock, OSC CLK, must run twice the rate of the CPU clock. Therefore a 32 MHz OSC clock is needed to drive an 8 MHz HC08.

The flagship member of the CPU08 family has a phase locked loop (PLL) synthesizer to generate the 32 MHz signal. It is derived from a suggested crystal frequency of 4.9152 MHz.

| Address/Data Rate | = | Ζ  | = | 8 MHz  |

|-------------------|---|----|---|--------|

| CPU Clock Rate    | = | 2Z | = | 16 MHz |

| OSC Clock Rate    | = | 4Z | = | 32 MHz |

# Index Registers

|                                           | CPU08 has the additional H index register which is the high byte<br>extension to the X index register. Together, the two index registers<br>formulate the concatenated 16-bit H:X index register. Five new<br>instructions are introduced on the CPU08 to allow manipulation of the<br>H:X index register. Source code written for the HC05 will not effect the<br>H register and it will remain in its reset state of \$00.<br>The TSX and the TXS instructions also utilize the H:X index register.<br>These instructions are covered in more detail in the stack pointer<br>section. |                                                                                       |                                                                                                                                                                                                                                                                   |

|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Five New Indexing<br>Instructions, Detail | The new CPU08 instructions that affect the index registers are listed below. Examples for these instructions are given in Appendix A — New CPU08 Indexing Instruction Examples.                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                       |                                                                                                                                                                                                                                                                   |

|                                           | AIX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Add Immedia                                                                           | ate to Index Register                                                                                                                                                                                                                                             |

|                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Operation:                                                                            | $X \gets (H{:}X) + (M)$                                                                                                                                                                                                                                           |

|                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Description:                                                                          | AIX adds an immediate value to the 16-bit<br>index register formed by the concatenation<br>of the H and X registers. The immediate<br>operand is an 8-bit two's complement<br>signed offset. Prior to addition to H:X, the<br>offset is sign extended to 16 bits. |

|                                           | CLRH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Clear Index                                                                           | High                                                                                                                                                                                                                                                              |

|                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Operation:                                                                            | H ← \$00                                                                                                                                                                                                                                                          |

|                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Description:                                                                          | The contents of H are replaced with zeros.                                                                                                                                                                                                                        |

|                                           | СРНХ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <ul> <li>Compare 16-bit Index Register</li> <li>Operation: (H:X) – (M:M+1)</li> </ul> |                                                                                                                                                                                                                                                                   |

|                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                       |                                                                                                                                                                                                                                                                   |

|                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Description:                                                                          | CPHX compares the 16-bit index register<br>H:X with the 16-bit value in memory and<br>sets the condition code register accordingly.                                                                                                                               |

| LDHX | Load 16-bit I | ndex Register                                                                                                                              |

|------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------|

|      | Operation:    | H:X ← (M:M+1)                                                                                                                              |

|      | Description:  | Loads the contents of the specified memory location into the 16-bit index register H:X. The condition codes are set according to the data. |

| STHX | Store 16-bit  | Index Register                                                                                                                             |

|      | Operation:    | $(M:M+1) \leftarrow (H:X)$                                                                                                                 |

Description: Stores the 16-bit index register H:X to the specified memory location. The condition codes are set according to the data.

Software<br/>Techniques Using<br/>IndexedThe CPU08 index register has some distinct advantages over the<br/>CPU05 index register. Even though the CPU05 has 16-bit index offset,<br/>the 8-bit index register restricts indexing to a maximum of 256 bytes.Addressing, TablesCPU08 with its H register extension allows full 16-bit index addressing<br/>equaling 65,536 bytes of memory access. Proper 16-bit pointers allow<br/>efficient compiling of C code and other higher level languages.<br/>Maximum table lengths in the CPU08 which can be accessed in a single<br/>instruction are therefore 64 KByte. An optional address extension<br/>module can extend the data space beyond 64 KBytes, but the maximum<br/>offset remains 64 KBytes. Index addressing modes include 8- and 16-<br/>bit offsets.

Many programmers like to use calculated addressing. CPU08 has a new instruction, AIX, that allows the addition of a two's complement number. Table access is easier and more flexible.

The H:X index register can also be used as an auxiliary 16-bit accumulator. Sixteen-bit data comparisons are easier with the CPHX instruction.

The following section illustrates the advantage of using a 16-bit index register.

Code Example We will now illustrate the added benefit of the CPU08 16-bit index register. The index will be used to address a 512 byte table. In the CPU05, the table must be broken up into sections of memory consisting of 256 bytes per section. Our table has 512 bytes, so we will be using two sections, section 0 and section 1, for the CPU05. The address to look up on the table will be found in RAM. Notice that the CPU05 code is longer. If your table was larger, you would require more sections of memory to handle your table. A subroutine might be written to make the job more modular. In the HC08 example, the 512 byte table can be handled directly. A comparison between CPU05 and CPU08 code is shown in Appendix B — CPU05 and CPU08 512-Byte Table Indexing Code.

## **Stack Pointer**

CPU08 has a full 16-bit stack pointer. To maintain compatibility with the CPU05, it is initialized to \$00FF out of reset.

Stack manipulation is from high to low memory. The SP is decremented each time data is pushed on the stack and incremented each time data is pulled from the stack. The SP points to the next available stack address rather than the latest stack entry address.

Nine new instructions have been added for the user to manipulate the stack. These instructions allow the direct push and pull of any register to the stack. The SP can be changed with a transfer of the H:X register to the SP or the SP can be augmented by the add immediate instruction.

Stack manipulation can be a very powerful programming technique. With the CPU08, the assembly programmer can pass parameters and store local or temporary variables when using subroutines and/or interrupts.

New addressing modes were added to address these variables on the stack. Using the stack pointer as an index register with 8- or 16-bit offsets, the user may access variables on the stack. These instructions greatly cut cycle count by not having to load/store the variable. RAM

requirements are also reduced. Significant C code efficiency can be gained when utilizing these new stack pointer addressing modes.

If interrupts are disabled, the stack pointer can be used as a second 16-bit index register with 8- or 16-bit offsets.

Nine New Stack Manipulation Instructions, Detail All the new CPU08 instructions that affect the stack pointer are listed below. Examples for these instructions are given in **Appendix C** — New CPU08 Stack Pointer Instructions.

| AIS  | Add Immedia  | ate to Stack Pointer                                                                                                                                                                                                                                                                                                               |

|------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | Operation:   | $SP \gets (SP) + (M)$                                                                                                                                                                                                                                                                                                              |

|      | Description: | Adds the immediate operand to the stack<br>pointer SP. The immediate value is an 8-bit<br>two's complement signed operand. Prior to<br>addition to the SP, the operand is sign<br>extended to 16 bits. This instruction can be<br>used to create and remove a stack frame<br>buffer which is used to store temporary<br>variables. |

| PSHA | Push Accum   | ulator onto Stack                                                                                                                                                                                                                                                                                                                  |

|      | Operation:   | $\Downarrow$ (A); SP $\leftarrow$ (SP-\$01)                                                                                                                                                                                                                                                                                        |

|      | Description: | The contents of the accumulator are pushed<br>onto the stack at the address contained in<br>the stack pointer. The stack pointer is then<br>decremented to point at the next available<br>location in the stack. The contents of the<br>accumulator remain unchanged.                                                              |

| PSHH | Push Index F | Register H onto Stack                                                                                                                                                                                                                                                                                                              |

|      | Operation:   | $\Downarrow$ (H); SP $\leftarrow$ (SP-\$01)                                                                                                                                                                                                                                                                                        |

|      | Description: | The contents of the 8-bit high order index<br>register H are pushed onto the stack at the<br>address contained in the stack pointer. The<br>stack pointer is then decremented to point at<br>the next available location in the stack. The<br>contents of the H register remain<br>unchanged.                                      |

|      |              |                                                                                                                                                                                                                                                                                                                                    |

| PSHX | Operation:    | Register X onto Stack<br>$\downarrow$ (X); SP $\leftarrow$ (SP-\$01)<br>The contents of the 8-bit low order index<br>register X are pushed onto the stack at the<br>address contained in the stack pointer. The<br>stack pointer is then decremented to point at<br>the next available location in the stack. The<br>contents of the X register remain<br>unchanged. |

|------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PULA |               | lator from Stack                                                                                                                                                                                                                                                                                                                                                     |

|      | Operation:    | $SP \leftarrow (SP+\$01); \ \Uparrow (A)$                                                                                                                                                                                                                                                                                                                            |

|      | Description:  | The stack pointer is incremented to address<br>the last operand on the stack. The<br>accumulator is then loaded with the<br>contents of the address pointed to by SP.                                                                                                                                                                                                |

| PULH | Pull Index Re | egister H from Stack                                                                                                                                                                                                                                                                                                                                                 |

|      | Operation:    | $SP \leftarrow (SP+\$01); \uparrow (H)$                                                                                                                                                                                                                                                                                                                              |

|      | Description:  | The stack pointer is incremented to address<br>the last operand on the stack. The 8-bit<br>index register H is then loaded with the<br>contents of the address pointed to by SP.                                                                                                                                                                                     |

| PULX | Pull Index Re | egister X from Stack                                                                                                                                                                                                                                                                                                                                                 |

|      | Operation:    | $SP \leftarrow (SP+\$01); \ \widehat{1} (X)$                                                                                                                                                                                                                                                                                                                         |

|      | Description:  | The stack pointer is incremented to address<br>the last operand on the stack. The 8-bit<br>index register X is then loaded with the<br>contents of the address pointed to by SP.                                                                                                                                                                                     |

| тѕх  | Transfer Stac | ck Pointer to Index Register                                                                                                                                                                                                                                                                                                                                         |

|      | Operation:    | H:X ← (SP) + \$0001                                                                                                                                                                                                                                                                                                                                                  |

|      | Description:  | Loads the index register H:X with one plus<br>the contents of the 16-bit stack pointer SP.<br>The contents of the stack pointer remain<br>unchanged. After a TSX instruction, the                                                                                                                                                                                    |

index register H:X points to the last value that was stored on the stack.

**TXS**Transfer Index Register to Stack PointerOperation: $SP \leftarrow (H:X) - \$0001$ Description:Loads the stack pointer SP with the<br/>contents of the index register H:X minus<br/>one.The contents of the index register H:X<br/>remain unchanged.

Software<br/>Techniques Using<br/>the SPThe CPU05 and the CPU08 use the stack for two primary purposes.<br/>First, every time the CPU executes an interrupt service routine, the<br/>register contents are saved on the stack. After the execution of a return<br/>from interrupt (RTI) instruction, the register contents on the stack are<br/>restored to the CPU. Second, every time a jump to subroutine (JSR) or<br/>a branch to subroutine (BSR) occurs, the return address is saved on the<br/>stack. The address is restored to the program counter after a return from<br/>subroutine (RTS) instruction is executed.

The CPU08 with its new stack manipulation instructions allows the user to pass parameters to the subroutine and store local or temporary values within the subroutine. Two major benefits are derived from using the stack for parameters and temporary values:

- A subroutine will allocate RAM storage for its variables and release this memory when the subroutine is finished. Therefore, global variables are not needed for these routines. This saves RAM memory space.

- 2. The allocation of new local variables for each subroutine makes the subroutine recursive and reentrant. This allows the programmer to easily modularize his code.

Let's look at the stacking operation of the CPU05 and the CPU08. The stack is located in RAM. Since stacking occurs from high memory to low memory, the SP usually points to the highest RAM memory address. Both the CPU05 and the CPU08 reset the SP at \$00FF. The CPU08 instruction set allows the programmer to move the stack out of Page 0 memory if needed.

## **Application Note**

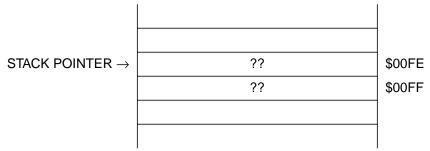

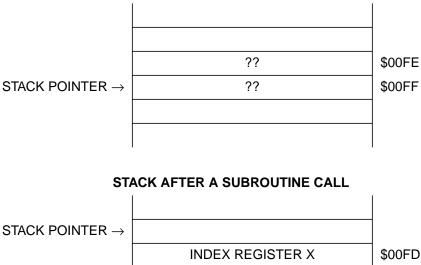

When an interrupt occurs, the contents of all the CPU registers are pushed onto the stack, the interrupt vector is fetched, and the program begins execution at the start of the interrupt routine. The stack contents before and after an interrupt are shown in **Figure 2**. For the CPU08 to remain upward compatible with the CPU05, the H index register is not pushed onto the stack.

**NOTE:** If the H register is used in the interrupt service routine or if indexed addressing modes are used, the H register must be pushed onto the stack.

This is accomplished by using the PSHH instruction. Before returning from the interrupt, the PULH instruction must be used to extract the H index register off the stack.

#### STACK BEFORE AN INTERRUPT CALL

Figure 2. Stack Before and After an Interrupt Call

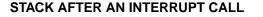

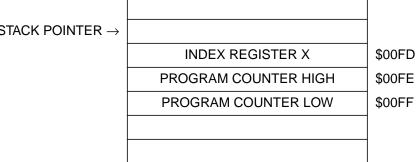

**Figure 3** illustrates the stack before and after a subroutine is called when the stack pointer is at \$00FF. When a subroutine is called, the 16bit program counter is pushed onto the stack and the execution of code begins at the start of the subroutine. The program counter is split into its 8-bit high and low bytes.

#### STACK BEFORE A SUBROUTINE CALL

Figure 3. Stack Before and After a Subroutine Call

If the values in the X register and the accumulator are needed within a subroutine, they will need to be saved somehow before the subroutine uses them. If using the CPU05, you would have to allocate global RAM space for saving these CPU registers. Your code would look something like that in Figure 4.

| *     | Subrou   | utine XX for | CPU05 *                 |

|-------|----------|--------------|-------------------------|

| START | STX      | \$50         | ;4 store X away to RAM  |

|       | STA      | \$51         | ;4 store A away to RAM  |

|       | XX<br>XX | XX<br>XX     | ;actual subroutine code |

|       | LDX      | \$50         | ;3 load X from RAM      |

|       | LDA      | \$51         | ;3 load A from RAM      |

#### Figure 4. CPU05 Subroutine Code

The CPU05 code will use 14 cycles to store and load registers. Also, two bytes of global RAM space are allocated for this subroutine. If we were to use the CPU08, the code could utilize the stack. Global RAM space and six cycles would be saved. Refer to **Figure 5**.

| *     | Subroutine X         | XX for CPU08 | *                                                              |

|-------|----------------------|--------------|----------------------------------------------------------------|

| START | PSHX<br>PSHH<br>PSHA | ;2 pu        | ash X onto stack<br>ash H onto stack<br>ash A onto stack       |

|       | XX XX<br>XX XX       | ;actu        | al subroutine code                                             |

|       | PULA<br>PULH<br>PULX | ;2 pu        | all A off of stack<br>all H off of stack<br>all X off of stack |

#### Figure 5. CPU08 Subroutine Code

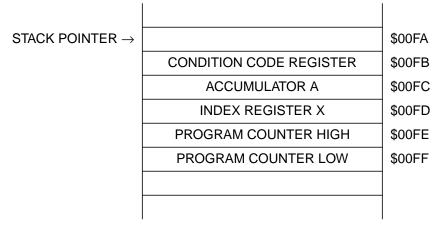

The stack helps in efficiently utilizing parameters, local variables, and subroutine return values. Parameters are variables that are passed to the subroutine. Local variables are variables that are only used within the scope of the subroutine. A subroutine return value is the output of the subroutine. An example of a subroutine and its variables are given below in equation form:

$$Y = (X)3$$

If we were to write a subroutine that calculates the cube of the value X, X would be the parameter passed to the subroutine. Y would be the subroutine return value, and any variable used to calculate Y would be

a local variable. The stack of these complex subroutines follow the generalized structure shown in **Figure 6**. **Figure 6** shows the stack before the subroutine initialization, before entering the subroutine, and during the subroutine. The actual cube subroutine is written in the following section of code. A diagram of the stack during its execution is given within the code listing.

|                                        |               | STACK                |        |

|----------------------------------------|---------------|----------------------|--------|

|                                        |               |                      |        |

| SP DURING SUBROUTINE                   | $\rightarrow$ |                      | \$00f7 |

|                                        |               | LOCAL VARIABLE 1     | \$00F8 |

|                                        |               | LOCAL VARIABLE 2     | \$00F9 |

|                                        |               | ACCUMULATOR A        | \$00FA |

|                                        |               | INDEX REGISTER X     | \$00FB |

|                                        |               | PROGRAM COUNTER HIGH | \$00FC |

| SP DURING SUBROUTINE                   | $\rightarrow$ | PROGRAM COUNTER LOW  | \$00FD |

|                                        |               | RETURN VALUE         | \$00FE |

| SP BEFORE<br>SUBROUTINE INITIALIZATION | $\rightarrow$ | PASSED PARAMETER     | \$00FF |

|                                        |               |                      |        |

|                                        |               |                      |        |

#### Figure 6. Stack Structure of a Complex Subroutine

Code ExampleRefer to Appendix D — Using the Stack in a Subroutine to Compute<br/>a Cube for an example of modular subroutine code that efficiently<br/>computes the cube of an 8-bit positive number.

## **Data Movement**

## Why Improve the Movement of Data in the CPU05?

The most common CPU function is the transfer of data. Most microcontroller-based systems spend the majority of their time moving data from one location to the other. Many different addressing modes are used to access and transfer bytes of data. If there was a way to decrease the time it takes to transfer data, then the overall performance of the system would be improved.

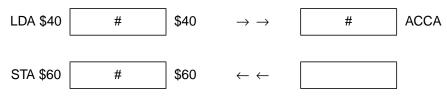

CPU05 moves data from one location to the next by first loading the accumulator with the byte from the transfer source. Next, CPU05 stores the byte from the accumulator to the transfer's destination. In this manner all data must pass through the accumulator, thus making the accumulator a bottleneck in data movement. The movement of the contents of location \$40 to location \$60 with the CPU05 is illustrated in **Figure 7**.

Figure 7. Accumulator as a Bottleneck

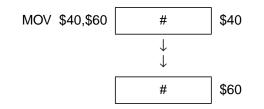

CPU08 provides the new MOV instruction which bypasses the accumulator. Using the MOV instruction, the CPU is instructed to take the contents of the source location and directly place the data in the destination. This is illustrated in **Figure 8**. There are four different addressing modes special to the MOV instruction. Details of this instruction are given below.

Figure 8. No Accumulator Bottleneck

| New MOVE<br>Instruction, Detail | The new CPU08 Move instruction is detailed below. Examples for this instruction and all four of its addressing modes are given in <b>Appendix E</b> — <b>New CPU08 MOV Instruction Examples</b> . The examples in <b>Appendix E</b> — <b>New CPU08 MOV Instruction Examples</b> also compare the CPU05 and the CPU08 bus cycles and memory requirements for the algorithm to execute the movement of data.         |                |                                                                                                                                                                                                                                                                                                                                                                 |  |

|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                 | MOV                                                                                                                                                                                                                                                                                                                                                                                                                | Move           |                                                                                                                                                                                                                                                                                                                                                                 |  |

|                                 |                                                                                                                                                                                                                                                                                                                                                                                                                    | Operation:     | (M)destination $\leftarrow$ (M)source                                                                                                                                                                                                                                                                                                                           |  |

|                                 |                                                                                                                                                                                                                                                                                                                                                                                                                    | Description:   | Moves a byte of data from a source address<br>to a destination address. Data is examined<br>as it is moved, and condition codes are set.<br>Source data is not changed. Internal<br>registers (other than CCR) are not affected.<br>There are four addressing modes for the<br>MOV instruction. A discussion of these<br>modes was given in an earlier section. |  |

| Software<br>Techniques          | data. The mo                                                                                                                                                                                                                                                                                                                                                                                                       | ost obvious ad | It cycle time and code space when moving<br>dvantage of the MOV instruction is when the<br>being initialized along with other RAM<br>program.                                                                                                                                                                                                                   |  |

| Code Example                    | A user wants to start his application one of two different ways. The user initializes the application on the MCU based on the logic level of port D bit 4. Once the part is out of reset, it reads port D and moves data from ROM into the RAM configuration registers according to the logic level of bit 4. Refer to Appendix F — CPU05 and CPU08 Data Movement Code for code comparing the CPU05 and the CPU08. |                |                                                                                                                                                                                                                                                                                                                                                                 |  |

# **New Branch Instructions**

| Description                            | of the CPUC<br>These instru<br>DBNZX. The<br>instructions<br>instructions<br>instructions<br>instructions | 08 to improve I<br>uctions are CB<br>le CBEQ instru<br>and the branc<br>combine the c<br>and the branc | instructions were added to the instruction set<br>ooping and table searching capabilities.<br>EQ, CBEQA, CBEQX, DBNZ, DBNZA, and<br>actions combine the compare (CMP and CPX)<br>h if equal (BEQ) instruction . The DBNZ<br>lecrement (DEC, DECA, and DECX)<br>h if not equal (BNE) instruction. These new<br>time and decrease code space. More detail<br>struction. |

|----------------------------------------|-----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Six New Branch<br>Instructions, Detail | Examples for<br>Branch Ins<br>Branch Ins                                                                  | or these instruction Exan<br>truction Exan<br>truction Exan<br>cycles and me                           | ctions that affect branching are listed below.<br>ctions are given in <b>Appendix G</b> — <b>New</b><br><b>pples</b> . The examples in <b>Appendix G</b> — <b>New</b><br><b>pples</b> also compare the CPU05 and the<br>emory requirements for the algorithm to                                                                                                       |

|                                        | CBEQ                                                                                                      | Compare an                                                                                             | d Branch if Equal                                                                                                                                                                                                                                                                                                                                                     |

|                                        |                                                                                                           | Operation:                                                                                             | A) - (M); PC $\leftarrow$ (PC) + \$0003 + Rel if result is \$00                                                                                                                                                                                                                                                                                                       |

|                                        |                                                                                                           | For IX+ mod                                                                                            | e: (A) - (M);                                                                                                                                                                                                                                                                                                                                                         |

|                                        |                                                                                                           | $PC \gets (PC) \cdot$                                                                                  | + \$0002 + Rel, if result is \$00                                                                                                                                                                                                                                                                                                                                     |

|                                        |                                                                                                           | Description:                                                                                           | CBEQ compares the operand from memory<br>with the accumulator and causes a branch if<br>the result is zero. This function combines<br>CMP and BEQ for faster table look-up<br>routines.                                                                                                                                                                               |

|                                        |                                                                                                           |                                                                                                        | The addressing mode CBEQ_IX+ compares<br>the operand addressed by the 16-bit index<br>register H:X to the accumulator and causes<br>a branch if the result is zero. The 16-bit<br>index register is then incremented<br>regardless of whether a branch is taken.<br>CBEQ_IX1+ operates the same way except                                                            |

an 8-bit offset is added to the effective address of the operand.

## **CBEQA** Compare and Branch if Equal

Operation: (A) - (M); PC  $\leftarrow$  (PC) + \$0003 + Rel if result is \$00

- Description: CBEQA compares an immediate operand in memory with the accumulator and causes a branch if the result is zero. This instruction combines CMP and BEQ for faster table look-up routines.

- **CBEQX** Compare and Branch if Equal

- Operation: (IX) (M); PC  $\leftarrow$  (PC) + \$0003 + Rel if result is \$00

- Description: CBEQX compares an immediate operand in memory with the lower order index register X and causes a branch if the result is zero. This instruction combines CPX and BEQ for faster loop counter control.

## DBNZ Decrement and Branch if Not Zero

- Operation:  $M \leftarrow (M) \$01;$

- $$\label{eq:PC} \begin{split} \text{PC} \leftarrow (\text{PC}) + \$0003 + \text{Rel, if result} \_\$00 \text{ for Direct, IX1,} \\ & \text{and SP1} \end{split}$$

- $PC \leftarrow (PC) + \$0002 + Rel$ , if result \_ \$00 for IX

- Description: DBNZ subtracts one from the operand M in memory and causes a branch if the result is not zero. This instruction combines DEC and BNE for faster loop counter control.

## **DBNZA** Decrement and Branch if Not Zero

- Operation:  $A \leftarrow (A) \$01$ ;  $PC \leftarrow (PC) + \$0002 + Rel$ , if result \_ \$00

- Description: DBNZA subtracts one from the accumulator and causes a branch if the result is not zero. This instruction combines DECA and BNE for faster loop counter control.

Code Example

| DBNZX        | Decrement a  | nd Branch if Not Zero                                                                                                                                                             |

|--------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              | Operation:   | $X \leftarrow (X)$ - \$01; PC $\leftarrow$ (PC) + \$0002 + Rel, if result _ \$00                                                                                                  |

|              | Description: | DBNZX subtracts one from the lower index<br>register and causes a branch if the result is<br>not zero. This instruction combines DECX<br>and BNE for faster loop counter control. |

| counting rou | tines. Compa | ructions can cut cycle time in looping or<br>re and branch routines can be used to search<br>or variable locations. Decrement and branch                                          |

The following piece of code shows how the compare and branch instruction searches a table for a match. As an example, let's say that you recently read in a table of 80 A/D data bytes. You would like to know if the signal was saturated above the rails of the A/D converter. You would then search the table for the value \$FF. If found, your code would branch out and execute some control algorithm to attenuate the analog signal. Refer to **Appendix H — CPU05 and CPU08 Search Code** for a comparison of CPU05 and CPU08 code.

## **Mathematical Operations**

| V Bit, DIV, DAA,<br>and the NSA<br>Instruction | New features and instructions added to the CPU08 have made some<br>mathematical computations easier. The V bit is added to the CCR to<br>support signed arithmetic. CPU08 has the capability of 16-bit division.<br>The DIV instruction will divide a 16-bit dividend by an 8-bit divisor. For<br>binary coded decimal operations, the CPU08 has a decimal adjust<br>accumulator, DAA, instruction and a nibble swap accumulator, NSA,<br>instruction. |

|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signed Math and                                | The V bit in the CCR adds greater programming flexibility to the user.                                                                                                                                                                                                                                                                                                                                                                                 |

| Signed Branches                                | The addition of two's complement comparisons can aid in the branching                                                                                                                                                                                                                                                                                                                                                                                  |

routines can be used for keeping count in loops.

operations of high level languages such as C. Also, the representation of signed numbers and their operations can easily be computed. This can be especially helpful with digital signal processing algorithms and the proper storage of signed analog to digital readings.

## Four New Signed Branch Instructions, Detail

All the new CPU08 instructions that affect signed branching are listed below. Examples for these instructions are given in Appendix I — New CPU08 Signed Branch Instruction Examples.

| BGE | Branch if Gre | eater Than or Equal (signed operands)                                                                                                                                                                                                                                                                                                           |

|-----|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | Operation:    | $PC \leftarrow (PC) + $0002 + Rel, if (N \oplus V)=0,$<br>i.e., if (A) _ (M), ("signed" numbers)                                                                                                                                                                                                                                                |

|     | Description:  | If the BGE instruction is executed<br>immediately after execution of any of the<br>compare or subtract instructions, the branch<br>will occur if and only if the two's complement<br>number represented by the appropriate<br>internal register (A, X, or H:X) was greater<br>than or equal to the two's complement<br>number represented by M. |

| BGT | Branch if Gre | eater Than (signed operands)                                                                                                                                                                                                                                                                                                                    |

|     | Operation:    | $\label{eq:PC} \begin{array}{l} \leftarrow (PC) + \$0002 + Rel, \mbox{ if } Z+(N \oplus V)=0, \\ \mbox{i.e., if (A) > (M), ("signed" numbers)} \end{array}$                                                                                                                                                                                     |

|     | Description:  | If the BGT instruction is executed<br>immediately after execution of any of the<br>compare or subtract instructions, the branch<br>will occur if and only if the two's complement<br>number represented by the appropriate<br>internal register (A, X, or H:X) was greater<br>than the two's complement number<br>represented by M.             |

| BLE | Branch if Les | s Than or Equal (signed operands)                                                                                                                                                                                                                                                                                                            |

|-----|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | Operation:    | $PC \leftarrow (PC) + 0002 + Rel, \text{ if } Z+(N \oplus V)=1$<br>i.e., if (A) _ (M), ("signed" numbers)                                                                                                                                                                                                                                    |

|     | Description:  | If the BLE instruction is executed<br>immediately after execution of any of the<br>compare or subtract instructions, the branch<br>will occur if and only if the two's complement<br>number represented by the appropriate<br>internal register (A, X, or H:X) was less than<br>or equal to the two's complement number<br>represented by M. |

| BLT | Branch if Les | s Than (signed operands)                                                                                                                                                                                                                                                                                                                     |

|     | Operation:    | $PC \leftarrow (PC) + $0002 + Rel, if (N \oplus V)=1$<br>i.e., if (A) < (M), ("signed" numbers)                                                                                                                                                                                                                                              |

|     | Description:  | If the BLT instruction is executed<br>immediately after execution of any of the<br>compare or subtract instructions, the branch<br>will occur if and only if the two's complement<br>number represented by the appropriate<br>internal register (A, X, or H:X) was less than<br>the two's complement number represented<br>by M.             |

## New DIV Instruction

The Divide instruction on the CPU08 does not require the lengthy code needed to divide numbers on the CPU05. A description of the Divide instruction is given below. Appendix J — Five Miscellaneous CPU08 Instructions Including BCD, Divide, and CCR Operations shows a short example of using the new Divide instruction. Appendix K — CPU08 Averaging Code illustrates an averaging routine implementing the Divide instruction.

| DIV | Divide       |                                                      |

|-----|--------------|------------------------------------------------------|

|     | Operation:   | (H:A) / X $\rightarrow$ A; Remainder $\rightarrow$ H |

|     | Description: | Divides a 16-bit unsigned dividend                   |

|     |              | contained in the concatenated registers H            |

|     |              | and A by an 8-bit divisor contained in index         |

register X. The quotient is placed in the accumulator A, and the remainder is placed in the high order index register H. The divisor is left unchanged.

New DAA and the NSA instruction

The decimal adjust accumulator, DAA, and the nibble swap accumulator, NSA, are new instructions to help with binary coded decimal (BCD) operations. The DAA instruction allows the user to adjust the accumulator so that the number represents a BCD number. Swapping nibbles is needed for packing BCD numbers into memory. One use of BCD is data instrumentation. It is easier to store and manipulate these numbers in BCD rather than convert or decode numbers from hexadecimal. Packing is used to store decimal numbers into memory. Instead of one byte storing one decimal, the NSA instruction easily swaps nibbles in the accumulator so that two decimal numbers can be stored in one byte. Appendix J — Five Miscellaneous CPU08 Instructions Including BCD, Divide, and CCR Operations gives examples using the DAA instruction and the NSA instruction. Refer to Appendix L — CPU08 BCD Example Code for an example of BCD code.

DAA Decimal Adjust Accumulator

Operation: (A)10

Description: Adjusts the contents of the accumulator and the state of the CCR carry bit after binary coded decimal operations so that there is a correct BCD sum and an accurate carry indication. The state of the CCR half carry bit affects operation.

NSA Nibble Swap Accumulator

Operation: A ← (A[3:0]:A[7:4])

Description: Swaps upper and lower nibbles (4 bits) of the accumulator. This is used for more efficient storage and use of binary coded

operands.

New TAP and TPAThe transfer accumulator to the condition code register, TAP, and the<br/>transfer condition code register to accumulator, TPA, are new<br/>instructions to modify or manipulate the condition code register, CCR.<br/>These instructions are detailed below. Code examples can be found in<br/>Appendix J — Five Miscellaneous CPU08 Instructions Including<br/>BCD, Divide, and CCR Operations.

| TAP | Transfer Acc               | umulator to Condition Code Register                                       |

|-----|----------------------------|---------------------------------------------------------------------------|

|     | Operation:                 | $CCR \leftarrow (A)$                                                      |

|     | Description:               | Transfers the contents of the Accumulator to the Condition Code Register. |

|     |                            |                                                                           |

| TPA | Transfer Con               | dition Code Register to Accumulator                                       |

| TPA | Transfer Con<br>Operation: | 0                                                                         |

## Instruction Cycle Improvements

The CPU08 instruction set not only has new instructions but many of the old instructions are faster. The CPU08 gathers data in a pipeline fashion. Instead of waiting for the instruction to be finished to gather the next opcode or operand, the CPU will fetch the next address byte during the execution of the current instruction. This pipelining overlaps execution of most instructions and thus increases the performance of the CPU08. A list of instructions that were improved is given in Table 3. Please refer to the CPU08 opcode map for further details.

| Opcode Mnemonic | Address Mode | HC05 Cycles | HC08 Cycles |

|-----------------|--------------|-------------|-------------|

| ADC             | IX           | 3           | 2           |

| ADC             | IX1          | 4           | 3           |

| ADC             | IX2          | 5           | 4           |

| ADD             | IX           | 3           | 2           |

| ADD             | IX1          | 4           | 3           |

| ADD             | IX2          | 5           | 4           |

| AND             | IX           | 3           | 2           |

| AND             | IX1          | 4           | 3           |

| AND             | IX2          | 5           | 4           |

| ASR             | DIR          | 5           | 4           |

| ASR             | IX           | 5           | 3           |

| ASR             | IX1          | 6           | 4           |

| ASRA            | INH          | 3           | 1           |

| ASRX            | INH          | 3           | 1           |

| BCLR0           | DIR          | 5           | 4           |

| BCLR1           | DIR          | 5           | 4           |

| BCLR2           | DIR          | 5           | 4           |

| BCLR3           | DIR          | 5           | 4           |

| BCLR4           | DIR          | 5           | 4           |

| BCLR5           | DIR          | 5           | 4           |

| BCLR6           | DIR          | 5           | 4           |

| BCLR7           | DIR          | 5           | 4           |

| BIT             | IX           | 3           | 2           |

| BIT             | IX1          | 4           | 3           |

| BIT             | IX2          | 5           | 4           |

| BSET0           | DIR          | 5           | 4           |

| BSET1           | DIR          | 5           | 4           |

| BSET2           | DIR          | 5           | 4           |

| BSET3           | DIR          | 5           | 4           |

| BSET4           | DIR          | 5           | 4           |

| BSET5           | DIR          | 5           | 4           |

| BSET6           | DIR          | 5           | 4           |

| BSET7           | DIR          | 5           | 4           |

| BSR             | REL          | 6           | 4           |

| CLC             | INH          | 2           | 1           |

Table 3. Instruction List (Sheet 1 of 4)

| Opcode Mnemonic | Address Mode | HC05 Cycles | HC08 Cycles |

|-----------------|--------------|-------------|-------------|

| CLR             | DIR          | 5           | 3           |

| CLR             | IX           | 5           | 2           |

| CLR             | IX1          | 6           | 3           |

| CLRA            | INH          | 3           | 1           |

| CLRX            | INH          | 3           | 1           |

| CMP             | IX           | 3           | 2           |

| CMP             | IX1          | 4           | 3           |

| CMP             | IX2          | 5           | 4           |

| СОМ             | DIR          | 5           | 4           |

| СОМ             | IX           | 5           | 3           |

| СОМ             | IX1          | 6           | 4           |

| COMA            | INH          | 3           | 1           |

| COMX            | INH          | 3           | 1           |

| CPX             | IX           | 3           | 2           |

| СРХ             | IX1          | 4           | 3           |

| СРХ             | IX2          | 5           | 4           |

| DEC             | DIR          | 5           | 4           |

| DEC             | IX           | 5           | 3           |

| DEC             | IX1          | 6           | 4           |