**AN1222**

# **Arithmetic Waveform Synthesis** with the HC05/08 MCUs

by Mark McQuilken & Mark Glenewinkel CSIC Applications

#### INTRODUCTION

IThis application note is intended to demonstrate the use of Arithmetic Synthesis to create sinusoidal waveforms from a microcontroller unit (MCU). Given an accumulation constant predefined in memory, a very precise sinusoidal waveform can be produced from a table of sinusoidal values in memory. The values selected from the table are then sent out an MCU port to a digital-to-analog converter (DAC). This application note has been written for the HC08 MCU. Although cycle execution time will be different, the program listing for the HC08 is also applicable to the HC05.

# **BACKGROUND**

The process of producing tones using an accumulated value that is used to point to the next output time (magnitude) sample is called "Arithmetic Synthesis". This is contrasted to Direct Digital Synthesis where the "distance" between each sample taken from sinewave table is constant.

Arithmetic Synthesis utilizes a standard DAC look-up, phase value table consisting of (in this case) 256 phase values for a single cycle of a sine wave. The position in this table is determined by two bytes of data: the MSB which is the integer index into the DAC look-up table, and the LSB which is the fractional depth into the table. Since this fractional portion is not used to directly address a sine sample directly, the effect is evident only when the continual accumulation of this fraction causes an overflow into the integer portion. This effect may be seen in a simple example of repeatedly adding (accumulating) a fixed value while only attributing significance to the integer portion:

| Αc                  | cumulation | Addend             | Result             |

|---------------------|------------|--------------------|--------------------|

| (Truncated Integer) |            | (Integer Fraction) | (Integer Fraction) |

| 0                   | +          | 1.25               | 1.25               |

| 1                   | +          | 1.25               | 2.50               |

| 2                   | +          | 1.25               | 3.75               |

| 3                   | +          | 1.25               | 5.00               |

| 5                   | +          | 1.25               | 6.25               |

| 6                   | etc        |                    |                    |

The effect of the fractional accumulation on the integer portion is an occasionally "skipped" value (like the value of 4 that was skipped above). The integer part of the accumulator is then used to point into the sine table to obtain a magnitude for that time sample. The frequency of occurance of this skipping is a function of the fractional value. Hence, we can determine, with the appropriate choice of fraction and integer, the output

frequency of the digitized sinewave to a high degree of accuracy. The exact mathematical relationship, for a 256 phase value table, is:

Accumulation Constant = 256 x Desired Frequency x Sampling Period

The sampling period would be:

Sampling Period = E clock period \* # of cycles in loop

Once the accumulation constant, D, is determined, it must be put into the memory locations Int\_K and Frac\_K. This calculation is shown below:

Once the accumulation constant is defined, the synthesizer is ready to be used. This application note uses the HC08 MCU but the algorithm can be used with any MCU so long as the algorithm is followed and the accumulation constant is defined for the appropriate sampling period.

Arithmetic synthesis produces some artifacts that are not desirable in some applications. One of those artifacts is called "phase noise" (or phase jitter). With an ideal sinewave, the period is fixed and unvarying for every cycle. This means that the instantaneous frequency and the average frequency are the same. What occurs with an arithmetically synthesized waveform, however, is that the instantaneous frequency changes from cycle-to-cycle due to the "sample skipping" performed in the AS algorithm while the average frequency remains quite stable and precise. This cycle-to-cycle variation in instantaneous frequency is called phase noise. Applications which are sensitive to changing instantaneous frequency and/or to the additional spectral components produced by the jitter (these components would be categorized anywhere from distortion to just plain noise, depending on the system) may not want to use AS as the primary method of signal synthesis.

### TESTING OF THE ARITHMETIC SYNTHESIZER

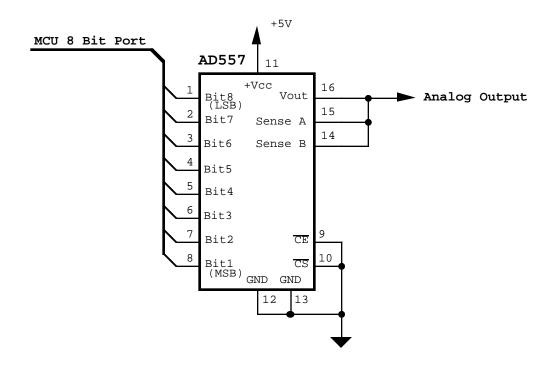

In order to test the arithmetic synthesizer, any 8 bit parallel DAC can be used. An Analog Devices AD557JN was used to test our code. The 557 is an easy to use DAC. A basic schematic for the 557 is listed below in Figure #1. The 8 bit digital waveform data is sent to the DAC and the conversion occurs immediately after receiving the information. The sampling period of the waveform is determined by the speed at which data is written to the DAC port. If other MCUs are to be used with this basic circuit, make sure the sampling frequency does exceed the specifed output settling time. Please refer to the AD557 data sheet if more information is needed.

Figure #1 - Basic schematic for the AD557 Digital-to-Analog Converter

# **DESCRIPTION OF THE ARITHMETIC SYNTHESIS SOFTWARE**

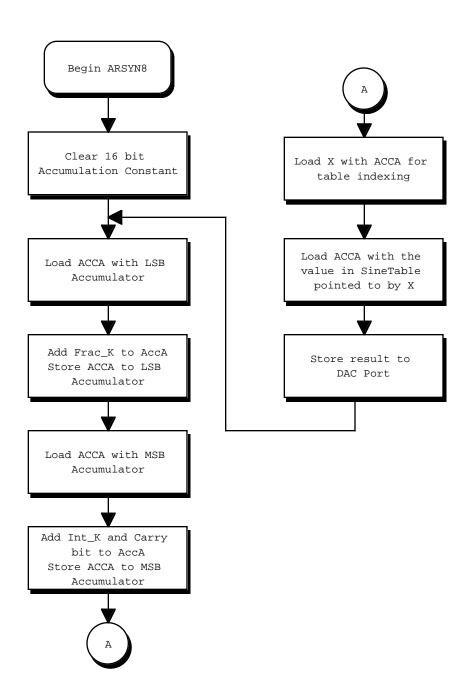

The flowchart and code listing written to illustrate arithmetic synthesis is given at the end of this application note. The file name is called ARSYN8.ASM. The code written to execute the loop routine takes 29 cycles. Assuming the HC08 is running at a speed of 8 MHz, the sampling period would be:

Let's say that you want to produce a sinewave with a frequency of 8 kHz. The accumulation constant will be:

The accumulation constant must now be put into the memory locations Int\_K and Frac\_K. These numbers are shown below:

The routine is written using an infinite loop. This is not the most practical application of the algorithm but it allows experimentation and measurement of the waveform. Some applications may need a waveform to last for a specified length of time. This can be done by adding a counter into the loop. The sampling period will be affected so the accumulation constant must be changed to reflect the new sampling period.

The sampling period will change when you use an HC05 MCU. Be sure to recalculate the sampling period with the HC05's bus frequency and cycle counts. The code listed will assemble with an HC05 assembler.

ARSYN8.ASM and can be downloaded from the Motorola MCU Bulletin Board Service. The BBS number is (512) 891-3733. The serial protocol is 1200 or 2400, 8 bits, 1 stop bit, and no parity. The file is located on the CSIC bulletin board in the APPNOTES directory.

# **ARSYN8 - ARITHMETIC SYNTHESIS FLOWCHART**

# **ARSYN8.ASM - ARITHMETIC SYNTHESIS CODE LISTING**

\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\* \* Program Name: ARSYN8.ASM ( Arithmetic Synthesizer ) \* Revision: 1.00 \* Date: February 3,1993 \* Written By: Mark Glenewinkel Motorola CSIC Applications Assembled Under: P&E Microcomputer Systems IASM08 \*\*\*\*\*\*\* Revision History \*\*\*\*\*\*\*\*\*\* 0.50 12/15/93 M.A. McQuilken Rev HC05 version to be translated to HC08 code Rev 0.60 01/21/93 M.R. Glenewinkel Added more comments M.R. Glenewinkel 02/18/93 1.00 Rev HC08 version \*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*

# \* Program Description:

This routine produces a sinusoid of a specified frequency at the output of a Digital-to-Analog Converter (DAC) attached to Port X (set by the user) of an HCO8.

Basically, this method utilizes a standard DAC look-up table consisting of (in this case) 256 phase values for a single cycle of a sinewave. The position in this table is determined by two bytes of data: the MSB which is the integer index into the DAC look-up table, and the LSB which is the fractional depth into the table. Since this fractional portion is not used to directly address a sine sample directly, its effect is made only when the continual accumulation of this fraction causes an overflow into the integer portion.

We can determine, with the appropriate choice of fraction and integer, the output frequency of the digitized sinewave to a high degree of accuracy. The exact mathematical relationship, for 256 phase values, is:

Accumulation Constant = 256 x Desired Frequency x Sample Time

The sample time, in this case, is 3.625 usec using an HC08 running with an 8MHz E clock. The sample period is calculated by determining the number of instructions within the generating loop (29 cyc) and multiplying the number by the bus clock period. In this example an 8kHz sinewave is to be sythesized. The accumulation constant will be:

D = 7.424Thus, in the source code, the memory locations Int\_K and Frac\_K should contain \$07 and \$6C, respectively, upon entering the ArithSyn routine. \* Please understand the impact that code and/or hardware changes may \* have on the desired, synthesized output frequency. Before making \* changes be certain that you understand the ramifications. \*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\* \* This code assumes that you've got an appropriate DAC on PortB (in \* this case, the testbed consisted of an AD557JN on PortB) and that \* you've made PortB an output port in your initialization code. \*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\* \* TASK DATA: Input Variables Output Variables Description Enter with the Frac\_K appropriate fractional accumulate value. Enter with appropriate Int\_K integer accumulation value. \* LOCAL DATA: Output Variables Description Input Variables ----------\_\_\_\_\_ Determines length of Cntr Cntr time the sinewave is generated with a maximum value of approx. 4.5 msec. AccumLSB AccumLSB Least significant byte of 16-bit phase accumulator. Most significant AccumMSB AccumMSB byte of 16-bit phase accumulator. This is the value that is used to point into the sine table. ACCA ACCA Misc. computational Misc. computational Χ

\* Register and Variable Equates

\*

\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*

```

equ

DAC

equ

PortB

******************

* Memory

$50

ORG

AccumLSB

RMB

AccumMSB

RMB

Frac_K

RMB

1

1

Int_K

RMB

ORG

$6E00

; beginning of program area

START

EQU

* Main Routine

* We must prepare the workspace, any nonzero variables could

* alter our process.

ArithSyn

clr

AccumLSB

clr

AccumMSB

* At this point we're ready to actually begin the process of

* generating the sinewave. The accumulation is done with an 8-bit

* fraction and an 8-bit integer.

* So, basically, we're going to have the HC08 do a 16-bit addition:

SignalGen

;3 - Get current LSB value

lda

AccumLSB

; of the phase accum.

;3 - The fractional

add

Frac_K

; constant is added to

; the LSB of the phase

; accumulator.

sta

AccumLSB

;3 - Make sure that

; the updated value is

; kept for the next time

; through the loop.

* Here's the second half of our 16-bit addition. This will

* propagate any overflow from the 8-bit addition of the

* AccumLSB and Frac_K into AccumMSB:

lda

;3 - Get current MSB value

AccumMSB

; of the phase accum.

;3 - The integer constant

adc

Int K

; is added to the MSB of

the phase accum.

Notice the addition

; with carry.

sta

AccumMSB

;3 - Save for next time

; through the loop.

```

\$01

PortB

```

* If we've made it here, then we are ready to turn our phase

```

\* value into a sine wave at the output of the DAC:

```

tax

;1 - ACCA contains the

; integer portion of the

; 16-bit phase value.

; We need to move it into

; the X-reg to do a table

; look-up.

lda

SineTable,X

;4 - Get the sine value

sta

DAC

;3 - Send it to the DAC

; to create a real-world

; signal.

;5 - Branch to top of

bra

SignalGen

; signal generation

; for an infinite loop

```

\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*

#### \* Tables

| SineTable | FCB | \$80,\$83,\$86,\$89,\$8C,\$90,\$93,\$96<br>\$99,\$9C,\$9F,\$A2,\$A5,\$A8,\$AB<br>\$AE,\$B1,\$B3,\$B6,\$B9,\$BC,\$BF,\$C1<br>\$C4,\$C7,\$C9,\$CC,\$CE,\$D1,\$D3<br>\$D5,\$D8,\$DA,\$DC,\$DE,\$E0,\$E2,\$E4<br>\$E6,\$E8,\$EA,\$EB,\$ED,\$EF,\$F0<br>\$F1,\$F3,\$F4,\$F5,\$F6,\$F8,\$F9,\$FA<br>\$FA,\$FB,\$FC,\$FD,\$FD,\$FC,\$FB<br>\$FE,\$FF,\$FF,\$FF,\$FF,\$FF,\$FF<br>\$FE,\$FE,\$FE,\$FD,\$FD,\$FC,\$FB<br>\$FA,\$FA,\$F9,\$F8,\$F6,\$F5,\$F4,\$F3<br>\$F1,\$F0,\$EF,\$ED,\$EB,\$EA,\$E8<br>\$E6,\$E4,\$E2,\$E0,\$DE,\$DC,\$DA,\$D8<br>\$D5,\$D3,\$D1,\$CE,\$CC,\$C9,\$C7<br>\$C4,\$C1,\$BF,\$BC,\$B9,\$B6,\$B3,\$B1<br>\$AE,\$AB,\$A8,\$A5,\$A2,\$9F,\$9C<br>\$99,\$96,\$93,\$90,\$8C,\$89,\$86,\$83<br>\$80,\$7D,\$7A,\$77,\$74,\$70,\$6D<br>\$6A,\$67,\$64,\$61,\$5E,\$5B,\$58,\$55<br>\$52,\$4F,\$4D,\$4A,\$47,\$44,\$41<br>\$3F,\$3C,\$39,\$37,\$34,\$32,\$2F,\$2D<br>\$2B,\$28,\$26,\$24,\$22,\$20,\$1E<br>\$1C,\$1A,\$18,\$16,\$15,\$13,\$11,\$10<br>\$0F,\$0D,\$0C,\$0B,\$0A,\$08,\$07<br>\$06,\$06,\$05,\$04,\$03,\$03,\$02,\$02<br>\$02,\$01,\$01,\$01,\$01,\$01,\$01<br>\$01,\$02,\$02,\$02,\$03,\$03,\$04,\$05<br>\$06,\$06,\$07,\$08,\$0A,\$0B,\$0C<br>\$0D,\$0F,\$10,\$11,\$13,\$15,\$16,\$18 |

|-----------|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | FCB<br>FCB                              | \$01,\$02,\$02,\$02,\$03,\$03,\$04,\$05<br>\$06,\$06,\$07,\$08,\$0A,\$0B,\$0C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|           | FCB<br>FCB<br>FCB<br>FCB<br>FCB<br>FCB  | \$0D,\$0F,\$10,\$11,\$13,\$15,\$16,\$18<br>\$1A,\$1C,\$1E,\$20,\$22,\$24,\$26<br>\$28,\$2B,\$2D,\$2F,\$32,\$34,\$37,\$39<br>\$3C,\$3F,\$41,\$44,\$47,\$4A,\$4D<br>\$4F,\$52,\$55,\$58,\$5B,\$5E,\$61,\$64<br>\$67,\$6A,\$6D,\$70,\$74,\$77,\$7A,\$7D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|           |                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| * * * * * * * * * * * * * * | *****     | *****           | *****         | ****** |

|-----------------------------|-----------|-----------------|---------------|--------|

| * Vector Setup              |           |                 |               |        |

|                             | ORG<br>DW | \$FFFE<br>START | ;set up reset | vector |