**NOVEMBER 1994**

# HC11KA4 EMULATOR MODULE USER'S MANUAL

Motorola reserves the right to make changes without further notice to any products herein to improve reliability, function, or design. Motorola does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part.

Motorola and the Motorola logo are registered trademarks of Motorola Inc.

Motorola Inc. is an Equal Opportunity/Affirmative Action Employer.

# **CONTENTS**

# **CHAPTER 1 INTRODUCTION**

| 1.1 | Development Systems                                | 1-1   |

|-----|----------------------------------------------------|-------|

|     | 1.1.1 Motorola Modular Development System (MMDS11) | 1-1   |

|     | 1.1.2 M68HC11EVS Evaluation System (HC11EVS)       | 1-2   |

| 1.2 | EM Layout                                          | 1-3   |

| 1.3 |                                                    |       |

|     | CHAPTER 2 MMDS11 CONFIGURATION AND OPERATION       |       |

| 2.1 | Setting Clock Source Select Jumper Headers         | 2-1   |

| 2.2 | The Emulated MCU                                   | 2-2   |

| 2.3 | Remaining System Installation                      | 2-3   |

|     | CHAPTER 3 HC11EVS CONFIGURATION AND OPERATION      |       |

| 3.1 | Setting Clock Source Select Jumper Headers         | 3-1   |

| 3.2 | EVS Limitations                                    | 3-2   |

| 3.3 | Logic Analyzer Connector (P1)                      | 3-4   |

| 3.4 | Remaining System Installation                      | 3-6   |

|     |                                                    |       |

| IND | <b>DEX</b> in                                      | dex-1 |

HC11KA4EMUM/D iii

# **FIGURES**

| 1-1 | HC11KA4 Emulator Module                         | 1-3 |

|-----|-------------------------------------------------|-----|

| 1-2 | Target Connector Pin Assignments                | 1-4 |

|     | Connector P1 Pin Assignments                    |     |

|     |                                                 |     |

|     |                                                 |     |

|     | TABLES                                          |     |

| 1-1 | Target Connector P4 Signal Descriptions         | 1-5 |

|     | Target Connector P5 Signal Descriptions         |     |

|     | Logic Analyzer Connector P1 Signal Descriptions |     |

# CHAPTER 1 INTRODUCTION

This user's manual explains connection, configuration, and operation information specific to the HC11KA4EM Emulator Module (KA4EM). The KA4EM makes possible emulation and debugging of target systems based on MC68HC11KA4 microcontroller units (MCUs).

Your KA4EM can be part of two Motorola development systems. This chapter describes those systems and explains the layout of the KA4EM.

#### 1.1 DEVELOPMENT SYSTEMS

Your KA4EM can be part of two Motorola development tools: the HC11 Motorola Modular Development System (MMDS11) and the M68HC11EVS Evaluation System (HC11EVS).

#### 1.1.1 Motorola Modular Development System (MMDS11)

The MMDS11 is an emulator system that provides a bus state analyzer and realtime memory windows. The unit's integrated design environment includes an editor, an assembler, user interface, and source-level debug. A complete MMDS11 consists of:

- a station module the metal MMDS11 enclosure, containing the control board and the internal power supply. Most system cables connect to the MMDS11 station module. (The cable to an optional target system, however, runs through an aperture in the station module enclosure to connect directly to the emulator module.

- an emulator module (EM) such as the KA4EM: a separately purchased printed circuit board that enables system functionality for a specific set of MCUs. The EM fits into the station module through a sliding panel in the enclosure top. The EM has a connector for the target cable.

- **two logic clip cable assemblies** twisted-pair cables that connect the station module to your target system, a test fixture, a clock, or any other circuitry useful for evaluation or analysis. One end of each cable assembly has a molded connector, which fits into station-module pod A or pod B. Leads at the other end of each cable terminate in female probe tips. Ball clips come with the cables.

HC11KA4EMUM/D 1-1

- a 9-lead RS-232 serial cable the cable that connects the station module to the host computer RS-232 port.

- **a 9- to 25-pin adapter** a molded assembly that lets you connect the 9-lead cable to a 25-pin serial port.

- **system software** software, on 3-1/2 inch diskettes.

- **MMDS11 documentation** an MMDS11 operations manual (MMDS11OM/D) and the appropriate EM user's manual.

You select the MMDS11 baud rate: 1200, 2400, 4800, 9600, 19200, 38400, or 57600.

As mentioned, your KA4EM gives the MMDS11 the ability to emulate target systems based on MC68HC11KA4 MCUs. By substituting a different EM, you can enable your MMDS11 to emulate an MCU of a different series. (Your Motorola representative can explain all the EMs available.)

Chapter 2 explains how to configure and use your KA4EM as part of an MMDS11 system. For information about MMDS11 software or the station module, see the MMDS11 operations manual. For layout and configuration information pertaining to a different EM, see the corresponding EM user's manual.

#### 1.1.2 M68HC11EVS Evaluation System (HC11EVS)

An HC11EVS is an economical, two-board tool for designing, debugging, and evaluating target systems based on an MC68HC11 MCU. A complete HC11EVS consists of:

- a platform board (PFB) the bottom board, which supports the emulator module. The platform board has connectors for power and for the terminal or host computer.

- an emulator module (EM) such as the KA4EM: a separately purchased printed circuit board that enables system functionality for a specific set of MCUs. The EM fits onto the PFB. The EM has connectors for a target cable and for a cable to a logic analyzer.

- an RS-232 serial cable a separately purchased cable that connects the PFB to the host computer RS-232 port.

- **system software** software, on 3-1/2 inch or 5-14 inch diskettes.

- **HC11EVS documentation** an HC11EVS operations manual (HC11EVSOM/D) and the appropriate EM user's manual.

An EVS features automatic baud rate selection: 2400, 4800, 9600, or 19200.

1-2 HC11KA4EMUM/D

As mentioned, your KA4EM gives the HC11EVS the ability to emulate target systems based on MC68HC11KA4 MCUs. By substituting a different EM, you can enable your HC11EVS to emulate an MCU of a different series. (Your Motorola representative can explain all the EMs available.)

Chapter 3 explains how to configure and use your KA4EM as part of an HC11EVS. For information about HC11EVS software or the platform board, see the HC11EVS operations manual. For layout and configuration information pertaining to a different EM, see the corresponding EM user's manual.

#### 1.2 EM LAYOUT

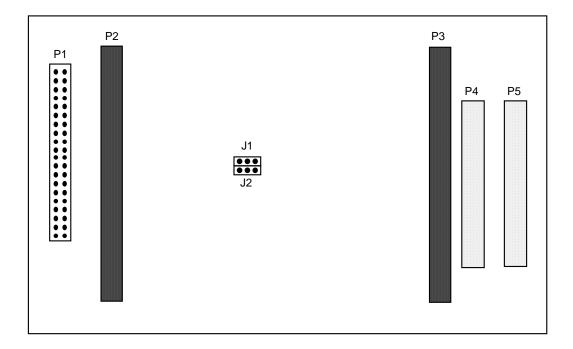

Figure 1-1 shows the layout of the KA4EM. Jumper headers J1 and J2 select the clock-signal source.

Connectors P4 and P5, for a separately purchased target cable assembly, are the interface to a target system. If you install the KA4EM in the MMDS11 station module, the target cable passes through the slit in the station module enclosure. Connector P1 connects to a logic analyzer. (Connector P1 has more significance for an HC11EVS, and an MMDS11 includes a bus state analyzer.)

Figure 1-1. HC11KA4 Emulator Module

HC11KA4EMUM/D 1-3

Expansion header connectors P2 and P3 connect together the EM and the control board (for an MMDS11) or the EM and the platform board (for an HC11EVS).

# 1.3 TARGET CONNECTORS (P4, P5)

Figure 1-2 shows the pin assignments for connectors P4 and P5. Tables 1-1 and 1-2 list signal descriptions.

|     |    | P4  |    |     |     |    | P5  |    |     |

|-----|----|-----|----|-----|-----|----|-----|----|-----|

| NC  | 1  | • • | 2  | GND | VRL | 1  | • • | 2  | PE0 |

| PD5 | 3  | • • | 4  | PD4 | PE1 | 3  | • • | 4  | PE2 |

| PD3 | 5  | • • | 6  | PD2 | PE3 | 5  | • • | 6  | PE4 |

| PD1 | 7  | • • | 8  | PD0 | PE5 | 7  | • • | 8  | PE6 |

| MDA | 9  | • • | 10 | MDB | PE7 | 9  | • • | 10 | NC  |

| RST | 11 | • • | 12 | T4X | IRQ | 11 | • • | 12 | PG7 |

| EXT | 13 | • • | 14 | 4XO | XRQ | 13 | • • | 14 | PH3 |

| Е   | 15 | • • | 16 | PC7 | PH2 | 15 | • • | 16 | PH1 |

| PC6 | 17 | • • | 18 | PC5 | PH0 | 17 | • • | 18 | PB0 |

| PC4 | 19 | • • | 20 | PC3 | PB1 | 19 | • • | 20 | PB2 |

| PC2 | 21 | • • | 22 | PC1 | PB3 | 21 | • • | 22 | PB4 |

| PC0 | 23 | • • | 24 | PF0 | PB5 | 23 | • • | 24 | PB6 |

| PF1 | 25 | • • | 26 | PF2 | PB7 | 25 | • • | 26 | PA0 |

| PF3 | 27 | • • | 28 | PF4 | PA1 | 27 | • • | 28 | PA2 |

| PF5 | 29 | • • | 30 | PF6 | PA3 | 29 | • • | 30 | PA4 |

| PF7 | 31 | • • | 32 | GND | PA5 | 31 | • • | 32 | PA6 |

| NC  | 33 | • • | 34 | VRH | PA7 | 33 | • • | 34 | VDD |

Figure 1-2. Target Connector Pin Assignments

1-4 HC11KA4EMUM/D

**Table 1-1. Target Connector P4 Signal Descriptions**

| Pin   | Mnemonic | Signal                                                                                                                                                                                                                                    |  |  |

|-------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1, 33 |          | No connection                                                                                                                                                                                                                             |  |  |

| 2, 32 | GND      | GROUND                                                                                                                                                                                                                                    |  |  |

| 3—8   | PD5—PD0  | PORT D (bits 5—0) - General-purpose I/O lines controlled by software via data direction and data registers (PD0 and PD1 are buffered).                                                                                                    |  |  |

| 9     | MDA      | MODE A SELECT - Select line for single-chip mode.                                                                                                                                                                                         |  |  |

| 10    | MDB      | MODE B SELECT - Select line for expanded or special test mode.                                                                                                                                                                            |  |  |

| 11    | RST      | RESET - Active-low bidirectional control line that initializes the MCU.                                                                                                                                                                   |  |  |

| 12    | XTL      | EXTERNAL CLOCK - MCU clock output line.                                                                                                                                                                                                   |  |  |

| 13    | EXT      | EXTERNAL TIMER - MCU clock input line.                                                                                                                                                                                                    |  |  |

| 14    | T4X      | 4 TIMES CLOCK - Extra timing signal: four times the E clock signal.                                                                                                                                                                       |  |  |

| 15    | Е        | E CLOCK - Main bus clock signal for timing reference.                                                                                                                                                                                     |  |  |

| 16—23 | PC7—PC0  | PORT C (bits 7—0) - In single-chip mode, buffered general-purpose I/O lines controlled by software via data direction and data registers.  DATA BUS (bits 7—0) - In expanded or special-test mode, buffered bidirectional data bus lines. |  |  |

| 24—31 | PF0—PF7  | PORT F (bits 0—7) - In single-chip mode, buffered general-purpose I/O lines controlled by software via data direction and data registers.  ADDRESSES (bits 0—7) - In expanded or special-test mode, MCU output address bus.               |  |  |

| 34    | VRH      | VOLTAGE REFERENCE HIGH - Input reference supply voltage (high) line.                                                                                                                                                                      |  |  |

HC11KA4EMUM/D 1-5

**Table 1-2. Target Connector P5 Signal Descriptions**

| Pin   | Mnemonic | Signal                                                                                                                                                                                                                       |  |  |

|-------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1     | VRL      | VOLTAGE REFERENCE LOW - Input reference supply voltage (low) line.                                                                                                                                                           |  |  |

| 2—9   | PE0—PE7  | PORT E (bits 0—7) - General-purpose I/O lines controlled by software via data direction and data registers.                                                                                                                  |  |  |

| 10    |          | No connection                                                                                                                                                                                                                |  |  |

| 11    | IRQ      | TARGET INTERRUPT REQUEST - Active-low input signal from the target that asynchronously applies a maskable MCU interrupt.                                                                                                     |  |  |

| 12    | PG7      | PORT G (bit 7) - General-purpose I/O line controlled by software via data direction and data registers.                                                                                                                      |  |  |

| 13    | XRQ      | X INTERRUPT REQUEST - Active-low input line for requesting MCU asynchronous non-maskable interrupts.                                                                                                                         |  |  |

| 14—17 | PH3—PH0  | PORT H (bits 3—0) - General-purpose I/O lines controlled by software via data direction and data registers.                                                                                                                  |  |  |

| 18—25 | PB0—PB7  | PORT B (bits 0—7) - In single-chip mode, buffered general-purpose I/O lines controlled by software via data direction and data registers.  ADDRESSES (bits 15—8) - In expanded or special-test mode, MCU output address bus. |  |  |

| 26—33 | PA0—PA7  | PORT A (bits 0—7) - General-purpose I/O lines controlled by software via data direction and data registers.                                                                                                                  |  |  |

| 34    | VDD      | VDD - Target power.                                                                                                                                                                                                          |  |  |

As connector P1 has more importance for an HC11EVS than for an MMDS11, pin assignments for connector P1 are in Chapter 3.

To configure your KA4EM for use as part of an MMDS11, follow the instructions of Chapter 2. To configure your KA4EM for use as part of an HC11EVS, follow the instructions of Chapter 3.

1-6 HC11KA4EMUM/D

#### **CHAPTER 2**

#### MMDS11 CONFIGURATION AND OPERATION

This chapter explains how to configure and use your KA4EM as part of an MMDS11. For other parts of system installation or configuration, see the MMDS11 operations manual (MMDS11OM/D). (If you will use your KA4EM as part of an HC11EVS, go to Chapter 3 for corresponding information.)

Paragraph 2.1 explains how to set KA4EM jumper headers. Paragraph 2.2 explains considerations pertaining to the MCU your emulate. Paragraph 2.3 explains remaining system installation.

Note that you can configure a KA4EM already installed in the MMDS11 station module enclosure. To do so, switch off station-module power, remove the panel, then follow the guidance of this chapter.

#### **CAUTION**

Be sure to switch off power if you reconfigure an installed EM. Reconfiguring EM jumper headers with power left on can damage MMDS11 circuits.

#### 2.1 SETTING CLOCK SOURCE SELECT JUMPER HEADERS

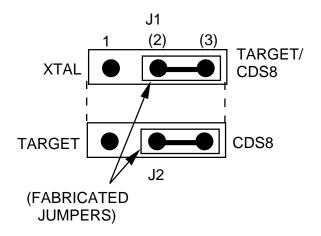

Your KA4EM has two jumper headers, J1 and J2, which determine the clock-signal source. The diagram below shows the factory configuration: the fabricated jumper between J1 pins 2 and 3 selects the jumper header J2 source, the fabricated jumper between J2 pins 2 and 3 selects the clock signal from the MMDS11 control board. (The CDS8 label means MMDS11.)

HC11KA4EMUM/D 2-1

Alternatively, you may select the KA4EM canned oscillator clock source. To do so, reposition the J1 jumper between pins 1 and 2. (The J2 configuration does not matter if the J1 jumper is between pins 1 and 2.)

The third possible clock-signal source is the target system. For this configuration, position the J1 jumper between pins 2 and 3, and the J2 jumper between pins 1 and 2. Then, connect the target-system clock signal to the EXT pin (pin 13 of connector P4). The target-system clock signal must have the appropriate frequency for the frequency of bus operation:

- For 1 MHz bus operation, the EXT-pin frequency must be 4 MHz.

- For 2 MHz bus operation, the EXT-pin frequency must be 8 MHz.

- For 3 MHz bus operation, the EXT-pin frequency must be 12 MHz.

- For 4 MHz bus operation, the EXT-pin frequency must be 16 MHz (the maximum for this signal).

#### 2.2 THE EMULATED MCU

Your MMDS11 uses a specific personality file for the MCU type being emulated. For example, to emulate an MC68HC11KA4 MCU, the system uses personality file 10001Vxx.MEM. (MMDS11 personality file names follow the pattern 100ZZVxx.MEM, where ZZ corresponds to one or more MCUs, and xx is the version of the file.)

MMDS11 software loads the default personality file (10001Vxx.MEM) upon powerup. To replace this file with a different one, use the LOADMEM command. (For more information about the LOADMEM command, see the explanation in the MMDS11 operations manual.)

Alternatively, you can insert the line LOADMEM 100ZZVxx.MEM in the STARTUP.11 script file. This way, the system automatically loads the specified personality file as part of system startup. (For more information about the STARTUP.11 script file, see the SCRIPT command explanation in the MMDS11 operations manual.)

Make sure that you properly configure all control registers of the MCU being emulated; you also should know the corresponding memory map. For more information, see the technical data book for the MCU.

2-2 HC11KA4EMUM/D

#### 2.3 REMAINING SYSTEM INSTALLATION

Once you have configured headers J1 and J2, you are through with KA4EM configuration:

- To install the KA4EM in an MMDS11 station module, remove the panel from the station-module top. Fit together EM connectors P2 and P3 (on the bottom of the board) and control-board connectors P1 and P2. Snap the corners of the EM onto the plastic standoffs. Connect the target cable, if appropriate. Replace the panel.

- If your KA4EM already is installed in the station module, reconnect the target cable (if necessary). Replace the panel.

At this point, you are ready to make remaining cable connections, as necessary, and restore power. For instructions, consult the MMDS11 operations manual (MMDS11OM/D).

HC11KA4EMUM/D 2-3

2-4 HC11KA4EMUM/D

#### **CHAPTER 3**

#### **HC11EVS CONFIGURATION AND OPERATION**

This chapter explains how to configure and use your KA4EM as part of an HC11EVS. For other parts of system installation or configuration, see the HC11EVS operations manual (HC11EVSOM/D). (If you will use your KA4EM as part of an MMDS11, go to Chapter 2 for corresponding information.)

Paragraph 3.1 explains how to set KA4EM jumper headers. Paragraph 3.2 explains limitations on using the KA4EM in an HC11EVS. Paragraph 3.3 explains pin assignments and signal descriptions for the logic analyzer connector (P1). Paragraph 3.4 explains remaining system installation.

Note that you can configure a KA4EM already installed on the HC11EVS platform board. To do so, disconnect platform-board power, then follow the guidance of this chapter.

#### **CAUTION**

Be sure to disconnect power if you reconfigure an installed EM. Reconfiguring EM jumper headers with power left on can damage HC11EVS circuits.

#### 3.1 SETTING CLOCK SOURCE SELECT JUMPER HEADERS

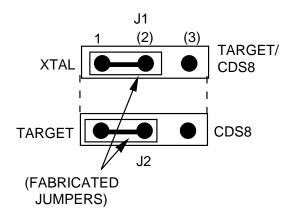

Your KA4EM has two jumper headers, J1 and J2, which determine the clock-signal source. To use the KA4EM canned oscillator clock source, position the J1 fabricated jumper between pins 1 and 2, per the diagram below. (The J2 configuration does not matter for this J1 configuration.)

HC11KA4EMUM/D 3-1

Alternatively, you may select a clock source from the target system. To do so, position the J1 jumper between pins 2 and 3, and the J2 jumper between pins 1 and 2. Then, connect the target-system clock signal to the EXT pin (pin 13 of connector P4). The target-system clock signal must have the appropriate frequency for the frequency of bus operation:

- For 1 MHz bus operation, the EXT-pin frequency must be 4 MHz.

- For 2 MHz bus operation, the EXT-pin frequency must be 8 MHz.

- For 3 MHz bus operation, the EXT-pin frequency must be 12 MHz.

- For 4 MHz bus operation, the EXT-pin frequency must be 16 MHz (the maximum for this signal).

#### **NOTE**

The pins 2-and-3 configuration for both headers J1 and J2 is not correct for a KA4EM that is part of an HC11EVS.

#### 3.2 EVS LIMITATIONS

To use your KA4EM as part of an HC11EVS, you must properly configure all control registers of the MCU being emulated; you also should know the corresponding memory map. For more information, see the technical data book for the MCU. Limitations 1 through 8, below, also apply when you use your KA4EM in an HC11EVS.

**Limitation 1. CLI/RTI.** You may not trace a clear interrupt mask (CLI) or return from interrupt (RTI) instruction with an interrupt enabled and pending, due to MCU interrupt handling. Attempting such a trace causes an interrupt in the monitor map; this forces a software reset of the HC05EVS. User breakpoints remain in the user map as SWI instructions; you must remove such SWI instructions.

**Limitation 2. Branch.** Do not trace a conditional branch instruction (such as BRCLR) that branches to itself. As the monitor places an SWI instruction on the object of the branch, the system never would execute the instruction. However, it would appear to you that the instruction had executed. You may enter a G command while the PC points to this type of instruction as long as the instruction is not a breakpoint address.

**Limitation 3. Internal RAM.** Do not trace instructions in internal MCU RAM. Do not insert breakpoints in internal MCU RAM. You may execute code out of internal RAM, provided that the code starts at address \$0001 or greater. (Such code starting at internal RAM address \$0000 would cause an HC11EVS malfunction.)

3-2 HC11KA4EMUM/D

**Limitation 4. IRQ/SWI.** Whenever possible, avoid mixing interrupt requests (IRQs) and user software interrupts (SWIs). This prevents a possible IRQ-SWI timing problem: a concurrent hardware interrupt and SWI could cause an HC05EVS failure that could stop program execution. To recover from such a failure (which occurs very infrequently, statistically), press the master reset switch (SW3).

**Limitation 5. Remapping.** To remap register locations, you first must issue an INIT command via the monitor. In special-test mode, the monitor automatically updates the initialization register. This restriction applies even if you use the user rest function. For proper HC11EVS operation, you always must update the monitor (via the INIT command) when you remap the initialization register, before your perform any INIT write operations. Such updates are necessary as the monitor must know register locations to access programmable chip selects, and to update the computer operating properly (COP) watchdog timer.

**Limitation 6. Breakpoint Debugging.** To debug via breakpoints, you must use the G or T command. If you press the platform-board user reset switch (SW2), the monitor ignores breakpoints during program execution.

**Limitation 7. Protected Registers.** Normally, it is not possible to write to 64-cycle protected registers, such as INIT and TMSK2 in single-chip or expanded mode. This is because the monitor initialization routines need more than 64 cycles: protection would be restored before the write could be carried out. But you may use the one-line assembler/disassembler to bypass this restriction:

1. 1. Enter this code:

```

>ASM E000

LDS #$FF

LDAA # (INIT value)

STAA $3D

LDAA # (OPTION value)

STAA $39

LDAA # (TMSK2 value)

STAA $24

LDAA # (BPROT value)

STAA $35

E017 BRA E017

```

2. Use the MM command to define the user reset vector as the start of the code entered:

HC11KA4EMUM/D 3-3

3. Press the platform-board user reset switch (SW2), then press the abort switch (SW1).

This initializes the protected registers. Note however, that the next master, user, or target reset will return the registers to their default state.

Note that 64-cycle protection does not apply to special-test mode. In special-test mode, you may write directly to such registers as INIT and TMSK2.

**Limitation 8. Moving EEPROM.** Do not move internal EEPROM to the range \$8D80 — \$BFFF in special-test mode. Similarly, do not move internal EEPROM to the range \$CD80 — \$FFFF in expanded mode. Either such move would overlap monitor EPROM.

### 3.3 LOGIC ANALYZER CONNECTOR (P1)

Figure 3-1 shows the pin assignments for logic analyzer connector P1. Table 3-2 lists the signal descriptions for this connector.

|       |    | Ρ | 1 |    |     |

|-------|----|---|---|----|-----|

| NC    | 1  | • | • | 2  | GND |

| NC    | 3  | • | • | 4  | NC  |

| A11   | 5  | • | • | 6  | GND |

| A10   | 7  | • | • | 8  | A12 |

| A9    | 9  | • | • | 10 | A13 |

| A8    | 11 | • | • | 12 | A14 |

| A7    | 13 | • | • | 14 | A15 |

| A6    | 15 | • | • | 16 | D7  |

| A5    | 17 | • | • | 18 | D6  |

| A4    | 19 | • | • | 20 | D5  |

| A3    | 21 | • | • | 22 | D4  |

| A2    | 23 | • | • | 24 | D3  |

| A1    | 25 | • | • | 26 | D2  |

| A0    | 27 | • | • | 28 | D1  |

| R/W   | 29 | • | • | 30 | D0  |

| NC    | 31 | • | • | 32 | LIR |

| NC    | 33 | • | • | 34 | NC  |

| NC    | 35 | • | • | 36 | NC  |

| VCC   | 37 | • | • | 38 | Е   |

| RESET | 39 | • | • | 40 | NC  |

Figure 3-1. Connector P1 Pin Assignments

3-4 HC11KA4EMUM/D

Table 3-1. Logic Analyzer Connector P1 Signal Descriptions

| Pin                                     | Mnemonic  | Signal                                                                                                                                                                   |  |

|-----------------------------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1, 3, 4, 31, 33<br>— 36, 40             |           | No connection                                                                                                                                                            |  |

| 2, 6                                    | GND       | GROUND                                                                                                                                                                   |  |

| 5, 7 — 15, 17,<br>19, 21, 23, 25,<br>27 | A0 — A15  | ADDRESS (bits 0—15) - MCU output address bus.                                                                                                                            |  |

| 16, 18, 20, 22,<br>24, 26, 28, 30       | AD7 — AD0 | DATA BUS (bits 7—0) - MCU multiplexed I/O data bus.                                                                                                                      |  |

| 29                                      | R/W       | READ/WRITE - Output signal that indicates the direction of data transferred on the bus.                                                                                  |  |

| 32                                      | LIR       | LOAD INSTRUCTION REGISTER - Open-drain, active-low output signal indicating that an instruction is starting.                                                             |  |

| 34                                      | AS        | ADDRESS STROBE - Active-low signal that indicates whether a valid address is on the address bus; used to demultiplex port C address and data signals.                    |  |

| 37                                      | VCC       | +5 VDC POWER - Input voltage (+5 Vdc @ 1.0 A) used by EVS logic circuits.                                                                                                |  |

| 38                                      | E         | EXTERNAL CLOCK - Internally generated output clock signal used as a timing reference. The frequency of E clock is 1/2 the input frequency of the signal on the OSC1 pin. |  |

| 39                                      | RESET     | RESET - Active-low bidirectional signal for starting an EVS reset.                                                                                                       |  |

HC11KA4EMUM/D 3-5

#### 3.4 REMAINING SYSTEM INSTALLATION

Once you have configured headers J1 and J2, you are through with KA4EM configuration:

To install the KA4EM on the HC11EVS platform board, fit together EM connectors P2 and P3 (on the bottom of the board) and platform-board connectors P4 and P5. Reposition the plastic standoffs as necessary, then snap the corners of the EM onto the standoffs.

At this point, you are ready to make cable connections, as necessary, and restore power. For instructions, consult the HC11EVS operations manual (HC11EVSOM/D).

3-6 HC11KA4EMUM/D

#### **INDEX**

```

baud rates: 1-2

clock source select jumper headers (J1, J2): 2-1, 2-2, 3-1, 3-2

components, system: 1-1 — 1-3

configuration and operation:

HC11EVS: 3-1 — 3-6

MMDS11: 2-1 — 2-3

connector pin assignments:

logic analyzer (P1): 3-4

target cable (P4, P5): 1-4

connector signal descriptions:

logic analyzer (P1): 3-5

target cable (P4): 1-5

target cable (P5): 1-6

EM layout: 1-3, 1-4

EVS: see HC11EVS

HC11EVS (HC11EVS Evaluation System):

configuration and operation: 3-1 — 3-6

description: 1-2, 1-3

limitations: 3-2 — 3-4

remaining system installation: 3-6

setting jumper headers: 3-1, 3-2

installation, remaining system: 2-3, 3-6

introduction: 1-1 — 1-6

jumper headers, clock source select (J1, J2): 2-1, 2-2, 3-1, 3-2

layout, EM: 1-3

limitations, HC11EVS: 3-2 — 3-4

logic analyzer connector (P1): 3-4, 3-5

```

HC11KA4EMUM/D Index-1

## MMDS11 (HC11 Motorola Modular Development System):

configuration and operation: 2-1 — 2-3

description: 1-1, 1-2 emulated MCU: 2-2

remaining system installation: 2-3 setting jumper headers: 2-1, 2-2

personality files: 2-2

pin assignments:

logic analyzer connector P1: 3-4 target cable connectors P4, P5: 1-4

remaining system installation: 2-3, 3-6

signal descriptions:

logic analyzer connector P1: 3-5 target cable connector P4: 1-5

target cable connector P5: 1-6

system components:

HC11EVS: 1-2

MMDS11: 1-1, 1-2

target cable connectors (P4, P5): 1-4 — 1-6