## Motorola Semiconductor Engineering Bulletin

**EB368**

# In-Circuit Programming of FLASH Memory Using the Monitor Mode for the MC68HC908GR8

By Timothy J. Airaudi

Applications Engineering, Microcontroller Division

Austin, Texas

#### Introduction

This engineering bulletin describes how to perform in-circuit programming (ICP) of the FLASH memory using monitor mode.

Two methods are discussed here:

- Using the M68ICS08GR in-circuit simulator (ICS) with P&E Microsystems software

- Using P&E Microsystems software with an external communications circuit

ICP is a process where user code is programmed into the device's FLASH memory after the part has been assembled into the application. ICP also allows the original users code to be erased and reprogrammed. This method can be used in development, production/manufacturing and in a field environment.

EB368. Rev. 1

© Motorola, Inc., 2000

#### **Using Monitor Mode for FLASH Programming**

Motorola's current solution for ICP is the In-Circuit Simulators and P&E's software.

The software and ICSs allow programming of the parts on the simulator or in the target circuit via a MON08 ribbon cable. The software also allows programming of the part without the ICS, with an external communications circuit.

All of the programming described in this engineering bulletin is accomplished by placing the part into monitor mode. In this mode, erasing and programming are done through a single-wire interface with the host computer.

The two ways to enter monitor mode are:

- The ICS provides the entry requirements to enter standard monitor mode. These entry requirements must be implemented on the target board if the ICS is not used.

- A second way to enter monitor mode, that does not require a high voltage on the IRQ pin, is called forced monitor mode. This mode does not need to meet all the monitor mode entry conditions of the standard monitor mode, but it does require the part to be blank (erased).

This engineering bulletin describes how to connect the part, communicate at different baud rates, place it into monitor mode, pass security, and erase and program the part. If the security code is not known, the contents of the FLASH can't be read, but the FLASH can be erased and reprogrammed.

Information on the M68ICS08GR can be found at http://mcu.motsps.com. P&E Microsystems software can be downloaded free from that company's Web site.

**NOTE:**

All of the oscillators used in this application note were the 4 pin "powered" or "canned" type oscillators. Discussing all the different vendors of crystals, ceramic oscillators, other required external components, and component layout variables would be too extensive.

EB368

#### ICP Using M68ICS08GR8's MON08 Interface

Use this procedure for performing ICP using the ICS's MON08 cable to the target application.

- 1. Materials required:

- a. PC with P&E software installed (version 1.25 or higher)

- b. M68ICS08GR simulator

- c. Adapter/connector to connect the female end of the MON08 cable to the part on the target application

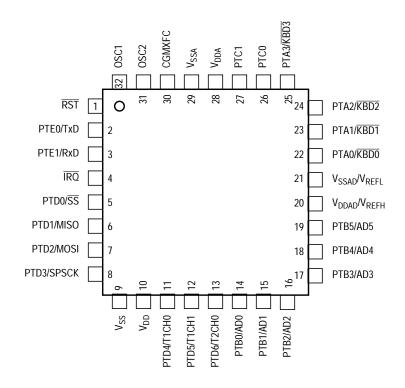

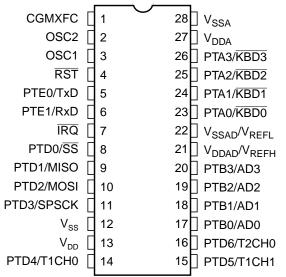

- d. Pin assignment diagram (see Figure 1 and Figure 2)

- e. Monitor mode entry requirements (see **Table 1**)

- f. Crystal oscillator on the target, or from an external clock source, with a value from Table 2

- g. Target board must have the ability to perform a power-on reset (POR) not just a reset (required to enter monitor mode).

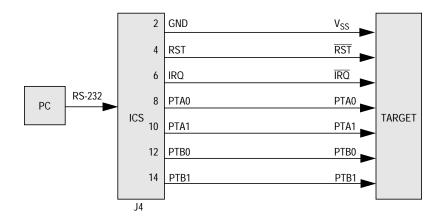

- 2. Connections (see Figure 3):

- a. 9-pin serial cable from PC to the ICS

- b. 5 volts to the ICS

- c. MON08 cable from J4 of the ICS to the target board with these connections:

- MON08 GND to the V<sub>SS</sub> pin on the part

- MON08 RST to the RST pin on the part

- MON08 IRQ to the  $\overline{IRQ}$  pin on the part

- MON08 PTA0 to the PTA0 pin on the part

- MON08 PTA1 to the PTA1 pin on the part

- MON08 PTB0 to the PTB0 pin on the part

- MON08 PTB1 to the PTB1 pin on the part

- d. ICS jumpers in these positions:

- W4 and W10 to V<sub>TST</sub>

- W3 to normal

- W6 to 5 V

- e. It is assumed that all V<sub>DD</sub> and V<sub>SS</sub> pins on the part are already connected.

EB368

- 3. Operation Standard monitor mode entry:

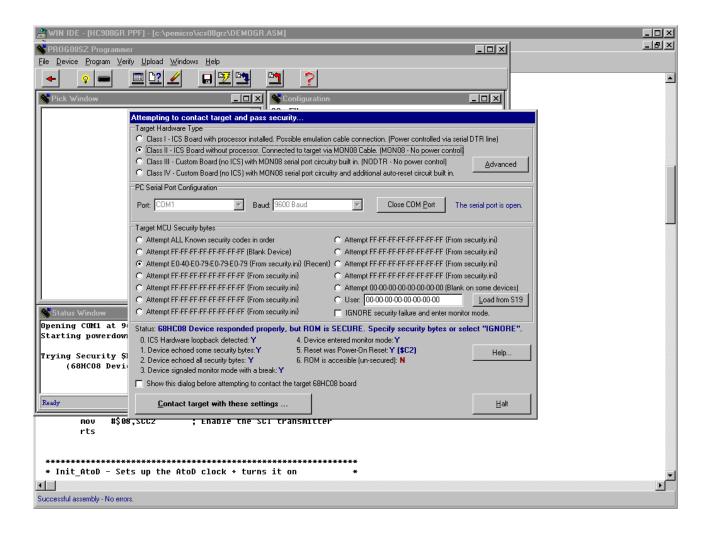

- a. Launch P&E's WINIDE in the ICS08GRZ software.

- b. Open desired file. (Demo file can be used.)

- c. Assemble/Compile the file (see Figure 7).

- d. Turn on power to the ICS.

- e. Turn on power to the target.

- f. Launch the programmer.

- g. From "Target Hardware Type," select "Class II" (see Figure 8).

- h. From "PC Serial Port Configuration," select the PC port you are using and the appropriate baud rate (see **Table 2**).

- From "Target MCU Security Bytes" select appropriate security code (blank part = FF).

- j. Select "Contact Target with these Settings..."

- Follow the instructions in the "Power down/up Dialog" windows.

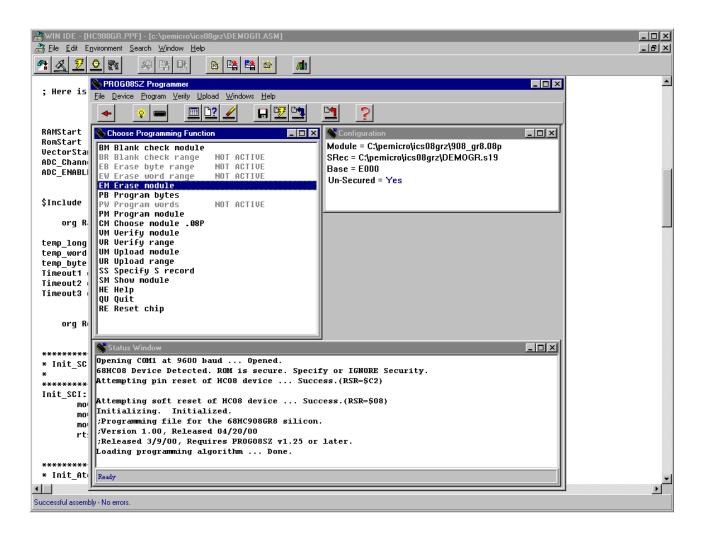

- I. Select appropriate algorithm for the part.

- m. Double click on "Erase Module" EM (see Figure 9)

- n. Double click on "Program Module" PM

- o. Record security bytes. This information can be seen by quitting and then re-entering the programmer. The S19 record will have the same security bytes as the part just programmed as long as it is not changed. The security bytes consist of the information stored in the interrupt vectors, \$FFF6-\$FFFD.

- 4. Operation Forced monitor mode entry:

- a. Blank part with oscillator value from Table 2:

- Move jumper W4 and W10 to Vdd\_MCU.

- PTB0 and PTB1 connections are not required.

- b. Blank part with 32.768-kHz oscillator, 9600 baud:

- Move jumper W3 to the "Forced 0" position.

EB368

ICP Using the External Communications Circuit (No ICS) Use this procedure for performing ICP via an external communications circuit in place of this ICS to the target application.

- 1. Materials required:

- a. PC with P&E software installed (version 1.25 or higher).

- Adapter/connector to connect the male end of the 9 pin serial cable to the part on the target application.

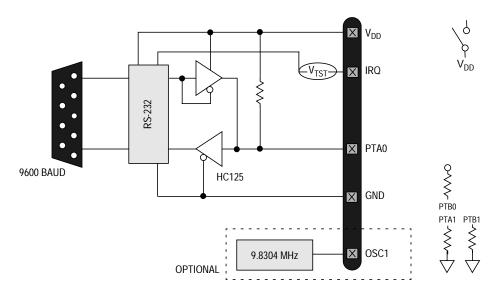

- RS-232 communications circuit. Also needed is a 5-volt power source to power this circuit. (see Figure 4, Figure 5, and Figure 6)

- d. Pin assignment diagram (see Figure 1 and Figure 2)

- e. Monitor mode entry requirements (see **Table 1**)

- f. Crystal oscillator on the target, or from an external clock source, with a value from Table 2

- g. Target board must have the ability to perform a POR not just a reset (required to enter monitor mode).

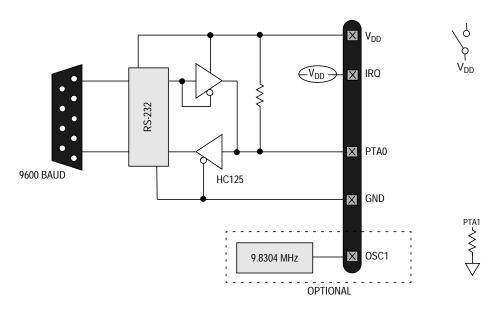

- 2. Connections (see Figure 4):

- a. 9-pin serial cable from PC to the communications circuit

- b. V+ pin of the RS-232 part to the  $\overline{IRQ}$  pin of the part

- c. Communications pin of HC125 to PTA0 of the part.

- d. Target pin requirements:

- PTA1 of part to V<sub>SS</sub>

- PTB0 of the part to V<sub>DD</sub> via pullup resistor

- PTB1 of the part to V<sub>SS</sub>

- RESET has an internal pullup resistor.

- e. It is assumed that all V<sub>DD</sub> and V<sub>SS</sub> pins on the part are already connected.

- 3. Operation Standard monitor mode entry:

- a. Launch P&E's WINIDE in the ICS08GR software.

- b. Open desired file. (Demo file can be used.)

- c. Assemble/Compile the file (see Figure 7).

EB368

- d. Apply power to the Communications Circuit.

- e. Turn on power to the target.

- f. Launch the programmer.

- g. From "Target Hardware Type" select "Class III" (see Figure 8).

- h. From "PC Serial Port Configuration," select the PC port you are using and the appropriate baud rate (see **Table 2**).

- From "Target MCU Security Bytes," select appropriate security code (blank part = FF).

- j. Select "Contact Target with these Settings..."

- k. Follow the instructions in the "Power Cycle Dialog" window.

- I. Select appropriate algorithm for the part.

- m. Double click on "Erase Module" EM (see Figure 9).

- n. Double click on "Program Module" PM.

- o. Record security bytes. This information can be seen by quitting and then re-entering the programmer. The S19 record will have the same security bytes as the part just programmed as long as it is not changed. The security bytes consist of the information stored in the interrupt vectors, \$FFF6—\$FFFD.

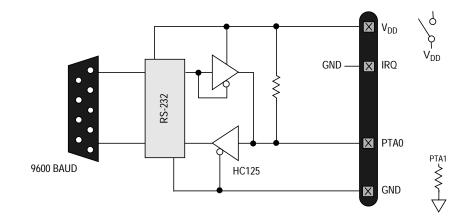

- 4. Operation Forced monitor mode entry:

- a. Blank part with oscillator value from Table 2. See Figure 5.

- Remove connection to IRQ pin of the part.

- IRQ has internal pullup resistor.

- PTB0 and PTB1 connections are not required.

- b. Blank part with 32.768-kHz oscillator. See Figure 6.

- Connect  $\overline{IRQ}$  pin to  $V_{SS}$ .

Figure 1. QFP Pin Assignment

NOTE: Ports PTB4, PTB5, PTC0, and PTC1 are available only with the QFP.

Figure 2. 28-Pin Pin Assignments

**Table 1. Monitor Mode Signal Requirements and Options**

| ĪRQ                          | RESET                                     | \$FFFE/<br>\$FFFF | PLL | РТВ0 | PTB1 | External<br>Clock <sup>(1)</sup> | CGMOUT        | Bus<br>Frequency | СОР      | For Serial<br>Communication |      |                                                      |                                                                     |

|------------------------------|-------------------------------------------|-------------------|-----|------|------|----------------------------------|---------------|------------------|----------|-----------------------------|------|------------------------------------------------------|---------------------------------------------------------------------|

|                              |                                           |                   |     |      |      |                                  |               |                  |          | PTA0                        | PTA1 | Baud<br>Rate <sup>(2) (3)</sup>                      | Comment                                                             |

| Х                            | GND                                       | х                 | Х   | х    | Х    | х                                | 0             | 0                | Disabled | Х                           | Х    | 0                                                    | No operation until reset goes high                                  |

|                              | V <sub>DD</sub>                           |                   |     |      |      |                                  |               |                  |          | 1                           | 0    | 9600                                                 | PTB0 and PTB1                                                       |

| V <sub>TST</sub>             | or<br>V <sub>TST</sub>                    | Х                 | OFF | 1    | 0    | 9.8304<br>MHz                    | 4.9152<br>MHz | 2.4576<br>MHz    | Disabled | х                           | 1    | DNA voltages only required if IRQ = V <sub>TST</sub> |                                                                     |

| V <sub>DD</sub>              | V <sub>DD</sub>                           | ФЕГЕ              | OFF | Х    | X    | 9.8304                           | 4.9152        | 2.4576           | Disabled | 1                           | 0    | 9600                                                 | External frequency always divided by 4                              |

| V DD                         | V DD                                      | \$FFFF            | OFF | ^    | ^    | MHz                              | MHz           | MHz              | Disabled | Х                           | 1    | DNA                                                  |                                                                     |

| OND                          | V                                         | ¢5555             | ON  | V    | V    | 32.768                           | 4.9152        | 2.4576           | B: 11 :  | 1                           | 0    | 9600                                                 | PLL enabled<br>(BCS set)<br>in monitor code                         |

| GND                          | V <sub>DD</sub>                           | \$FFFF            | ON  | X    | X    | kHz                              | MHz           | MHz              | Disabled | Х                           | 1    | DNA                                                  |                                                                     |

| V <sub>DD</sub><br>or<br>GND | V <sub>TST</sub>                          | \$FFFF            | OFF | х    | х    | х                                | _             | _                | Enabled  | Х                           | х    | _                                                    | Enters user<br>mode — will<br>encounter an illegal<br>address reset |

| V <sub>DD</sub><br>or<br>GND | V <sub>DD</sub><br>or<br>V <sub>TST</sub> | Non-blank         | OFF | х    | х    | х                                | _             | _                | Enabled  | Х                           | х    | _                                                    | Enters user mode                                                    |

External clock is derived by a 32.768-kHz crystal or a 9.8304-MHz off-chip oscillator.

PTA0 = 1 if serial communication; PTA0 = X if parallel communication

PTA1 = 0 → serial, PTA1 = 1 → parallel communication for security code entry

DNA = does not apply, X = don't care

| Table 2. Crysta | l Frequency vs. | Baud Rate |

|-----------------|-----------------|-----------|

|-----------------|-----------------|-----------|

| Crystal<br>Frequency (MHz) | Internal Bus<br>Frequency (MHz) | Baud<br>Rate |

|----------------------------|---------------------------------|--------------|

| 4.9152                     | 1.2288                          | 4800         |

| 9.8304                     | 2.4576                          | 9600         |

| 14.7456                    | 3.6864                          | 14,400       |

| 19.6608                    | 4.9152                          | 19,200       |

| 29.4912                    | 7.3728                          | 28,800       |

Figure 3. MC68HC908GR8 MON08 Connections

Figure 4. MC68HC908GR8 Standard Monitor Mode (9.8304 MHz)

Figure 5. MC68HC908GR8 Forced Monitor Mode (9.8304 MHz)

Figure 6. MC68HC908GR8 Forced Monitor Mode (32.768 kHz)

```

🚵 WIN IDE - [HC908GR.PPF] - [c:\pemicro\ics08grz\DEM0GR.ASM]

<u>File Edit Environment Search Window Help</u>

29 科 및

B B B E

•

; Here is the sample application...

RAMStart

EQU $0040

RomStart EQU $E000

VectorStart EQU $FFDC

; This is valid ROM on the GR8

ADC Channel EQU 5t

; Bit mask for interrupt enable bit

ADC ENABLE INT EQU 01000000q

; in the ADC status/control register

$Include 'grregs.inc'

org RamStart

temp_long ds 4

temp_word ds 2

temp_byte ds 1

Timeout1 ds 1 ; Allows three timeout routines to be called each of which Timeout2 ds 1 ; can run for up to ^{\sim} 1/2 second.

Timeout3 ds 1

org RomStart

Init_SCI:

#$03,SCBR

; Baud Rate = 9600

mov

#$40,SCC1

; Enable the SCI peripheral

mov

#$08,SCC2

; Enable the SCI transmitter

rts

* Init_AtoD - Sets up the AtoD clock + turns it on

Assemble Compile File - Hotkey F4

```

Figure 7. P&E's WINIDE Window

Figure 8. P&E's Target and Security Window

Figure 9. P&E's Programmer Window

EB368

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Motorola data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights or the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and Archiver are registered trademarks of Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

#### How to reach us:

USA/EUROPE/Locations Not Listed: Motorola Literature Distribution; P.O. Box 5405, Denver, Colorado 80217. 1-303-675-2140 or 1-800-441-2447

JAPAN: Motorola Japan Ltd.; SPS, Technical Information Center, 3-20-1, Minami-Azabu, Minato-ku, Tokyo 106-8573 Japan. 81-3-3440-3569

ASIA/PACIFIC: Motorola Semiconductors H.K. Ltd.; Silicon Harbour Centre, 2 Dai King Street, Tai Po Industrial Estate, Tai Po, N.T., Hong Kong. 852-26668334

Technical Information Center: 1-800-521-6274

HOME PAGE: http://www.motorola.com/semiconductors/

© Motorola, Inc., 2000