# Minimizing Output Skew Using Ganged Outputs

SCAA032

#### **IMPORTANT NOTICE**

Texas Instruments (TI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

TI warrants performance of its semiconductor products and related software to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Certain applications using semiconductor products may involve potential risks of death, personal injury, or severe property or environmental damage ("Critical Applications").

TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

Inclusion of TI products in such applications is understood to be fully at the risk of the customer. Use of TI products in such applications requires the written approval of an appropriate TI officer. Questions concerning potential risk applications should be directed to TI through a local SC sales office.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards should be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

Copyright © 1994, Texas Instruments Incorporated

# Contents

|         | Title                                                        | Page |

|---------|--------------------------------------------------------------|------|

| Introdu | luction                                                      | 1    |

| Skew I  | Definitions                                                  | 1    |

| Gange   | ed Outputs                                                   | 1    |

| Perform | mance Evaluation                                             | 1    |

| Reliabi | oility                                                       |      |

| Applica | cations                                                      |      |

| Ackno   | owledgment                                                   |      |

|         | List of Illustrations                                        |      |

| Figure  | Title                                                        | Page |

| 1       | Graphics Plot CDC209 V <sub>OH</sub> /I <sub>OH</sub> Curves |      |

| 2       | Graphics Plot CDC209 V <sub>OL</sub> /I <sub>OL</sub> Curves |      |

| 3       | CDC209 Ganged Outputs                                        |      |

| 4       | CDC209 T <sub>PLH</sub> vs C <sub>LOAD</sub>                 |      |

| 5       | CDC209 T <sub>PHL</sub> vs C <sub>LOAD</sub>                 |      |

| 6       | CDC209 Output Waveforms                                      |      |

| 7       | Test Circuit                                                 | 4    |

#### Introduction

The purpose of this application report is to help designers use existing clock-driver products to drive large loads and maintain a minimum amount of skew between outputs of the device. The emphasis of this report will be on using parallel, or ganged, outputs to drive loads.

#### **Skew Definitions**

# Output Skew - tsk(o)

Output skew is defined as the difference in propagation delay of the fastest and slowest paths on a single device that originate at either a single input or multiple simultaneously switched inputs. This parameter is useful when considering the distribution of a clock signal to multiple targets.

# Pulse Skew - t<sub>sk(p)</sub>

Pulse skew is defined as the difference between the propagation delay times  $t_{PLH}$  and  $t_{PHL}$  on the same pin at identical operating conditions. This parameter is useful when considering the output duty cycle characteristics of a device.

# Process Skew - t<sub>sk(pr)</sub>

Process skew is defined as the difference between propagation delay times on any two samples of an integrated circuit at identical operating conditions. This parameter addresses the difference in propagation delay times due to process variations.

#### **Board Skew**

Board skew is introduced into the clock system by unequal trace lengths and loads. It is independent of the skew generated by the clock driver. It is important to keep line lengths equal to minimize board skew.

When measuring propagation delays to determine the parameters  $t_{sk(0)}$ ,  $t_{sk(p)}$ , and  $t_{sk(pr)}$ , the device(s) must be tested under identical operating conditions such as temperature, power supply voltage ( $V_{CC}$ ), output loading, and input edge rates.

## **Ganged Outputs**

As system frequencies increase, the need to minimize skews of clock drivers becomes critical to overall system performance. Existing non-PLL-based clock driver products deliver guaranteed output skews  $(t_{sk(o)})$  in the 500-ps to 1-ns range. It is possible to use these low-skew clock drivers in a way that eliminates the output skew of the device. This can be achieved by using parallel, or ganged, outputs. Two or more outputs ganged (connected to a single transmission line) create a single clock source for all the target devices. Output skew of the clock driver is eliminated, and the drive capability is increased.

#### **Performance Evaluation**

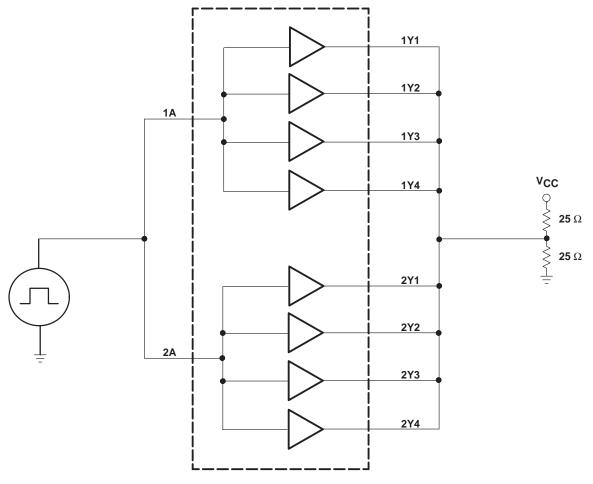

To evaluate the impact of connecting all the outputs of a device to a single transmission line, a test board with traces of equal length to and from the inputs and outputs of the device was constructed. Using traces of equal length prevents board skew from being introduced into the system.

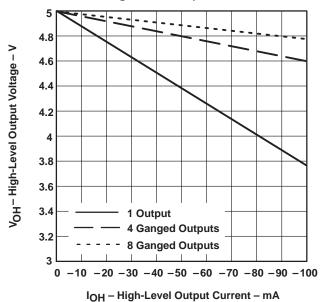

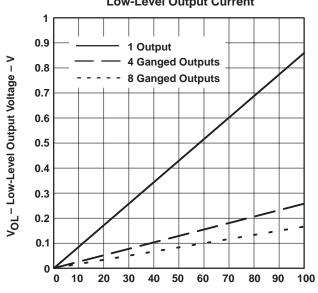

Various tests were performed on the CDC209 and CDC208 to evaluate their changes in performance when one output was used to drive a load versus four or eight ganged outputs. The dc-drive capability increases as more outputs are used to drive the load. Figures 1 and 2 show  $V_{OH}/I_{OH}$  and  $V_{OI}/I_{OL}$  curves displaying the difference between one, four, and eight outputs.

CDC209 High-Level Output Voltage vs High-Level Output Current

Figure 1

## CDC209 Low-Level Output Voltage vs Low-Level Output Current

Figure 2

IOL - Low-Level Output Current - mA

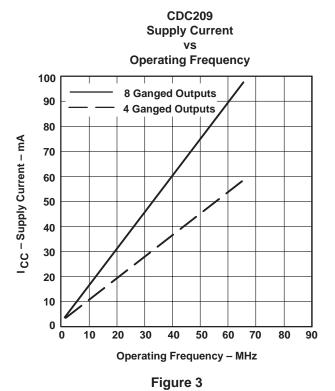

Figure 3 shows the difference in supply current versus operating frequency for four and eight ganged outputs.

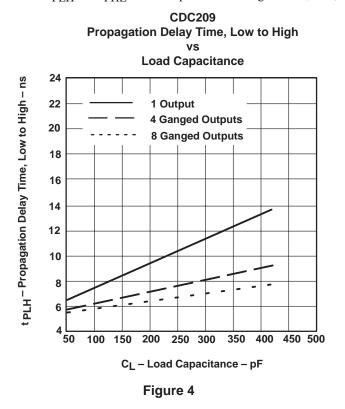

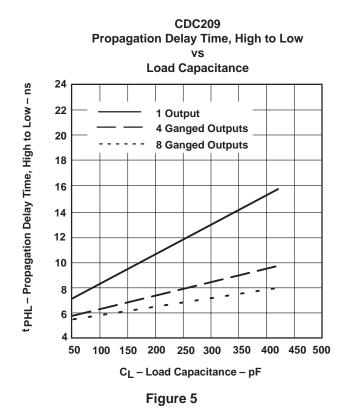

Figures 4 and 5 show the difference in  $t_{PLH}$  and  $t_{PHL}$  versus capacitive loading for one, four, and eight ganged outputs.

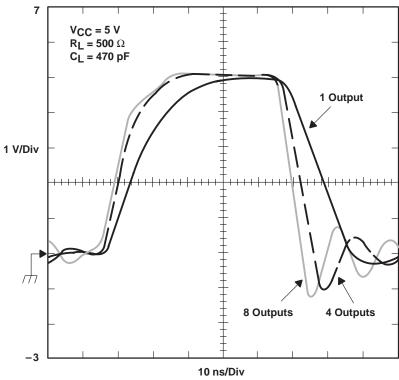

Figure 6 shows the difference in output waveforms of a CDC209 for one, four, and eight ganged outputs driving a 470-pF load in parallel with 500  $\Omega$ .

Figure 6. CDC209 Output Waveforms

## Reliability

A life test of 1000 hours was also performed on 52 devices using the circuit shown in Figure 7. No failures were observed.

NOTES: A. Life test conditions:  $V_{CC} = 7 \text{ V}$ ,  $T_A = 150^{\circ}\text{C}$ , input frequency = 10 MHz

B. It is very important to keep all of the input and output transmission lines equal length to prevent skew from being introduced.

Figure 7. Test Circuit

## **Applications**

One application for ganged outputs is a backplane or bus on a motherboard. A backplane usually requires a single system clock capable of driving multiple plug-in boards. Ganged outputs are very effective at driving capacitive loads distributed along a single transmission line.

Great care must be taken when connecting more than one output to a single transmission line. The length and impedance of the transmission lines from each output to the point of intersection must be matched. The same attention must be given to the input traces if the outputs are driven from multiple inputs. If the lengths and impedances are not matched, a shelf may be visible in the output waveform.

### **Acknowledgment**

The author of this report is Brett Clark.