# Next-Generation BTL/Futurebus Transceivers Allow Single-Sided SMT Manufacturing

SCBA003C March 1997

### **IMPORTANT NOTICE**

Texas Instruments (TI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

TI warrants performance of its semiconductor products and related software to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Certain applications using semiconductor products may involve potential risks of death, personal injury, or severe property or environmental damage ("Critical Applications").

TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

Inclusion of TI products in such applications is understood to be fully at the risk of the customer. Use of TI products in such applications requires the written approval of an appropriate TI officer. Questions concerning potential risk applications should be directed to TI through a local SC sales office.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards should be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

Copyright © 1997, Texas Instruments Incorporated

# **Contents**

|         | Title                                                                                                               | Page |

|---------|---------------------------------------------------------------------------------------------------------------------|------|

| Introdu | uction                                                                                                              | 1    |

| Curren  | at Generation of BTL/Futurebus Transceivers                                                                         | 1    |

| A New   | Generation of BTL/Futurebus Transceivers                                                                            | 5    |

| Summa   | ary                                                                                                                 | 8    |

|         |                                                                                                                     |      |

|         | List of Illustrations                                                                                               |      |

| Figure  | Title                                                                                                               | Page |

| 1       | Comparison of TTL and BTL Switching Standards                                                                       |      |

| 2       | Slew-Rate Control (OEC™) Diagram                                                                                    | 2    |

| 3       | Uncached 64-Bit Futurebus Layout With Texas Instruments Controller Chipset and Today's Most Integrated Transceivers | 3    |

| 4       | Functional Differences Between FB2040 Control Transceiver and FB2031 Address/Data Transceiver                       |      |

| 5       | Cross Section of Thermally Enhanced EIAJ 100-Pin TQFP                                                               | 5    |

| 6       | Functional Circuit Diagram of FB1650                                                                                | 6    |

| 7       | Uncached 64 Rit Futurabus Layout With Tayas Instruments Chinest and FR16vy Transcaivers                             | 7    |

### Introduction

BTL (IEEE 1194.1-1991) and Futurebus designs offer significant performance advantages over conventional TTL backplane implementations, but these advantages come with trade-offs. Switching noise in the form of ground bounce and EMI must be controlled, and proper termination schemes must be employed to ensure signal integrity in this high-speed switching environment. Trade-offs for price in the form of total system solution versus overall system performance are also of concern. This paper begins with the historical perspective on signal-integrity issues addressed by the IEEE and follows with new pioneering bus-interface solutions to help reduce overall BTL or Futurebus system costs and design complexities.

### **Current Generation of BTL/Futurebus Transceivers**

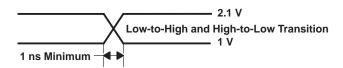

A number of suppliers have developed BTL and Futurebus transceiver solutions that comply with IEEE 1194.1. These devices share the same reduced output swing and tight switching thresholds shown in Figure 1 and a slew-rate control (see Figure 2). The various devices differ considerably in wafer-fab process technology, propagation-delay performance, and other performance metrics (see Table 1).

Figure 1. Comparison of TTL and BTL Switching Standards

Figure 2. Slew-Rate Control (OEC™) Diagram

Table 1 shows an evolutionary progression in bipolar wafer-fab technology and improved propagation-delay performance. Bipolar fab technologies are chosen for this class of device for their high drive capability, low switching noise, and relative ease of designing (relative to pure CMOS) the analog circuitry required to meet the slew-rate control requirement (see Figure 2). Bipolar circuits have the disadvantage of relatively high power dissipation. The heat generated by this high power dissipation, coupled with the large switching currents coming from the bus termination, place a thermal limitation on the numbers of bits that can be integrated into a single, standard integrated-circuit package (typically, only four bits).

Table 1. BTL/Futurebus Transceiver Offering Available Today

| TRANSCEIVER | SUPPLIER    | TECHNOLOGY     | BITS/PACKAGE | t <sub>pd</sub> (ns) |

|-------------|-------------|----------------|--------------|----------------------|

| ALS056/057  | TI, NSC     | 3-μm Bipolar   | 4/8          | 20                   |

| DS3890      | NSC         | 2-μm Bipolar   | 8†           | 15                   |

| DS3896/7    | NSC         | 1.5-μm Bipolar | 4/8          | 12                   |

| DS3893A     | NSC         | 1.2-μm Bipolar | 4            | 7                    |

| FB1650      | TI          | 0.8-μm BiCMOS  | 18           | 7.2                  |

| FB1651      | TI          | 0.8-μm BiCMOS  | 17           | 7.2                  |

| FB1653      | TI          | 0.8-μm BiCMOS  | 17           | 6.6                  |

| FB2032      | TI          | 0.8-μm BiCMOS  | 9            | 8.3                  |

| FB2033A     | TI          | 0.8-μm BiCMOS  | 8            | 5.6                  |

| FB2031      | TI, Philips | 0.8-μm BiCMOS  | 9            | 6.6                  |

| FB2040      | TI, Philips | 0.8-μm BiCMOS  | 8            | 6.5                  |

| FB2041A     | TI, Philips | 0.8-μm BiCMOS  | 7            | 5.6                  |

<sup>†</sup> Unidirectional driver only; not a true bidirectional transceiver

The newer class of BiCMOS transceivers employs a bipolar output structure to achieve the desired drive, noise, and slew-rate control of previous-generation products. They also offer higher performance, much lower power dissipation, and take the next step toward higher integration.

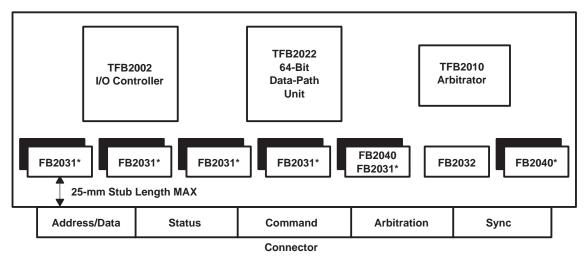

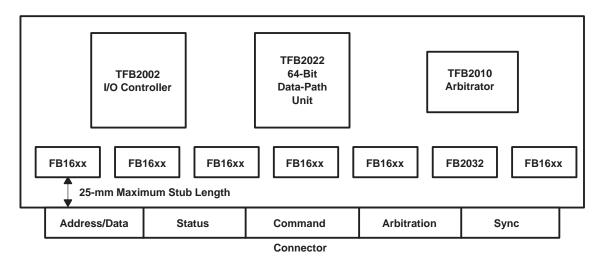

Futurebus adds an additional constraint to board layout by mandating that all compliant cards have a maximum stub length of 25 mm to reduce loading and minimize reflections. This is also a wise rule of thumb for non-BTL/Futurebus designs. As data paths have increased in width from 32 to 64 bits (128 bits in the future), this stub-length requirement has forced system designers to wrestle with the manufacturing problems of double-sided surface mounting of the transceivers on boards as large as 12 Standard Units (12SU). Even with the relatively dense packaging of today's fastest and most integrated transceivers, this can be a formidable design problem that adds significantly to the overall manufacturing cost of a board (see Figure 3).

NOTE: The second-part type descriptor (\*) indicates that a second transceiver is mounted on the opposite side of the board.

Figure 3. Uncached 64-Bit Futurebus Layout With Texas Instruments Controller Chipset and Today's Most Integrated Transceivers

Another problem with the present generation of transceivers is the purchasing requirement for multiple transceiver types. Continuing with the above example, the common 64-bit uncached solution requires three different transceiver types for a complete distributed arbitration Futurebus implementation (see Table 2).

Table 2. Transceiver Descriptions for 64-Bit Uncached Futurebus Boards

Using FB20xx Series Transceivers

| DEVICE              | DESCRIPTION                                         | QUANTITY<br>PER<br>BOARD |

|---------------------|-----------------------------------------------------|--------------------------|

| FB2031              | 9-Bit Data/Address Transceiver With Clock and Latch | 9                        |

| FB2032 <sup>†</sup> | Arbitration Contest Transceiver                     | 1                        |

| FB2040              | 8-Bit Status/Sync Transceiver With Split TTL I/O    | 3                        |

|                     | 13                                                  |                          |

<sup>†</sup> Optional for distributed arbitration only

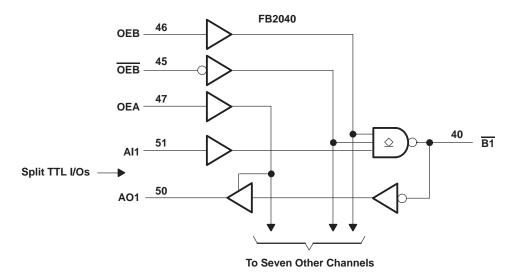

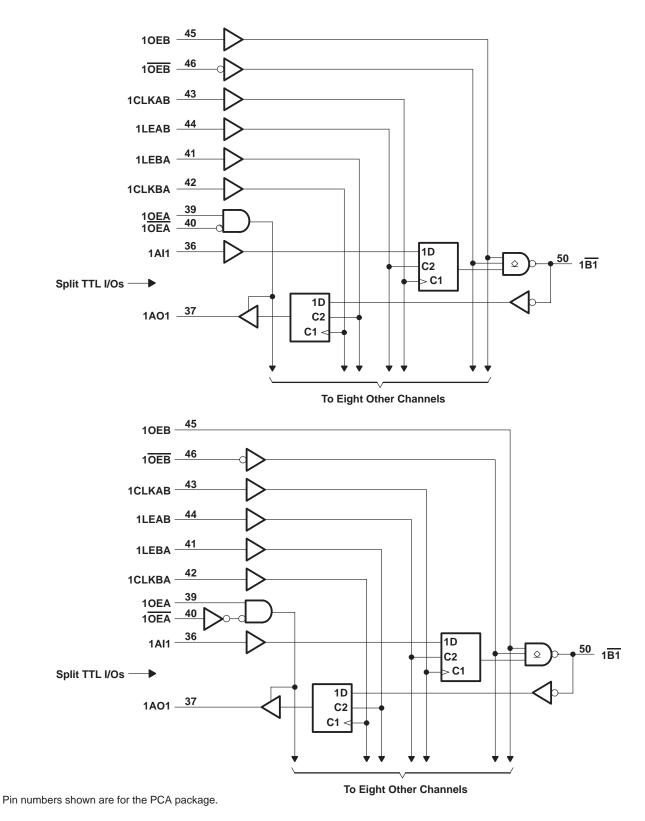

These transceivers were designed quite differently from one another due to the specific functions they perform in the system (data/address, sync, arbitration, status, or command). Figure 4 highlights the functional differences between the FB2040 (status and sync transceiver) and the FB2031 (address/data transceiver). The main distinctions are the universal storage modes (transparent, latched, or clocked) of the FB2031 and the separate, or split, TTL I/O pins of the FB2040. As previously noted, until recently, efforts to develop any sort of true universal BTL/Futurebus transceiver have not been practical due to the absence of a viable, high-power, fine-pitch package with more than 56 pins.

LCA \_\_\_\_\_ FB2031 SEL0 \_\_\_\_\_\_\_ OEB -1D OEA -C1 B1 1D MUX 1D MUX C1 1D C1 <

Pin numbers shown are for the RC package.

Figure 4. Functional Differences Between FB2040 Control Transceiver and FB2031 Address/Data Transceiver

To Eight Other Channels

### A New Generation of BTL/Futurebus Transceivers

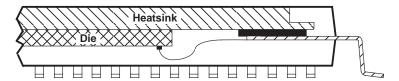

In response to the need for single-sided surface mounting and simplified transceiver architectures, Texas Instruments has developed both a high-power package and a series of 18-channel BTL/Futurebus universal bus transceivers (UBT<sup>TM</sup>). These new devices, designated as the FB16xx series, are packaged in a high-power version of the EIAJ standard 100-pin TQFP package (0.5-mm lead pitch). A package cross section, as shown in Figure 5, reveals a metal heatsink that facilitates the excellent thermal performance of the package. Refer to *Thermal Characteristics of SLL Packages and Devices*, literature number SCZA005, for  $\theta_{JA}$  and reliability issues.

Figure 5. Cross Section of Thermally Enhanced EIAJ 100-Pin TQFP

The FB16xx series devices are designed with both the universal data-storage capabilities of the FB2031 address/data transceiver and the separate TTL I/O of the FB2040 control transceiver. This series of devices can be configured as two independent 9-channel transceivers (see Figure 6) or one coherent 18-channel transceiver.

Figure 6. Functional Circuit Diagram of FB1650

This flexible design approach eliminates the need for double-sided surface mounting, along with all of the associated manufacturing costs, and still meets the IEEE 896.2-1991 25-mm maximum-stub-length requirement (see Figure 7).

NOTE: There is no double-sided SMT requirement.

Figure 7. Uncached 64-Bit Futurebus Layout With Texas Instruments Chipset and FB16xx Transceivers

In addition, the 18-channel architecture lends itself naturally to reduced pin-to-pin signal skew. Advanced BiCMOS circuit design techniques have improved propagation-delay performance over the previous generation of BiCMOS transceivers. Table 3 shows a transceiver description for the same 64-bit uncached Futurebus example considered previously (see Table 2).

Table 3. Transceiver Descriptions for 64-Bit Uncached Futurebus Board Using FB16xx Series Transceivers

| DEVICE  | DESCRIPTION                           | QUANTITY<br>PER<br>BOARD |

|---------|---------------------------------------|--------------------------|

| FB16xx  | 18-Bit TTL/BTL UBT With Split TTL I/O | 6                        |

| FB2032† | Arbitration Contest Transceiver       | 1                        |

|         | 7                                     |                          |

<sup>†</sup> Optional for distributed arbitration only

This is nearly a 50% reduction in component count and approximately 15% in cost savings on the transceivers alone. Significant savings (tens of dollars per board) in manufacturing costs also are realized by moving to single-sided SMT manufacturing. Other members of the FB16xx family include system clock-distribution features that lend themselves to more specific end-system applications such as ATM hubs and routers (see Table 4).

Table 4. Transceiver Descriptions for Other Members of the FB16xx Series

| DEVICE | DESCRIPTION                                                            |

|--------|------------------------------------------------------------------------|

| FB1650 | 18-Bit TTL/BTL UBT With Split TTL I/O                                  |

| FB1651 | 17-Channel UBT With Separate Buffered and Delayed Clock Bit            |

| FB1653 | 17-Channel UBT With Separate Buffered Clock Bit (variable delay lines) |

## **Summary**

The high-speed data-communication requirements of today's fastest board-level computers and telecommunications and network switching equipments can be met with BTL- and Futurebus-compatible transceivers and switching levels. Stub-length constraints and ever-increasing data-path widths have made it difficult to control signal integrity and manufacturing and procurement costs in these high-performance systems. The next generation of 18-channel BTL/Futurebus universal bus transceivers meets this market need by facilitating low-cost single-sided surface-mount manufacturing, and single-device-type procurement, characterization, qualification, and specification.