# TMS3637 Remote Control Transmitter/Receiver Data Manual

SCTS037B JUNE 1997

#### IMPORTANT NOTICE

Texas Instruments (TI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

TI warrants performance of its semiconductor products and related software to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Certain applications using semiconductor products may involve potential risks of death, personal injury, or severe property or environmental damage ("Critical Applications").

TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

Inclusion of TI products in such applications is understood to be fully at the risk of the customer. Use of TI products in such applications requires the written approval of an appropriate TI officer. Questions concerning potential risk applications should be directed to TI through a local SC sales office.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards should be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

### **Contents**

|   |                          | Title                                                                                                           | Page              |

|---|--------------------------|-----------------------------------------------------------------------------------------------------------------|-------------------|

| 1 | 1.1<br>1.2<br>1.3<br>1.4 | Features Functional Block Diagram Terminal Assignments Terminal Functions                                       | 1–1<br>1–2<br>1–2 |

| 2 | 2.1<br>2.2<br>2.3        | Absolute Maximum Ratings Over Operating Free-Air Temperature Range Recommended Operating Conditions             | 2–1<br>2–1        |

|   |                          | and Operating Free-Air Temperature  2.3.1 Signal Interface  2.3.2 Amplifier                                     | 2–2               |

|   |                          | <ul><li>2.3.3 Internal Oscillator</li><li>2.3.4 Power-On Reset</li><li>2.3.5 Write/Erase Endurance</li></ul>    | 2–2               |

|   | 2.4                      | Timing Requirements Over Recommended Ranges of Supply Voltages and Free-Air Temperature                         | 2–3<br>2–3<br>2–3 |

|   | 2.5                      | Switching Characteristics Over Recommended Ranges of Supply Voltages and Free-Air Temperature                   | 2–3<br>2–3        |

| 3 | Para                     | ameter Measurement Information                                                                                  | 3–1               |

| 4 | Турі                     | cal Characteristics                                                                                             | 4–1               |

| 5 | <b>Prin</b> 5.1 5.2      | ciples of Operation  Power-On Reset  EEPROM Memory (31 Bits)  5.2.1 Program Read Mode  5.2.2 Program Write Mode | 5–1<br>5–1<br>5–1 |

|   | 5.3                      | Internal Oscillator Operation for Transmit and Receive Modes Setting Frequency                                  |                   |

|   | 5.4                      | Internal Oscillator Operation for Transmit and Receive Modes Sampling Frequency                                 |                   |

|   | 5.5<br>5.6               | External Oscillator Operation for Transmit and Receive Modes                                                    |                   |

|   | 5.7  |          | Amplifier/Comparator Test Mode                                   |        |

|---|------|----------|------------------------------------------------------------------|--------|

|   | 5.8  |          | nd Configuration Overview                                        |        |

|   | 5.9  |          | itter Configurations                                             |        |

|   |      |          | Continuous Transmitter (CC = 1)                                  |        |

|   |      |          | Friggered Transmitter (CC = 0, CI = 1)                           |        |

|   |      |          | Periodic Transmitter (CC = 0, CI = 0)                            |        |

|   | 5.10 |          | itter Modes                                                      |        |

|   |      | 5.10.1   | Normal Mode (CB = 1)                                             |        |

|   |      | 5.10.2   | Modulated Mode (CB = 0)                                          |        |

|   |      | 5.10.3   | Code-Train Mode (CD, CE)                                         |        |

|   | 5.11 |          | er Configurations                                                |        |

|   |      | 5.11.1   | Valid Transmission Receiver (CG = 1, CH = 0)                     |        |

|   |      | 5.11.2   | Train Receiver (CG = 1, CH = 1, CD, CE)                          |        |

|   |      | 5.11.3   | Q-State Receiver (CG = 0, CH = 0, CD, CE)                        | . 5–12 |

|   | 5.12 | Receiv   | er Modes                                                         |        |

|   |      | 5.12.1   | Normal Mode (CB = 1)                                             | . 5–13 |

|   |      | 5.12.2   | Modulated Mode (CB = 0)                                          |        |

|   |      | 5.12.3   | Analog Mode (CF = 0)                                             |        |

|   |      | 5.12.4   | Logic Mode (CF = 1)                                              |        |

|   |      | 5.12.5   | Noninverting Mode ( $CI = 0$ ) or Inverting Mode ( $CI = 1$ )    | . 5–14 |

| 6 | App  | lication | Information                                                      | 6–1    |

|   | 6.1  |          | I Applications                                                   |        |

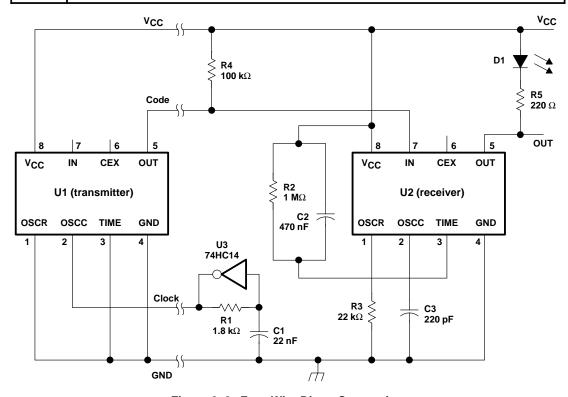

|   | 6.2  |          | Vired Connection of Transmitter and Receiver                     |        |

|   |      | 6.2.1    | Two-Wire Direct Connection                                       | 6–1    |

|   |      | 6.2.2    | Four-Wire Direct Connection                                      | 6–3    |

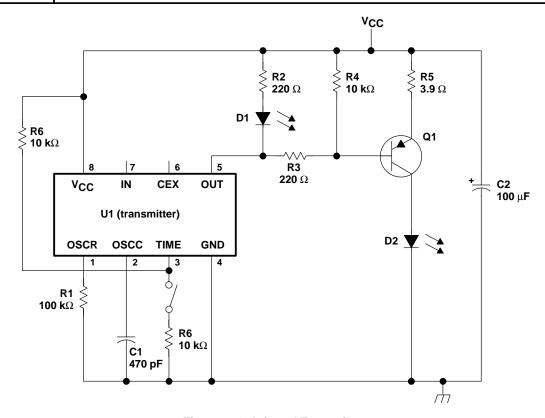

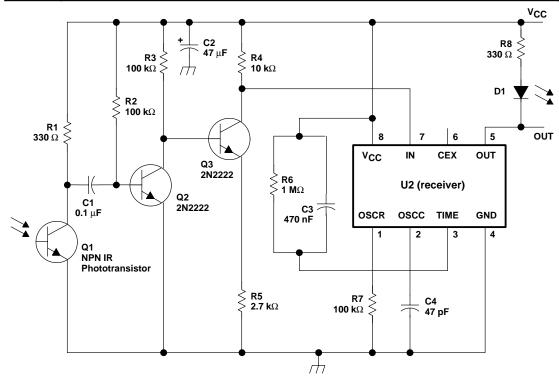

|   | 6.3  | Infrared | Coupling of Transmitter/Receiver – Normal Transmission Mode      | 6–5    |

|   | 6.4  | Infrared | Coupling of Transmitter/Receiver – Modulated Transmission Mode . | 6–8    |

|   | 6.5  | Radio F  | requency (RF) Coupling of Transmitter and Receiver               | . 6–10 |

|   | 6.6  |          | eiver and Decoder                                                |        |

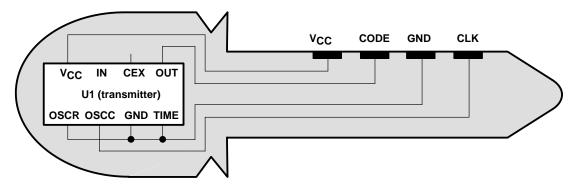

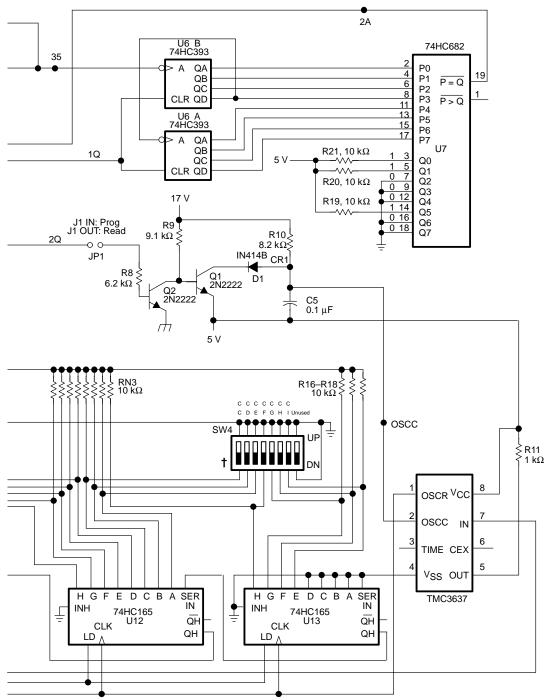

|   | 6.7  |          | mming Station                                                    |        |

|   | 6.8  |          | 37 Programming Station Parts Lists                               |        |

|   | 6.9  |          | 37 Edge-Connector Pinout                                         |        |

# **List of Figures**

| Figure     | Title                                                                  | Page |

|------------|------------------------------------------------------------------------|------|

| 3–1<br>3–2 | Normal Transmission – External Clock  VTR Generation  FERROM Read Mode | 3–1  |

| 3–3<br>3–4 | EEPROM Read Mode EEPROM Write Mode                                     | _    |

| 3–4<br>3–5 | Data In Setup and Hold Times                                           |      |

| 3–6        | Normal Transmission – Internal Clock                                   |      |

| 3–7        | Modulated Transmission – Internal Clock                                |      |

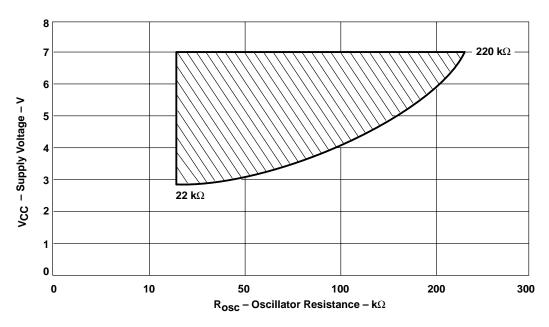

| 4–1        | Oscillator Resistance Versus Supply Voltage                            | 4–1  |

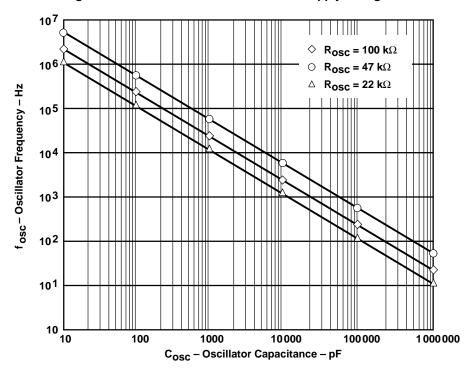

| 4–2        | Oscillator Frequency Versus Oscillator Capacitance                     |      |

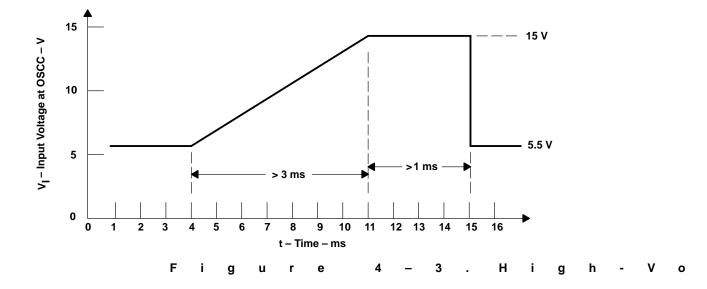

| 4–3        | High-Voltage Programming Pulse                                         | 4–2  |

| 5–1        | EEPROM Read Mode                                                       |      |

| 5–2        | EEPROM Write Mode                                                      |      |

| 5–3        | Amplifier/Comparator Schematic                                         |      |

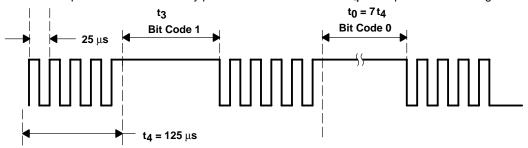

| 5–4        | OUT Waveform in Normal Transmission                                    |      |

| 5–5        | OUT Waveform in Modulated Mode                                         |      |

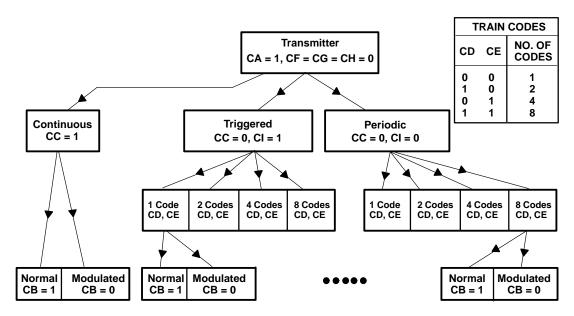

| 5–6        | Transmitter Configurations                                             |      |

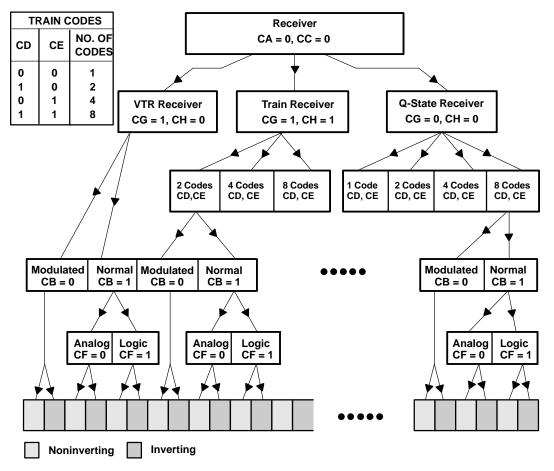

| 5–7        | Receiver Configurations                                                | 5–13 |

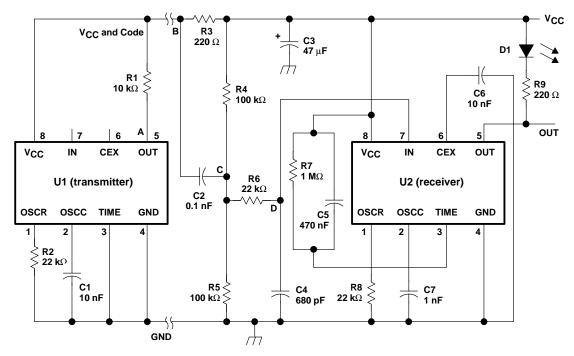

| 6–1        | Two-Wire Direct Connection                                             | 6–3  |

| 6–2        | Four-Wire Direct Connection                                            | 6–4  |

| 6–3        | Four-Wire Direct Connection Key                                        |      |

| 6–4        | Infrared Transmitter                                                   |      |

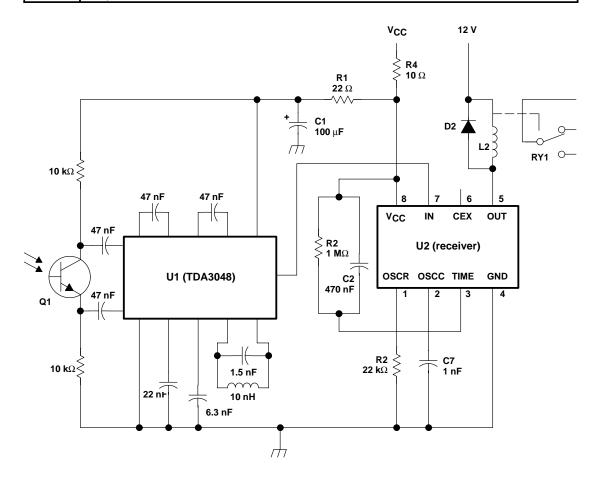

| 6–5        | Infrared Receiver                                                      |      |

| 6–6        | Infrared Modulated Receiver                                            |      |

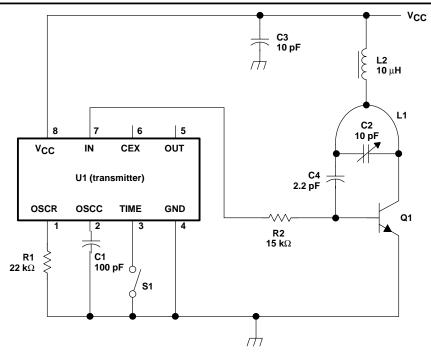

| 6–7        | Radio Frequency Transmitter                                            |      |

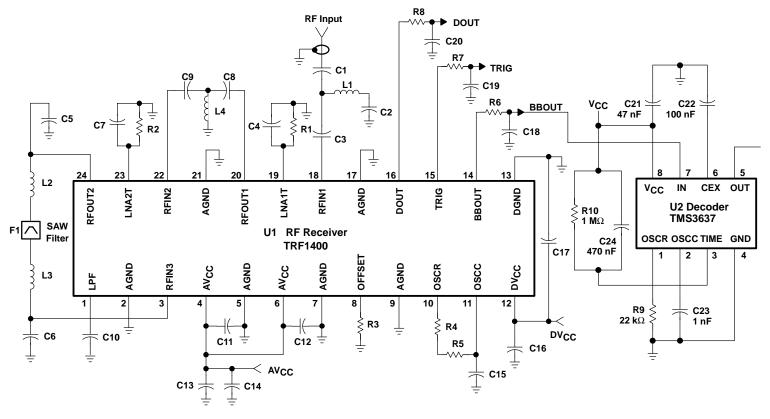

| 6–8        | TRF1400 RF Receiver and TMS3637 Decoder Circuit                        |      |

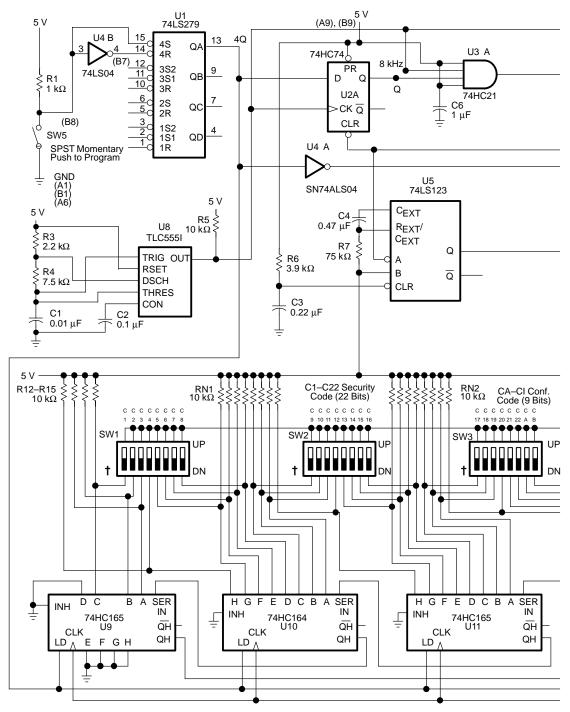

| 6–9        | Programming Station                                                    | 6–16 |

### **List of Tables**

| Table | Title                                                               | Page |

|-------|---------------------------------------------------------------------|------|

| 5–1   | Mode and Test Configuration                                         | 5–5  |

| 5–2   | Transmitter Modes                                                   |      |

| 5–3   | Receiver Modes                                                      | 5–7  |

| 5–4   | Amplifier Test, Program, and Read Modes                             | 5–7  |

| 5–5   | Code-Train Modes                                                    | 5–10 |

| 5–6   | Transmitter/Receiver Compatibility                                  | 5–11 |

| 5–7   | Bits CD and CE in Train Receiver                                    | 5–12 |

| 5–8   | Bits CD and CE in Q-State Receiver                                  | 5–12 |

| 6–1   | Two-Wire Direct Connection                                          | 6–2  |

| 6–2   | Four-Wire Direct Connection                                         | 6–4  |

| 6–3   | Infrared Transmitter Component Functions (Normal Transmission Mode) | 6–6  |

| 6–4   | Infrared Receiver Component Functions (Normal Transmission Mode)    | 6–7  |

| 6–5   | Infrared Receiver Component Functions (Modulated Tranmission Mode)  |      |

| 6–6   | RF Transmitter Component Functions                                  | 6–10 |

| 6–7   | TRF1400 RF Receiver and TCM3637 Decoder Parts List                  |      |

|       | (for 300 MHz operation)                                             | 6–13 |

| 6–8   | TMS3637 Programming Station Part List                               | 6–18 |

| 6–9   | Edge Connector Pinout                                               | 6–19 |

### 1 Introduction

The TMS3637 is a versatile 3-V to 6-V remote control transmitter/receiver in a small package that requires no external dual-in-line package (DIP) switches on the system circuit board. The device can be easily set for one of many transmit/receive configurations using configuration codes along with the desired security code, both of which are user programmable. When used as a transmitter, the device encodes the stored security code, transmits it to the remote receiver using any transmission media such as direct wiring, infrared, or radio frequency. When configured as a receiver, the TMS3637 continuously monitors and decodes the transmitted security code (at speeds that can exceed 90 kHz) and activates the output of the device when a match with its internally stored code has been found. All programmed data is stored in nonvolatile EEPROM memory. With more than four million codes alterable only with a programming station, the TMS3637 is well suited for remote control system designs that require high security and accuracy. Schematics of the programming station and other suggested circuits are included in this data manual.

In addition to the device configuration and security code capabilities, the TMS3637 includes several internal features that normally require additional circuitry in a system design. These include an amplifier/comparator for detection and shaping of input signals as low as several millivolts (typically used when an RF link is employed) and an internal oscillator (used to clock the transmitted or received security code).

The TMS3637 is characterized for operation from −25°C to 85°C.

#### 1.1 Features

- Data Encoder (Transmitter) or Data Decoder (Receiver) for Use in Remote Control Applications

- High Security

- 4,194,304 Unique Codes Available

- Codes Stored in Nonvolatile Memory (EEPROM)

- Codes Alterable Only With a Programming Station That Ensures No Security Code Duplications

- Versatile

- 48 Possible Configurations as a Receiver

- 18 Possible Configurations as a Transmitter

- Single, Multiple, or Continuous Cycling Transmission

- Easy Circuit Interface With Various Transmission Media

- Direct Wired

- Infrared

- Radio Frequency

- Minimal Board Space Required: 8-Pin (D or P) Package and No DIP Switches

- Internal On-Chip Oscillator Included, No External Clock Required

- CMOS 2-µm Process Used for Very Low-Power Consumption and 3-V to 6-V Supply Voltage

- Well Suited for All Applications Requiring Remote-Control Operation

- Garage Door Openers

- Security Systems for Auto and Home

- Electronic Keys

- Consumer Electronics

- Cable Decoder Boxes

- Industrial Controls Requiring Precise Activation of Equipment

- Electronic Serial Number (ESN) Device Identification

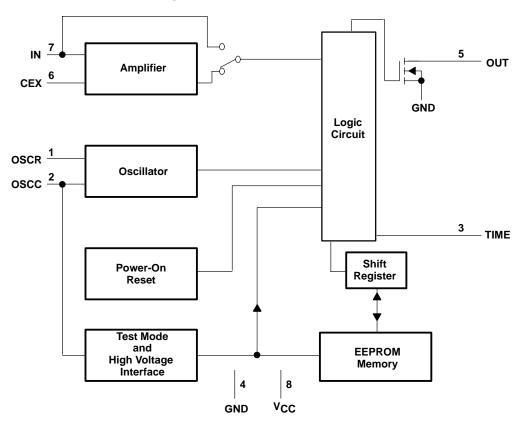

### 1.2 Functional Block Diagram

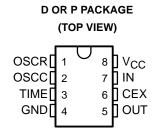

### 1.3 Terminal Assignments

### 1.4 Terminal Functions

| TERMINAL |     |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

|----------|-----|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| NAME     | NO. | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| CEX      | 6   | I   | Capacitor external. CEX is used for gain control of the internal analog amplifier. An external capacitor connected from CEX to GND determines the gain of the amplifier. If the internal amplifier is set for unity gain or the device is not used as a receiver, CEX is left unconnected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| GND      | 4   |     | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| IN       | 7   | I/O | Depending on the device configuration, IN provides inverted OUT data, is used as a receiver input, or is used to enter data during programming.  - When the device is configured as a transmitter, IN provides the complement of the OUT data stream and is considered to be noninverted. IN provides its own internal pullup, so no external pullup is required when IN is used to transmit the data. It is cleared to 0 in standby.  - When the device is configured as a receiver, IN is used to receive the code.  - When the device is in the program mode, IN is used to enter serial data into the device shift registers that load into the EEPROM memory.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| oscc     | 2   | I/O | Oscillator capacitor. Depending on the configuration, OSCC is used for external transmit/receive clock input, control of the internal oscillator, to place the device into program mode, input for a high-voltage EEPROM programming pulse, or the internal analog amplifier in the test mode.  - When the device is used as a transmitter or receiver using an external clock, the external clock is connected directly to OSCC. (OSCR must be held low to use an external clock.)  - When the device is used as a transmitter or receiver and the internal oscillator is used, a capacitor from OSCC to GND and a resistor from OSCR to GND determines the free-running internal oscillator frequency. In addition, the internal oscillator triangular waveform can be seen at OSCC in this configuration.  - When the device is in the data-loading phase of the programming mode, OSCC must be held at V <sub>CC</sub> + 0.5 V.  - After the device has been loaded with data in the programming mode, the internal registers transfer the data to the EEPROM permanently by applying a high-voltage programming pulse to OSCC.  - When OSCC is held at V <sub>CC</sub> + 0.5 V and three or more low pulses are applied to OSCR, the device is in the test mode and the output of the internal analog amplifier can be measured at TIME. |  |  |  |  |

| OSCR     | 1   | Ι   | Oscillator resistor. Depending on the configuration, OSCR is used as an external program/ read clock input or to control the internal clock frequency.  — When the device is in the program/read mode, OSCR is connected to an external clock.  — When the device is in the transmit or receive mode, a resistor connected from OSCR to GND (along with a capacitor from OSCC to GND) determines the frequency of the internal clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| OUT      | 5   | 0   | OUT is an open-drain output. For that reason, it is necessary to connect a pullup resistor to OUT. Depending on the configuration, OUT provides transmit data, acts as the output for the receiver, or provides the serial output of the stored data in memory during the program and read modes.  - When the device is configured as a transmitter, the transmitted data is seen at OUT and is in a 3-state output mode during standby (OUT is floating). While transmitting, the data from OUT is considered inverted.  - When the device is configured as a valid transmission receiver (VTR) receiver, OUT provides a VTR pulse and goes low in the standby mode.  - When the device is configured as a Q-state receiver, OUT toggles high and low each time a valid code is received.  - During the program mode, OUT provides the current data from the EEPROM memory when the new data is clocked into the device.                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

### 1.4 Terminal Functions (Continued)

|                      | Terminal Lunctions (Continued) |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

|----------------------|--------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| TERMINAL<br>NAME NO. |                                | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| TIME                 | 3                              | I/O | Depending on the configuration, TIME is used for measuring the internal analog-amplifier output in the device test mode, putting the device into the transmit mode, or controlling an internal clock oscillator for various transmitter and receiver configurations.  - When OSCC is held at V <sub>CC</sub> + 0.5 V and three or more low pulses are applied to OSCR, the device is in the test mode and the output of the internal analog amplifier can be measured at TIME.  - When the device is configured as a continuous transmitter, an internal pullup is connected to TIME. If TIME is then forced low, the device transmits codes for the duration that TIME is held low. (TIME must be connected to an external pullup.)  - When the device is configured as a triggered transmitter and if TIME is then forced low, the device transmits one code or a code train. (TIME must be connected to an external pullup.)  - When the device is configured as a periodic transmitter, connect an external resistor and capacitor between TIME and V <sub>CC</sub> to transmit code after each RC time constant has expired.  - When the device is configured as a VTR, TIME must be held high to receive codes. The device produces a VTR pulse on OUT after confirmation of a correct received code. Connecting a parallel resistor and capacitor between TIME and V <sub>CC</sub> lengthens the output pulse (VTR) duration.  - Configured as a train receiver, connect an external parallel resistor and capacitor between TIME and V <sub>CC</sub> , which are used to set the length of time the device is looking for two, four, or eight correct received codes to output a valid VTR pulse on OUT.  - Configured as a Q-state receiver, TIME has the same function as the VTR receiver above, except the detection of the correct code causes OUT to toggle between the low and high states. |  |  |

| Vcc                  | 8                              |     | 5-V supply voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

### 2 Specifications

# 2.1 Absolute Maximum Ratings Over Operating Free-Air Temperature Range (Unless Otherwise Noted)<sup>†</sup>

| Supply voltage range, V <sub>CC</sub> (see Note 1)    | 0.6 V to 7 V          |

|-------------------------------------------------------|-----------------------|

| Input voltage range (except OSCC), V <sub>I</sub> 0.6 | V to $V_{CC}$ + 0.5 V |

| Input voltage range, OSCC, V <sub>I</sub>             | 0.6 V to 15 V         |

| Output voltage range, OUT, VO                         | 0.6 V to 15 V         |

| Operating free-air temperature range, T <sub>A</sub>  | –25°C to 85°C         |

| Storage temperature range, T <sub>stq</sub>           | . −65°C to 150°C      |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTE 1: Voltage values are with respect to GND.

### 2.2 Recommended Operating Conditions

|                                                                                                            | MIN                  | NOM                                       | MAX                                                | UNIT |

|------------------------------------------------------------------------------------------------------------|----------------------|-------------------------------------------|----------------------------------------------------|------|

| Supply voltage, V <sub>CC</sub>                                                                            | 3                    |                                           | 6                                                  | V    |

| High-level input voltage, VIH                                                                              | V <sub>CC</sub> -0.5 |                                           | VCC                                                | V    |

| Low-level input voltage, $V_{\text{IL}}$                                                                   | 0                    |                                           | 0.5                                                | V    |

| Operating free-air temperature, TA                                                                         | -25                  |                                           | 85                                                 | °C   |

| Receiver supply current, analog, ICC(an)                                                                   |                      |                                           | 2                                                  | mA   |

| Receiver supply current, digital, ICC(dig)                                                                 |                      |                                           | 200                                                | μΑ   |

| Transmitter supply current, standby, ICC(stdby)                                                            |                      |                                           | 13                                                 | μΑ   |

| Transmitter supply current, code transmission,                                                             |                      |                                           | 260                                                | μΑ   |

| ICC(code)                                                                                                  |                      |                                           |                                                    |      |

| Programming current at OSCC, IOSCC                                                                         |                      |                                           | 100                                                | μΑ   |

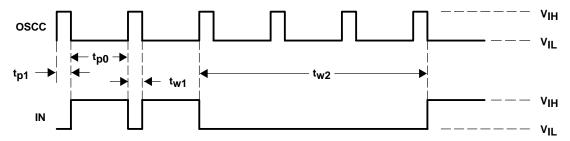

| Oscillating period, t <sub>p0</sub> + t <sub>p1</sub> (see Figure 3–1)                                     | 10                   | 1/(f <sub>OSC</sub> )                     | 200                                                | μs   |

| Pulse duration, logic 1 bit, t <sub>W1</sub> (see Figure 3–1)                                              | 5                    | <sup>t</sup> p1                           | 100                                                | μs   |

| Pulse duration, logic 0 bit, t <sub>w2</sub> (see Figure 3–1)                                              | 35                   | 3 x t <sub>p0</sub> + 4 x t <sub>p1</sub> | 700                                                | μs   |

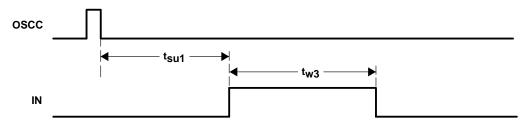

| Setup time, transmitter/receiver external clock on OSCC↓ and before IN↑, t <sub>Su1</sub> (see Figure 3–2) | 152                  | 19 × t <sub>W1</sub><br>(receiver)        |                                                    | μs   |

| Pulse duration, IN high, t <sub>w3</sub> (see Figure 3–2)                                                  | 48                   | 6 × t <sub>W1</sub><br>(receiver)         | R <sub>TIME</sub> × C <sub>TIME</sub> (see Note 2) | μs   |

NOTES: 2. RTIME is the value of the pullup resistor on TIME and CTIME is the value of the capacitor in parallel with RTIME. CTIME should not exceed 3 µF.

# 2.3 Electrical Characteristics Over Recommended Ranges of Supply Voltage and Operating Free-Air Temperature (unless otherwise noted)

### 2.3.1 Signal Interface

|     | PARAMETER                       | TEST CONDITIONS              | MIN                  | TYP | MAX | UNIT |

|-----|---------------------------------|------------------------------|----------------------|-----|-----|------|

| VOL | Low-level output voltage, OUT   | $I_{OL} < 5 \text{ mA}$      | 0.5                  |     |     | V    |

|     | Low-level output voltage, OSCC  |                              | 0.6                  |     | 0.7 | V    |

| Vон | High-level output voltage, OUT  | I <sub>OH</sub> < 5 mA       | V <sub>CC</sub> -0.5 |     |     | V    |

|     | High-level output voltage, OSCC |                              | 1.2                  |     | 1.6 | V    |

| lį  | Input current, IN               | V <sub>I</sub> = 0 V to 6 V  |                      |     | ±10 | μΑ   |

| IO  | Output current, OUT             | $V_0 = 0 V \text{ to } 12 V$ |                      |     | ±10 | μΑ   |

| Ci  | Input capacitance               |                              |                      | 10  |     | pF   |

| Со  | Output capacitance              |                              |                      | 5   | ·   | pF   |

### 2.3.2 Amplifier

|                    | PARAMETER                           | TEST CONDITIONS                                 | MIN | TYP | MAX  | UNIT |

|--------------------|-------------------------------------|-------------------------------------------------|-----|-----|------|------|

| V <sub>I(PP)</sub> | Peak-to-peak input voltage          |                                                 | 3   |     |      | mV   |

| V <sub>N(PP)</sub> | External peak-to-peak noise voltage |                                                 |     |     | 1    | mV   |

| VO                 | Output voltage, TIME                |                                                 | VOL |     | VOH  | V    |

| В                  | Bandwidth                           | $V_I = 3 \text{ mV}$                            |     |     | 15   | kHz  |

|                    |                                     | V <sub>I</sub> = 100 mV <sub>peak</sub> to peak |     |     | 500  |      |

|                    |                                     | V <sub>I</sub> = 200 mV <sub>peak</sub> to peak |     |     | 1000 |      |

| A <sub>V</sub>     | Flatband gain                       | CEX (nF) > 900/f <sub>OSC</sub> (kHz)           |     | 200 |      | V/V  |

|                    |                                     | CEX not connected                               |     | 1   |      |      |

### 2.3.3 Internal Oscillator (see Note 3)

|                  | PARAMETER                                        | MIN                 | TYP                 | MAX                  | UNIT |

|------------------|--------------------------------------------------|---------------------|---------------------|----------------------|------|

| f <sub>RX</sub>  | Receiver frequency                               | 10                  |                     | 500                  | kHz  |

| f <sub>T</sub> X | Transmitter frequency                            | f <sub>RX</sub> /10 | f <sub>RX</sub> /10 | f <sub>RX</sub> /5.5 | kHz  |

|                  | Frequency spread (temperature, V <sub>CC</sub> ) |                     |                     | ± 20%                |      |

NOTE 3: Typical values are recommended whenever possible.

### 2.3.4 Power-On Reset

| PARAMETER                                                | MIN | MAX | UNIT |

|----------------------------------------------------------|-----|-----|------|

| V <sub>CC</sub> level required to trigger power-on reset |     | 2.7 | V    |

| Power-on reset duration                                  |     | 40  | ms   |

### 2.3.5 Write/Erase Endurance

| PARAMETER                | MIN | TYP   | MAX | UNIT |

|--------------------------|-----|-------|-----|------|

| Number of program cycles | 20  | 10000 |     |      |

# 2.4 Timing Requirements Over Recommended Ranges of Supply Voltages and Free-Air Temperature

### 2.4.1 Abort/Retry

|                                                                             | MIN | NOM                               | MAX |  |  |

|-----------------------------------------------------------------------------|-----|-----------------------------------|-----|--|--|

| Time between consecutive codes                                              |     | 46 x t <sub>W</sub> (transmitter) |     |  |  |

| Time out for high-level bit to abort the code 3 x t <sub>W</sub> (receiver) |     |                                   |     |  |  |

| Time out for low-level bit to abort the code                                |     | 25 x t <sub>W</sub> (receiver)    |     |  |  |

| Time between aborted code and reading of new code                           |     | 3 x t <sub>W</sub> (receiver)     |     |  |  |

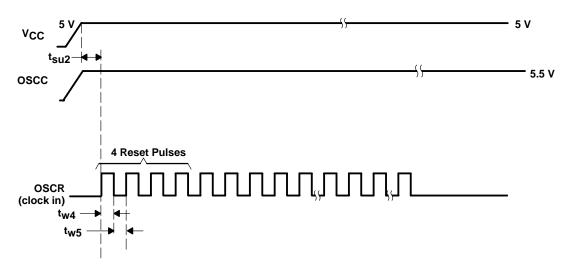

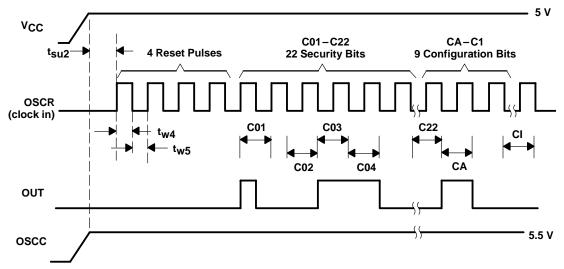

### 2.4.2 EEPROM Read Mode (see Figure 3–3)

|                  |                                                 | MIN | MAX | UNIT |

|------------------|-------------------------------------------------|-----|-----|------|

| t <sub>su2</sub> | Setup time, OSCR high after $V_{CC}$ $\uparrow$ | 50  |     | ms   |

| t <sub>w4</sub>  | Pulse width, OSCR high                          | 10  |     | μs   |

| t <sub>w5</sub>  | Pulse width, OSCR low                           | 10  |     | μs   |

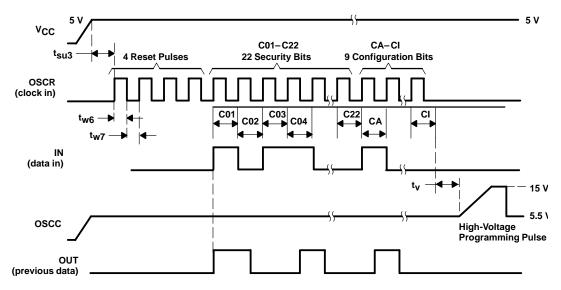

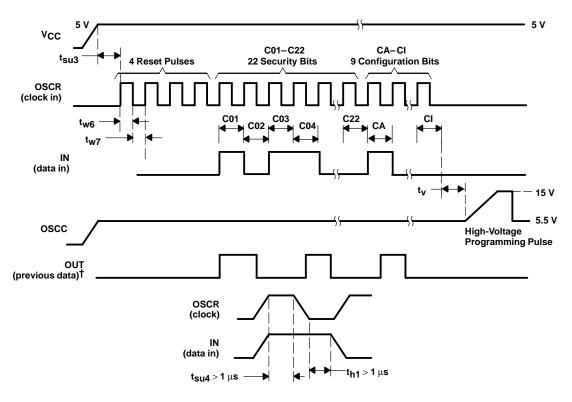

### 2.4.3 EEPROM Write Mode (see Figure 3–3 and Figure 3–4)

|                  |                                                  | MIN | MAX | UNIT |  |

|------------------|--------------------------------------------------|-----|-----|------|--|

| t <sub>su3</sub> | Setup time, OSCR high after V <sub>CC</sub> high | 50  |     | ms   |  |

| t <sub>w6</sub>  | N6 Pulse duration, OSCR high 5                   |     |     |      |  |

| tw7              | Pulse duration, OSCR low                         | 5   |     | μs   |  |

| t <sub>V</sub>   | Valid time, data IN valid before OSCC↑           | 10  |     | μs   |  |

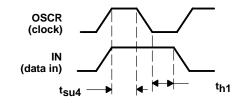

### 2.4.4 Data Input Setup and Hold Times (see Figure 3–5)

|                  |                                              | MIN | NOM | MAX | UNIT |

|------------------|----------------------------------------------|-----|-----|-----|------|

| t <sub>su4</sub> | Setup time, data in before OSCR $\downarrow$ |     | 1   |     | μs   |

| t <sub>h1</sub>  | Hold time, data in after OSCR↓               |     | 1   | ·   | μs   |

# 2.5 Switching Characteristics Over Recommended Ranges of Supply Voltages and Free-Air Temperature (unless otherwise noted)

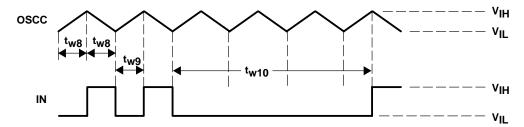

### 2.5.1 Normal Transmission – Internal Clock (see Figure 3–6)

|                 | PARAMETER                                                                      | MIN | TYP                       | MAX | UNIT |

|-----------------|--------------------------------------------------------------------------------|-----|---------------------------|-----|------|

| t <sub>w8</sub> | Pulse duration, half-oscillating period for OSCC sawtooth $\uparrow\downarrow$ | 5   | 1/(2 x f <sub>OSC</sub> ) | 100 | μs   |

| t <sub>w9</sub> | Pulse duration, logic bit 1 for IN                                             | 5   | t <sub>W</sub>            | 100 | μs   |

| tw10            | Pulse duration, logic bit 0 for IN                                             | 35  | 7 x t <sub>W</sub>        | 700 | μs   |

### 2.5.2 Modulated Transmission – Internal Clock

|                   | PARAMETER                                   | TEST<br>CONDITIOINS | MIN | TYP                   | MAX  | UNIT |

|-------------------|---------------------------------------------|---------------------|-----|-----------------------|------|------|

| fosc(t)           | Transmitter oscillator frequency            |                     | 100 | 110                   | 120  | kHz  |

| fosc(r)           | Receiver oscillator frequency               |                     | 400 | 440                   | 480  | kHz  |

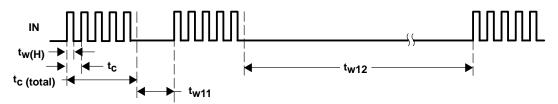

| t <sub>w(H)</sub> | Pulse duration, high-level modulation at IN | See Figure 3-7      | 9   | 1/fosc(t)             | 10   | μs   |

| t <sub>C</sub>    | Cycle time, IN                              | See Figure 3-7      | 27  | 3 x t <sub>w(H)</sub> | 30   | μs   |

| tc(total)         | Total cycle time, IN                        | See Figure 3-7      | 135 | 5 x t <sub>C</sub>    | 150  | μs   |

| tw11              | Pulse duration, logic bit 1 for IN          | See Figure 3-7      | 135 | 5 x t <sub>C</sub>    | 150  | μs   |

| tw12              | Pulse duration, logic bit 0 for IN          | See Figure 3-7      | 945 | 7 x t <sub>w10</sub>  | 1050 | μs   |

### 3 Parameter Measurement Information

Figure 3-1. Normal Transmission - External Clock

Figure 3-2. VTR Generation

Figure 3-3. EEPROM Read Mode

Figure 3-4. EEPROM Write Mode

Figure 3-5. Data In Setup and Hold Times

Figure 3-6. Normal Transmission - Internal Clock

Figure 3-7. Modulated Transmission - Internal Clock

### 4 Typical Characteristics

Figure 4-1. Oscillator Resistance Versus Supply Voltage

Figure 4–2. Oscillator Frequency Versus Oscillator Capacitance

### 5 Principles of Operation

### 5.1 Power-On Reset

The power-on reset function starts when  $V_{CC}$  rises above 2.7 V and is completed after four clock periods. After power-on reset, the nine configuration bits contained in the EEPROM memory are loaded into the logic circuits, which determine the device mode and configuration of operation. For correct enabling of the power-on reset operation, it is necessary for  $V_{CC}$  to first fall below 2.3 V and remain in this condition for at least 0.5 ms.

### 5.2 EEPROM Memory (31 Bits)

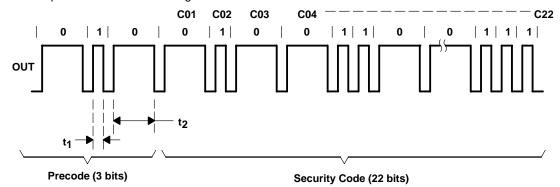

The EEPROM memory contains a total of 31 bits. The first 22 of the 31 bits contain the security code. These 22 bits are named C01, C02,...C22, and are user definable. The last 9 bits of the total 31 bits are configuration bits named CA,CB,...CI, and are also user definable to select the mode of operation for the device.

### 5.2.1 Program Read Mode

The procedure described in the following steps is used to read the current contents of the EEPROM memory. This can verify that the correct 22 security codes and 9 configuration bits are stored in memory (see Figure 5–1):

- 1. Set V<sub>CC</sub> to 5 V.

- 2. Apply  $V_{CC}$  + 0.5 V to OSCC. Wait at least 50 ms to allow the device to assume the read mode ( $t_{su2}$  > 50 ms). This voltage on OSCC forces the device into the read mode, and the terminals are in the following configuration:

- OSCR: program/read external clock input

- OUT: serial output of 31 data bits currently stored in EEPROM

- Apply four reset pulses to OSCR (t<sub>w4</sub> = t<sub>w5</sub> = 10 µs). This only needs to be done once during each read operation.

- 4. Apply 31 clock pulses to clock input OSCR (t<sub>w4</sub> = t<sub>w5</sub> = 10 μs min). This clocks out the 31 data bits (C01,C02,...C22, and CA,CB,...CI) that are stored in memory. Output data changes state only on falling edge of clock pulses, except on data bit C01. If used, data bit C01 goes high on the rising edge of the clock pulse.

#### NOTE:

Each succeeding group of 31 clock pulses, when applied, clocks out the data again without any reset pulses required.

Figure 5-1. EEPROM Read Mode

### 5.2.2 Program Write Mode

The procedure to write the 31 security code and configuration bits to memory is described below (see Section 3 for timing diagram):

- 1. Set V<sub>CC</sub> to 5 V.

- Apply V<sub>CC</sub> + 0.5 V to OSCC. This voltage on OSCC forces the device into the program mode, and the terminals are in the following configuration:

- OSCR: program/read external clock input

- OSCC: input for high-voltage programming pulse used to permanently store data in memory (see Figure 5–2).

- OUT: serial output of 31 data bits currently stored in EEPROM

- IN: serial input for 31 bits of data to be stored

- 3. After applying  $V_{CC}$  + 0.5 V to OSCC (step 2), wait at least 50 ms to allow device to go into the program mode.

- 4. Apply exactly four clock reset pulses to OSCR (clock input). These reset pulses are applied before clock input pulses for the 31 data bits that contain the security code and configuration bits. The minimum duration of the clock reset pulses must be  $t_{\rm W6} = t_{\rm W7} = > 5~\mu \rm s$ , which equates to a clock frequency <100 kHz.

- 5. Apply exactly 31 clock input pulses to OSCR. This serves to clock in the 31 data bits that should be applied to IN (C01,C02,...C22, and CA,CB,...CI). Each of the 31 data bits must be present on the falling edges of the clock input pulses applied to OSCR with the setup and hold times being 1 μs minimum.

- The data at OUT is previous data that was stored in EEPROM before this operation. If the device has never been programmed, this data is a random factory test code. The newly programmed data can be read only after it is loaded.

- 7. Apply a logic low to OSCR for at least 10  $\mu$ s.

8. After a minimum valid time of  $t_V = 10~\mu s$ , apply the high-voltage programming pulse to permanently store the 31 code bits in EEPROM memory as shown in Figure 5–2. As stated in steps 4 and 5, exactly 4 reset and 31 clock pulses must be applied for the device to successfully program. The device does not transfer the code from its registers into the EEPROM if less than or greater than 4 reset and 31 clock pulses are used before the programming pulse is applied.

<sup>†</sup> Previous data refers to data that was previously programmed into the device. If programmed for first time, this contains a random test code from the factory.

Figure 5-2. EEPROM Write Mode

## 5.3 Internal Oscillator Operation for Transmit and Receive Modes Setting Frequency

The TMS3637 has an internal oscillator that can be used in either the transmit or receive configurations of the device. The oscillator free-running frequency ( $f_{OSC}$ ) is controlled by an external resistor and capacitor and is determined by:

$$f_{osc} = 5 / (4 \times C_{osc} \times R_{osc})$$

(1)

where

Cosc = capacitor from OSCC to GND

R<sub>osc</sub> = resistor from OSCR to GND

The allowable oscillation range or  $R_{OSC}$  versus  $V_{CC}$ , and associated  $f_{OSC}$  values, and range versus  $C_{OSC}$  for three given values of  $R_{OSC}$  are given in Section 4.

# 5.4 Internal Oscillator Operation for Transmit and Receive Modes Sampling Frequency

The internal oscillator of the transmitter or receiver can be externally sampled at OSCC and OSCR. The waveform at OSCC is triangular and the waveform at OSCR is square. The amplitude of these waveforms depends on the capacitor and resistor values used.

### 5.5 External Oscillator Operation for Transmit and Receive Modes

Instead of using the internal oscillator (with an external resistor and capacitor) in the transmit or receive modes, it is possible to externally drive the device by applying a logic level clock to OSCC. When an externally driven oscillator is used, OSCR must be held to GND. To avoid entering the test/program modes, ensure that the external clock applied to OSCC does not exceed  $V_{CC}$  (for more information see Section 5.12).

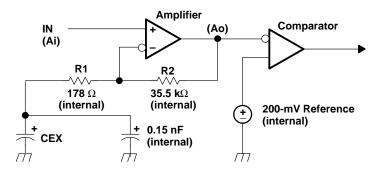

### 5.6 Internal Amplifier/Comparator, Description and Gain Setting

The TMS3637 has an internal amplifier that is designed to amplify received signals up to logic levels. In addition, a comparator is cascaded with the amplifier to provide wave shaping of received signals. The comparator also inverts the signal. The minimum received signal strength must be at least 3 mV peak-to-peak (see Figure 5–3 for a schematic of the amplifier/comparator section). The amplifier is enabled only when the TMS3637 is configured as an analog receiver. When the amplifier is not configured as an analog receiver, it is disabled and bypassed to reduce power consumption in any of the three logic receiver modes. A capacitor connected between CEX to GND determines the gain of the amplifier stage. When no capacitor is connected from CEX to GND, the amplifier assumes unity gain and the comparator still functions to shape the received signal. When the internal amplifier is used, it is usually run at the maximum gain of 200. The maximum gain is set by resistances internal to the device as shown in the equation 2. However, to achieve this maximum gain, a low impedance from CEX to GND must exist. Equation 2 defines the capacitance necessary at CEX for maximum gain at different oscillator frequencies (f<sub>OSC</sub>):

$$CEX > 1 / (6.28 \times f_{OSC} \times R1)$$

(2)

where:

CEX = capacitance required for maximum gain

R1 =  $178 \Omega$  (set internally)

With a low impedance between GND and CEX, note that the maximum gain is derived from the noninverting operational amplifier gain equation, (see Figure 5–3):

$$Gv = 1 + R2/R1 = 200$$

(3)

where:

$R1 = 178 \Omega$  (set internally)

$R2 = 35.5 \text{ k}\Omega$  (set internally)

If a capacitor is used at CEX, but maximum gain is not desired, equation 4 can determine the gain for any value of CEX:

$$Gv = \sqrt{\left(\frac{1 + 4\pi^2 f_{OSC}^2 CT^2 (R1 + R2)^2}{1 + 4\pi^2 f_{OSC}^2 CT^2 R1^2}\right)}$$

(4)

where:

f<sub>osc</sub> = oscillator frequency of transmitter (it is the transmitted frequency that is being amplified)

$C_T = CEX + 0.15 \text{ nF}$  (there is an internal capacitance of 0.15 nF at CEX)

R1 = 178  $\Omega$  (set internally)

$R2 = 35.5 \text{ k}\Omega \text{ (set internally)}$

Figure 5-3. Amplifier/Comparator Schematic

### 5.7 Internal Amplifier/Comparator Test Mode

Normally, the output of the amplifier/comparator section is fed directly to the logic circuitry internal to the device; however, the output of the amplifier/comparator can be sampled external to the device during the amplifier test mode to determine if the amplitude and shape of the received signal is acceptable for the application. To enter the amplifier test mode, apply  $V_{CC} + 0.5 \text{ V}$  to OSCC and apply three or more low-level pulses to OSCR. This can be done by simply brushing a wire connected from OSCR to GND. The output of the amplifier stage is then connected internally to TIME, where it can be sampled for evaluation purposes.

### 5.8 Mode and Configuration Overview

The TMS3637 device is designed to function in many modes and configurations. The device has five primary modes of operation as shown in Table 5–1.

Table 5-1. Mode and Test Configuration

| MODE | DESCRIPTION    |  |  |  |  |

|------|----------------|--|--|--|--|

| 1    | Amplifier Test |  |  |  |  |

| 2    | Program        |  |  |  |  |

| 3    | Read           |  |  |  |  |

| 4    | Transmitter    |  |  |  |  |

| 5    | Receiver       |  |  |  |  |

In the transmitter and receiver modes (see Tables 5–2 and 5–3), there are a total of 66 configurations available, 48 in the receiver mode and 18 in the transmitter mode.

Table 5-2. Transmitter Modes

| NO. OF<br>MODES | CONFIG.                              | OSCR<br>(PIN 1)                | OSCC<br>(PIN 2)                                                                                                | TIME<br>(PIN 3)                                                                    | OUT<br>(PIN 5)                                                                     | CEX<br>(PIN 6)                                  | IN<br>(PIN 7)                                   | C1–C22<br>ABCDEFG<br>HI  | CA-CI<br>ABCDEFG<br>HIT  |                          |                          |                        |                            |           |     |

|-----------------|--------------------------------------|--------------------------------|----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|-------------------------------------------------|-------------------------------------------------|--------------------------|--------------------------|--------------------------|--------------------------|------------------------|----------------------------|-----------|-----|

| 1               | Normal<br>Continuous                 |                                |                                                                                                                |                                                                                    |                                                                                    |                                                 |                                                 |                          |                          |                          | 11100000X                |                        |                            |           |     |

| 1               | Normal<br>Triggered                  |                                |                                                                                                                |                                                                                    |                                                                                    |                                                 |                                                 |                          | 110DE0001                |                          |                          |                        |                            |           |     |

| 1               | Normal<br>Periodic                   |                                |                                                                                                                |                                                                                    |                                                                                    |                                                 |                                                 |                          | 110DE0000                |                          |                          |                        |                            |           |     |

| 1               | Modulated<br>Triggered               |                                | Capacitor to<br>GND<br>(internal<br>clock) and<br>output of the<br>internal<br>clock<br>triangular<br>waveform | GND<br>(internal<br>clock) and<br>output of the<br>internal<br>clock<br>triangular | GND<br>(internal<br>clock) and<br>output of the<br>internal<br>clock<br>triangular | GND<br>(internal<br>clock) and<br>output of the | GND<br>(internal<br>clock) and<br>output of the |                          |                          |                          |                          |                        |                            | 100DE0001 |     |

| 1               | Modulated<br>Continuous              | External                       |                                                                                                                |                                                                                    |                                                                                    |                                                 |                                                 |                          |                          |                          |                          |                        | 10100000X                  |           |     |

| 1               | Modulated<br>Periodic                | clock or<br>resistor to<br>GND |                                                                                                                |                                                                                    |                                                                                    |                                                 |                                                 | clock) and output of the | Starts<br>transmitting | Serial output of currently | N/C       | N/C |

| 3               | Code Train<br>Normal<br>Triggered    | (internal<br>clock)            |                                                                                                                |                                                                                    |                                                                                    | when low                                        | stored data                                     |                          |                          | memory                   | 110DE0001                |                        |                            |           |     |

| 3               | Code Train<br>Normal<br>Periodic     |                                |                                                                                                                |                                                                                    |                                                                                    |                                                 |                                                 |                          |                          |                          |                          |                        |                            | 110DE0000 |     |

| 1               | Code Train<br>Modulated<br>Triggered |                                |                                                                                                                |                                                                                    |                                                                                    |                                                 |                                                 |                          | 100DE0001                |                          |                          |                        |                            |           |     |

| 3               | Code Train<br>Modulated<br>Periodic  |                                |                                                                                                                |                                                                                    |                                                                                    |                                                 |                                                 |                          |                          |                          | 100DE0000                |                        |                            |           |     |

$<sup>\</sup>dagger X = don't care and can be held high or low$

Table 5-3. Receiver Modes

| NO. OF<br>MODES <sup>†</sup> | CONFIG.                     | OSCR<br>(PIN 1)       | OSCC<br>(PIN 2)                                                                                                                                               | TIME<br>(PIN 3)                                                                                                                             | OUT<br>(PIN 5)                                           | CEX<br>(PIN 6)                                          | IN<br>(PIN 7)                  | C1-C22<br>ABCDEF<br>GHI                | CA-CI<br>ABCDEFG<br>HI <sup>‡</sup> |                      |                            |                      |                                  |                                  |                      |                                  |                                  |                                  |                                  |                      |                      |                   |                      |                      |                      |                      |  |                           |  |  |

|------------------------------|-----------------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|---------------------------------------------------------|--------------------------------|----------------------------------------|-------------------------------------|----------------------|----------------------------|----------------------|----------------------------------|----------------------------------|----------------------|----------------------------------|----------------------------------|----------------------------------|----------------------------------|----------------------|----------------------|-------------------|----------------------|----------------------|----------------------|----------------------|--|---------------------------|--|--|

| 2                            | Analog<br>Normal<br>VTR     |                       |                                                                                                                                                               | Requires a<br>high-to-<br>enable                                                                                                            |                                                          |                                                         |                                |                                        | 010XX010I                           |                      |                            |                      |                                  |                                  |                      |                                  |                                  |                                  |                                  |                      |                      |                   |                      |                      |                      |                      |  |                           |  |  |

| 6                            | Analog<br>Normal<br>Train   |                       |                                                                                                                                                               |                                                                                                                                             | a resistor and                                           | and<br>capacitor in<br>parallel<br>connected<br>between | stor                           | Capacitor to GND                       |                                     |                      | 010DE011I                  |                      |                                  |                                  |                      |                                  |                                  |                                  |                                  |                      |                      |                   |                      |                      |                      |                      |  |                           |  |  |

| 8                            | Analog<br>Normal<br>Q-state |                       |                                                                                                                                                               | parallel connected between V <sub>CC</sub> and ground to                                                                                    | parallel connected between V <sub>CC</sub> and ground to |                                                         | connected between              | parallel<br>connected<br>between       | parallel<br>connected<br>between    | connected<br>between | connected<br>between       | connected<br>between | parallel<br>connected<br>between | parallel<br>connected<br>between | connected<br>between | parallel<br>connected<br>between | parallel<br>connected<br>between | parallel<br>connected<br>between | parallel<br>connected<br>between | connected<br>between | connected<br>between | connected between | connected<br>between | connected<br>between | connected<br>between | connected<br>between |  | for<br>receiver<br>analog |  |  |

| 2                            | Modulated<br>VTR            | External clock or     | Capacitor                                                                                                                                                     |                                                                                                                                             |                                                          | Serial output of currently                              | amplifier<br>gain              |                                        |                                     | 000XXX10I            |                            |                      |                                  |                                  |                      |                                  |                                  |                                  |                                  |                      |                      |                   |                      |                      |                      |                      |  |                           |  |  |

| 6                            | Modulated<br>Train          | resistor to<br>GND    | to GND (Internal clock)  the OUT pulse. When operated in periodic mode, a resistor and capacitor in parallel connected between VCC and ground causes a reset. | to GND the OUT sulse. Clock) When operated in periodic mode, a resistor and capacitor in parallel connected between VCC and ground causes a | to GND the Control (Internal clock) Whe oper             | to GND<br>(Internal<br>clock)                           | to GND the (Internal clock) Wh | to GND the OUT pulse. When operated in | stored data<br>and                  |                      | Receive<br>signal<br>input | Data received        | 000DEX11I                        |                                  |                      |                                  |                                  |                                  |                                  |                      |                      |                   |                      |                      |                      |                      |  |                           |  |  |

| 8                            | Modulated<br>Q-state        | (Internal<br>clock)   |                                                                                                                                                               |                                                                                                                                             |                                                          |                                                         |                                |                                        | clock)                              | clock)               | operated in                | operated in          | operated in                      | operated in                      | operated in          | operated in                      | operated in                      | operated in                      | operated in data                 | l input              |                      | 000DEX00I         |                      |                      |                      |                      |  |                           |  |  |