# TLC7225C, TLC7225I QUADRUPLE 8-BIT DIGITAL-TO-ANALOG CONVERTERS

SLAS109 - OCTOBER 1996

- Direct Bipolar Operation Without an External Level Shift Amplifier

- Microprocessor Compatible

- TTL/CMOS Compatible

- Single Supply Operation Possible

- Simultaneous Update Facility

- Binary Input Coding

#### applications

- Process Control

- Automatic Test Equipment

- Automatic Calibration of Large System Parameters e.g., Gain/Offset

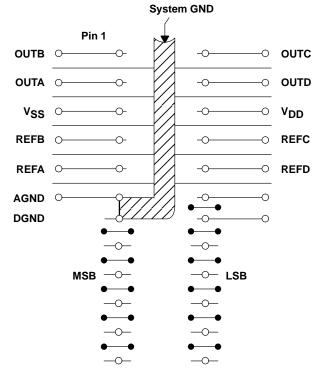

#### **DW PACKAGE** (TOP VIEW) OUTB [ 24 OUTC OUTA [ 2 Vss [ 3 REFB ∏ 4 21 ∏ REFC 20 REFD REFA [ AGND [ 19 🛮 A0 DGND [ 18**∏** A1 17 WR LDAC [ (MSB) DB7 16 DB0 (LSB) 9 DB6 **□** 10 15 DB1 DB5 14 DB2 11 13 DB3 DB4 | 12

#### description

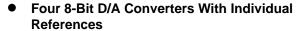

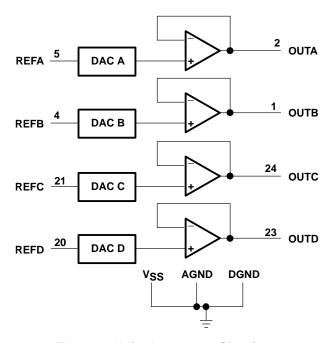

The TLC7225 consists of four 8-bit voltage-output digital-to-analog converters (DACs), with output buffer amplifiers and interface logic with double register-buffering.

Separate on-chip latches are provided for each of the DACs. Data is transferred into one of these data latches through a common 8-bit TTL/CMOS compatible (5 V) input port. Control inputs A0 and A1 determine which DAC is loaded when  $\overline{WR}$  goes low. Only the data held in the DAC registers determines the analog outputs of the converters. The double register-buffering allows simultaneous update of all four outputs under control of  $\overline{LDAC}$ . All logic inputs are TTL- and CMOS-level compatible and the control logic is speed compatible with most 8-bit microprocessors. Each DAC includes an output buffer amplifier capable of driving up to 5 mA of output current.

The TLC7225 performance is specified for input reference voltages from 2 V to  $V_{DD}$  – 4 V with dual supplies. The voltage-mode configuration of the DACs allow the TLC7225 to be operated from a single power-supply rail at a reference of 10 V.

The TLC7225 is fabricated in a LinBiCMOS<sup>™</sup> process that has been specifically developed to allow high-speed digital logic circuits and precision analog circuits to be integrated on the same chip. The TLC7225 has a common 8-bit data bus with individual DAC latches. This provides a versatile control architecture for simple interface to microprocessors. All latch-enable signals are level triggered.

Combining four DACs, four operational amplifiers, and interface logic into a small, 0.3-inch wide, 24-terminal SOIC allows significant reduction in board space requirements and offers increased reliability in systems using multiple converters. The pinout optimizes board layout with all of the analog inputs and outputs at one end of the package and all of the digital inputs at the other.

The TLC7225C is characterized for operation from 0°C to 70°C. The TLC7225I is characterized for operation from –40°C to 85°C.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

LinBiCMOS is a trademark of Texas Instruments Incorporated.

#### **AVAILABLE OPTIONS**

| PACKAGED DEVICES |                       |  |  |  |

|------------------|-----------------------|--|--|--|

| TA               | SMALL OUTLINE<br>(DW) |  |  |  |

| 0°C to 70°C      | TLC7225CDW            |  |  |  |

| -40°C to 85°C    | TLC7225IDW            |  |  |  |

# functional block diagram

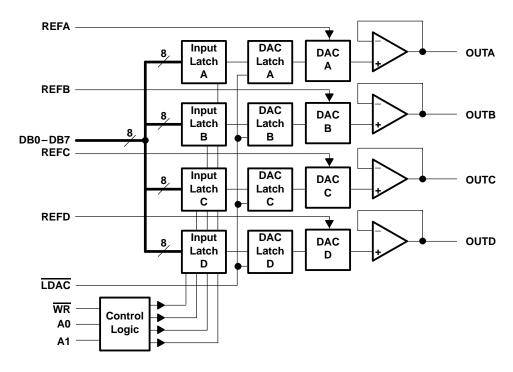

# schematic of outputs

#### **Terminal Functions**

| TERMINAL  |        | 1/0 | DESCRIPTION                                                                                                         |

|-----------|--------|-----|---------------------------------------------------------------------------------------------------------------------|

| NAME      | NO.    | 1/0 | DESCRIPTION                                                                                                         |

| AGND      | 6      |     | Analog ground                                                                                                       |

| A0, A1    | 18, 19 | ı   | DAC select inputs                                                                                                   |

| DGND      | 7      |     | Digital ground                                                                                                      |

| DB0 – DB7 | 9 – 16 | I   | Digital DAC data inputs                                                                                             |

| LDAC      | 8      |     | Load DAC. A high level simultaneously loads all four DAC registers. DAC registers are transparent when LDAC is low. |

| OUTA      | 2      | 0   | DACA output                                                                                                         |

| OUTB      | 1      | 0   | DACB output                                                                                                         |

| OUTC      | 24     | 0   | DACC output                                                                                                         |

| OUTD      | 23     | 0   | DACD output                                                                                                         |

| REFA      | 5      | I   | Voltage reference input to DACA                                                                                     |

| REFB      | 4      | I   | Voltage reference input to DACB                                                                                     |

| REFC      | 21     | I   | Voltage reference input to DACC                                                                                     |

| REFD      | 20     | ı   | Voltage reference input to DACD                                                                                     |

| $V_{DD}$  | 22     |     | Positive supply voltage                                                                                             |

| VSS       | 3      |     | Negative supply voltage                                                                                             |

| WR        | 17     | Ī   | Write input selects DAC transparency or latch mode                                                                  |

# absolute maximum ratings over operating free-air temperature range (unless otherwise note)†

| Supply voltage range, V <sub>DD</sub> : to AGND or DGND                             | 0.3 V to 17 V                              |

|-------------------------------------------------------------------------------------|--------------------------------------------|

| to V <sub>SS</sub>                                                                  | 0.3 V to 24 V                              |

| Supply voltage range, V <sub>SS</sub> : to AGND or DGND                             | –7 V to V <sub>DD</sub>                    |

| Voltage range between AGND and DGND                                                 | –0.3 V to V <sub>DD</sub>                  |

| Input voltage range, V <sub>I</sub> (to DGND)                                       | $-0.3 \text{ V to V}_{DD} + 0.3 \text{ V}$ |

| Reference voltage range, V <sub>ref</sub> (to AGND)                                 | –0.3 V to V <sub>DD</sub>                  |

| Output voltage range, V <sub>O</sub> (to AGND) (see Note 1)                         | $\dots$ $V_{SS}$ to $V_{DD}$               |

| Continuous total power dissipation at (or below) T <sub>A</sub> = 25°C (see Note 2) | 500 mW                                     |

| Operating free-air temperature range: C suffix                                      | 0°C to 70°C                                |

| I suffix                                                                            | –40°C to 85°C                              |

| Storage temperature range, T <sub>stq</sub>                                         | –65°C to 150°C                             |

| Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds                        |                                            |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

2. For operation above  $T_A = 75^{\circ}C$  derate linearly at the rate of 2.0 mW/°C.

NOTES: 1. Output voltages may be shorted to AGND provided that the power dissipation of the package is not exceeded. Typically short circuit current to AGND is 50 mA.

# TLC7225C, TLC7225I QUADRUPLE 8-BIT DIGITAL-TO-ANALOG CONVERTERS

SLAS109 - OCTOBER 1996

# recommended operating conditions

|                                          |                                 |   | MIN        | MAX  | UNIT |

|------------------------------------------|---------------------------------|---|------------|------|------|

| Supply voltage, V <sub>DD</sub>          |                                 |   |            | 16.5 | V    |

| Supply voltage, VSS                      |                                 |   | -5.5       | 0    | V    |

| High-level input voltage, VIH            | High-level input voltage, VIH   |   |            |      | V    |

| Low-level input voltage, V <sub>IL</sub> |                                 |   |            | 0.8  | V    |

| Reference voltage, V <sub>ref</sub>      |                                 | 2 | $V_{DD}-4$ | V    |      |

| Load resistance, R <sub>L</sub>          | Load resistance, R <sub>L</sub> |   | 2          |      | kΩ   |

| Operating free air temperature. To       | C suffix                        |   | 0          | 70   | °C   |

| Operating free-air temperature, Тд       | I suffix                        |   | -40        | 85   | °C   |

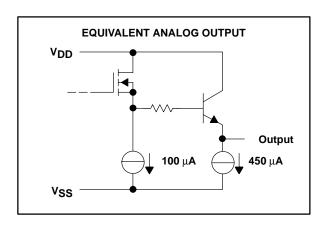

# timing requirements (see Figure 1)

|                     | PARAMETER                                                       | TEST CONDITIONS                                                                    |    | TYP | MAX | UNIT |

|---------------------|-----------------------------------------------------------------|------------------------------------------------------------------------------------|----|-----|-----|------|

| t <sub>su(AW)</sub> | Setup time, address valid before $\overline{WR} \!\!\downarrow$ |                                                                                    | 0  |     |     | ns   |

| t <sub>su(DW)</sub> | Setup time, data valid before WR↑                               | $V_{DD} = 11.4 \text{ V to } 16.5 \text{ V},  V_{SS} = 0 \text{ or } -5 \text{ V}$ | 45 |     |     | ns   |

| th(AW)              | Hold time, address valid after WR↑                              | $V_{DD} = 11.4 \text{ V to } 16.5 \text{ V},  V_{SS} = 0 \text{ or } -5 \text{ V}$ | 0  |     |     | ns   |

| th(DW)              | Hold time, data valid after WR↑                                 | $V_{DD} = 11.4 \text{ V to } 16.5 \text{ V},  V_{SS} = 0 \text{ or } -5 \text{ V}$ | 10 |     |     | ns   |

| t <sub>w1</sub>     | Pulse duration, WR low                                          | $V_{DD} = 11.4 \text{ V to } 16.5 \text{ V},  V_{SS} = 0 \text{ or } -5 \text{ V}$ | 50 |     |     | ns   |

| t <sub>w2</sub>     | Pulse duration, LDAC low                                        | $V_{DD} = 11.4 \text{ V to } 16.5 \text{ V},  V_{SS} = 0 \text{ or } -5 \text{ V}$ | 50 |     |     | ns   |

# electrical characteristics over recommended operating free-air temperature range

# reference inputs (all supply ranges)

| PARAMETER |                                            | TEST CONDITIONS                           | MIN | TYP | MAX | UNIT |

|-----------|--------------------------------------------|-------------------------------------------|-----|-----|-----|------|

| rį        | Input resistance, REFA, REFB, REFC, REFD   |                                           | 1.5 | 4   |     | kΩ   |

| Ci        | Input capacitance, REFA, REFB, REFC, REFD  | DAC loaded with all 1s                    |     |     | 300 | pF   |

|           | input capacitatice, NETA, NETB, NETG, NETB | DAC loaded with all 0s                    | 65  |     |     | pF   |

|           | Channel-to-channel isolation               | V 4 – 10 V sino ways at 10 kHz            | 60  |     |     | dB   |

|           | ac feedthrough                             | $V_{ref} = 10 V_{pp}$ sine wave at 10 kHz | 70  |     |     | dB   |

# dual power supply over recommended supply and reference voltage ranges, AGND = DGND = 0 V (unless otherwise noted)

|                 | PARAMETER                       |                | TEST CONDI                         | TIONS   | MIN | TYP | MAX  | UNIT |

|-----------------|---------------------------------|----------------|------------------------------------|---------|-----|-----|------|------|

| Ц               | Input current, digital          |                | $V_I = 0$ or $V_{DD}$              |         |     |     | ±1   | μΑ   |

| I <sub>DD</sub> | Supply current, V <sub>DD</sub> |                | $V_I = V_{IL} \text{ or } V_{IH},$ | No load |     | 10  | 16   | mA   |

| ISS             | Supply current, VSS             |                | $V_I = V_{IL} \text{ or } V_{IH},$ | No load |     | 4   | 10   | mA   |

|                 | Power supply sensitivity        |                | $\Delta V_{DD} = \pm 5\%$          |         |     |     | 0.01 | %/%  |

| Ci              | Input capacitance               | Digital inputs |                                    |         |     |     | 8    | pF   |

# single power supply, $V_{DD}$ = 14.25 V to 15.75 V, $V_{SS}$ = AGND = DGND = 0 V, $V_{ref}$ (A, B, C, D) = 10 V

|                 | PARAMETER                       |                |                                    | TIONS   | MIN | TYP | MAX  | UNIT |

|-----------------|---------------------------------|----------------|------------------------------------|---------|-----|-----|------|------|

| II              | Input current, digital          |                | $V_I = 0$ or $V_{DD}$              |         |     |     | ±1   | μΑ   |

| I <sub>DD</sub> | Supply current, V <sub>DD</sub> |                | $V_I = V_{IL} \text{ or } V_{IH},$ | No load |     | 5   | 13   | mA   |

|                 | Power supply sensitivity        |                | $\Delta V_{DD} = \pm 5\%$          |         |     |     | 0.01 | %/%  |

| Ci              | Input capacitance               | Digital inputs |                                    |         |     |     | 8    | pF   |

# TLC7225C, TLC7225I QUADRUPLE 8-BIT DIGITAL-TO-ANALOG CONVERTERS

SLAS109 - OCTOBER 1996

# operating characteristics over recommended operating free-air temperature range

# dual power supply over recommended supply and reference voltage ranges, AGND = DGND = 0 V (unless otherwise noted)

|                 | PARAMETE                                             | ER .                | TEST CO                              | ONDITIONS                    | MIN | TYP   | MAX | UNIT   |

|-----------------|------------------------------------------------------|---------------------|--------------------------------------|------------------------------|-----|-------|-----|--------|

|                 | Slew rate                                            |                     |                                      |                              | 2.5 |       |     | V/μs   |

| Γ.              | Settling time to 1/2                                 | Positive full scale | V                                    |                              |     |       | 5   |        |

| t <sub>S</sub>  | LSB                                                  | Negative full scale | V <sub>ref</sub> (A, B, C, D) = 10 V |                              |     |       | 7   | μs     |

|                 | Resolution                                           |                     |                                      |                              |     | 8     |     | Bits   |

|                 | Total unadjusted error                               |                     | $V_{DD} = 15 \text{ V} \pm 5\%,$     | Vref(A, B, C, D) = 10 V      |     |       | ±2  | LSB    |

|                 | Integral nonlinearity (IN                            | L)                  | $V_{DD} = 15 \text{ V} \pm 5\%,$     | Vref(A, B, C, D) = 10 V      |     |       | ±1  | LSB    |

|                 | Differential nonlinearity                            | (DNL)               | $V_{DD} = 15 \text{ V} \pm 5\%,$     | Vref(A, B, C, D) = 10 V      |     |       | ±1  | LSB    |

| E <sub>FS</sub> | Full-scale error                                     |                     | $V_{DD} = 15 \text{ V} \pm 5\%,$     | $V_{ref(A, B, C, D)} = 10 V$ |     |       | ±2  | LSB    |

| EG              | Gain error                                           |                     | $V_{DD} = 15 \text{ V} \pm 5\%,$     | Vref(A, B, C, D) = 10 V      |     | ±0.25 |     | LSB    |

|                 | Temperature coeffi-                                  | Full-scale error    | V <sub>DD</sub> = 14 V to 16.5 V,    | V 5 6 5 - 10 V               |     | ±20   |     | ppm/°C |

|                 | cient of gain                                        | Zero-code error     | ν <sub>DD</sub> = 14 ν to 16.5 ν,    | $V_{ref(A, B, C, D)} = 10 V$ |     | ±50   |     | μV/°C  |

|                 | Zero-code error                                      |                     |                                      |                              |     | ±20   | ±80 | mV     |

|                 | Digital crosstalk or feedthrough glitch impulse area |                     | V <sub>ref</sub> (A, B, C, D) = 0    |                              |     | 50    |     | nV-s   |

# single power supply, $V_{DD}$ = 14.25 V to 15.75 V, $V_{SS}$ = AGND = DGND = 0 V, $V_{ref(A, B, C, D)}$ = 10 V

|                 | PARAMETER                                           |                     | TEST CONDITIONS                                                           | MIN | TYP | MAX | UNIT   |

|-----------------|-----------------------------------------------------|---------------------|---------------------------------------------------------------------------|-----|-----|-----|--------|

|                 | Slew rate                                           | _                   |                                                                           | 2   |     |     | V/μA   |

|                 | Settling time to 1/2 LSB                            | Positive full scale |                                                                           |     |     | 5   |        |

| t <sub>S</sub>  | Settling time to 1/2 LSB                            | Negative full scale |                                                                           |     |     | 20  | μs     |

|                 | Resolution                                          |                     |                                                                           |     | 8   |     | Bits   |

|                 | Total unadjusted error                              |                     |                                                                           |     |     | ±2  | LSB    |

| E <sub>FS</sub> | Full-scale error                                    |                     |                                                                           |     |     | ±2  | LSB    |

|                 | Temperature coefficient of gain                     | Full-scale error    | V <sub>DD</sub> = 14 V to 16.5 V,<br>V <sub>ref</sub> (A, B, C, D) = 10 V |     | ±20 |     | ppm/°C |

|                 |                                                     | Zero-code error     |                                                                           |     | ±50 |     | μV/°C  |

|                 | Differential nonlinearity error (DNL)               | •                   |                                                                           |     |     | ±1  | LSB    |

|                 | Digital crosstalk or feedthrough glitch impulse are | a                   |                                                                           |     | 50  | ·   | nV-s   |

#### PARAMETER MEASUREMENT INFORMATION

NOTES: A.  $t_r = t_f = 20$  ns over  $V_{DD}$  range.

- B. The timing-measurement reference level is equal to  $V_{IH} + V_{IL}$  divided by 2.

- C. If LDAC is activated prior to the rising edge of WR, then it must remain low for at least two after WR goes high.

Figure 1. Write-Cycle Voltage Waveforms

## **TYPICAL CHARACTERISTICS**

#### specification ranges

For the TLC7225 to operate to rated specifications, the input reference voltage must be at least 4 V below the power supply voltage at the  $V_{DD}$  terminal. This voltage differential is the overhead voltage required by the output amplifiers.

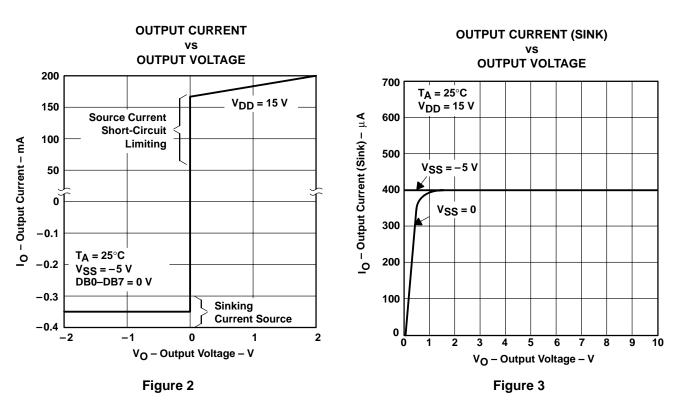

The TLC7225 is specified to operate over a  $V_{DD}$  range from 12 V  $\pm$  5% to 15 V  $\pm$  10% (i.e., from 11.4 V to 16.5 V) with a  $V_{SS}$  of -5 V  $\pm$  10%. Operation is also specified for a single supply with a  $V_{DD}$  of 15 V  $\pm$  5%. Applying a  $V_{SS}$  of -5 V results in improved zero-code error, improved output sink capability with outputs near AGND, and improved negative going settling time.

Performance is specified over the range of reference voltages from 2 V to  $(V_{DD}-4 V)$  with dual supplies. This allows a range of standard refence generators to be used such as the TL1431, with an adjustable 2.5-V bandgap reference. Note that an output voltage range 0 V to 10 V requires a nominal 15 V  $\pm$  5% power supply voltage.

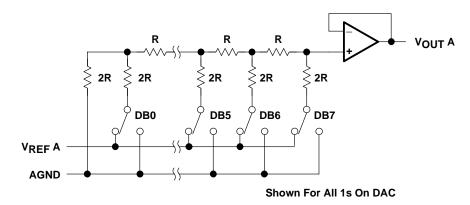

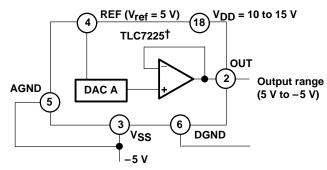

#### **DAC** section

The TLC7225 contains four, identical, 8-bit voltage-mode DACs. Each converter has a separate reference input. The output voltages from the converters have the same polarity as the reference voltages, thus allowing single supply operation.

The simplified circuit diagram for channel A is shown in Figure 4. Note that AGND (terminal 6) is common to all four DACs.

Figure 4. DAC Simplified-Circuit Diagram

The input impedance at any of the reference inputs is code dependent and can vary from 1.4 k $\Omega$  minimum to an open circuit. The lowest input impedance at any reference input occurs when that DAC is loaded with the digital code 01010101. Therefore, it is important that the reference source presents a low output impedance under changing load conditions. The nodal capacitance at the reference terminals is also code dependent and typically varies from 60 pF to 300 pF.

Each VOLIT terminal can be considered as a digitally programmable voltage source with an output voltage of:

$$V_{OUTX} = D_X \times V_{REFX}$$

where D<sub>X</sub> is the fractional representation of the digital input code and can vary from 0 to 255/256.

The output impedance is that of the output buffer amplifier.

#### APPLICATION INFORMATION

#### output buffer

Each voltage-mode DAC output is buffered by a unity-gain noninverting amplifier. This buffer amplifier is capable of developing 10 V across a 2-k $\Omega$  load and can drive capacitive loads of 3300 pF.

The TLC7225 can be operated as a single or dual supply; operating with dual supplies results in enhanced performance in some parameters which cannot be achieved with a single-supply operation. In a single supply operating ( $V_{SS} = 0 \text{ V} = \text{AGND}$ ) the sink capability of the amplifier, which is normally 400  $\mu$ A, is reduced as the output voltage nears AGND. The full sink capability of 400  $\mu$ A is maintained over the full output voltage range by tying  $V_{SS}$  to -5 V. This is indicated in Figure 3.

Settling time for negative-going output signals approaching AGND is similarly affected by  $V_{SS}$ . Negative-going settling time for single supply operation is longer than for dual supply operation. Positive-going settling-time is not affected by  $V_{SS}$ .

Additionally, the negative V<sub>SS</sub> gives more headroom to the output amplifiers which results in better zero code performance and improved slew rate at the output, than can be obtained in the single-supply mode.

#### digital inputs

The TLC7225 digital inputs are compatible with either TTL or 5-V CMOS levels. To minimize power supply currents, it is recommended that the digital input voltages be driven as close to the supply rails (V<sub>DD</sub> and DGND) as practically possible.

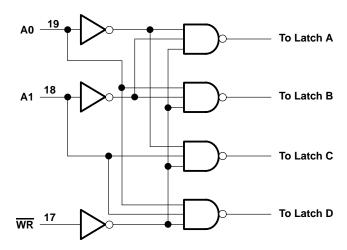

### interface logic information

The TLC7225 contains two registers per DAC, an input register and a DAC register. Address lines A0 and A1 select which input register accepts data from the input port. When the  $\overline{WR}$  signal is low, the input latches of the selected DAC are transparent. The data is latched into the addressed input register on the rising edge of  $\overline{WR}$ . Table 1 shows the addressing for the input registers on the TLC7225.

|    | TROL<br>UTS | SELECTED INPUT REGISTER |

|----|-------------|-------------------------|

| A1 | A0          | REGISTER                |

| L  | L           | DAC A input register    |

| L  | Н           | DAC B input register    |

| Н  | L           | DAC C input register    |

| Н  | Н           | DAC D input register    |

Table 1. TLC7225 Addressing

Only the data held in the DAC register determines the analog output of the converter. The  $\overline{LDAC}$  signal is common to all four DACs and controls the transfer of information from the input registers to the DAC registers. Data is latched into all four DAC registers simultaneously on the rising edge of  $\overline{LDAC}$ . The  $\overline{LDAC}$  signal is level triggered and, therefore, the DAC registers may be made transparent by tying  $\overline{LDAC}$  low (the outputs of the converters responds to the data held in their respective input latches).  $\overline{LDAC}$  is an asynchronous signal and is independent of  $\overline{WR}$ . This is useful in many applications. However, in systems where the asynchronous  $\overline{LDAC}$  can occur during a write cycle (or vice versa) care must be taken to ensure that incorrect data is not latched through to the output. In other words, if  $\overline{LDAC}$  is activated prior to the rising edge of  $\overline{WR}$  (or  $\overline{WR}$  occurs during  $\overline{LDAC}$ ), then  $\overline{LDAC}$  must stay low for a time of  $t_{W2}$  or longer after  $\overline{WR}$  goes high to ensure that the correct data is latched through to the output. Table 2 shows the truth table for TLC7225 operation. Figure 5 shows the input control logic for the device and the write cycles timing diagram is shown in Figure 1.

Table 2. TLC7225 Truth Table

| CONTRO | L INPUTS | FUNCTION                                                                                                                               |

|--------|----------|----------------------------------------------------------------------------------------------------------------------------------------|

| WR     | LDAC     | FONCTION                                                                                                                               |

| Н      | Н        | No operation. Device not selected                                                                                                      |

| L      | Н        | Input register of selected DAC is transparant.                                                                                         |

| 1      | Н        | Input register of selected DAC is latched.                                                                                             |

| Н      | L        | All four DAC registers are transparent (i.e., outputs respond to data held in respective input registers) input registers are latched. |

| Н      | 1        | All four DAC registers are latched.                                                                                                    |

| L      | L        | DAC registers and selected input register are transparent. Output follows input data for selected channel.                             |

Figure 5. Input Control Logic

### ground management and layout

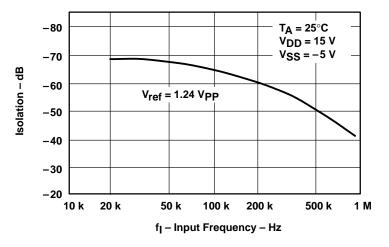

The TLC7225 contains four reference inputs that can be driven from ac sources (see multiplying DAC using AC input to the REF terminals section) so careful layout and grounding is important to minimize analog crosstalk between the four channels. The dynamic performance of the four DACs depends upon the optimum choice of board layout. Figure 6 shows the relationship between input frequency and channel-to-channel isolation. Figure 7 shows a printed circuit board layout that minimizes crosstalk and feedthrough. The four input signals are screened by AGND. V<sub>ref</sub> was limited between 2 V and 3.24 V to avoid slew-rate limiting effects from the output amplifier during measurements.

Figure 6. Channel-to-Channel Isolation

Figure 7. Suggested PCB Layout (Top View)

### unipolar output operation

The unipolar output operation is the basic mode of operation for each channel of the TLC7225, with the output voltages having the same positive polarity as  $V_{ref}$ . The TLC7225 can be operated with a single supply ( $V_{SS} = AGND$ ) or with positive or negative supplies. The voltage at  $V_{ref}$  must never be negative with respect to DGND to prevent parasitic transistor turn-on. Connections for the unipolar output operation are shown in Figure 8. The transfer values are shown in Table 3.

Figure 8. Unipolar Output Circuit

**Table 3. Unipolar Code**

| DAC LATC | H CONTENTS<br>LSB | ANALOG OUTPUT                                                    |

|----------|-------------------|------------------------------------------------------------------|

| 1111     | 1111              | + V <sub>ref</sub> (255/256)                                     |

| 1000     | 0001              | $+ V_{ref} \left( \frac{129}{256} \right)$                       |

| 1000     | 0000              | $+ V_{ref} \left( \frac{128}{256} \right) = + \frac{V_{ref}}{2}$ |

| 0111     | 1111              | + $V_{ref} \left( \frac{127}{256} \right)$                       |

| 0000     | 0001              | $+ V_{ref} \left( \frac{1}{256} \right)$                         |

| 0000     | 0000              | 0 V                                                              |

NOTE 3: 1 LSB =

$$\left(V_{\text{ref}} \ 2^{-8}\right) = V_{\text{ref}} \left(\frac{1}{256}\right)$$

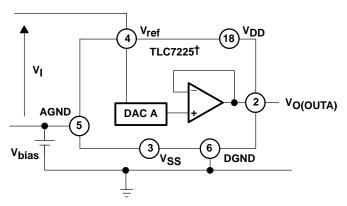

### AGND bias for direct bipolar-output operation

The TLC7225 can be used in bipolar operation without adding additional external operational amplifiers as shown in Figure 9 by biasing AGND to V<sub>SS</sub>. This configuration provides an excellent method for providing a direct bipolar output with no additional components. The transfer values are shown in Table 4.

<sup>†</sup> Digital inputs omitted for clarity.

Figure 9. AGND Bias for Direct Bipolar-Output Operation

Table 4. Bipolar (Offset Binary) Code

| DAC LATC<br>MSB | H CONTENTS<br>LSB | ANALOG OUTPUT                                     |

|-----------------|-------------------|---------------------------------------------------|

| 1111            | 1111              | + V <sub>ref</sub> (127/128)                      |

| 1000            | 0001              | $+ V_{ref} \left( \frac{1}{128} \right)$          |

| 1000            | 0000              | 0 V                                               |

| 0111            | 1111              | $- V_{ref} \left( \frac{1}{128} \right)$          |

| 0000            | 0001              | $-V_{ref}\left(\frac{127}{128}\right)$            |

| 0000            | 0000              | $-V_{ref}\left(\frac{128}{128}\right) = -V_{ref}$ |

### AGND bias for positive output offset

The TLC7225 AGND terminal can be biased above or below the system ground terminal, DGND, to provide an offset-zero analog-output voltage level. Figure 10 shows a circuit configuration to achieve this for channel A of the TLC7225. The output voltage, V<sub>O</sub> at OUTA, can be expressed as:

$$V_{O} = V_{bias} + D_{A} (V_{I})$$

Where  $D_A$  is a fractional representation of the digital input word (0  $\leq$  D  $\leq$  255/256).

† Digital inputs omitted for clarity.

Figure 10. AGND Bias Circuit

Increasing AGND above system GND reduces the output range.  $V_{DD} - V_{ref}$  must be at least 4 V to ensure specified operation. Since the AGND terminal is common to all four DACs, this method biases up the output voltages of all the DACs in the TLC7225. Supply voltages  $V_{DD}$  and  $V_{SS}$  for the TLC7225 should be referenced to DGND.

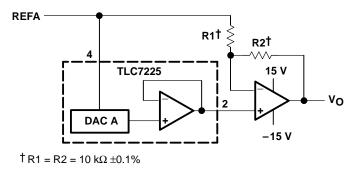

#### bipolar-output operation using external amplifier

Each of the DACs of the TLC7225 can also be individually configured to provide bipolar output operation using an external amplifier and two resistors per channel. Figure 11 shows a circuit used to implement offset binary coding (bipolar operation) with DAC A of the TLC7225. In this case (see equation 1):

$$V_{O} = 1 + \frac{R2}{R1} \left( D_{A} V_{ref} \right) - \frac{R2}{R1} \left( V_{ref} \right)$$

(1)

With R1 = R2

$$V_O = (2D_A - 1) V_{ref}$$

Where  $\mathbf{D}_{\Delta}$  is a fractional representation of the digital word in latch A.

Mismatch between R1 and R2 causes gain and offset errors. Therefore, these resistors must match and track over temperature. The TLC7225 can be operated with a single supply or from positive and negative supplies.

Figure 11. Bipolar-Output Circuit

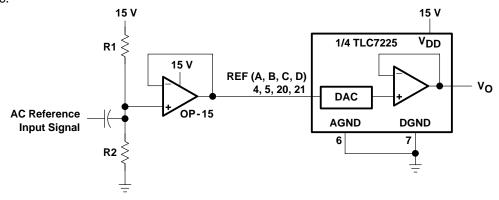

#### multiplying DAC using AC input to the REF terminals

The TLC7225 can be used as a multiplying DAC when the reference signal is maintained between 2 V and  $V_{DD}$  –4 V. When this configuration is used,  $V_{DD}$  should be 14.25 V to 15.75 V. A low output-impedance buffer should be used so that the input signal is not loaded by the resistor ladder. Figure 12 shows the general schematic.

Figure 12. AC Signal-Input Scheme

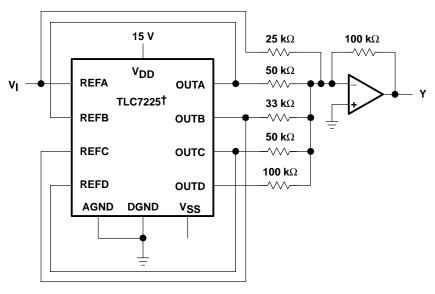

#### digital word multiplication

Since each DAC of the TLC7225 has a separate reference input, the output of one DAC can be used as the reference input for another. Therefore, multiplication of digital words can be performed (with the result given in analog form). For example, when the output from DACA is applied to V<sub>REF</sub> B then the output from DACB, V<sub>OLT</sub> B, can be expressed as given in equation 2:

$$V_{OUT} B = (D_A) (D_B) (V_{REF} A)$$

(2)

where  $D_A$  and  $D_B$  are the fractional representations of the digital words in DAC latches A and B respectively.

If

$$D_A = D_B = D$$

then the result is  $D^2 (V_{REF} A)$

In this manner, the four DACs can be used on their own or in conjunction with an external summing amplifier to generate complex waveforms. Figure 13 shows one such application with the output waveform, Y, which is represented by equation 3:

$$Y = -(x^4 + 2x^3 + 3x^2 + 2x + 4) V_{IN}$$

(3)

where x is the digital code that is applied to all four DAC latches.

<sup>†</sup> Digital inputs omitted for clarity

Figure 13. Complex-Waveform Generation

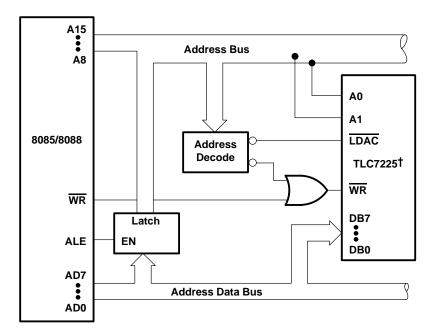

# microprocessor interface

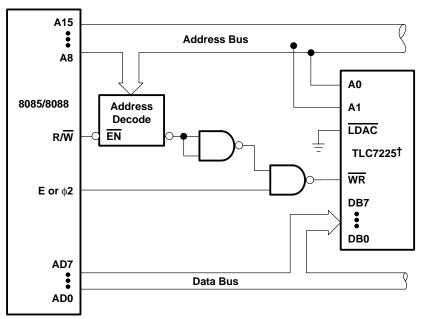

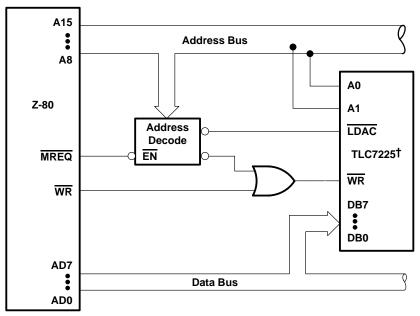

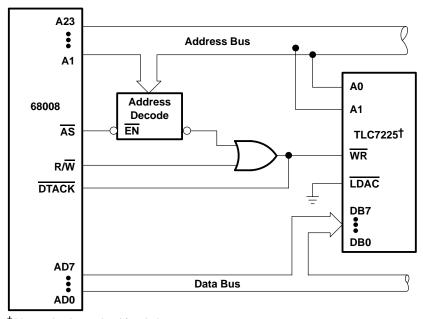

Figures 14, 15, 16, and 17 show the hardware interface to some of the standard processors.

†Linear circuitry omitted for clarity

Figure 14. TLC7225 to 8085A/8088 Interface, Double-Buffered Mode

†Linear circuitry omitted for clarity

Figure 15. TLC7225 to 6809/6502 Interface, Single-Buffered Mode

<sup>†</sup>Linear circuitry omitted for clarity

Figure 16. TLC7225 to Z-80 Interface, Double-Buffered Mode

<sup>†</sup>Linear circuitry omitted for clarity

Figure 17. TLC7225 to 68008 Interface, Single-Buffered Mode

#### **APPLICATION INFORMATION**

#### linearity, offset, and gain error using single-ended supplies

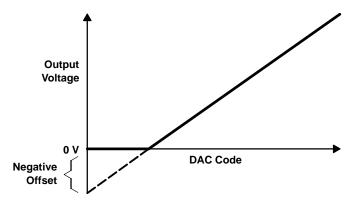

When an amplifier is operated from a single supply, the voltage offset can still be either positive or negative. With a positive offset, the output voltage changes on the first code change. With a negative offset the output voltage may not change with the first code depending on the magnitude of the offset voltage.

The output amplifier attempts to drive the output to a negative voltage. However, since the most negative supply rail is ground, the output cannot drive to a negative voltage.

So when the output offset voltage is negative, the output voltage remains at zero until the input-code value produces a sufficient output voltage to overcome the inherent negative offset voltage, resulting in a transfer function shown in Figure 18.

Figure 18. Effect of Negative Offset (Single Supply)

This offset error, not the linearity error, produces this breakpoint. The transfer function would have followed the dotted line if the output buffer could drive below ground.

For a DAC, linearity is measured between zero-input code (all inputs 0) and full-scale code (all inputs 1) after offset and full scale is adjusted out or accounted for in some way. However, single supply operation does not allow for adjustment when the offset is negative due to the breakpoint in the transfer function. So the linearity in the unipolar mode is measured between full-scale code and the lowest code, which produces a positive output voltage.

The code is calculated from the maximum specification for the zero offset error.

#### **IMPORTANT NOTICE**

Texas Instruments (TI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

TI warrants performance of its semiconductor products and related software to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Certain applications using semiconductor products may involve potential risks of death, personal injury, or severe property or environmental damage ("Critical Applications").

TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

Inclusion of TI products in such applications is understood to be fully at the risk of the customer. Use of TI products in such applications requires the written approval of an appropriate TI officer. Questions concerning potential risk applications should be directed to TI through a local SC sales office.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards should be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

Copyright © 1996, Texas Instruments Incorporated