# SN75C091A SCSI Bus Controller

**Data Manual**

# 1 Introduction

## 1.1 Description

The SN75C091A provides the capability to interface a microprocessor subsystem to the ANSI Small Computer Systems Interface (SCSI). This single-ended SCSI implementation acts as one of up to eight nodes communicating over a maximum six-meter bus as detailed in the SCSI specification (ANSI X3.131-1986). Its microprocessor and DMA interfaces allow the SN75C091A SCSI Bus Controller (SBC) to be used in a variety of host or peripheral applications.

This document is not intended to serve as a tutorial on the Small Computer Systems Interface bus; users should refer to ANSI X3.131-1986 for detailed information regarding the SCSI bus.

#### 1.2 Features

#### 1.2.1 SCSI Bus Interface

- Complies with ANSI X3.131-1986 SCSI standard

- Performs INITIATOR and TARGET functions

- Supports arbitration, selection, and reselection

- Performs asynchronous data transfers of up to 5 Megabytes/second (MBps)

- Performs synchronous data transfers of up to 5 Megabytes/second (MBps) with programmable offset up to 15

- Has on-chip 48-mA transceivers

- Provides optional parity generation, checking, and pass-through

- Reduces overhead associated with initiator multi-threading by automatically handling savedata-pointer messages, disconnects, and reconnects

- Performs automatic message and command-length decoding

- Has two 32-byte FIFOs for command and message preloading

#### 1.2.2 Microprocessor Interface

- Provides chip control via directly-addressable registers

- Has optional address latch line for multiplexed address/data buses

- Allows DMA- or programmed-I/O data transfers

- Is interrupt-driven to minimize host polling

- Can execute multi-phase commands to minimize interrupts

- Has 24-bit transfer counter

- Provides byte-stacking control to accommodate 8-, 16-, and 32-bit systems

- Offers optional parity generation and checking

- Is equipped with separate ports for DMA and microprocessor interfacing

#### 1.2.3 General

- Requires a single 5 V ± 5% power supply

- Low-power CMOS technology

- 68-pin PLCC package

#### 2 Architecture

# 2.1 Block Diagram

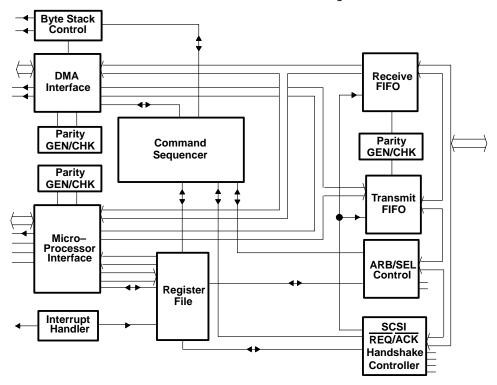

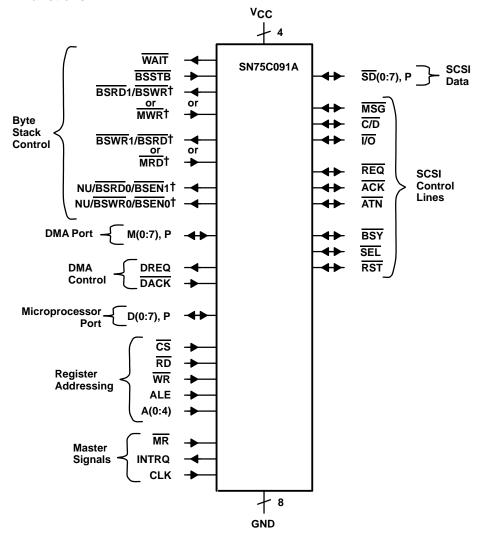

The functional block architecture of the SN75C091A is as shown in Figure 2–1 below:

Figure 2-1. SN75C091A Functional Block Architecture

#### 2.1.1 Command Sequencer

The heart of the SN75C091A is a large state machine called the command sequencer. Microprocessor commands to the SN75C091A are interpreted by the command sequencer, which then activates subordinate state machines (e.g. the arbitration controller, REQ/ACK handshake controller, and DMA interface controller) to perform the functions necessary to carry out each command. The command sequencer enables the SN75C091A to execute powerful multiphase SCSI sequences with very few interrupts.

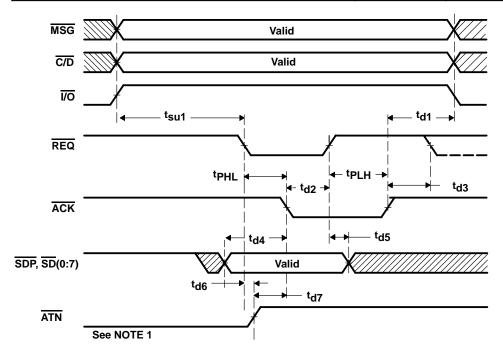

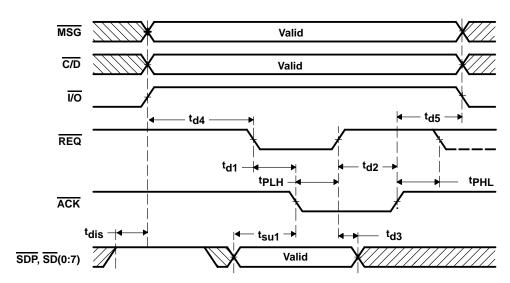

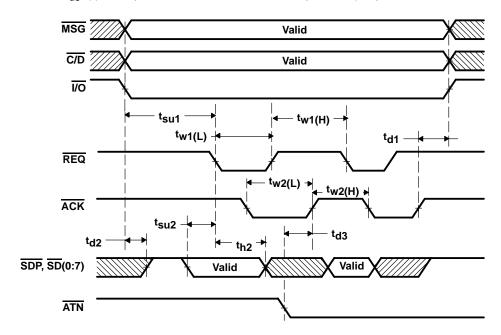

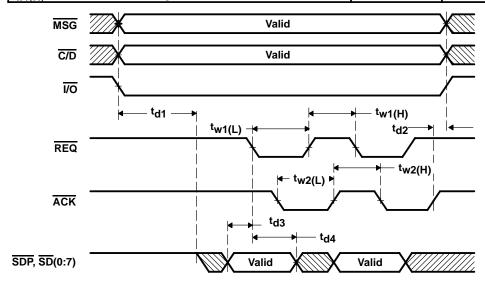

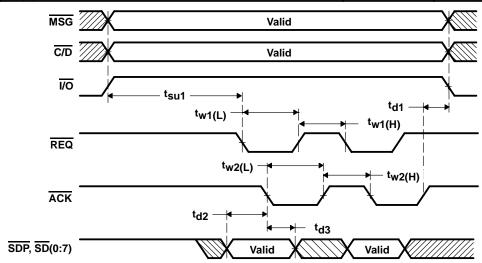

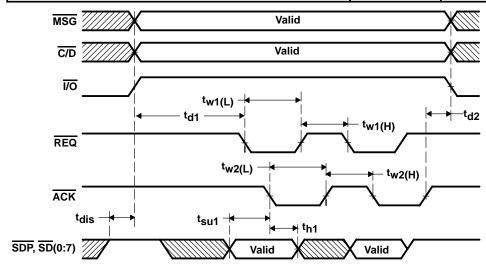

# 2.1.2 SCSI REQ/ACK Handshake Controller

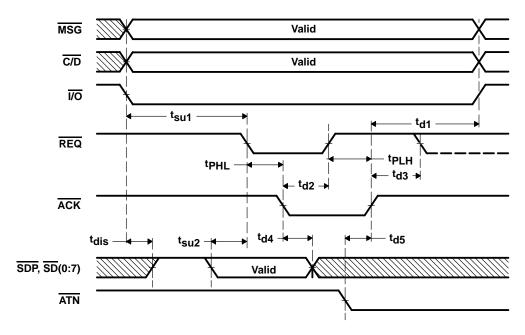

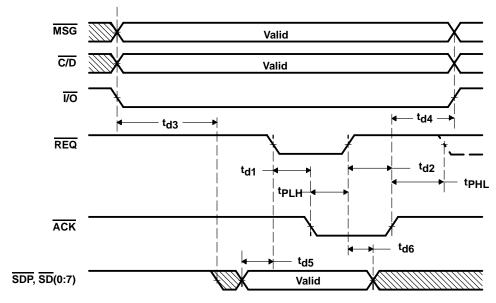

The REQ/ACK handshake controller handles requests from the command sequencer to perform single SCSI phase transfers such as Message, Command, Status, and Data. REQ, ACK, ATN, MSG, C/D and I/O are controlled and/or monitored (depending on the mode, target or initiator) to transfer information between the transmit and receive FIFOs and the SCSI bus. The REQ/ACK handshake controller supports both synchronous and asynchronous data transfers.

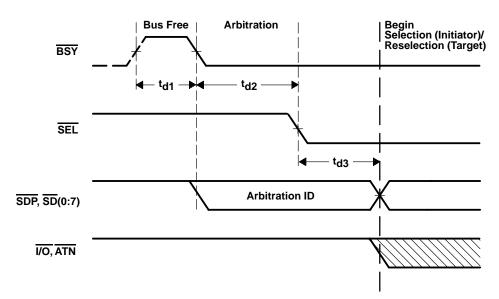

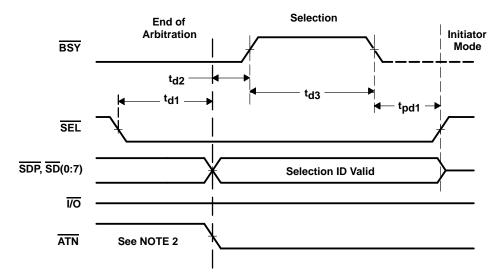

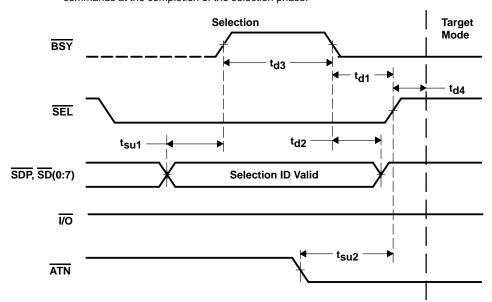

#### 2.1.3 Arbitration and Selection Controller

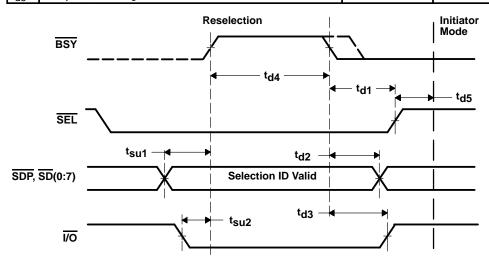

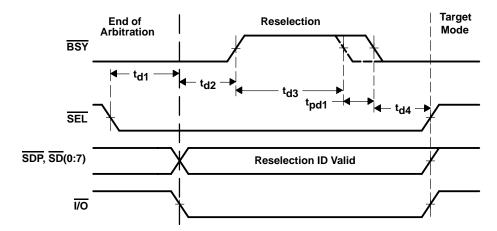

The arbitration and selection controller handles requests from the <u>command sequencer</u> to establish a connection with another device on the SCSI bus. SCSI bus signals BSY, SEL, I/O and ATN are controlled and/or monitored to effect automatic completion of SCSI arbitration, selection, and reselection phases. This state machine also concurrently monitors the SCSI bus and alerts the command sequencer and interrupt logic if the SN75C091A has been selected or reselected by another device on the SCSI bus.

#### 2.1.4 Register File

The register file consists of 32 registers which allow the local microprocessor to initiate, control, and monitor SCSI transfer operations performed by the SN75C091A. The 32-byte transfer and receive FIFOs can also be accessed through the register file.

#### 2.1.5 Microprocessor Interface

The microprocessor interface provides the logic necessary for a microprocessor or other host computer system to access and store information in the register file. Both multiplexed and nonmultiplexed address/data buses are supported through this interface.

#### 2.1.6 Receive and Transmit FIFOs

These 32-byte by 9-bit FIFOs provide a buffer between the SCSI bus and memory to improve transfer efficiency and minimize microprocessor overhead. These FIFOs are accessed in the same manner as a register in the register file: through the microprocessor interface for programmed I/O or through the DMA interface for SCSI data transfers performed via an intermediate DMA controller. The 32-byte FIFOs allow SCSI commands and messages to be preloaded or fully received, thus minimizing microprocessor intervention. The ninth bit allows parity pass-through mode for high-reliability systems.

#### 2.1.7 Interrupt Control

Interrupt control logic monitors the various state machines to determine when microprocessor intervention is required. Interrupt status information is maintained in the register file and the interrupt is reported either by microprocessor polling or via the INTRQ signal (if external interrupts are enabled).

#### 2.1.8 DMA Interface

The DMA interface provides the control logic necessary to interface the SN75C091A with an external DMA controller. DMA handshake signals DREQ and DACK and a separate 9-bit data port form the data path used to transfer SCSI data between external memory and the SN75C091A transmit and receive FIFOs without microprocessor intervention.

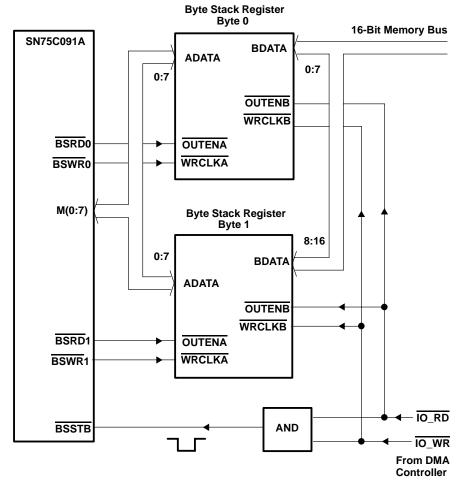

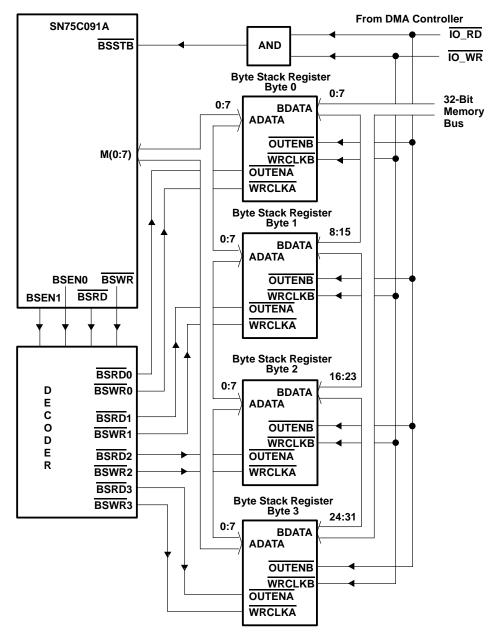

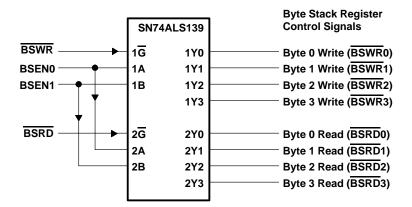

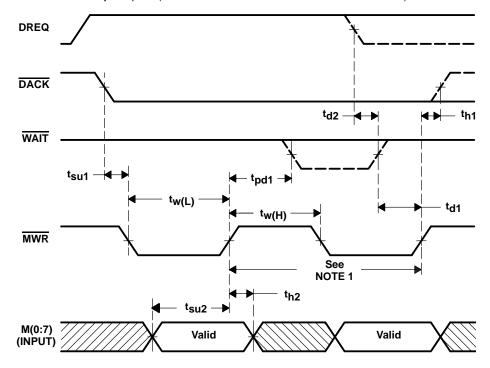

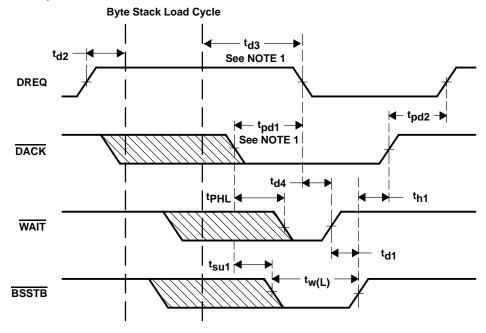

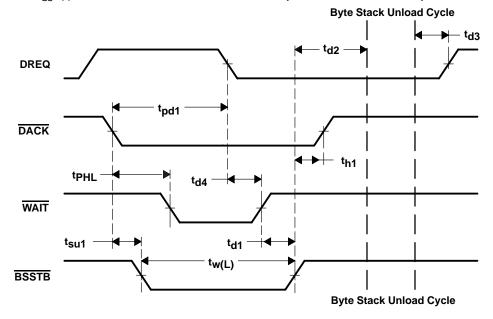

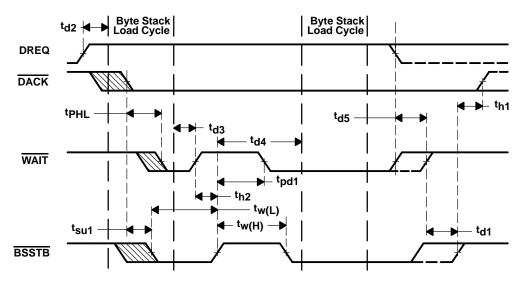

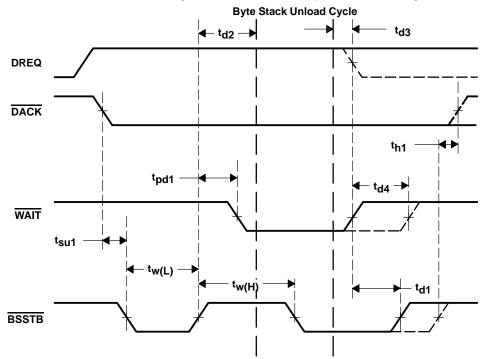

# 2.1.9 Byte Stack Control

The byte stack control is used in conjunction with the DMA interface to allow easy interfacing of the 8-bit SCSI bus to 16-, 24-, and 32-bit systems. This control logic facilitates loading and unloading of external bidirectional registers (byte stack registers) so that 16-, 24-, and 32-bit words can be broken down into their constituent bytes. No external logic is required to interface the SN75C091A to a 16-bit bytestack register; a decoder is necessary for interfacing to 24- and 32-bit systems.

#### 2.1.10 Parity Generators/Checkers

Parity generation and checking is provided for all three SN75C091A ports (SCSI, DMA, and microprocessor). Versatile parity control via the register file allows the SN75C091A to adapt easily to any system. Parity generation control allows memory and SCSI parity information to be passed through the FIFOs. User-selectable parity sense (odd or even) provides error generation capabilities to assist in system checkout.

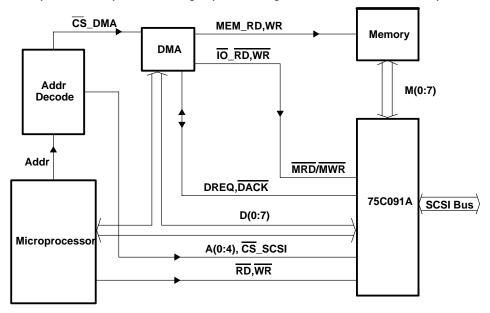

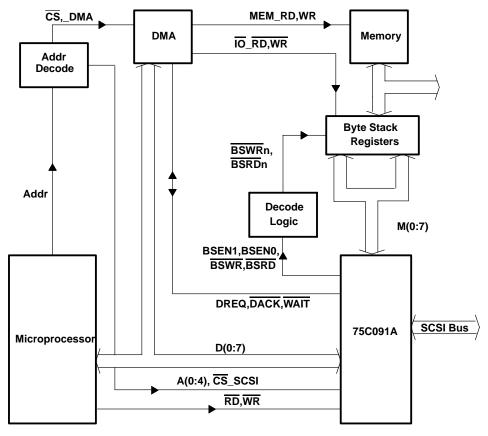

# 2.2 Data Path Examples

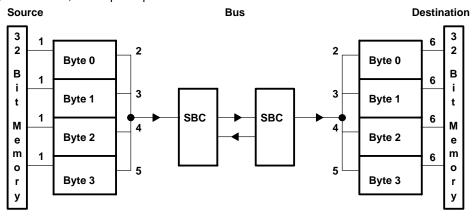

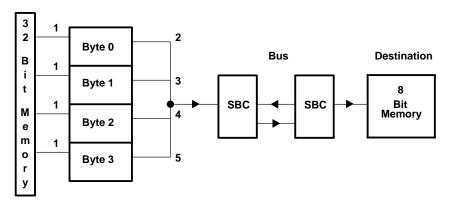

The SN75C091A provides a microprocessor port for information transfer and chip control. A separate DMA port is also provided for SCSI data transfers between memory and the SCSI bus. The DMA port may be connected directly to an 8-bit system or through byte stack registers to 16-, 24-, and 32-bit systems.

Figure 2-2. Data Paths (No Byte Stacking)

NOTE: For 16-bit byte stack operation, no decode logic is required to produce BSWRn and BSRDn. These signals are decoded internally to minimize the external logic required for this application.

Figure 2-3. Data Paths (With Byte Stacking)

# 2.3 Pin Assignments and Functions

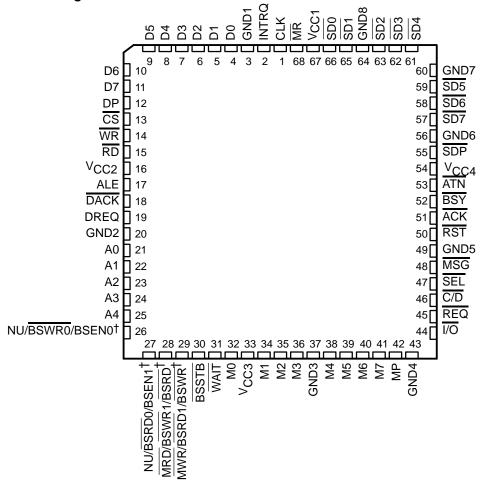

# 2.3.1 Pin Assignments

NU - make no external connection

Figure 2-4. SN75C091A Pin Assignments

<sup>&</sup>lt;sup>†</sup> Use of these pins varies depending on whether non-byte-stack, 16-bit byte stack, or 24-/32-bit byte stack mode is being used. See Section 2.4.2, DMA Interface Signals, for details.

#### 2.3.2 Pin Functions

NU - Make no external connection

Figure 2-5. SN75C091A Pin Functions

<sup>&</sup>lt;sup>†</sup> Use of these pins varies depending on whether non-byte-stack, 16-bit byte stack, or 24-/32-bit byte stack mode is being used. See Section 2.4.2, DMA Interface Signals, for details.

# 2.4 Pin Functional Descriptions

The following tables describe the function of the SN75C091A signals. Local processor and DMA signals are presented first, followed by SCSI bus control and miscellaneous signals.

# 2.4.1 Microprocessor Interface Signals

|                             | •         | ~                                                   |     | 91A SIGNALS<br>ESSOR INTERFACE                                                                                                                                                      |  |  |  |

|-----------------------------|-----------|-----------------------------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| PIN NO.                     | MNEMONIC  | SIGNAL NAME                                         | 1/0 | FUNCTION                                                                                                                                                                            |  |  |  |

| 1                           | CLK       | Clock                                               | I   | Clock used for timing and internal control. This clock must meet chip specifications in order to produce proper timing to meet the SCSI specification. Nominal frequency is 20 MHz. |  |  |  |

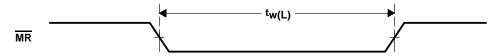

| 68                          | MR        | Mister Reset                                        | ļ   | MR places the SN75C091A into an idle state with all signals in the passive mode.                                                                                                    |  |  |  |

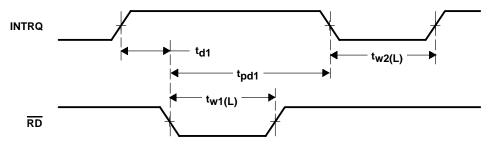

| 2                           | INTRQ     | Interrupt Request                                   | 0   | Indicates to the host or local processor that the interrupt registers should be read.                                                                                               |  |  |  |

| 4, 5, 6, 7,<br>8, 9, 10, 11 | D(0:7)    | Data 0 through<br>Data 7                            | I/O | Local processor data bus bits 0 through 7.                                                                                                                                          |  |  |  |

| 12                          | DP        | Parity                                              | I/O | Parity bit for the local processor data bus.                                                                                                                                        |  |  |  |

| 13                          | <u>cs</u> | Chip Select                                         | I   | Asserted by the processor to enable access to the register file or FIFOs.                                                                                                           |  |  |  |

| 14                          | WR        | Write Enable                                        | I   | When asserted in conjunction with $\overline{\text{CS}}$ , latches data into the register file on the rising edge.                                                                  |  |  |  |

| 15                          | RD        | Read Emab;e                                         | I   | Used in conjunction with CS to read from the register file.                                                                                                                         |  |  |  |

| 17                          | ALE       | Address Latch<br>Enable                             | ı   | On the falling edge of ALE, address on A(0:4) is latched into address register for multiplexed address/data buses. For non-multiplexed address/data buses, ALE should be tied high. |  |  |  |

| 21, 22, 23,<br>24, 25       | A(0:4)    | Register Address<br>0 through Register<br>Address 4 | I   | Address bit 0 (least significant bit) of the register file through address bit 4 (most significant bit) of the register file.                                                       |  |  |  |

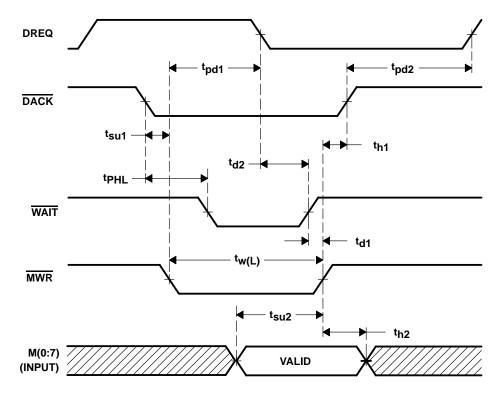

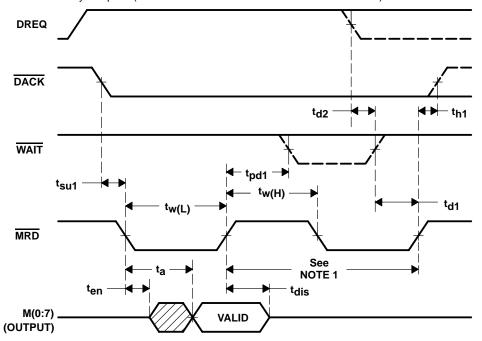

# 2.4.2 DMA Interface Signals

|                                      | SN75C091A SIGNALS<br>DMA INTERFACE |                          |     |                                                                                                                                                                                          |  |  |  |  |  |  |  |

|--------------------------------------|------------------------------------|--------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| PIN NO.                              | MNEMONIC                           | SIGNAL NAME              | 1/0 | FUNCTION                                                                                                                                                                                 |  |  |  |  |  |  |  |

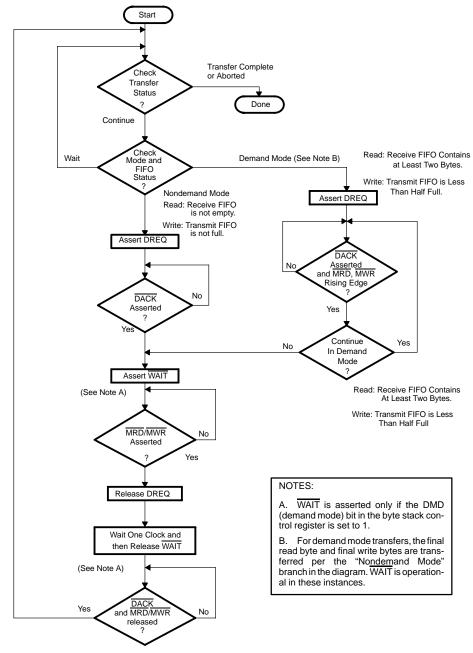

| 19                                   | DREQ                               | DMA Request              | 0   | DREQ interfaces with an external DMA controller and forms the handshake for data transfers.                                                                                              |  |  |  |  |  |  |  |

| 18                                   | DACK                               | DMA<br>Acknowledge       | Ι   | DACK interfaces with an external DMA controller and is the response to DREQ. Data is read or written from/to the FIFOs while DACK is asserted.                                           |  |  |  |  |  |  |  |

| 32, 34, 35,<br>36, 38, 39,<br>40, 41 | M(0:7)                             | DMA Port<br>Data Bus     | I/O | DMA port data bits 0 through 7. This bus is an alternate path into the transmit and receive FIFOs.                                                                                       |  |  |  |  |  |  |  |

| 42                                   | MP                                 | DMA Port Parity          | I/O | Parity for DMA port.                                                                                                                                                                     |  |  |  |  |  |  |  |

| 31                                   | WAIT                               | Processor Wait<br>Enable | 0   | Signals the DMA to wait when the FIFO status is inappropriate for loading or unloading in DMA demand mode. Also used to suspend DMA activity while the byte stack is loaded or unloaded. |  |  |  |  |  |  |  |

| 30                                   | BSSTB                              | Byte Stack<br>Strobe     |     | Informs the byte stack control logic that a read or write from the byte stack register has been completed. For 8-bit mod BSSTB should be tied high.                                      |  |  |  |  |  |  |  |

The following DMA interface pins have different functions depending on whether the chip is in byte stack or non-byte-stack mode. Also, their byte stack mode functions vary with byte stack width (16, 24, or 32 bits).

|         | SN75C091A SIGNALS<br>DMA INTERFACE (8-BIT NON-BYTE-STACK MODE) |                          |     |                                                                                                                  |  |  |  |  |  |

|---------|----------------------------------------------------------------|--------------------------|-----|------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| PIN NO. | MNEMONIC                                                       | SIGNAL NAME              | 1/0 | FUNCTION                                                                                                         |  |  |  |  |  |

| 29      | MWR                                                            | DMA Port Write<br>Enable | I   | MWR is used with DACK to write to the transmit FIFO through the DMA port. Data is latched on rising edge of MWR. |  |  |  |  |  |

| 28      | MRD                                                            | DMA Port Read<br>Enable  | I   | MRD is used with DACK to read from the receive FIFO through the DMA port.                                        |  |  |  |  |  |

| 27, 26  | n/a                                                            | n/a                      | 0   | Not used in 8-bit mode.                                                                                          |  |  |  |  |  |

|         | SN75C091A SIGNALS<br>DMA INTERFACE (16-BIT MODE) |                            |     |                                                                                           |  |  |  |  |  |  |  |

|---------|--------------------------------------------------|----------------------------|-----|-------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| PIN NO. | MNEMONIC                                         | SIGNAL NAME                | 1/0 | FUNCTION                                                                                  |  |  |  |  |  |  |  |

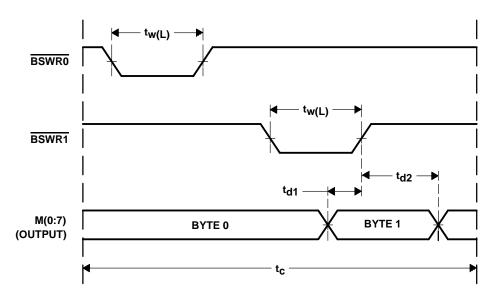

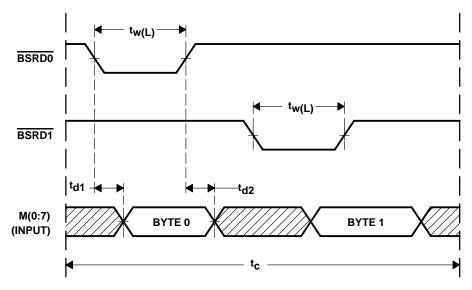

| 29      | BSRD1                                            | Byte Stack<br>Read-Byte 1  | 0   | Enables byte stack register byte 1 onto $M(0:7)$ , MP for loading into the transmit FIFO. |  |  |  |  |  |  |  |

| 28      | BSWR1                                            | Byte Stack<br>Write-Byte 1 |     | Loads receive FIFO byte into byte stack register byte 1 on rising edge.                   |  |  |  |  |  |  |  |

| 27      | BSRD0                                            | Byte Stack<br>Read-Byte0   | 0   | Enables byte stack register byte 0 onto M(0:7), MP for loading into the transmit FIFO.    |  |  |  |  |  |  |  |

| 26      | BSWR0                                            | Byte Stack<br>Write-Byte 0 | 0   | Loads receive FIFO byte into byte stack register byte 0 on risin edge.                    |  |  |  |  |  |  |  |

|         | SN75C091A SIGNALS<br>DMA INTERFACE (24- OR 32-BIT MODE) |                           |   |                                                                                               |  |  |  |  |  |  |

|---------|---------------------------------------------------------|---------------------------|---|-----------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| PIN NO. | PIN NO.   MNEMONIC   SIGNAL NAME   I/O   FUNCTION       |                           |   |                                                                                               |  |  |  |  |  |  |

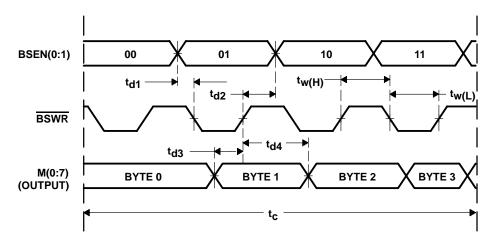

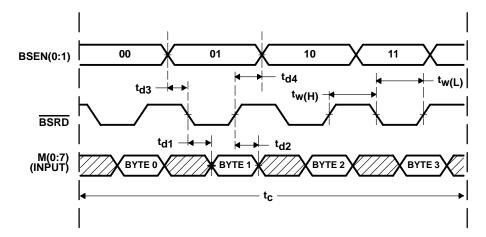

| 29      | BSWR                                                    | Byte Stack Write          | 0 | Loads receive FIFO byte into selected byte stack register byte on rising edge.                |  |  |  |  |  |  |

| 28      | BSRD                                                    | Byte Stack Read           | 0 | Enables selected byte stack register byte onto M(0:7), MP for loading into the transmit FIFO. |  |  |  |  |  |  |

| 27, 26  | BSEN1-<br>BSEN0                                         | Byte Stack Byte<br>Enable | 0 | Encoded value of selected byte stack register byte to be enabled for read or write.           |  |  |  |  |  |  |

# 2.4.3 SCSI Bus Interface Signals

|                                         | SN75C091A SIGNALS<br>SCSI BUS INTERFACE |                                       |     |                                                                                                                                  |  |  |  |  |  |  |  |  |

|-----------------------------------------|-----------------------------------------|---------------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| PIN NO.                                 | MNEMONIC                                | SIGNAL NAME                           | I/O | FUNCTION                                                                                                                         |  |  |  |  |  |  |  |  |

| 48                                      | MSG                                     | Message                               | I/O | MSG, C/D, and I/O are the SCSI bus phase signals used to                                                                         |  |  |  |  |  |  |  |  |

| 46                                      | C/D                                     | Command/Data                          | I/O | determine the type and direction of a transfer. They are driven                                                                  |  |  |  |  |  |  |  |  |

| 44                                      | Ī/O                                     | Input/Output                          | I/O | by a target and received by an initiator.                                                                                        |  |  |  |  |  |  |  |  |

| 52                                      | BSY                                     | Busy                                  | I/O | Drives and monitors the BSY line of the SCSI bus.                                                                                |  |  |  |  |  |  |  |  |

| 47                                      | SEL                                     | Se;ect                                | I/O | Drives and monitors the SEL line of the SCSI bus.                                                                                |  |  |  |  |  |  |  |  |

| 50                                      | RST                                     | SCSI Reset                            | I/O | Drives and monitors the RST line of the SCSI bus.                                                                                |  |  |  |  |  |  |  |  |

| 45                                      | REQ                                     | Request                               | I/O | REQ starts the REQ/ACK handshake. It is driven by the target and received by the initiator.                                      |  |  |  |  |  |  |  |  |

| 51                                      | ACK                                     | Acknowledge                           | I/O | ACK answers the REQ/ACK information handshake. It is driven by the initiator and received by the target.                         |  |  |  |  |  |  |  |  |

| 53                                      | ATN                                     | Attention                             | I/O | ATN indicates to the target that the initiator has a message to send. ATN is driven by the initiator and received by the target. |  |  |  |  |  |  |  |  |

| 55                                      | SDP                                     | SCSI Data Parity                      | I/O | SCSI bus data parity line.                                                                                                       |  |  |  |  |  |  |  |  |

| 66, 65,<br>63, 62,<br>61, 59,<br>58, 57 | SD(0:7)                                 | SCSI Data 0<br>through<br>SCSI Data 7 | I/O | SCSI bus data bit 0 through SCSI bus data bit 7.                                                                                 |  |  |  |  |  |  |  |  |

# 2.4.4 Miscellaneous Signals

|                                                                  | SN75C091A SIGNALS<br>MISCELLANEOUS      |        |  |                  |  |  |  |  |  |

|------------------------------------------------------------------|-----------------------------------------|--------|--|------------------|--|--|--|--|--|

| PIN#                                                             | PIN # MNEMONIC SIGNAL NAME I/O FUNCTION |        |  |                  |  |  |  |  |  |

| 3, 20, 37,<br>43, 49, 56,<br>60, 64                              | GND                                     | Ground |  | Ground reference |  |  |  |  |  |

| 67, 16, 33, V <sub>CC</sub> V <sub>CC</sub> 5 V ±5% power supply |                                         |        |  |                  |  |  |  |  |  |

# 3 Internal Registers

#### 3.1 General

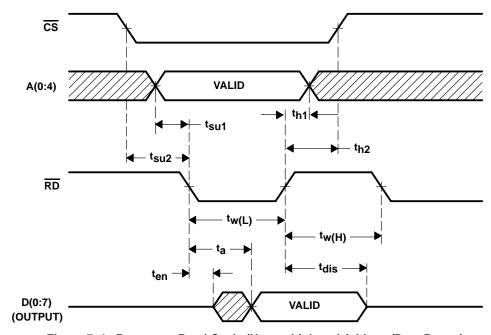

The local microprocessor directs the operation of the SCSI bus controller (SBC) through a set of registers internal to the SBC. For nonmultiplexed address/data bus systems, these registers are read or written by asserting CS with the proper address on A(0:4) and then asserting RD or WR. For multiplexed systems, the address and chip select are latched internally using ALE; the read or write strobes can then be applied. The following table lists the register addresses; subsequent paragraphs describe the functions of the various registers. (Note: many of the register function descriptions state that the register is set to all zeros by a master reset. "Master reset" in this context means either that the microprocessor has sent a Chip Reset command to the SBC or that the MR (master reset) line has been asserted.)

|    |    |    |            |    | REGISTER AI | DDRESSES                                  |

|----|----|----|------------|----|-------------|-------------------------------------------|

| A4 | А3 | A2 | <b>A</b> 1 | A0 | READ/WRITE  | REGISTER                                  |

| 0  | 0  | 0  | 0          | 0  | R           | Receive FIFO                              |

| 0  | 0  | 0  | 0          | 0  | W           | Transmit FIFO                             |

| 0  | 0  | 0  | 0          | 1  | R/W         | Command                                   |

| 0  | 0  | 0  | 1          | 0  | R           | Transfer status                           |

| 0  | 0  | 0  | 1          | 1  | R           | Bus phase status                          |

| 0  | 0  | 1  | 0          | 0  | R           | Function interrupt status                 |

| 0  | 0  | 1  | 0          | 1  | R           | Error interrupt status                    |

| 0  | 0  | 1  | 1          | 0  | R/W         | Interrupt enable                          |

| 0  | 0  | 1  | 1          | 1  |             | (Reserved)                                |

| 0  | 1  | 0  | 0          | 0  | R/W         | Control                                   |

| 0  | 1  | 0  | 0          | 1  | R/W         | Byte stack control                        |

| 0  | 1  | 0  | 1          | 0  | R/W         | Parity control                            |

| 0  | 1  | 0  | 1          | 1  | R/W         | Synchronous transfer                      |

| 0  | 1  | 1  | 0          | 0  | R/W         | Selection or Reselection timeout          |

| 0  | 1  | 1  | 0          | 1  | R/W         | Self-ID                                   |

| 0  | 1  | 1  | 1          | 0  | R/W         | Destination ID                            |

| 0  | 1  | 1  | 1          | 1  | R           | Source ID                                 |

| 1  | 0  | 0  | 0          | 0  | R/W         | Target LUN                                |

| 1  | 0  | 0  | 0          | 1  | R/W         | Command state                             |

| 1  | 0  | 0  | 1          | 0  | R/W         | Transfer counter (least significant byte) |

| 1  | 0  | 0  | 1          | 1  | R/W         | Transfer counter (middle byte)            |

| 1  | 0  | 1  | 0          | 0  | R/W         | Transfer counter (most significant byte)  |

| 1  | 0  | 1  | 0          | 1  | R           | Backup counter (least significant byte)   |

| 1  | 0  | 1  | 1          | 0  | R           | Backup counter (middle byte)              |

| 1  | 0  | 1  | 1          | 1  | R           | Backup counter (most significant byte)    |

| 1  | 1  | 0  | 0          | 0  | R/W         | Offset counter                            |

|    | REGISTER ADDRESSES |    |    |    |            |                        |  |  |  |  |  |  |  |

|----|--------------------|----|----|----|------------|------------------------|--|--|--|--|--|--|--|

| A4 | А3                 | A2 | A1 | A0 | READ/WRITE | REGISTER               |  |  |  |  |  |  |  |

| 1  | 1                  | 0  | 0  | 1  |            | (Reserved)             |  |  |  |  |  |  |  |

| 1  | 1                  | 0  | 1  | 0  | R/W        | Test control           |  |  |  |  |  |  |  |

| 1  | 1                  | 0  | 1  | 1  | R          | Test points register 0 |  |  |  |  |  |  |  |

| 1  | 1                  | 1  | 0  | 0  |            | (Reserved)             |  |  |  |  |  |  |  |

| 1  | 1                  | 1  | 0  | 1  |            | (Reserved)             |  |  |  |  |  |  |  |

| 1  | 1                  | 1  | 1  | 0  |            | (Reserved)             |  |  |  |  |  |  |  |

| 1  | 1                  | 1  | 1  | 1  |            | (Reserved)             |  |  |  |  |  |  |  |

#### 3.2 Transmit and Receive FIFOs

The SN75C091A uses two 32-byte by 9-bit FIFOs to buffer SCSI bus information transfers. The Receive and Transmit FIFOs are accessed through the microprocessor port at register file hexadecimal address 00000. Writing loads a byte into the transmit FIFO through the microprocessor port; reading enables the information onto the microprocessor port and unloads the byte from the receive FIFO. By polling the transfer status register FIFO status bits, the microprocessor can determine availability of space in the transmit FIFO or data in the receive FIFO. The microprocessor should never read the receive FIFO when it is empty or write the transmit FIFO when it is full, as loss of information integrity will result. Also, the FIFOs should not be acessed during execution of a command which uses the DMA interface. Note that 32-byte FIFOs are large enough to accommodate most SCSI messages or commands, so no polling is required for these types of transfers. Transmit and Receive FIFO pointers are reset by a master reset or by the appropriate FIFO clear command.

| Parity | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|--------|---|---|---|---|---|---|---|---|

|        |   |   |   |   |   |   |   |   |

#### 3.3 Command Register

The command register is an eight-bit read/write register that stores chip commands written by the microprocessor. Each command is executed immediately upon being sent to the chip. Generally, the microprocessor should not issue a new command to the SN75C091A while the previously issued command is still active (for exceptions, see Section 4, Commands). The command register is set to all zeros by a master reset.

| 7   | 6   | 5    | 4   | 3   | 2   | 1   | 0   | _ |

|-----|-----|------|-----|-----|-----|-----|-----|---|

| DMA | M/A | DDIR | CC4 | CC3 | CC2 | CC1 | CC0 | l |

**DMA:** Direct Memory Access. This bit controls the mode of data transfer from the SCSI bus to the microprocessor or DMA bus. When set low, the interface uses programmed I/O. When set high, DMA transfers are enabled. The microprocessor should not access the FIFOs until the command is complete if DMA transfers are enabled.

**M/A**: Manual/Automatic. This bit allows the microprocessor to manually control the number of bytes transferred during a command or message phase. When this bit is set to one, the count written to the offset counter by the microprocessor is used to determine the transfer length of the command or message phase. When this bit is set to zero, the group code of a command or the second byte of an extended message is decoded to determine a count value to be automatically loaded into the offset counter. Automatic mode eliminates the need for software to decode the command or message prior to completing the transfer. Manual mode may be used to complete a phase which was terminated prematurely.

**DDIR:** Data DIRection. This bit establishes the direction of data transfer during Select with- or Select without- ATN and Transfer commands. When DDIR is set low, a data-out phase is expected; when set high, a data-in phase is expected. If the data phase set up by the target does not match that expected by the initiator, a bus service interrupt is generated and the command stops.

CC4-CC0: Command codes (see Section 4, Commands).

# 3.4 Transfer Status Register

The transfer status register is an eight-bit read-only register that stores bits which reflect the operational state of the chip.

| 7   | 6   | 5    | 4   | 3    | 2   | 1   | 0     |

|-----|-----|------|-----|------|-----|-----|-------|

| INT | RFE | RFHF | TFF | TFHF | TC0 | OC0 | CDACT |

**INT:** INTerrupt pending. When set to 1, this bit indicates that an interrupt condition is pending (i.e., one or more bits in either the functional interrupt status register or error interrupt status register are set to 1). This bit is provided for systems which detect pending interrupt conditions through the use of a polling scheme rather than by monitoring the external INTRQ line (see description of MIE bit in the Interrupt Enable Register description). If INT is set to 1, the microprocessor must read the functional interrupt status register before issuing a command (the error interrupt status register may also need to be read). This bit is set to 0 when all interrupts in both interrupt registers have been cleared.

**RFE:** Receive Fifo Empty. This bit indicates the state of the receive FIFO during incoming information transfers. When this bit is set to 1, either no bytes have been received from the bus or all bytes that had been received have already been read. RFE is also set to 1 by a master reset. When RFE is set to 0, some bytes remain to be read from the FIFO.

**RFHF:** Receive Fifo Half Full. This bit is set to 1 if the receive FIFO contains sixteen or more bytes, and is set to 0 otherwise. It is also set to 0 by a master reset.

**TFF:** Transmit Fifo Full. This bit indicates the state of the transmit FIFO during outgoing information transfers. When this bit is set to 1, the FIFO is full and no more bytes may be written to it; when set to 0, the FIFO has room to accept more bytes.TFF is also set to 0 by a master reset.

**TFHF:** Transmit Fifo Half Full. This bit is set to 1 if the transmit FIFO contains sixteen or more bytes, and is set to 0 otherwise. It is also set to 0 by a master reset.

**TC0:** Transfer Counter Zero. This bit is set to1 whenever the transfer counter is zero.

**OCO:** Offset Counter Zero. This bit is set to 1 whenever the offset counter is zero.

**CDACT:** CommanD ACTive. This bit, when set to 1, indicates that an interrupting command is being executed. Only the command, transfer status, or bus phase status registers or the transmit/receive FIFOs should be accessed while this bit is set to 1.

#### 3.5 Bus Phase Status Register

The bus phase status register is an eight-bit read-only register that stores bits which reflect the operational state of the chip and the present SCSI bus phase.

| 7    | 6    | 5 | 4   | 3   | 2   | 1   | 0    |

|------|------|---|-----|-----|-----|-----|------|

| INIT | TARG | 0 | ATN | MSG | C/D | 1/0 | SRST |

**INIT:** INITiator. This bit is set to 1 whenever the chip is logically connected as an initiator. It is set to 0 upon target disconnection, by a master reset, or by a SCSI reset.

**TARG:** TARGet. This bit is set to 1 whenever the chip is logically connected as a target. It is set to 0 at disconnection (disconnect command or multiphase command internal disconnect), by a master reset, or by a SCSI reset.

**ATN:** If the ATNDS (attention disable) bit in the control register is set to 0, this active-high bit represents the state of the SCSI bus line ATN.

$\overline{\text{MSG}}$ , C/D, I/O: These three active-high bits represent the state of the SCSI bus phase lines  $\overline{\text{MSG}}$ ,  $\overline{\text{C/D}}$ , and I/O, respectively. They are used by a device connected in the initiator mode to determine which bus phase the target is requesting when a bus service interrupt is generated.

SRST: Scsi RST. This active-high bit represents the state of the SCSI bus line RST.

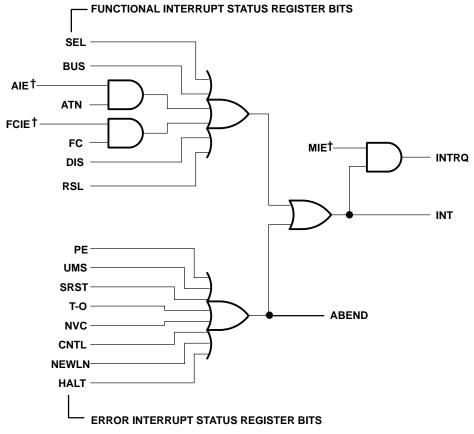

# 3.6 Functional Interrupt Status Register

The functional interrupt status register is an eight-bit read-only register that reflects SN75C091A functional interrupts. If no interrupting commands are active, this register reports an interrupt condition immediately; otherwise, the bits in this register are updated as the SN75C091A completes or aborts command execution. When this register is read, its bits are latched in order to provide stable data to the microprocessor. With the exception of the ABEND bit, any read-latched interrupt bit is cleared (set to 0) after the read is complete. A cleared interrupt bit is not be set to 1 again until the corresponding interrupt condition recurs. A persistent condition such as SCSI bus ATN only causes the ATN interrupt once. If new interrupts occur during a read of the functional interrupt status register, they are queued; when the register read is complete, these queued interrupts then cause the appropriate functional interrupt status register bits to be set to 1.

The functional interrupt status register is set to all zeros by a master reset. All bits except FC are also set to 0 by a SCSI reset.

| 7   | 6   | 5   | 4  | 3   | 2 | 1   | 0     |   |

|-----|-----|-----|----|-----|---|-----|-------|---|

| SEL | BUS | ATN | FC | DIS | 0 | RSL | ABEND | l |

**SEL:** SELected. When set to 1, this bit indicates that the chip has been selected as a target by another device on the bus. The chip is selected only if it detects its own ID with good parity on the data bus during the selection phase and if there is only one other ID on the bus. After setting this interrupt, the chip is connected as a target and waits for a command to be loaded.

**BUS:** BUS Service. When set to 1, this bit indicates to an initiator-connected device that an unanswered SCSI bus request is pending and that the microprocessor needs to issue an appropriate command based on the SCSI phase observed in the bus phase register. There are three occasions when this situation may occur:

When a REQ follows a reselection.

When a pending  $\overline{\text{REQ}}$  follows an aborted command (for example, a command may be aborted due to a parity error halt condition or an unexpected phase change).

When a REQ follows a completed command.

**ATN:** ATtentioN. This interrupt indicates to a device connected as a target that the ATN bus line has been asserted by the initiator. This interrupt occurs only if the control register ATNDS (attention disable) bit is set to 0 (ATNDS inactive).

**FC:** Function Complete. When set to 1, this bit indicates that the previous interrupting command has fully completed (i.e., has not been halted).

**DIS:** DISconnected. This bit is set to 1 when a device connected in the initiator role detects that the target has legally released the  $\overline{\mathsf{BSY}}$  line (i.e., has disconnected).

**RSL:** ReSeLected. This bit is set to 1 when the SBC has been reselected by another device on the bus. The SBC is reselected only if it detects its own ID on the data bus with good parity and if there is only one other <u>ID</u> asserted on the data bus. After the interrupt, the SBC is logically connected as an initiator and waits for a REQ from the target.

**ABEND:** ABnormal ENDing. This bit, when set to 1, indicates that further interrupt information is available in the error interrupt status register (EISR). If set to 0, then all interrupt information can be obtained from the functional interrupt status register. This bit is the logical OR of all the bits in the EISR. It is set to 0 when the EISR is read.

# 3.7 Error Interrupt Status Register

The error interrupt status register is an eight-bit read-only register that reflects SN75C091A error condition interrupts. If any bit in this register is set to 1, the ABEND bit in the functional interrupt status register is also set to 1. All bits in this register are set to 0 by a master reset. This register operates in the same manner as the functional interrupt status register.

| 7  | 6   | 5    | 4   | 3   | 2    | 1     | 0    |

|----|-----|------|-----|-----|------|-------|------|

| PE | UMS | SRST | T-O | NVC | CNTL | NEWLN | HALT |

**PE:** Parity Error. This bit is set to 1 when a parity error is detected on a byte received from any port on the chip. Note that this assumes that parity checking is enabled.

**UMS:** Unexpected Message Sequence. This bit is set to 1 when a target executing a Wait for Select with ATN Command receives a message other than an ID message following the selection phase.

**SRST:** Scsi ReSeT. This bit is set to 1 when the chip detects assertion of the SCSI RST line. Release of the SCSI reset line may be detected by polling the SRST bit in the bus phase status register. SCSI reset has the same effect as a Chip Reset command except that only selected bits in the register file are reset and the FIFO pointers are not reset.

**T-O:** Time-Out. This bit is set to 1 when a selection or reselection timeout occurs. Following the timeout interrupt, the SCSI select line is held active until the microprocessor issues either a SCSI reset or disconnect command.

**NVC:** iNValid Command. This bit is set to 1 when an invalid command is written to the command register. An invalid command is a reserved command code or a command issued at an inappropriate time (e.g., a Send command issued by a device in initiator mode). See Appendix C for a listing of invalid command conditions.

**CNTL:** CoNTroL error. When set to 1, this bit indicates to an initiator that the target has unexpectedly and illegally disconnected while a chip command is active.

**NEWLN:** NEW LuN. When set to 1, this bit indicates that a new LUN (Logical Unit Number) reselected the chip during a Select and Transfer command. The new LUN is available in the LUN register. The microprocessor should also check the SDP bit in the command phase register to see if the data pointer for the previous LUN should be updated.

**HALT:** HALTed. This bit is set to 1 whenever a chip operation is halted by a Pause command or an error condition such as a parity error. See the individual command descriptions for further detail.

#### 3.8 Interrupt Enable Register

Interrupt conditions are reported to the SBC through bits in the functional interrupt status register (FISR) and error interrupt status register (EISR). However, corresponding interrupts are not issued from the SBC to the microprocessor unless certain bits in the SBC interrupt enable register are set to 1. The interrupt enable register FCIE and AIE bits enable interrupt reporting to the microprocessor via the INT bit in the transfer status register. If the interrupt enable register MIE bit is set to 1, then interrupts can also be reported to the microprocessor via the SBC INTRQ line.

| I MIE |

|-------|

| NAIE. |

**FCIE:** Function Complete Interrupt Enable. When set to 1, this bit enables the chip to report a function-complete interrupt to the microprocessor via the transfer status register INT bit upon command completion. When FCIE is set to 0, no interrupt is reported. For initiator mode transfers, this allows the interrupt to be held off until a subsequent bus service request is generated; for target commands, the interrupt is held off until a subsequent selection occurs.

AIE: ATN Interrupt Enable. This bit, when set to 1, enables an ATN interrupt to be generated for a target device when the SCSI ATN line is detected active. If AIE is set to 0, no interrupt is generated. In either case, the ATN bits in both the bus phase status register and the functional interrupt status register are set to 1.

**MIE:** Master Interrupt Enable. When set to 1, this bit enables the INTRQ line to reflect a pending interrupt. If MIE is set to 0, the INT bit in the transfer status register must be polled to determine when an interrupt is active.

## 3.9 Control Register

The control register is an eight-bit read/write register used to store bits which control various functions and operating modes within the SCSI interface of the SBC chip. This register is set to all zeros by a master reset.

| 7  | 6  | 5  | 4   | 3    | 2  | 1    | 0     |

|----|----|----|-----|------|----|------|-------|

| SE | RE | HA | HPE | AAPE | HD | HAAM | ATNDS |

**SE:** Selection Enable. This bit, when set to 1, allows the SBC device to be selected as a target. If this bit is set to 0, then the SBC ignores any selection attempt.

**RE:** Reselection Enable. This bit, when set to 1, allows the SBC to be reselected as an <u>initiator</u>. If this bit is set to 0, then the chip ignores all reselection attempts. Also, during a Select with ATN and Transfer command, RE is copied into bit 6 of the automatically assembled ID message sent during the message-out phase.

**HA:** Halt on  $\overline{ATN}$ . Setting this bit to 1 causes a device in target mode to halt a chip command during a data phase (whether invoked by low-level or multiphase command) when the  $\overline{ATN}$  line is asserted. The HALT bit in the error interrupt status register and the ATN bit in the functional interrupt status register are both set to 1, and no further REQs are generated. For asynchronous data, interrupts are updated after  $\overline{ACK}$ . For synchronous data, interrupts are updated when the  $\overline{REQ}$ - $\overline{ACK}$  offset reaches zero. If HA is set to 0, the attention interrupt is generated when the chip command completes or is aborted for some other reason (i.e., halt on parity error).

**HPE:** Halt on Parity Error. If this bit is set to 1, detection of a parity error on an incoming data byte by any of the SCSI, microprocessor, or DMA interfaces during a data phase results in a halt of the current chip command and the setting to 1 of error interrupt status register bits HALT and PE. If HPE is set to 0, the parity error is reported when the chip command completes or is aborted for some other reason (i.e., a pause command is issued).

AAPE: Assert ATN on Parity Error. Setting this bit to 1 causes a chip in initiator mode to assert the ATN bus line when a parity error is detected on an incoming byte by any of the SCSI, microprocessor, or DMA interfaces. Note that preloading the FIFO via the microprocessor interface (prior to issuing a chip command) does not affect the ATN line if a parity error occurs because a chip command is not active. In this case, the parity error is reported to the microprocessor through an interrupt, allowing the microprocessor to clear the FIFO and start over. A parity error has no effect on the ATN line if the AAPE bit is set to 0.

**HD:** Halt on Disconnect. Setting this bit to 1 causes the chip to halt the Select with  $\overline{\text{ATN}}$  and Transfer command and generate a disconnect interrupt if the target legally disconnects prior to a command-complete message. If HD is set to 0, the SBC waits indefinitely to be reselected.

HAAM: Hold ATN After Message. Setting this bit to 1 provides the special control needed for sending multiple messages during a message-out phase when the chip is acting as an initiator. When HAAM is set to 1, the ATN line is held low when the command terminates. In contrast, when HAAM is set to 0, the ATN line is released before ACK is asserted for the last byte of the message.

**ATNDS:** ATN DiSable. Setting this bit to 1 masks the SCSI ATN input so that ATN does not cause an interrupt, is not available in the bus phase or functional interrupt status registers, and is not recognized by any command. This feature is provided for target applications which do not support messages. For example, ATNDS can be used in conjunction with the Wait for Select without ATN command so that the command continues to execute even if the initiator asserts ATN.

# 3.10 Byte Stack Control Register

The byte stack control register is an eight-bit read/write register used to store bits which control byte stack features of the chip. This register is set to all zeros by a master reset.

| 7   | 6 | 5 | 4 | 3   | 2   | 1    | 0    |

|-----|---|---|---|-----|-----|------|------|

| DMD | 0 | 0 | 0 | WL1 | WL0 | BOF1 | BOF0 |

**DMD:** DeManD transfer DMA. This bit controls the DMA interface demand transfer mode. If set to 1, demand mode is enabled and DREQ (once asserted) is held asserted as long as there are enough bytes in the receive FIFO to read from or space in the transmit FIFO to write. In byte stack mode, the WAIT line is used to give the chip enough time to load or unload the required number of bytes from the byte stack register. The chip automatically switches in and out of demand mode as dictated by the FIFO status. If DMD is set to 0, then single transfer mode, in which a DREQ/DACK handshake is required for each transfer, is used. This feature is provided for systems in which the microprocessor needs to access memory for instructions on an interleaved basis.

**WL0,1:** Word Length 0,1. These bits determine the length of multi-byte words used in the byte stack interface to the DMA controller, as follows:

| WL1 | WL0 | WORD LENGTH (BYTES)            |

|-----|-----|--------------------------------|

| 0   | 0   | 1 (default – no byte stacking) |

| 0   | 1   | 2                              |

| 1   | 0   | 3                              |

| 1   | 1   | 4                              |

**BOF0,1:** Byte Offset 0,1. These bits determine the length of the byte offset used for the first word transferred to or from the DMA controller when using the byte stack control logic, as follows:

| BOF1 | BOF0 | BYTE OFFSET (BYTES) |

|------|------|---------------------|

| 0    | 0    | 0 (default)         |

| 0    | 1    | 1                   |

| 1    | 0    | 2                   |

| 1    | 1    | 3                   |

Further examples of byte offsets are shown in Section 6.3.3.

# 3.11 Parity Control Register

The parity control register is an eight-bit read/write register used to select the desired parity check/generate options for the SCSI, DMA, and microprocessor interfaces. This register is set to all zeros by a master reset.

| 7    | 6    | 5    | 4    | 3    | 2   | 1    | 0    |

|------|------|------|------|------|-----|------|------|

| PMPE | MPCE | MPGE | PPCE | PPGE | SPE | SPCE | SPGE |

**PMPE:** Processor/Memory Parity Even. Setting this bit to 1 causes the microprocessor- and DMA-port parity check/generation to be even parity. If PMPE is set to 0, then parity is odd for both ports.

**MPCE**: Memory Parity Check Enable. Setting this bit to 1 forces the chip to check incoming bytes from the DMA memory port for correct parity as defined by the PMPE bit. If a parity error is detected, the proper error bit is set to 1 in the error interrupt status register. If MPCE is set to 0, no parity checking is done and no parity error flagged.

**MPGE:** Memory Parity Generation Enable. This bit, when set to 1, forces the chip to generate parity (type determined by the PMPE bit) on outgoing bytes to the DMA memory port. If MPGE is set to 0, then the parity sense for the DMA memory port is determined by the receive FIFO parity bit.

**PPCE:** Processor Parity Check Enable. When PPCE is set to 1, the chip checks incoming bytes from the local processor for correct parity as determined by PMPE bit. If a parity error is detected, the proper error bit is set to 1 in the error interrupt status register. If PPCE is set to 0, no parity checking is performed and no parity error flagged.

**PPGE:** Processor Parity Generation Enable. This bit, when set to 1, causes the chip to generate parity (type determined by the PMPE bit) for FIFO data accessed through the processor interface. If PPGE is set to 0, then FIFO data parity is obtained from the FIFO. (Note: parity is always generated for other registers in the register file.)

**SPE:** SCSI Parity Even. When set to 1, this bit causes the SCSI interface parity check/generation to be even parity. Odd parity is used if SPE is set to 0..

**SPCE:** SCSI Parity Check Enable. Setting this bit to 1 forces the chip to check incoming bytes from the SCSI bus for correct parity as determined by the SPE parity bit. If a parity error is detected, the proper error bit is set to 1 in the error interrupt status register. If SPCE is set to 0, then no parity checking is performed and no parity error flagged.

**SPGE:** SCSI Bus Parity Generation Enable. When SPGE is set to 1, the chip generates parity (type determined by the SPE bit) for data output to the SCSI bus from the FIFO. If SPGE is set to 0, parity information in the FIFO is used. Note that for automatically generated SCSI information such as the command-complete message or the selection ID, parity is always generated according to the SPE bit.

#### 3.12 Synchronous Transfer Register

The synchronous transfer register is an eight-bit read/write register used to define the offset length and transfer period for synchronous data transfers over the SCSI bus. This register is set to all zeros by a master reset. The Offset Length bits (OL3–OL0) define the REQ-ACK offset; the maximum allowed offset is 15. This offset corresponds to the number of REQ pulses allowed to be outstanding before a corresponding ACK pulse is received by the target during synchronous data transfers. An offset length of zero implies that asynchronous mode transfers are to be used.

The Transfer Period bits (TP3–TP0) define the transfer period length in terms of internal clock cycles of the chip. The transfer period is the minimum time between leading edges of successive REQ pulses (target) or of successive ACK pulses (initiator). REQ is always active for two clock cycles, and bits TP3-TP0 contain the number of internal clock cycles for which the REQ line is held inactive prior to the next REQ pulse. Thus, the transfer period corresponds to the value in (TP3-TP0) + 2. For example, a value of 3 in bits TP3-TP0 indicates a transfer period of 5 clock cycles. The minimum allowed transfer period is four clock cycles, so

TP3-TP0 values of 0, 1, and 2 all correspond to a four-clock-cycle transfer period (REQ is always released for at least two clock cycles).

In multiple-thread Initiator SCSI applications, following reselection by a different target, the synchronous transfer register must be updated prior to negation of ACK for the ID message. This action guarantees that the correct mode is set up before data phase requests begin.

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| TP3 | TP2 | TP1 | TP0 | OL3 | OL2 | OL1 | OL0 |

#### 3.13 Selection/Reselection Time-Out Register

The selection/reselection time-out register programs the selection/reselection time-out period for a command that is selecting/reselecting another device. This time-out period begins when the chip releases BSY during the selection/reselection phase and ends when the target (initiator) responds by asserting BSY. If a time-out occurs, the chip waits for a length of time known as the selection abort time (after removing the selection/reselection ID from the bus) prior to halting the command and generating a time-out interrupt. The time-out values are multiples of 3.27 ms and the maximum programmable time-out period is 0.83 seconds. A value of zero in this register disables the time-out mechanism, allowing indefinite time-outs. The microprocessor must issue a pause command in order for a time-out to occur. Once the pause command is issued, the chip continues as if the time-out has expired. Note that this sequence assumes that the selection phase is in progress. If arbitration has not been won, a pause simply halts the command and generates a halted interrupt. This register is set to all zeros by a master reset.

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| T07 | TO6 | TO5 | TO4 | TO3 | TO2 | TO1 | TO0 |

# 3.14 Self ID Register

The self ID register is a read/write register that contains the encoded SCSI address of the device which is using the chip. This address is decoded and the corresponding data bus line is asserted during an arbitration phase and again during the selection or reselection phase after arbitration is won. The Self ID register is set to all zeros by a master reset.

| 7 | 6 | 5 | 4 | 3 | 2   | 1   | 0   |

|---|---|---|---|---|-----|-----|-----|

| 0 | 0 | 0 | 0 | 0 | ID2 | ID1 | ID0 |

#### 3.15 Destination ID Register

The destination ID register contains the encoded address of the SCSI device which is to be selected or reselected. It must be loaded prior to any command which attempts a selection or reselection phase, such as the Select with ATN, Select without ATN, Reselect, Select and Transfer, or Reselect and Send/Receive Data. This address is decoded and then loaded onto the data bus during a selection or reselection phase. This read/write register is set to all zeros by a master reset.

| 7 | 6 | 5 | 4 | 3 | 2   | 1   | 0   |

|---|---|---|---|---|-----|-----|-----|

| 0 | 0 | 0 | 0 | 0 | ID2 | ID1 | ID0 |

#### 3.16 Source ID Register

Bits 2-0 of the source ID register contain the encoded address of the initiator/target which last selected/reselected the SBC chip. The Source ID valid (SIV) bit is set to 1 if the selecting/reselecting device asserted its own ID on the bus during the selection/reselection phase. If SIV is set to 0, then the source ID is not valid. This distinction is necessary since an all-zero ID is valid and cannot otherwise be distinguished from a cleared register. If SIV is set to 0 in the source ID register after a selection, then the initiator is operating in the single-initiator mode and does not support reselection. A target has no option and must

place both its own ID and the ID of the initiator it wants to reselect on the bus when attempting a reselection phase. Thus, SIV is always set to 1 in the initiator source ID register after a successful reselection. This register is set to all zeros following a master reset.

| 7 | 6 | 5 | 4 | 3   | 2   | 1   | 0   |

|---|---|---|---|-----|-----|-----|-----|

| 0 | 0 | 0 | 0 | S/V | ID2 | ID1 | ID0 |

# 3.17 Target Logical Unit Number (LUN) Register

The target LUN register is used to store received ID messages or ID messages to be sent during Select with ATN and Transfer, Reselect and Send or Reselect and Receive, or Wait for Select with ATN multiphase commands. This register must be loaded prior to commands which send an ID message. Although it is a full 8-bit register, bits 6 and 7 are not used to formulate outgoing ID messages (see bit descriptions below). Received ID messages stored in the target LUN register contain the entire 8-bit message from the SCSI bus. This register is set to all zeros by a master reset.

|   | 7 | 6      | 5      | 4        | 3        | 2   | 1   | 0   |   |

|---|---|--------|--------|----------|----------|-----|-----|-----|---|

| I | 1 | DSCPRV | LUNTAR | Reserved | Reserved | TL2 | TL1 | TL0 | ĺ |

**Bit 7:** This bit is tied high internally for initiator or target multiphase commands sending an ID message (by definition of ID message, this bit value must be "1").

**DSCPRV:** DisConnect PRiVilege. This bit is used by the initiator to grant the target the privilege of disconnecting. It is internally connected to the RE (Reselection Enable) bit in the control register for initiator ID message out. This creates an interlock to prevent reselection from being granted to the target when it is disabled in the initiator's control register. For a target sending the ID message, this bit is internally set to 0.

**LUNTAR:** For SCSI 1, this bit is reserved and should be set to 0. SCSI 2 protocols use this bit to associate the identify message with a target routine (bit value 1) or a logical unit (bit value 0).

Bits 4-3: These bits are reserved by the SCSI specification and should be set to 0.

**TL2-TL0:** Target Lun 2-0. For SCSI 1, these bits represent the logical unit number of the thread being established by the initiator or reestablished by the target. SCSI 2 uses them to identify a target routine or a logical unit, depending on the LUNTAR bit.

During an initiator Select with  $\overline{\text{ATN}}$  and Transfer command, the TL2-TL0 bits of an incoming ID message are compared with the current TL2-TL0 bits in the LUN register before they are loaded. If the compare is unsuccessful, the "new LUN" interrupt is generated to indicate that a target is trying to reestablish a connection to a different logical unit. The incoming ID message is then loaded into the LUN register.

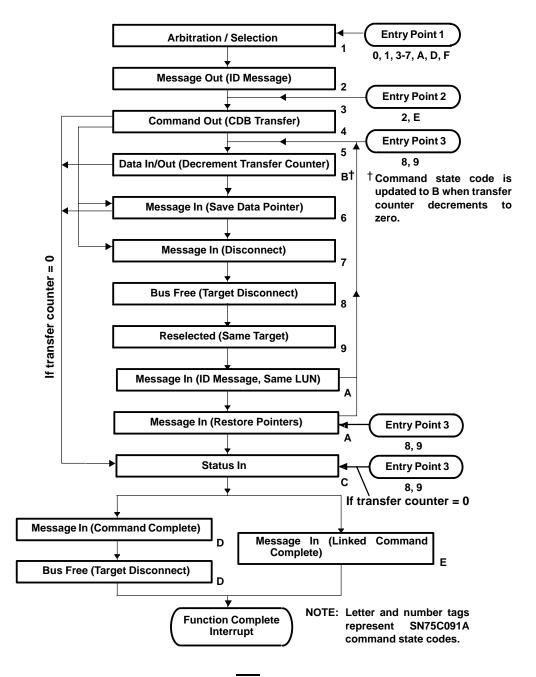

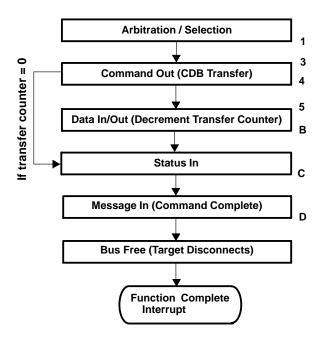

#### 3.18 Command State Register

The command state register incrementally stores a code representing each successfully completed phase of a multiphase command. Each command has code definitions which are shown in the command description. The intent of this register is twofold:

- To inform the microprocessor how far a multiphase command executed before some type of abnormal termination (something other than a function-complete interrupt) occurred so that the microprocessor can complete the transaction in low-level mode.

- To begin execution of a Select with ATN and Transfer command at one of three possible entry points.

This register should only be accessed after a command has terminated due to completion, after an abnormal sequence, or after a pause command. The microprocessor can read the register after determining the type of interrupt that halted activity.

This register is set to all zeros by a master reset.

| 7   | 6 | 5 | 4 | 3   | 2   | 1   | 0   |

|-----|---|---|---|-----|-----|-----|-----|

| SDP | 0 | 0 | 0 | CS3 | CS2 | CS1 | CS0 |

**SDP:** Save Data Pointer. This bit is set to 1 when the chip receives a save-data-pointer message while connected as an initiator and executing a Select with ATN and Transfer command. This bit is set to 0 by a master reset, by a function-complete interrupt, or by reading the command phase register. When the microprocessor detects that SDP is set to 1, the backup transfer counter should be read to determine the value of the data transfer counter at the time of the save-data-pointer message.

**CS3-CS0:** Command State 3-0. These bits represent an encoded phase of a multiphase command. See Section 4, Commands, for a description of the codes.

# 3.19 Transfer Counter Register

The transfer counter register is a 24-bit down-counter used to keep track of the data bytes traversing the chip-SCSI bus interface. It is composed of three 8-bit bytes, each of which may be addressed and read or written individually. The microprocessor loads the number of SCSI data bytes to be transferred into the transfer counter register prior to issuing a chip command to transfer data. When the counter decrements to zero, the data transfer is complete. If a data transfer is aborted, the transfer counter indicates how many bytes are left to transfer (see also the description of the backup transfer counter register).

The transfer counter register is loaded by writing to each of the three bytes. A write to the least-significant byte sets both of the higher-order bytes to all zeros. This allows the microprocessor to perform only one write to define the length for relatively short transfers (< 256 bytes). For longer transfers, the low-order byte should be written first, followed by writes to one or both of the higher-order registers. This register is set to all zeros by a master reset.

| 7   | 6 | 5 | 4 | 3 | 2 | 1 | 0   |

|-----|---|---|---|---|---|---|-----|

|     |   |   |   |   |   |   | Isb |

|     |   |   |   |   |   |   |     |

| msb |   |   |   |   |   |   |     |

#### 3.20 Backup Counter Register

The backup counter register is used to save a copy of the contents of the transfer counter register whenever a save-data-pointer message is received by a chip in initiator mode during a Select with ATN and Transfer command. It may be read by the microprocessor to determine the amount of data successfully transferred over the SCSI bus in case an error occurs or a different target or LUN reconnects. The SDP (save data pointer) bit in the command phase register indicates whether a save-data-pointer message has been received and, thus, if the backup counter register has been updated. This register is set to all zeros by a master reset.

| 7   | 6 | 5 | 4 | 3 | 2 | 1 | 0   |

|-----|---|---|---|---|---|---|-----|

|     |   |   |   |   |   |   | Isb |

|     |   |   |   |   |   |   |     |

| msb |   |   |   |   |   |   |     |

# 3.21 Offset Count Register

The offset count register is used internally by the SBC to control the number of bytes transferred across the SCSI bus for synchronous data, extended messages, or command transfers. The SBC decodes the number of bytes to be transferred from the second byte of an extended message or the group code of a command. The offset counter can also be loaded by the microprocessor and used with manual transfer mode (selected by the control bit M/A in the command register) to override the automatic handling of these flows. The offset count register is an eight-bit register which allows a count of up to 255 to be stored. This register is set to all zeros by a master reset.

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| OC7 | OC6 | OC5 | OC4 | OC3 | OC2 | OC1 | OC0 |

# 3.22 Supplemental Register Features

Registers 25 through 31 were used for SBC chip development and debug and are not intended for system use. However, the following specific features may be helpful to designers:

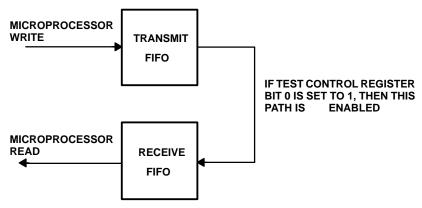

Register 26 (Test control register):

Bit 0 (FIFO): When set to 1, this bit enables an internal loop-back path from the Transmit FIFO to the Receive FIFO. Operation is as follows and can be monitored via the FIFO status bits in the Transfer status register. This bit is set to 0 by a master reset.

Figure 3-1. Internal Loop-Back Path for FIFO Test

Transmit FIFO Writes: A microprocessor-FIFO write causes a write to the transmit FIFO. If, prior to the microprocessor-FIFO write, the receive FIFO is not full and the transmit FIFO is not empty, then a write to the receive FIFO from the transmit FIFO and a read out from the transmit FIFO also occur. Thus, successive microprocessor-FIFO writes fill the receive FIFO first and then the transmit FIFO.

Receive FIFO Reads: A microprocessor-FIFO read causes a read from the receive FIFO. If, prior to the microprocessor-FIFO read, the receive FIFO is not full and the transmit FIFO is not empty, then a write to the receive FIFO from the transmit FIFO and a read out from the transmit FIFO also occur. Thus, successive microprocessor-FIFO reads empty the transmit FIFO first and then the receive FIFO.

If SCSI parity checking is enabled, data coming out of the transmit FIFO is checked for correct parity and an interrupt is generated if a parity error is detected.

Register 27 (Test points register 0):

Bit 0 (TFMTY): When set to 1, this bit indicates that the transfer FIFO is empty. This bit supplements the information provided by the TFF (transfer FIFO full) and TFHF (transfer FIFO half full) bits in the transfer status register. This bit is set to 0 by a master reset.

# 4 Commands

#### 4.1 General

The SBC is driven by chip commands written by the local microprocessor to the SBC command register. The format and bit definitions of the command register are repeated below. The first three bits set modes for information transfer and are only valid for those types of commands (i.e., send, receive, and transfer).

| 7   | 6   | 5    | 4   | 3   | 2   | 1   | 0   |

|-----|-----|------|-----|-----|-----|-----|-----|

| DMA | M/A | DDIR | CC4 | CC3 | CC2 | CC1 | CC0 |

**DMA:** Direct Memory Access. This bit controls the mode of data transfer from the SCSI bus to the microprocessor or DMA bus. When set to 0, the interface uses programmed I/O; when set to 1, DMA transfers are enabled. If DMA transfers are enabled, the microprocessor should not access the FIFOs until the command is complete.

**M/A**: Manual/Automatic. This bit allows the microprocessor to manually control the number of bytes transferred during a command or message phase. When this bit is set to 1, the count written to the offset counter by the microprocessor is used to determine the transfer length of the command or message phase. When this bit is set to 0, the group code of a command or the second byte of an extended message is decoded to determine a count value to be automatically loaded into the offset counter. Automatic mode eliminates the need for software to decode the command or message prior to completing the transfer. Manual mode may be used to complete a phase which was terminated prematurely.

**DDIR:** Data DIRection. This bit establishes the direction of data transfer during initiator-mode Select without ATN and Transfer commands. When set to 0, the SBC expects a data-out phase; when set to 1, a data-in phase is expected. If the data phase set up by the target does not match that expected by the initiator, a bus service interrupt is generated and the command stops.

#### CC4-CC0: Command codes

#### 4.2 Command Types

The chip commands are divided into two subsets: interrupting and noninterrupting. Both types of commands are executed immediately after they are written to the command register. As their names imply, they differ in whether or not an interrupt is generated to indicate command completion. The noninterrupting commands generally complete within a few clock cycles, while the interrupting commands can take from ten to several thousand clock cycles to complete.

The interrupting commands are subdivided into single-phase and multiphase commands. Phase refers to the SCSI bus phase encountered during command execution. The single-phase commands (also called low-level commands) execute bus management phases (e.g., arbitration, selection/reselection) or a single information transfer phase. The multiphase commands (also called high-level commands) combine information-transfer phases and bus management phases.

The SBC examines each command received from the microprocessor to determine if the command is valid (i.e., if it has been issued while the SBC is in an appropriate state to receive that command). A command issued at an inappropriate time causes the generation of an invalid command interrupt. The following table summarizes the chip commands, the valid states in which they can be issued, the resultant state if the command is successful, and whether they are noninterrupting (NI) or interrupting (I) commands. A description of each command follows the table.

# 4.3 Command Summary

# 4.3.1 Noninterrupting Commands

| COMMAND<br>CODE | COMMAND NAME        | ISSUED<br>STATE | RESULT<br>STATE |

|-----------------|---------------------|-----------------|-----------------|

| 00000           | Chip Reset          | ANY             | D               |

| 00001           | Disconnect          | T, TO           | D               |

| 00010           | Pause               | I, T            | I, T            |

| 00011           | Assert ATN          | I               | I               |

| 00100           | Negate ACK          | I               | I               |

| 00101           | Clear Receive FIFO  | D, I, T         | D, I, T         |

| 00110           | Clear Transmit FIFO | D, I, T         | D, I, T         |

# **STATE**

D = Disconnected, I = Initiator, T = Target, TO = Time-Out

# 4.3.2 Single-Phase Interrupting Commands

| COMMAND<br>CODE | COMMAND NAME                        | ISSUED<br>STATE | RESULT<br>STATE |

|-----------------|-------------------------------------|-----------------|-----------------|

| 00111           | SCSI Bus Reset                      | ANY             | D               |

| 01000           | Select with ATN                     | D               | I               |

| 01001           | Select without ATN                  | D               | I               |

| 01010           | Reselect                            | D               | Т               |

| 01011           | (reserved)                          | -               | -               |

| 01100           | Receive Command                     | Т               | Т               |

| 01101           | Receive Data                        | Т               | Т               |

| 01110           | Receive Message Out                 | Т               | Т               |

| 01111           | Receive Unspecified Information Out | Т               | Т               |

| 10000           | Send Status                         | Т               | Т               |

| 10001           | Send Data                           | Т               | Т               |

| 10010           | Send Message In                     | T               | Т               |

| 10011           | Send Unspecified Information In     | T               | Т               |

| 10100           | Transfer Information                | ı               | ı               |

| 10101           | Transfer Pad                        |                 | I               |

| 10110           | (reserved)                          | _               | -               |

| 10111           | (reserved)                          | -               | _               |

# **STATE**

$\label{eq:defD} D = Disconnected, \quad I = Initiator, \quad T = Target, \quad TO = Time-Out$

#### 4.3.3 Multiphase Interrupting Commands

| COMMAND<br>CODE | COMMAND NAME                            | ISSUED<br>STATE | RESULT<br>STATE |

|-----------------|-----------------------------------------|-----------------|-----------------|

| 11000           | Select with ATN and Transfer            | D, I            | D               |

| 11001           | Select without ATN and Transfer         | D               | D               |

| 11010           | Reselect and Receive Data               | D               | Т               |

| 11011           | Reselect and Send Data                  | D               | Т               |

| 11100           | Wait for Select with ATN and Receive    | D, T            | Т               |

| 11101           | Wait for Select without ATN and Receive | D, T            | Т               |

| 11110           | Conclude                                | T               | D               |

| 11111           | Link to Next Command                    | Т               | Т               |

**STATE**

D = Disconnected, I = Initiator, T = Target, TO = Time-Out

# 4.4 Noninterrupting Commands

# 4.4.1 Chip Reset

Chip Reset halts all operations and returns the chip to a master reset state. The SBC releases all SCSI bus lines and the receive and transmit FIFO pointers are reset.

#### 4.4.2 Disconnect

In response to a disconnect command, the SBC releases the SCSI BSY signal and exits target mode. The disconnect command is also used following a selection/reselection time-out interrupt to cause the SCSI SEL signal to be released, indicating the end of the selection/reselection attempt by freeing the SCSI bus.

## 4.4.3 Pause

The pause command is used to halt execution of certain chip commands. Pause capability gives the microprocessor additional control over commands with long execution times. In cases such as arbitration, the pause command may not immediately be recognized. Thus, once a pause command is issued, the command register should not be written again until an interrupt indicating command completion or termination is received. Case-by-case use of the pause command is as follows:

**Arbitration Phase Pause:** Issuing a pause command during any chip command performing arbitration and selection halts that command and generates a halted interrupt if arbitration is lost or if the SCSI bus is being used by another device. For example, if a bus-free phase has been detected and the chip is actively involved in the arbitration process, a pause does not occur unless and until arbitration is lost. If arbitration is won, the pause command has no effect on the arbitration process.

**Selection/Reselection Time-Out:** Issuing a pause command during any chip command performing selection/reselection with a selection/reselection time-out value of zero (see Section 3.13, Selection/Reselection time-out register) causes a time-out to occur when the selection/reselection time-out begins. The pause command causes the selection/reselection ID to be released on the SCSI bus and a selection/reselection abort time to be started. If no BSY response is detected within the abort time, the time-out interrupt is generated. This capability allows indefinite arbitration/selection time-outs to be used by the microprocessor for cases in which the time-out register does not provide a long enough delay.

**Data Phase Pause:** A pause command can be used to halt any data phase. Data phase pause capability allows the microprocessor to halt a long data transfer phase in case of unexpected error situations.

Initiator Asynchronous: Following receipt of the pause command, the SBC performs one REQ/ACK handshake, then generates a halted interrupt. The transfer counter contains the number of bytes left to transfer. A transfer pad command can be used to finish the data phase.

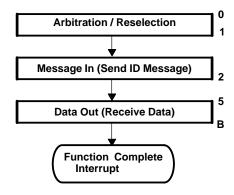

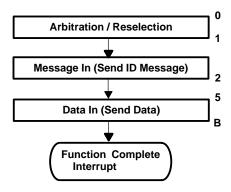

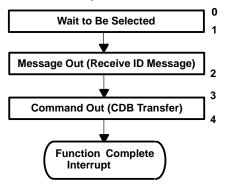

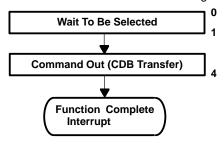

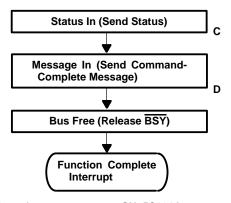

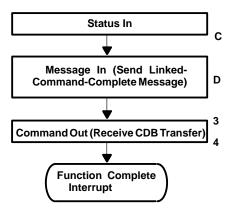

- Target Asynchronous: Following receipt of the pause command, the SBC performs one REQ/ACK handshake, then generates a halted interrupt. The target may reissue a data transfer command to continue the transfer or may issue a command to change phases. If the data phase is not completed, a FIFO clear command may be needed prior to performing another type of transfer.