- Nine Differential Channels for the Data and **Control Paths of the Differential Small** Computer Systems Interface (SCSI)

- Meets or Exceeds the Requirements of **ANSI Standard RS-485 and ISO** 8482:1987(E)

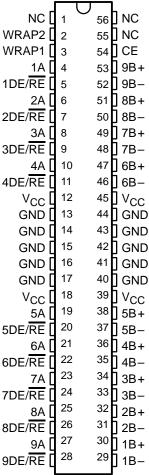

- Packaged in Shrink Small-Outline Package With 25-mil Terminal Pitch

- **Designed to Operate at 10 Million Transfers** Per Second

- **Low Disabled Supply Current** 1.4 mA Typ

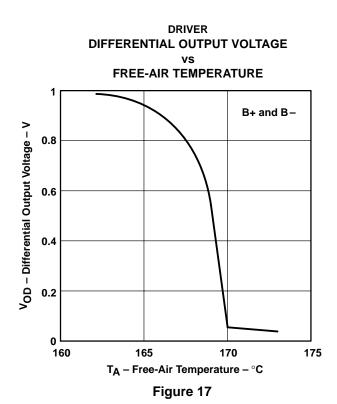

- **Thermal Shutdown Protection**

- Power-Up/Power-Down Glitch Protection

- **Positive and Negative Output-Current** Limiting

- **Open-Circuit Fail-Safe Receiver Design**

#### description

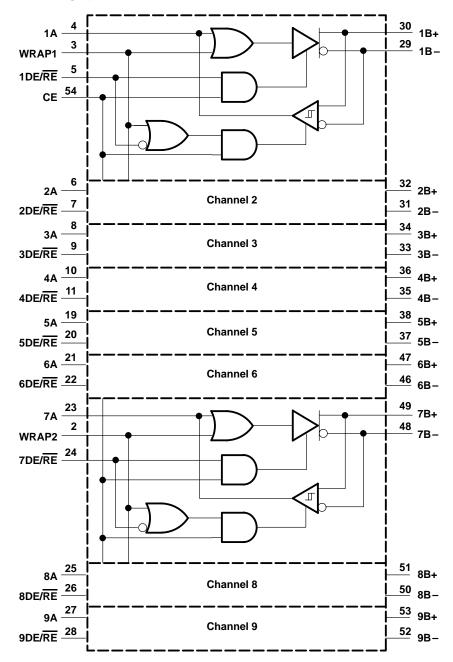

The SN75LBC978 is a nine-channel differential transceiver based on the 75LBC176 LinASIC™ cell. Use of TI's LinBiCMOS™† process technology allows the power reduction necessary to integrate nine differential balanced transceivers. On-chip enabling logic makes this device applicable for the data path (eight data bits plus parity) and the control path (nine bits) for the Small Computer Systems Interface (SCSI) standard. The WRAP function allows in-circuit testing and wired-OR channels for the BSY, RST, and SEL signals of the SCSI bus.

The SN75LBC978 is packaged in a shrink small-outline package (DL) with improved thermal characteristics using heat-sink terminals. This package is ideal for low-profile, space-restricted applications such as hard disk drives.

Pins 13 through 17 and 40 through 44 are connected together to the package lead frame and signal ground.

The switching speed of the SN75LBC978 is sufficient to transfer data over the data bus at 10 million transfers per second. Each of the nine identical channels conforms to the requirements of the ANSI RS-485 and ISO 8482:1987(E) standards referenced by ANSI X3.131-1993 (SCSI-2) and the proposed SCSI-3 standards.

The SN75LBC978 is characterized for operation from 0°C to 70°C.

† Patent Pending

LinASIC and LinBiCMOS are trademarks of Texas Instruments Incorporated.

#### logic diagram (positive logic)

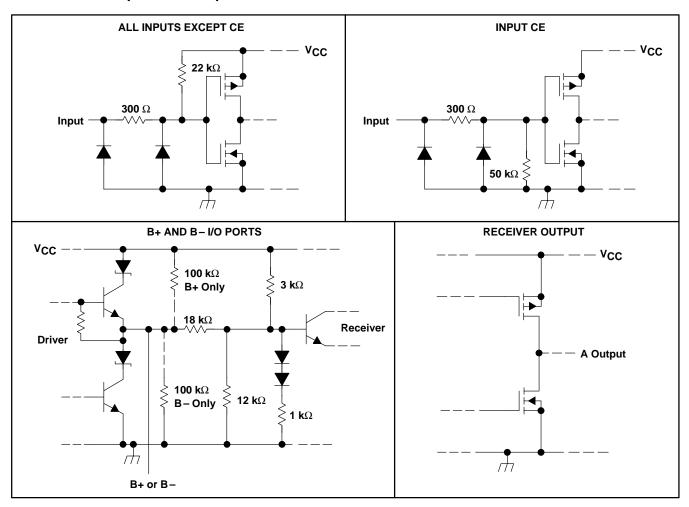

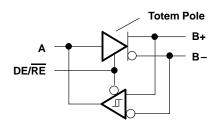

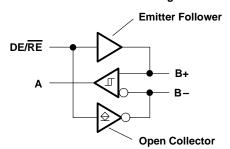

#### schematics of inputs and outputs

# absolute maximum ratings over operating free-air temperature range (unless otherwise noted)†

| Supply voltage range, V <sub>CC</sub> (see Note 1)           | 0.3 V to 7 V       |

|--------------------------------------------------------------|--------------------|

| Bus voltage range                                            |                    |

| Data I/O and control (A-side) voltage range                  | 0.3 V to 7 V       |

| Continuous power dissipation                                 | internally limited |

| Operating free-air temperature range, T <sub>A</sub>         | 0°C to 70°C        |

| Storage temperature range, T <sub>stg</sub>                  |                    |

| Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds | 260°C              |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTE 1: All voltage values are dc and with respect to GND.

# SN75LBC978 9-CHANNEL DIFFERENTIAL TRANSCEIVER

SLLS134E - APRIL 1992 - REVISED MAY 1997

#### recommended operating conditions

|                                                                          |                                                                                                           | MIN  | NOM | MAX  | UNIT |

|--------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|------|-----|------|------|

| Supply voltage, V <sub>CC</sub>                                          |                                                                                                           | 4.75 | 5   | 5.25 | V    |

| Voltage at any bus terminal (constrately or common mode) Vo. V. or V. o  | y bus terminal (separately or common-mode), V <sub>O</sub> , V <sub>I</sub> , or V <sub>IC</sub> B+ or B- |      |     | 12   | V    |

| voltage at any bus terminal (separately of common-mode), vo, vi, or vice |                                                                                                           |      |     | -7   | ٧    |

| High-level input voltage, VIH                                            | All except B+ and B-                                                                                      | 2    |     |      | V    |

| Low-level input voltage, V <sub>IL</sub>                                 | All except B+ and B-                                                                                      |      |     | 0.8  | V    |

| High-level output current, I <sub>OH</sub>                               | B+ or B-                                                                                                  |      |     | -60  | mA   |

| Triigit-level output current, IOH                                        | А                                                                                                         |      |     | -8   | mA   |

| Low lovel output current les                                             | B+ or B-                                                                                                  |      |     | 60   | mA   |

| Low-level output current, IOL                                            | А                                                                                                         |      |     | 8    | mA   |

| Operating free-air temperature, T <sub>A</sub>                           |                                                                                                           | 0    |     | 70   | °C   |

# device electrical characteristics over recommended ranges of operating conditions

|                 | PARAME                      | TER                                | TES                     | T CONDITIONS                                     | MIN          | TYP <sup>†</sup> | MAX  | UNIT |    |

|-----------------|-----------------------------|------------------------------------|-------------------------|--------------------------------------------------|--------------|------------------|------|------|----|

|                 | High lovel input ourrent    | A, WRAP, DE/RE                     |                         | V <sub>IH</sub> = 2 V                            |              |                  | -200 | μΑ   |    |

| ΊΗ              | High-level input current    | CE                                 | Soo Figure 1            | See Figure 1                                     |              |                  | 100  | μΑ   |    |

|                 | Low lovel input current     | A, WRAP, DE/RE                     | See Figure 1            | See Figure 1                                     | \/u = 0.8.\/ |                  |      | -200 | μΑ |

| 'IL             | Low-level input current     | CE                                 |                         | V <sub>IL</sub> = 0.8 V                          |              |                  | 100  | μΑ   |    |

|                 |                             | All drivers and receivers disabled | CE at 0 V               | CE at 0 V                                        |              | 1.4              | 3    | mA   |    |

| Icc             | Supply current              | All receivers enabled              | No load,<br>CE at 5 V,  | $V_{ID} = 5 \text{ V},$<br>WRAP and DE/RE at 0 V |              | 29               | 45   | mA   |    |

|                 |                             | All drivers enabled                | No load,<br>WRAP at 0 V | CE and DE/RE at 5 V,                             |              | 7                | 10   | mA   |    |

| CO              | Bus port output capacitant  | се                                 | B+ or B-                |                                                  |              | 19               |      | pF   |    |

| <u> </u>        | Power dissipation capacita  | ance                               | One driver              |                                                  |              | 460              |      | pF   |    |

| C <sub>pd</sub> | i owei dissipation capacita | ance                               | One receiver            |                                                  |              | 40               |      | pF   |    |

# driver electrical characteristics over recommended ranges of operating conditions (unless otherwise noted)

| PARAMETER       |                                     | TEST CONDITIONS                                                   | MIN    | TYP | MAX  | UNIT |

|-----------------|-------------------------------------|-------------------------------------------------------------------|--------|-----|------|------|

| V <sub>OD</sub> | Differential output voltage         | $V_{test} = -7 \text{ V to } 12 \text{ V},  \text{See Figure } 2$ | 1      | 2   |      | V    |

| los             | Output short-circuit current        | See Figure 3                                                      |        |     | ±250 | mA   |

| loz             | High-impedance-state output current | See receiver input co                                             | urrent |     |      |      |

SLLS134E - APRIL 1992 - REVISED MAY 1997

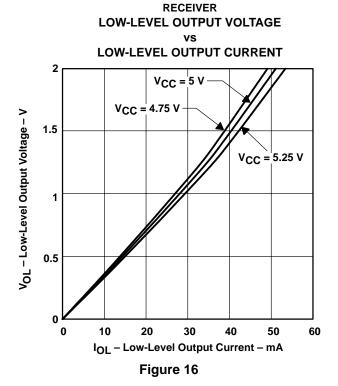

## receiver electrical characteristics over recommended ranges of operating conditions (unless otherwise noted) (see Figure 3)

|                   | PARAME                           | TER                                          | TEST CONI                                    | DITIONS                  | MIN  | TYP† | MAX  | UNIT |

|-------------------|----------------------------------|----------------------------------------------|----------------------------------------------|--------------------------|------|------|------|------|

| Vон               | High-level output voltage        |                                              | $V_{ID} = 200 \text{ mV},$                   | $I_{OH} = -8 \text{ mA}$ | 2.5  |      |      | V    |

| VOL               | Low-level output voltage         |                                              | $V_{ID} = -200 \text{ mV},$                  | $I_{OL} = 8 \text{ mA}$  |      |      | 0.8  | V    |

| V <sub>IT+</sub>  | Differential-input high-level to | hreshold voltage                             | I <sub>OH</sub> = -8 mA                      |                          |      |      | 0.2  | ٧    |

| V <sub>IT</sub> – | Differential-input low-level th  | reshold voltage                              | I <sub>OL</sub> = 8 mA                       |                          | -0.2 |      |      | V    |

| V <sub>hys</sub>  | Receiver input hysteresis vo     | ltage (V <sub>IT+</sub> - V <sub>IT-</sub> ) |                                              |                          |      | 45   |      | mV   |

|                   |                                  |                                              | V <sub>I</sub> = 12 V,<br>Other input at 0 V | V <sub>CC</sub> = 5 V,   |      | 0.7  | 1    | mA   |

|                   | Descriver input ourrest          | B+ and B-                                    | V <sub>I</sub> = 12 V,<br>Other input at 0 V | V <sub>CC</sub> = 0 V,   |      | 0.8  | 1    | mA   |

| l ti              | Receiver input current           | D+ aliu D-                                   | $V_I = -7 \text{ V},$<br>Other input at 0 V  | $V_{CC} = 5 V$ ,         |      | -0.5 | -0.8 | mA   |

|                   |                                  |                                              | $V_I = -7 \text{ V},$<br>Other input at 0 V  | $V_{CC} = 0 V$ ,         |      | -0.4 | -0.8 | mA   |

| 107               | High-impedance-state output      | t current                                    | $V_O = GND$                                  |                          |      |      | -200 |      |

| loz               | r ligh-limpedance-state outpu    | ii Current                                   | AO = ACC                                     |                          |      |      | 50   | μΑ   |

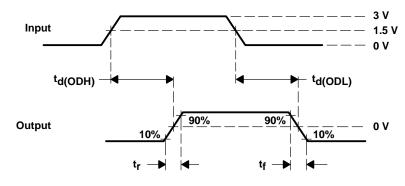

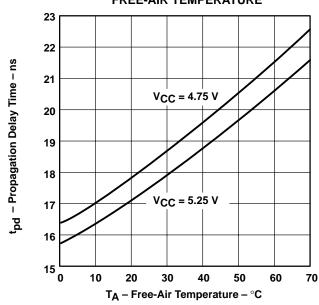

## driver switching characteristics over recommended ranges of operating conditions (unless otherwise noted)

|                      | PARAMETER                                                                                                        | TEST CONDITIONS                                                       | MIN  | TYP <sup>†</sup> | MAX  | UNIT |

|----------------------|------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|------|------------------|------|------|

| t <sub>d</sub> (OD)  | Differential delay time, high- to low-level output ( $t_{d(ODH)}$ ) or low-to high-level output ( $t_{d(ODL)}$ ) | See Figure 4                                                          | 11.8 |                  | 26.4 |      |

|                      |                                                                                                                  | $V_{CC} = 5 \text{ V}, \qquad T_A = 25^{\circ}\text{C},$ See Figure 4 | 14   | 18               | 22   | ns   |

|                      |                                                                                                                  | $V_{CC} = 5 \text{ V}, \qquad T_A = 70^{\circ}\text{C},$ See Figure 4 | 18   | 22               | 26   |      |

| + \                  | Skew limit, the maximum difference in propagation delay times                                                    |                                                                       |      |                  | 15   | ns   |

| <sup>t</sup> sk(lim) | between any two drivers on any two devices                                                                       | V <sub>CC</sub> = 5 V, See Note 2                                     |      |                  | 8    | 110  |

| t <sub>sk(p)</sub>   | Pulse skew ( t <sub>d</sub> (ODL) - t <sub>d</sub> (ODH) )                                                       | See Figure 4                                                          |      | 0                | 6    | ns   |

| t <sub>t</sub>       | Transition time (t <sub>r</sub> or t <sub>f</sub> )                                                              | See Figure 4                                                          |      | 10               | ·    | ns   |

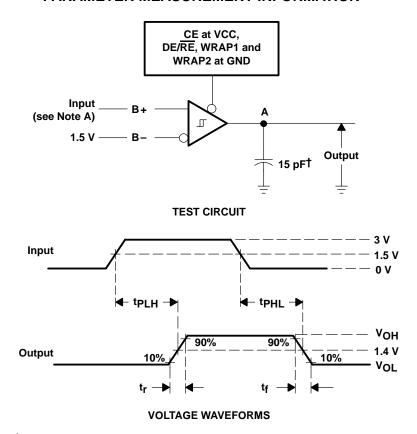

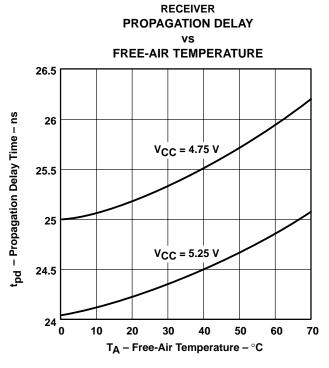

#### receiver switching characteristics over recommended ranges of operating conditions (unless otherwise noted)

|                      | PARAMETER                                                     | TEST CONDI                                            | ITIONS     | MIN  | TYP† | MAX  | UNIT |

|----------------------|---------------------------------------------------------------|-------------------------------------------------------|------------|------|------|------|------|

| t <sub>pd</sub>      |                                                               | See Figure 5                                          |            | 19.5 |      | 30.7 |      |

|                      |                                                               | V <sub>CC</sub> = 5 V, T <sub>i</sub><br>See Figure 5 | A = 25°C,  | 20.2 | 24.7 | 29.2 | ns   |

|                      | mgn 10701 odipat (tpLn)                                       | V <sub>CC</sub> = 5 V, T <sub>i</sub><br>See Figure 5 | A = 70°C,  | 21.1 | 25.6 | 30.1 |      |

|                      | Skew limit, the maximum difference in propagation delay times |                                                       |            |      |      | 12   | no   |

| <sup>l</sup> sk(lim) | tsk(lim) between any two drivers on any two devices           |                                                       | See Note 2 |      |      | 9    | ns   |

| t <sub>sk(p)</sub>   | Pulse skew ( tpHL - tpLH )                                    | See Figure 5                                          |            |      | 2    | 6    | ns   |

| t <sub>t</sub>       | Transition timeor(tr)                                         |                                                       |            |      | 3    |      | ns   |

<sup>†</sup> All typical values are at  $V_{CC} = 5 \text{ V}$ ,  $T_A = 25^{\circ}\text{C}$ . ‡  $C_{pd}$  determines the no-load dynamic current consumption;  $I_S = C_{pd} \cdot V_{CC} \cdot f + I_{CC}$ . NOTE 2: This specification applies to any 5°C band within the operating temperature range.

SLLS134E - APRIL 1992 - REVISED MAY 1997

#### transceiver switching characteristics over recommended ranges of operating conditions

|                 | PARAMETER                                                      | TEST CONDITIONS | MIN | MAX | UNIT |

|-----------------|----------------------------------------------------------------|-----------------|-----|-----|------|

| ten(TXL)        | Enable time, transmit-to-receive to low-level output           |                 |     | 80  | ns   |

| ten(TXH)        | Enable time, transmit-to-receive to high-level output          |                 |     | 80  | ns   |

| ten(RXL)        | Enable time, receive-to-transmit to low-level output           | See Figure 6    |     | 150 | ns   |

| ten(RXH)        | Enable time, receive-to-transmit to high-level output          |                 |     | 150 | ns   |

| t <sub>su</sub> | Setup time, WRAP1 or WRAP2 before active input(s) or output(s) |                 | 150 |     | ns   |

#### thermal characteristics

| PARAMETER       |                                         | TEST CONDITIONS            | MIN | TYP | MAX | UNIT |

|-----------------|-----------------------------------------|----------------------------|-----|-----|-----|------|

| $R_{\theta JA}$ | Junction-to-free-air thermal resistance | Board mounted, No air flow |     | 50  |     | °C/W |

| $R_{\theta JC}$ | Junction-to-case thermal resistance     |                            |     | 12  |     | °C/W |

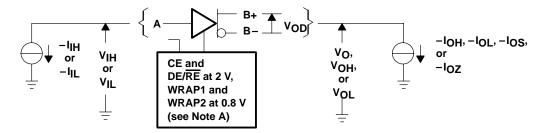

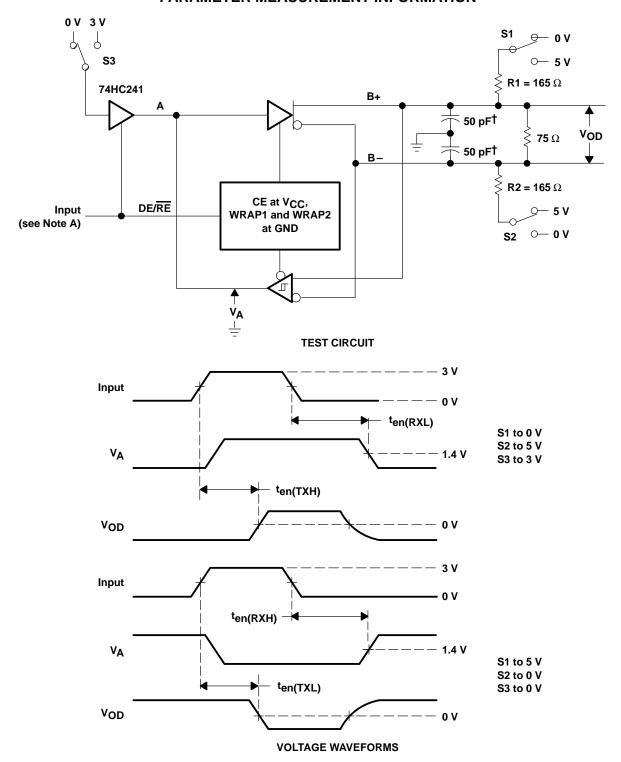

#### PARAMETER MEASUREMENT INFORMATION

Figure 1. Driver V<sub>OD</sub> Test Circuit

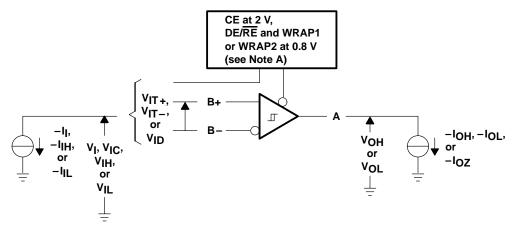

NOTE A: For the  $I_{\mbox{OZ}}$  measurement, CE is at 0.8 V.

Figure 2. Receiver Test Circuit and Input Conditions

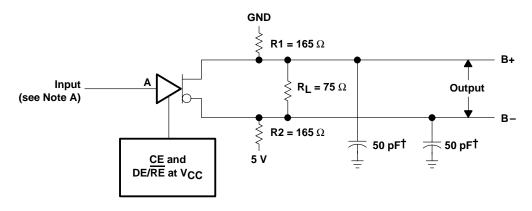

#### PARAMETER MEASUREMENT INFORMATION

NOTE A: For the  $I_{\mbox{\scriptsize OZ}}$  test, the CE input is at 0.8 V.

Figure 3. Driver Test and Input Conditions

#### **TEST CIRCUIT**

**VOLTAGE WAVEFORMS**

† Includes probe and jig capacitance.

NOTE A: The input is provided by a pulse generator with an output of 0 to 3 V, PRR of 1 MHz, 50% duty cycle,  $t_r$  and  $t_f < 6$  ns, and  $Z_O = 50 \Omega$ .

Figure 4. Driver Propagation Delay Time Test Circuit and Waveforms

#### PARAMETER MEASUREMENT INFORMATION

† Includes probe and jig capacitance.

NOTE A: The input is provided by a pulse generator with an output of 0 to 3 V, PRR of 1 MHz, 50% duty cycle,  $t_\Gamma$  and  $t_f$  < 6 ns, and  $Z_O$  = 50  $\Omega$ .

Figure 5. Receiver Propagation Delay Time Test Circuit and Waveforms

#### PARAMETER MEASUREMENT INFORMATION

<sup>†</sup> Includes probe and jig capacitance.

NOTE A: The input is provided by a pulse generator with an output of 0 to 3 V, PRR of 1 MHz, 50% duty cycle,  $t_f$  and  $t_f$  < 6 ns, and  $Z_O$  = 50  $\Omega$ .

Figure 6. Enable Time Test Circuit and Voltage Waveforms

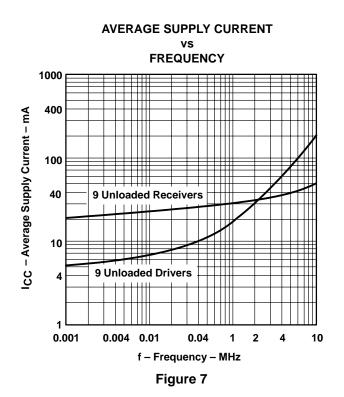

Figure 8

DRIVER **HIGH-LEVEL OUTPUT VOLTAGE HIGH-LEVEL OUTPUT CURRENT** 5 B+ and B-4.75 VOH - High-Level Output Voltage - mV 4.5 4.25 4  $V_{CC} = 5.25 \text{ V}$ 3.75  $V_{CC} = 5 V$ 3.5 3.25 3 2.75 V<sub>CC</sub> = 4.75 \ 2.5 30 50 0 10 20 40 60 70 80 90

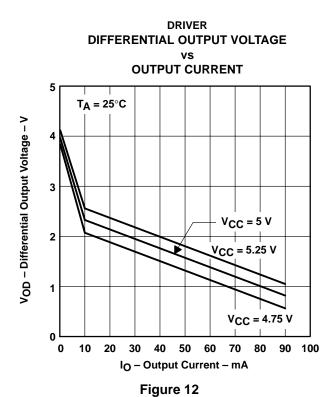

Figure 10

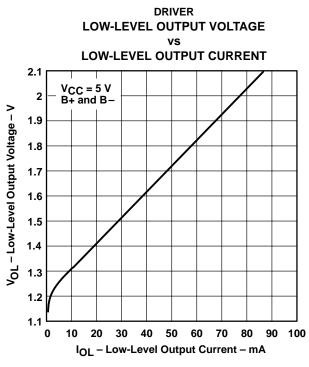

Figure 11

IOH - High-Level Output Current - mA

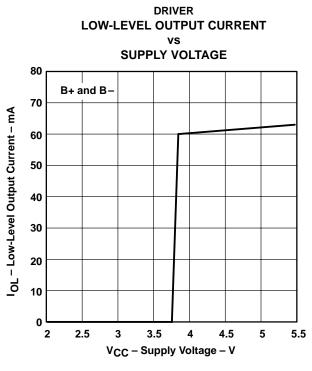

Figure 13

DRIVER **HIGH-LEVEL OUTPUT CURRENT SUPPLY VOLTAGE** 0 B+ and B--10IOH - High-Level Output Current - mA - 20 - 30 -40- 50 - 60 **- 70** - 80 <u>-</u> 2.5 3.5 5.5 V<sub>CC</sub> - Supply Voltage - V

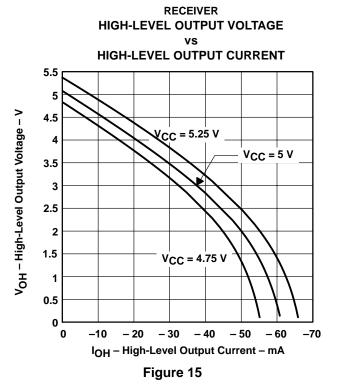

Figure 14

Figure 18

# DRIVER PROPAGATION DELAY TIME vs FREE-AIR TEMPERATURE

Figure 19

#### **APPLICATION INFORMATION**

#### function tables

Table 1. Channel Configuration for Totem Pole Circuit

CE is high, WRAP1 or WRAP2 is low

|       | 0 | UTPUT | S   |   |    |    |

|-------|---|-------|-----|---|----|----|

| DE/RE | Α | в+†   | в-† | Α | B+ | B- |

| L     | Χ | L     | H   | L | Z  | Ζ  |

| L     | Χ | Н     | L   | Н | Z  | Z  |

| Н     | L | X     | Χ   | Z | L  | Н  |

| Н     | Н | Χ     | Χ   | Z | Н  | L  |

H = high level L = low level X = irrelevant Z = high impedance

#### Table 2. Channel Configuration for Emitter Follower Circuit

CE is high, WRAP1 or WRAP2 is high

| IN    | PUTS | 0 | UTPUT | S  |   |

|-------|------|---|-------|----|---|

| DE/RE | B+   | Α | B+    | B- |   |

| L     | L    | Н | L     | Z  | Z |

| L     | Н    | L | Н     | Z  | Z |

| Н     | Χ    | Χ | Н     | Н  | L |

| Н     | Χ    | X | Н     | Н  | L |

$H = high \ level \ L = low \ level \ X = irrelevant \ Z = high impedance$

<sup>†</sup> An H in this column represents a voltage 200 mV higher than the other bus input. An L represents a voltage 200 mV lower than the other bus input. Any voltage less than 200 mV results in an indeterminate receiver output.

SLLS134E - APRIL 1992 - REVISED MAY 1997

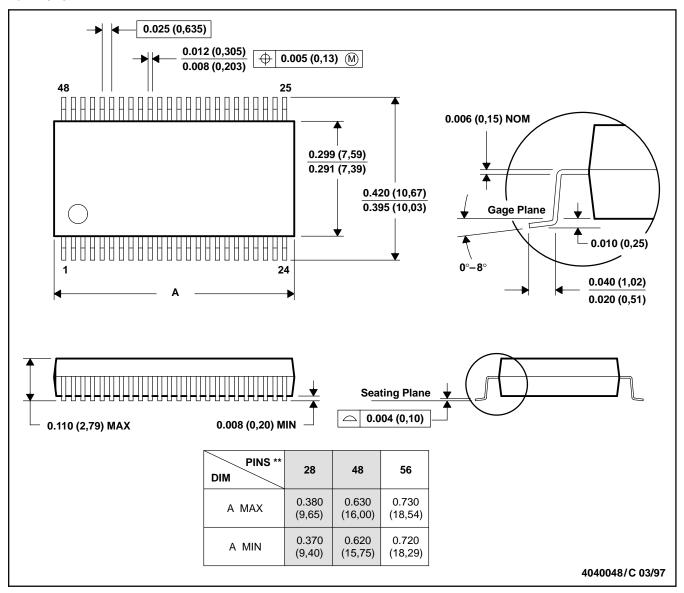

#### **MECHANICAL INFORMATION**

#### DL (R-PDSO-G\*\*)

#### PLASTIC SMALL-OUTLINE PACKAGE

#### **48 PIN SHOWN**

NOTES: A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion not to exceed 0.006 (0,15).

- D. Falls within JEDEC MO-118

#### **IMPORTANT NOTICE**

Texas Instruments (TI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

TI warrants performance of its semiconductor products and related software to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Certain applications using semiconductor products may involve potential risks of death, personal injury, or severe property or environmental damage ("Critical Applications").

TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

Inclusion of TI products in such applications is understood to be fully at the risk of the customer. Use of TI products in such applications requires the written approval of an appropriate TI officer. Questions concerning potential risk applications should be directed to TI through a local SC sales office.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards should be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

Copyright © 1996, Texas Instruments Incorporated