- Industrial Temperature Version of the TFB2002B With an Operating Range of -20°C to 85°C

- Provides Control Logic Necessary to Operate a Data Path Unit (TFB2022A) on Futurebus+

- Parallel-Protocol Support Is Fully Compliant to Futurebus+ Standard (IEEE Std 896.1–1991)

- Interfaces Easily to a Variety of Popular Microprocessors Such as SPARC™, R4000, 680x0, 88xxx, 80x86, and Alpha AXP™

- Provides Full Support for Futurebus+ Cache Commands (for Memory or I/O Modules in Shared-Memory Systems)

- Capable of Handling a Single Outstanding Split Transaction

- Parallel-Protocol-Related CSR Locations Are Provided on Chip

- Offers Autonomous Control for Futurebus+ and Host-Module Reads and Writes

#### description

The TFB2002BI I/O controller (IOC) is a member of the Texas Instruments Futurebus+ (FB+) chip set. This chip set provides a highly integrated approach to the Futurebus+ interface that reduces new-product design time, allows more functionality per circuit board, improves overall interface reliability, and reduces end-user down time through built-in test capabilities. The Futurebus+ chip set is capable of supporting 32- or 64-bit data widths in any combination on both the host-bus interface (HIF) and Futurebus+. The address width is programmable to be 32 bits or 36 bits (with either data width).

The TFB2002BI contains the control logic necessary to translate Futurebus+ transactions into host bus transactions and vice versa. It contains a high-speed Futurebus+ handshake controller, a synchronous host bus controller, and reset-type determination logic.

When combined with a TFB2022A Futurebus+ data path unit (DPU), the TFB2002BI provides a complete 64-bit-wide interface to the Futurebus+. The TFB2002BI provides the necessary control logic for the data path unit to provide a complete interface to the Futurebus+ for a Profile-B-compliant module. It may also be used on I/O or memory modules in a cache-coherent system.

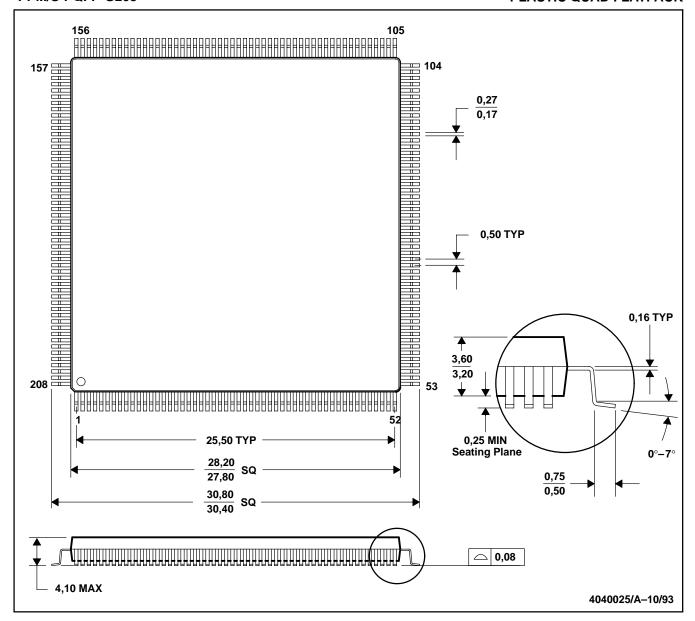

The TFB2002BI is offered in a 208-pin plastic quad flat package (PPM). The TFB2002BI is characterized for operation over the industrial temperature range of  $-20^{\circ}$ C to  $85^{\circ}$ C.

NOTE: To maintain consistency with the notation used in the Futurebus+standard (IEEE Std 896. 1–1991), an active-low signal is denoted herein by use of the trailing asterisk (\*) on the signal name.

SPARC is a trademark of Sun Microsystems, Inc. Alpha AXP is a trademark of Digital Equipment Corporation.

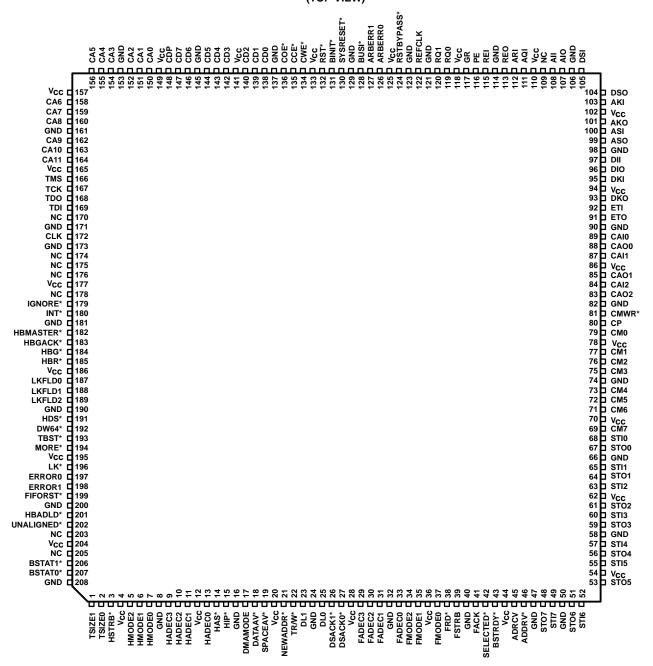

#### terminal assignments

#### PPM PACKAGE (TOP VIEW)

NC - No internal connection

# **Terminal Functions**

#### host interface

| TERMINA                      | AL                | 1/2                     | FROMTO         | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|------------------------------|-------------------|-------------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME                         | NO.               | I/O                     | FROM/TO        | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| BSTAT<1:0>*                  | 206<br>207        | I/O                     | Host interface | Host-interface status:  HH Normal  HL Reserved  LH Bus error  LL Backoff/retry                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| BSTRDY*                      | 43                | I/O                     | Host interface | Burst ready                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| CLK                          | 172               | I                       | Host interface | Clock input. CLK is the processor clock for synchronous transactions on the host side. Up to 25 MHz is recommended.                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| DL<1:0>                      | 23, 25            | I/O                     | Host interface | Host-interface data length:  LL 64 bytes  LH 32 bytes  HL 16 bytes  HH 8 bytes                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| DSACK<1:0>*                  | 26<br>27          | I/O                     | Host interface | Data acknowledge: Single mode (TBST* = high): Burst mode (TBST* = low):  LL Complete cycle, LL Low speed, 32-bit burst capable data bus port 32  LH Reserved LH High speed, 32-bit burst capable HL Reserved HL Low speed, 64-bit burst capable HH Insert wait state HH High speed, 64-bit burst capable                                                                                                                                                   |  |  |  |

| DW64*                        | 192               | I/O                     | Host interface | Host-interface data width of 64 (burst mode only)                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| HAS*                         | 14                | I/O                     | Host interface | Host-interface address strobe                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| HBG*                         | 184               | ı                       | Host interface | Host-interface grant input                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| HBGACK*                      | 183               | I/O<br>(open collector) | Host interface | Host-interface grant acknowledge                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| HBR*                         | 185               | O<br>(open collector)   | Host interface | Host-interface request output                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| HDS*                         | 191               | I/O                     | Host interface | Host-interface data strobe                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| HIP*                         | 15                | I/O                     | Host interface | Host-interface transaction in progress                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| IGNORE*                      | 179               | I                       | Host interface | Ignore the current host transaction input. IGNORE* is supplied by the host-memory decoder when an access to private memory occurs. IGNORE* is optional and should be tied high if it is not used.                                                                                                                                                                                                                                                          |  |  |  |

| INT*                         | 180               | O<br>(open collector)   | Host interface | Host interrupt output. When an enabled interrupt condition occurs, INT* is driven low. Interrupts are cleared by writing a one to the appropriate bit in the interrupt register. The interrupt goes high during the write cycle to the interrupt register even if another interrupt is pending. Also used from FB+ CM<2:0> lines to a mastered HIF locked operation. These terminals are used as inputs when the IOC is a host-interface slave/FB+ master. |  |  |  |

| LK*                          | 196               | I/O                     | Host interface | Host cycle is locked (indivisible)                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| LKFLD0,<br>LKFLD1,<br>LKFLD2 | 187<br>188<br>189 | I/O                     | Host interface | Locked-command bits passed from the host interface to FB+ or from FB+ to the host interface via the CM<2:0> lines during a mastered FB+ data phase in a locked operation. Also used from FB+ CM<2:0> lines to a mastered HIF locked operation. These terminals are used as inputs when the IOC is a host interface slave/FB+ master.                                                                                                                       |  |  |  |

## **Terminal Functions**

## host interface (continued)

| TERMIN        | AL   | 1/0 | FROM/TO        | DESCRIPTION                                                                                                                                                                                                                                                                                       |  |  |  |

|---------------|------|-----|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME          | NO.  | 1/0 | FROM/10        | DESCRIPTION                                                                                                                                                                                                                                                                                       |  |  |  |

| MORE*         | 194  | I   | Host interface | Host cycle is part of a longer transaction input. MORE* is used in DMA writes to indicate that this transaction should be included in the same tenure with the next host-interface transaction. MORE* is used in reads to indicate that MR* should be asserted during the Futurebus+ transaction. |  |  |  |

| TBST*         | 193  | I/O | Host interface | Host-transaction burst request                                                                                                                                                                                                                                                                    |  |  |  |

| TR/W*         | 22   | I/O | Host interface | Host-interface read or write                                                                                                                                                                                                                                                                      |  |  |  |

| TSIZE < 1:0 > | 1, 2 | I   | Host interface | Host-interface transaction size input:  LL Word (32 bits or greater)  LH Byte (8 bits)  HL Half word (16 bits)  HH Three bytes (24 bits)                                                                                                                                                          |  |  |  |

## other module interface signals

| TERMINAL    |             | 1/0 | FROM/TO | DESCRIPTION                                                                                                                                                    |  |  |

|-------------|-------------|-----|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME        | NO.         | 1/0 | FROM/10 | DESCRIPTION                                                                                                                                                    |  |  |

| ARBERR<1:0> | 127,<br>126 | I   | Arbiter | Arbitration error input:  LL No error  LH ACO and AC1 asserted during phase 3  HL Arbitration comparison error  HH Arbitration time-out error (phase 2 or 4)   |  |  |

| REFCLK      | 122         | I   | Module  | Clock input. A 25-MHz, 50% $\pm$ 5% duty-cycle signal is recommended; any frequency between 20 MHz and 40 MHz and duty cycle of 50% $\pm$ 5% can be tolerated. |  |  |

#### **CSR** bus

| TER      | RMINAL                                                              | 1/0 | FROM/TO | DESCRIPTION             |  |  |

|----------|---------------------------------------------------------------------|-----|---------|-------------------------|--|--|

| NAME     | NO.                                                                 | 2   | FROM/10 | DESCRIPTION             |  |  |

| CA<11:0> | 164, 163, 162,<br>160, 159, 158,<br>156, 155, 154,<br>152, 151, 150 | -   | CSR bus | CSR bus address         |  |  |

| CD<7:0>  | 147, 146, 144,<br>143, 142, 140,<br>139, 138                        | I/O | CSR bus | CSR bus data            |  |  |

| CDP      | 148                                                                 | I/O | CSR bus | CSR bus data odd parity |  |  |

| CCE*     | 135                                                                 | I   | CSR bus | CSR bus chip enable     |  |  |

| COE*     | 136                                                                 | I   | CSR bus | CSR bus output enable   |  |  |

| CWE*     | 134                                                                 | I   | CSR bus | CSR bus write enable    |  |  |

# **Terminal Functions**

#### interface to TFB2022A

| TERMIN        | NAL        | l.,,_ |              | DECORPORA                                                                                                                                                                                                                                                                                                                     |  |  |

|---------------|------------|-------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME          | NO.        | 1/0   | FROM/TO      | DESCRIPTION                                                                                                                                                                                                                                                                                                                   |  |  |

| DATAAV*       | 18         | I     | TFB2022A DPU | Data available in FIFO. In compelled mode, DATAAV* indicates if any data is in the FIFO. In packet or burst mode, DATAAV* indicates if a packet or burst data of length encoded on the Futurebus packet size or the DL<1:0> lines is available.                                                                               |  |  |

| DMAMODE       | 17         | 0     | TFB2022A DPU | DMA operation is occurring. DMAMODE turns off critical word first on the TFB2022A.                                                                                                                                                                                                                                            |  |  |

| ERROR<1:0>    | 198, 197   | I     | TFB2022A DPU | Futurebus+ error indicators:                                                                                                                                                                                                                                                                                                  |  |  |

|               |            |       |              | LL No error LH Futurebus+ parity error HL Packet longitudinal parity error HH Host-bus parity error                                                                                                                                                                                                                           |  |  |

| FADEC < 3:0>  | 29, 30     | I     | TFB2022A DPU | Futurebus+ address decode:                                                                                                                                                                                                                                                                                                    |  |  |

|               | 31, 33     |       |              | LLLL Unselected  LLLH Host memory  LLHL Host extended-unit space  LLHH Host CSR  LHLL Broadcast mailbox  LHLH Reserved  LHHL Reserved  LHHL Mailbox address  HLLL Mailbox address  HLLH Packet-mode-capable memory address  HLH Reserved  HLHL Reserved  HLHL Reserved  HLH Broadcast CSR (non-DPU)  HHHH Broadcast CSR (DPU) |  |  |

| FIFORST*      | 199        | 0     | TFB2022A DPU | FIFO reset. FIFORST* resets the FIFO pointers.                                                                                                                                                                                                                                                                                |  |  |

| FACK          | 41         | ı     | TFB2022A DPU | Futurebus+ acknowledge. FACK indicates Futurebus+ event is complete                                                                                                                                                                                                                                                           |  |  |

| FMODE < 2:0 > | 34, 35, 37 | 0     | TFB2022A DPU | Futurebus+ mode. FMODE < 2:0 > indicates to the TFB2022A what action is to be taken in the Futurebus+ interface:                                                                                                                                                                                                              |  |  |

|               |            |       |              | LLL Compelled-mode Futurebus+ LLH Packet-mode Futurebus+ LHL Partial transfer LHH Disconnect data for master write HLL Reserved HLH Reserved HHL Disconnect data for split requestor HHH Reserved                                                                                                                             |  |  |

| FRD*          | 38         | 0     | TFB2022A DPU | Futurebus+ read/write indicator: L = read from Futurebus+ to FIFO; H = write from FIFO to Futurebus+                                                                                                                                                                                                                          |  |  |

| FSTRB         | 39         | 0     | TFB2022A DPU | Futurebus+ strobe. FSTRB performs next Futurebus+ event                                                                                                                                                                                                                                                                       |  |  |

## **Terminal Functions**

## interface to TFB2022A (continued)

| TERMINAL<br>NAME NO. |         | 1/0 | FROM/TO      | DESCRIPTION                                                                                                        |                                                                                                                                                                               |                                           |                                                                            |  |  |

|----------------------|---------|-----|--------------|--------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|----------------------------------------------------------------------------|--|--|

| HADEC < 3:0 >        | 9, 10,  | I   | TFB2022A DPU | Host address decode. Address decoding for the host-interface address:                                              |                                                                                                                                                                               |                                           |                                                                            |  |  |

|                      | 11, 13  |     |              | Slave enco                                                                                                         | ding:                                                                                                                                                                         | Master enc                                | oding:                                                                     |  |  |

|                      |         |     |              | LLLL<br>LLLH<br>LLHL                                                                                               | Unselected<br>Host memory<br>Host extended-unit space                                                                                                                         | LLLL<br>LLLH<br>LLHL                      | Unselected Memory address compelled Maximum capable burst or               |  |  |

|                      |         |     |              | LLHH                                                                                                               | Host CSR                                                                                                                                                                      | LLHH                                      | extended unit space<br>Memory address 64-byte<br>burst                     |  |  |

|                      |         |     |              | LHLL                                                                                                               | Broadcast mailbox                                                                                                                                                             | LHLL                                      | 32-byte-memory-address capable                                             |  |  |

|                      |         |     |              | LHLH                                                                                                               | Reserved                                                                                                                                                                      | LHLH                                      | 16-byte-memory-address capable                                             |  |  |

|                      |         |     |              | LHHL                                                                                                               | Split response hit                                                                                                                                                            | LHHL                                      | 8-byte-memory-address capable                                              |  |  |

|                      |         |     |              | LHHH                                                                                                               | Futurebus+ CSR address                                                                                                                                                        | LHHH                                      | Reserved                                                                   |  |  |

|                      |         |     |              | HLLL                                                                                                               | Reserved                                                                                                                                                                      | HLLL                                      | Reserved                                                                   |  |  |

|                      |         |     |              | HLLH                                                                                                               | Broadcast CSR address                                                                                                                                                         | HLLH                                      | Reserved                                                                   |  |  |

|                      |         |     |              | HLHL                                                                                                               | Reserved                                                                                                                                                                      | HLHL                                      | Reserved                                                                   |  |  |

|                      |         |     |              | HLHH                                                                                                               | Reserved                                                                                                                                                                      | HLHH                                      | Reserved                                                                   |  |  |

|                      |         |     |              | HHLL                                                                                                               | Reserved                                                                                                                                                                      | HHLL                                      | Reserved                                                                   |  |  |

| Í                    |         |     |              | HHLH                                                                                                               | DPU CSR                                                                                                                                                                       | HHLH                                      | Reserved                                                                   |  |  |

|                      |         |     |              | HHHL                                                                                                               | Reserved                                                                                                                                                                      | HHHL                                      | Reserved                                                                   |  |  |

|                      |         |     |              | HHHH                                                                                                               | Reserved                                                                                                                                                                      | HHHH                                      | Reserved                                                                   |  |  |

| HBADLD*              | 201     | 0   | TFB2022A DPU | Host address load. Futurebus+ has been granted for the requested transaction output.                               |                                                                                                                                                                               |                                           |                                                                            |  |  |

| HBMASTER*            | 182     | 0   | TFB2022A DPU | Host maste                                                                                                         | er. This device is mastering the                                                                                                                                              | host bus trar                             | nsaction.                                                                  |  |  |

| HMODE < 2:0 >        | 5, 6, 7 | 0   | TFB2022A DPU | Host mode the host int                                                                                             | . HMODE < 2:0 > indicates to the erface:                                                                                                                                      | ne TFB2022A                               | what action is to be taken in                                              |  |  |

|                      |         |     |              |                                                                                                                    | Reserved Between FIFO and host inte TFB2022A resident CSR ar TFB2022A resident CSR ar From FIFO to TFB2022A re Reserved Reserved Between FIFO and host inte Reserved Reserved | nd host interfa<br>nd FIFO<br>sident CSR. | ce, or between                                                             |  |  |

| HSTRB*               | 3       | 0   | TFB2022A DPU | Host strok                                                                                                         | •                                                                                                                                                                             | host-interfa                              | ce request as indicated in                                                 |  |  |

| NEWADDR*             | 21      | 0   | TFB2022A DPU | New address. NEWADDR* increments address in the TFB2022A address register.                                         |                                                                                                                                                                               |                                           |                                                                            |  |  |

| SELECTED*            | 42      | 0   | TFB2022A DPU | Module selected. Futurebus+ transaction uses this module. The DPU is used as a slave of the Futurebus+ transaction |                                                                                                                                                                               |                                           |                                                                            |  |  |

| SPACEAV*             | 19      | I   | TFB2022A DPU | available in                                                                                                       |                                                                                                                                                                               | n packet or bu                            | CEAV* indicates that space is<br>irst mode, SPACEAV* indicates<br>or burst |  |  |

|                      |         |     | TFB2022A DPU | <del></del>                                                                                                        | partial unaligned operation                                                                                                                                                   |                                           |                                                                            |  |  |

# **Terminal Functions**

#### JTAG test port

| TERMIN | TERMINAL I/O |     | FROM/TO | DESCRIPTION           |  |

|--------|--------------|-----|---------|-----------------------|--|

| NAME   | NO.          | 1/0 | FROW/10 | DESCRIFTION           |  |

| TCK    | 167          | I   | Module  | JTAG test clock       |  |

| TDI    | 169          | I   | Module  | JTAG test data in     |  |

| TDO    | 168          | 0   | Module  | JTAG test data out    |  |

| TMS    | 166          | I   | Module  | JTAG test-mode select |  |

#### reset port

| TERMINA    | L   |     | FROMTO  | DECODIDATION                                                                                                                                                                   |  |  |

|------------|-----|-----|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME       | NO. | 1/0 | FROM/TO | DESCRIPTION                                                                                                                                                                    |  |  |

| AQI        | 111 | I   |         | Arbitration handshake. AQI is used to determine if the arbitration bus has been idle for 1 $\mu$ s. If the arbitration bus is not implemented, this signal should be tied low. |  |  |

| ARI        | 112 | I   |         | Arbitration handshake. ARI is used to determine if the arbitration bus has been idle for 1 plf the arbitration bus is not implemented, this signal should be tied high.        |  |  |

| BINIT*     | 131 | 0   | Module  | Bus interface reset. BINIT* is an open-collector signal indicating that a bus interface reset is required.                                                                     |  |  |

| BUSI*      | 128 | 0   |         | Bus idle. Bus has been idle for longer than 1 µs, and REO is asserted.                                                                                                         |  |  |

| REI        | 115 | I   |         | Futurebus+ reset in                                                                                                                                                            |  |  |

| REO        | 113 | 0   |         | Futurebus+ reset out                                                                                                                                                           |  |  |

| RST*       | 132 | I   | Module  | Module power-up reset. RST* resets all logic; output signals go to their inactive states, state outputs and bidirectional signals take on the high-impedance state.            |  |  |

| SYSRESET*  | 130 | 0   | Module  | System reset required. SYSRESET* is an open-collector signal indicating that a system reset is required.                                                                       |  |  |

| RSTBYPASS* | 124 | I   | Module  | Reset bypass. Bypass auto alignment after power up.                                                                                                                            |  |  |

#### **Terminal Functions**

#### Futurebus+ interface

| TERM          | INAL                                     | 1/0 | EDOM/TO    | DECORIDATION                                                                                                                        |  |

|---------------|------------------------------------------|-----|------------|-------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME          | NO.                                      | 1/0 | FROM/TO    | DESCRIPTION                                                                                                                         |  |

| ADRCV         | 45                                       | 0   | Futurebus+ | Transceiver receiver enable                                                                                                         |  |

| ADDRV*        | 46                                       | 0   | Futurebus+ | Transceiver driver enable                                                                                                           |  |

| ASI, AKI, AII | 100, 103, 108                            | I   | Futurebus+ | Futurebus+ address synchronization signals: address strobe (ASI), address acknowledge (AKI), address acknowledge inverse (AII)      |  |

| ASO, AKO, AIO | 99, 101, 107                             | 0   | Futurebus+ | Futurebus+ address synchronization signals: address strobe (ASO), address acknowledge (AKO), address acknowledge inverse (AIO)      |  |

| CAI<2:0>      | 84, 87, 89                               | I   | Futurebus+ | Futurebus+ capability bits                                                                                                          |  |

| CAO<2:0>      | 83, 85, 88                               | 0   | Futurebus+ | Futurebus+ capability bits                                                                                                          |  |

| CM<7:0>, CP   | 69, 71, 72, 73,<br>75, 76, 77, 79,<br>80 | I/O | Futurebus+ | Futurebus+ command bits and parity                                                                                                  |  |

| CMWR*         | 81                                       | 0   | Futurebus+ | Transceiver control for command: H = read, L = write                                                                                |  |

| DSI, DKI, DII | 105, 95, 97                              | 1   | Futurebus+ | ebus+ Futurebus+ data-path-synchronization input signals: data strobe (DSI), data acknowledge (DKI), data acknowledge inverse (DII) |  |

| DSO, DKO, DIO | 104, 93, 96                              | 0   | Futurebus+ | Futurebus+ data-path-synchronization output signals: data strobe (DSO), data acknowledge (DKO), data acknowledge inverse (DIO)      |  |

| ETI           | 92                                       | I   | Futurebus+ | Futurebus+ end-of-tenure in                                                                                                         |  |

| ETO           | 91                                       | 0   | Futurebus+ | Futurebus+ end-of-tenure out                                                                                                        |  |

| GR            | 117                                      | I   | Futurebus+ | Futurebus+ mastership has been granted (bus tenure may begin when ETI is released).                                                 |  |

| PE            | 116                                      | 1   | Futurebus+ | Futurebus+ preemption has occurred.                                                                                                 |  |

| RQ<1:0>       | 120, 119                                 | 0   | Futurebus+ | Futurebus+ is requested at level 1 or level 0. RQO is used for DMA operations; RQ1 is used for all other operations.                |  |

| STI<7:0>      | 49, 52, 55, 57,<br>60, 63, 65, 68        | I   | Futurebus+ | Futurebus+ status in                                                                                                                |  |

| STO<7:0>      | 48, 51, 53, 56,<br>59, 61, 64, 67        | 0   | Futurebus+ | Futurebus+ status out                                                                                                               |  |

## absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage range, V <sub>CC</sub> (see Note 1)   | $\dots \dots \dots \dots \dots -0.5$ V to 7 V                                                                        |

|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| Input voltage range, V <sub>I</sub> (at any input)   | $\dots \dots $ |

| Output voltage range, V <sub>O</sub>                 | –0.5 V to 7 V                                                                                                        |

| Continuous total power dissipation                   | See Dissipation Rating Table                                                                                         |

| Power dissipation                                    | 500 mW                                                                                                               |

| Operating free-air temperature range, T <sub>A</sub> | –20°C to 85°C                                                                                                        |

| Storage temperature range                            | –65°C to 150°C                                                                                                       |

| Case temperature for 10 seconds                      |                                                                                                                      |

NOTE 1: All voltage values are with respect to GND.

#### **DISSIPATION RATING TABLE**

| PACKAGE | $T_{\mbox{A}} \le 25^{\circ}\mbox{C}$ POWER RATING | DERATING FACTOR<br>ABOVE T <sub>A</sub> = 25°C | T <sub>A</sub> = 70°C<br>POWER RATING |

|---------|----------------------------------------------------|------------------------------------------------|---------------------------------------|

| PPM     | 3175 mW                                            | 25.4 mW/°C                                     | 2032 mW                               |

## recommended operating conditions

|                                          | MIN  | NOM | MAX  | UNIT |

|------------------------------------------|------|-----|------|------|

| Supply voltage, V <sub>CC</sub>          | 4.75 | 5   | 5.25 | V    |

| High-level input voltage, VIH            | 2    |     | VCC  | V    |

| Low-level input voltage, V <sub>IL</sub> | -0.5 |     | 0.8  | V    |

| Operating free-air temperature range, TA | -20  |     | 85   | °C   |

# electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

|      | PARAMETER                              | MACRO     | TEST CONDITIONS                                             | MIN | TYP | MAX | UNIT |

|------|----------------------------------------|-----------|-------------------------------------------------------------|-----|-----|-----|------|

| VIT  | Input threshold voltage                | IPI04LK   | $V_I = V_{CC}$ or 0 V,                                      |     | 1.3 |     | V    |

| VIT+ | Positive-going input threshold voltage | IPI09LK   | $I_{\parallel} = \pm 1 \mu A,$ $C_{\perp} = 7.4 \text{ pF}$ |     | 1.6 |     | V    |

| VIT- | Negative-going input threshold voltage | IPIO9LK C |                                                             |     | 1.2 |     | V    |

| VOL  | Low-level output voltage (open drain)  | OPI82LK   | $I_{OL} = 8 \text{ mA}$                                     |     |     | 0.5 | V    |

| Vон  | High-level output voltage              | OPI43LK   | $I_{OH} = -4 \text{ mA}$                                    | 3.7 |     |     | V    |

| VOL  | Low-level output voltage               | OP143LK   | I <sub>OL</sub> = 4 mA                                      |     |     | 0.5 | V    |

| Vон  | High-level output voltage              | OPI83LK   | $I_{OH} = -8 \text{ mA}$                                    | 3.7 |     |     | V    |

| VOL  | Low-level output voltage               | OPIOSEN   | I <sub>OL</sub> = 8 mA                                      |     |     | 0.5 | V    |

| Vон  | High-level output voltage              | OPIH3LK   | $I_{OH} = -12 \text{ mA}$                                   | 3.7 |     |     | V    |

| VOL  | Low-level output voltage               | OPINSLK   | I <sub>OL</sub> = 12 mA                                     |     |     | 0.5 | V    |

| VOH  | High-level output voltage              | OPJ83LK   | $I_{OH} = -8 \text{ mA}$                                    | 3.7 |     |     | V    |

| VOL  | Low-level output voltage               | OI JOSEK  | I <sub>OL</sub> = 8 mA                                      |     |     | 0.5 | V    |

#### macros

Table 1 lists the internal and external buffer macros used in the TFB2002BI design. To use this table, find the pin of interest and note the macro name(s). If there is an entry only in the input macro column, the pin is an input. If there is an entry only in the output macro column, the pin is an output. If there is an entry in both columns, this is a 3-state bidirectional pin. The macro(s) are also listed in the electrical characteristics table.

Table 1. TFB2002BI (IOC) Pin Names and Macro Numbers

| PIN NAME       | INPUT MACRO | OUTPUT MACRO |

|----------------|-------------|--------------|

| ADDRV*         |             | OPIH3LK      |

| ADRCV          |             | OPIH3LK      |

| All            | IPI04LK     |              |

| AIO            |             | OPI43LK      |

| AKI            | IPI04LK     |              |

| AKO            |             | OPI43LK      |

| AQI            | IPI04LK     |              |

| ARBERR<1:0>    | IPI04LK     |              |

| ARI            | IPI04LK     |              |

| ASI            | IPI04LK     |              |

| ASO            |             | OPI43LK      |

| BINIT*         |             | OPI43LK      |

| BSTAT < 1:0 >* | IPI04LK     | OPIH3LK      |

| BSTRDY*        | IPI04LK     | OPIH3LK      |

| PIN NAME | INPUT MACRO | OUTPUT MACRO |

|----------|-------------|--------------|

| BUSI*    |             | OPI43LK      |

| CA<11:0> | IPI04LK     |              |

| CAI<2:0> | IPI04LK     |              |

| CAO<2:0> |             | OPI43LK      |

| CCE*     | IPI04LK     |              |

| CD<7:0>  | IPI04LK     | OPJ83LK      |

| CDP      | IPI04LK     | OPJ83LK      |

| CLK      | IPI04LK     |              |

| CM<7:0>  | IPI04LK     | OPI43LK      |

| CMWR*    |             | OPI43LK      |

| COE*     | IPI04LK     |              |

| СР       | IPI04LK     | OPI43LK      |

| CWE*     | IPI04LK     |              |

| DATAAV*  | IPI04LK     |              |

Table 1. TFB2002BI (IOC) Pin Names and Macro Numbers (Continued)

| PIN NAME      | INPUT MACRO | OUTPUT MACRO |

|---------------|-------------|--------------|

| DII           | IPI04LK     |              |

| DIO           |             | OPI43LK      |

| DKI           | IPI04LK     |              |

| DKO           |             | OPI43LK      |

| DL<1:0>       | IPI04LK     | OPIH3LK      |

| DMAMODE       |             | OPI43LK      |

| DSACK<1:0>*   | IPI04LK     | OPIH3LK      |

| DSI           | IPI04LK     |              |

| DSO           |             | OPI43LK      |

| DW64*         | IPI04LK     | OPIH3LK      |

| ERROR<1:0>    | IPI04LK     |              |

| ETI           | IPI04LK     |              |

| ETO           |             | OPI43LK      |

| FACK          | IPI04LK     |              |

| FADEC < 3:0 > | IPI04LK     |              |

| FIFORST*      |             | OPI43LK      |

| FMODE < 2:0 > |             | OPI43LK      |

| FRD*          |             | OPI43LK      |

| FSTRB         |             | OPI43LK      |

| GR            | IPI04LK     |              |

| HADEC<3:0>    | IPI04LK     |              |

| HAS*          | IPI04LK     | OPIH3LK      |

| HBADLD*       |             | OPI43LK      |

| HBG*          | IPI04LK     |              |

| HBGACK*       | IPI04LK     | OPIH3LK      |

| HBMASTER*     |             | OPI43LK      |

| HBR*          |             | OPI82LK      |

| HDS*          | IPI04LK     | OPIH3LK      |

| HIP*          | IPI04LK     | OPIH3LK      |

| PIN NAME      | INPUT MACRO | OUTPUT MACRO |

|---------------|-------------|--------------|

| HMODE < 2:0 > |             | OPI43LK      |

| HSTRB*        |             | OPI43LK      |

| IGNORE*       | IPI04LK     |              |

| INT*          |             | OPI82LK      |

| LK*           | IPI04LK     | OPIH3LK      |

| LKFLD0, 1, 2  | IPI04LK     | OPI43LK      |

| MORE*         | IPI04LK     |              |

| NEWADDR*      |             | OPI43LK      |

| PE            | IPI04LK     |              |

| REFCLK        | IPI04LK     |              |

| REI           | IPI04LK     |              |

| REO           |             | OPI43LK      |

| RQ<1:0>       |             | OPI43LK      |

| RST*          | IPI09LK     |              |

| RSTBYPASS*    | IPI04LK     |              |

| SELECTED*     |             | OPI43LK      |

| SPACEAV*      | IPI04LK     |              |

| STI<7:0>      | IPI04LK     |              |

| STO<7:0>      |             | OPI43LK      |

| SYSRESET*     |             | OPI83LK      |

| TBST*         | IPI04LK     | OPIH3LK      |

| TCK           | IPI04LK     |              |

| TDI           | IPI04LK     |              |

| TDO           |             | OPI43LK      |

| TMS           | IPI04LK     |              |

| TR/W*         | IPI04LK     | OPIH3LK      |

| TSIZE < 1:0 > | IPI04LK     |              |

| UNALIGNED*    | IPI04LK     |              |

#### **MECHANICAL DATA**

#### PPM/S-PQFP-G208

#### **PLASTIC QUAD FLATPACK**

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Falls within JEDEC MO-143.

#### **IMPORTANT NOTICE**

Texas Instruments (TI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

TI warrants performance of its semiconductor products and related software to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Certain applications using semiconductor products may involve potential risks of death, personal injury, or severe property or environmental damage ("Critical Applications").

TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

Inclusion of TI products in such applications is understood to be fully at the risk of the customer. Use of TI products in such applications requires the written approval of an appropriate TI officer. Questions concerning potential risk applications should be directed to TI through a local SC sales office.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards should be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

Copyright © 1996, Texas Instruments Incorporated