SLOS214 - OCTOBER 1998

- ADSL Differential Receiver

- Preamp Features

- Low Voltage Noise . . . 2nV/VHz

- Accessible Output Pin for External Filtering

- Voltage Feedback,  $G_{min} = -1, 2$

- PGA Features

- Digitally Programmable Gain

- Constant -3 dB Bandwidth

- -22 dB to 20 dB Gain/Attenuation Range

- 6 dB Step Resolution

- Output Clamp Protection

- Separate Low Noise Preamp and PGA Stages

- High Speed

70-MHz Bandwidth (–3 dB)

200 V/μs Slew Rate

- Shutdown Control

- Wide Supply Range ±4.5 V to ±16 V

- PowerPAD<sup>™</sup> Package for Enhanced Thermal Performance

#### description

The THS7002 is high-speed programmable-gain amplifier, ideal for applications as an ADSL receiver for both central office and remote terminal, where line impedance can often vary depending on line conditions. Each channel on this device consists of a separate low-noise input preamp and a programmable gain amplifier (PGA). The preamp is a voltage-feedback amplifier offering a low  $2-nV/\sqrt{Hz}$  voltage noise. The output pin of the preamp is accessible so that filters can be easily added to the amplifier.

The 3-bit digitally controlled PGA provides a -22-dB to 20-dB attenuation/gain range with a 6-dB step resolution. In addition, the PGA provides both high and low output clamp protection to prevent the output signal from swinging outside the common-mode input range of an analog-to-digital converter. Both the preamp and the PGA provide a wide 70-MHz (-3 dB) bandwidth, with the PGA bandwidth remaining relatively constant over the entire gain/attenuation range. The THS7002 also provides independent shutdown control for power conservation and multiplexing. This device operates over a wide  $\pm 4.5$ -V to  $\pm 16$ -V supply voltage range.

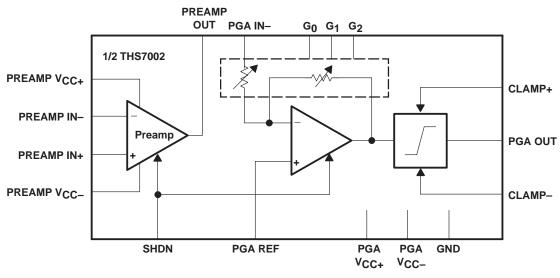

## Figure 1. One Channel of the THS7002

CAUTION: The THS7002 provides ESD protection circuitry. However, permanent damage can still occur if this device is subjected to high-energy electrostatic discharges. Proper ESD precautions are recommended to avoid any performance degradation or loss of functionality.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PowerPAD is a trademark of Texas Instruments Incorporated.

PRODUCT PREVIEW information concerns products in the formative or design phase of development. Characteristic data and other specifications are design goals. Texas Instruments reserves the right to change or discontinue these products without notice.

SLOS214 - OCTOBER 1998

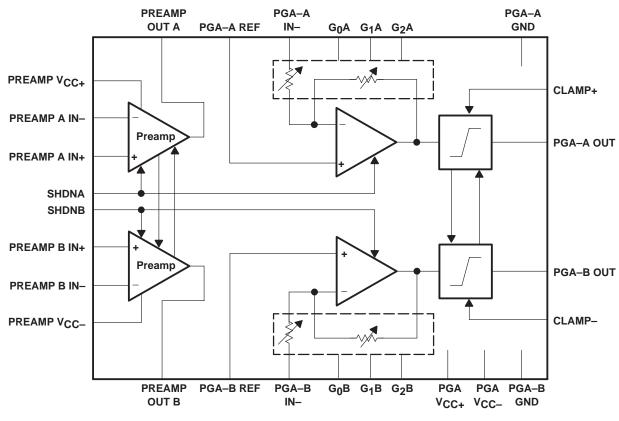

AVAILABLE OPTIONS

|               | PACKAGED DEVICES                |

|---------------|---------------------------------|

| TA            | PowerPAD PLASTIC TSSOP<br>(PWP) |

| 0°C to 70°C   | THS7002CPWP                     |

| -40°C to 85°C | THS7002IPWP                     |

SLOS214 - OCTOBER 1998

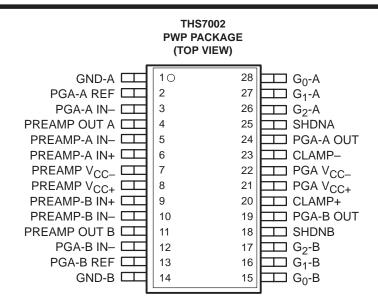

Figure 2. THS7002 Dual Channel PGA

## input preamp

To achieve the minimum input equivalent noise, the input preamp is configured as a classic voltage feedback amplifier with a minimum gain of 2 or -1. The output of the preamp is accessible, allowing for adjustment of gain using external resistors and for external filtering between the preamp and the PGA.

#### programmable gain amplifier (PGA)

The PGA is an inverting, programmable gain amplifier. The gain is digitally programmable using three control bits (TTL-compatible terminals) that are encoded to provide eight distinct levels of gain/attenuation. Nominal gain/attenuation is shown in Table 1.

| G <sub>2</sub> | G <sub>1</sub> | G <sub>0</sub> | PGA GAIN<br>(dB) |

|----------------|----------------|----------------|------------------|

| 0              | 0              | 0              | -22              |

| 0              | 0              | 1              | -16              |

| 0              | 1              | 0              | -10              |

| 0              | 1              | 1              | -4               |

| 1              | 0              | 0              | 2                |

| 1              | 0              | 1              | 8                |

| 1              | 1              | 0              | 14               |

| 1              | 1              | 1              | 20               |

#### Table 1. Nominal Gain/Attenuation

## block diagram

#### SLOS214 - OCTOBER 1998

#### output clamping

Output clamping for both upper (VH) and lower (VL) levels for the PGAs is provided. There is only one terminal for the positive output clamp and one for the negative output clamp for both channels.

#### shutdown control

The SHDN terminals allow for powering down the internal circuitry for power conservation or for multiplexing. Separate shutdown controls are available for each channel. The control levels are TTL compatible.

#### absolute maximum ratings over operating free-air temperature (see Notes 1 and 2)<sup>†</sup>

| Supply voltage, V <sub>CC</sub>                                                   | ±16.5 V          |

|-----------------------------------------------------------------------------------|------------------|

| Input voltage, VI                                                                 | ±V <sub>CC</sub> |

| Output current, I <sub>O</sub> (preamp) (see Note 1)                              | 150 mA           |

| I <sub>O</sub> (PGA) (see Note 1)                                                 | 50 mA            |

| Differential input voltage, VID                                                   | ±4 V             |

| Total continuous power dissipation at (or below) $T_A = 25^{\circ}C$ (see Note 2) | 4.48 W           |

| Operating free-air temperature, T <sub>A</sub>                                    | –40°C to 85°C    |

| Storage temperature, T <sub>stg</sub>                                             | –65°C to 125°C   |

| Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds                      | 300°C            |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- NOTES: 1. The THS7002 incorporates a PowerPAD on the underside of the chip. The PowerPAD acts as a heatsink and must be connected to a thermal dissipation plane for proper power dissipation. Failure to do so can result in exceeding the maximum junction temperature, which could permanently damage the device. See the *Thermal Information* section of this document for more information about PowerPAD technology.

- 2. For operation above  $T_A = 25^{\circ}C$ , derate linearly to 2.33 W at the rate of 35.9 mW/°C.

## recommended operating conditions

|                                                              |              | MIN   | NOM MAX | UNIT |

|--------------------------------------------------------------|--------------|-------|---------|------|

| Preamp supply voltage, V <sub>CC+</sub> and V <sub>CC-</sub> | Split supply | ±4.5  | ±16     | V    |

| PGA supply voltage, V <sub>CC+</sub> and V <sub>CC-</sub>    | Split supply | ±4.5‡ | ±16     | V    |

| Operating free-air temperature, T <sub>A</sub>               |              | -40   | 85      | °C   |

<sup>‡</sup>PGA minimum supply voltage **must be** less than or equal to preamp supply voltage.

SLOS214 - OCTOBER 1998

|                | PARAMETER                                 | TEST CON                                                                   | DITIONS <sup>†</sup>        | MIN           | TYP           | MAX   | UNIT  |

|----------------|-------------------------------------------|----------------------------------------------------------------------------|-----------------------------|---------------|---------------|-------|-------|

| VCC            | Supply voltage operating range            | y voltage operating range Split supply                                     |                             |               |               | ±16.5 | V     |

|                |                                           | $R_{I} = 1 k\Omega$                                                        | $V_{CC} = \pm 5 V$          | ±3.4          | ±3.8          |       |       |

| V              | Maximum output voltage swing              |                                                                            | $V_{CC} = \pm 15 V$         | ±13           | ±13.5         |       | V     |

| VOM            | Maximum output voltage swing              | Rլ = 150 kΩ                                                                | $V_{CC} = \pm 5 V$          | ±2.9          | ±3.3          |       | v     |

|                |                                           | KL = 100 K22                                                               | $V_{CC} = \pm 15 V$         | ±12           | ±12.6         |       |       |

| Vie            | Input offect veltors                      | V <sub>CC</sub> = ±5 V or ±15 V                                            | $T_A = 25^{\circ}C$         |               | 1.5           | 6     | mV    |

| VIO            | Input offset voltage                      | $ACC = \pm 2 A OL \pm 12 A$                                                | $T_A = $ full range         |               |               | 8     | mv    |

|                | Input offset voltage drift                |                                                                            |                             |               | 10            |       | μV/°C |

|                |                                           | $V_{CC} = \pm 5 V$                                                         |                             | 3.6<br>-3     | 4.4<br>3.8    |       |       |

| VICR           | Common-mode input voltage range           | V <sub>CC</sub> = ±15 V                                                    |                             | 13.5<br>-13.2 | 14.8<br>-14.2 |       | V     |

|                | Output ourrest (see Note 2)               | D: 450.0                                                                   | $V_{CC} = \pm 5 V$          |               | 85            |       | A     |

| 0              | Output current (see Note 3)               | R <sub>L</sub> = 150 Ω                                                     | $V_{CC} = \pm 15 V$         | 80            | 95            | mA    |       |

| loc            | Short-circuit output current (see Note 3) | V <sub>CC</sub> = ±15 V                                                    | RL = 20 Ω                   |               | 125           |       | mA    |

|                | lanut hing aumont                         |                                                                            | T <sub>A</sub> = 25°C       |               | 3             | 6     | A     |

| IВ             | Input bias current                        | $V_{CC} = \pm 5 V \text{ or } \pm 15 V$                                    | T <sub>A</sub> = full range |               |               | 8     | μA    |

|                | Input offset current                      | V <sub>CC</sub> = ±5 V or ±15 V                                            | T <sub>A</sub> = 25°C       |               | 30            | 175   | ~ ^   |

| 10             |                                           | $VCC = \pm 3 \vee 01 \pm 13 \vee$                                          | T <sub>A</sub> = full range |               |               | 400   | nA    |

|                | Input offset current drift                |                                                                            |                             |               | 0.3           |       | nA/°C |

|                |                                           | V <sub>CC</sub> = ±5 V,                                                    | $T_A = 25^{\circ}C$         | 85            | 95            |       |       |

| CMRR           | Common-mode rejection ratio               | $V_{IC} = \pm 2.5 V$                                                       | $T_A = $ full range         | 80            |               |       | dB    |

| CIVIRR         | Common-mode rejection ratio               | $V_{CC} = \pm 15 V,$                                                       | $T_A = 25^{\circ}C$         | 85            | 95            |       | uБ    |

|                |                                           | $V_{IC} = \pm 12 V$                                                        | $T_A = $ full range         | 80            |               |       | 1     |

|                | Dowor oupply rejection ratio              | V <sub>CC</sub> = ±5 V or ±15 V                                            | $T_A = 25^{\circ}C$         | 85            | 95            |       | dB    |

|                | Power supply rejection ratio              | $VCC = \pm 5 \vee 01 \pm 15 \vee$                                          | $T_A = $ full range         | 80            |               |       | uБ    |

| RI             | Input resistance                          |                                                                            |                             |               | 1             |       | MΩ    |

| Cl             | Input capacitance                         |                                                                            |                             |               | 1.2           |       | pF    |

| R <sub>O</sub> | Output resistance                         | Open loop                                                                  |                             |               | 12            |       | Ω     |

|                | Channel-to-channel crosstalk              | $V_{CC} = \pm 5 \text{ V or } \pm 15 \text{ V},$<br>$V_O = 200 \text{ mV}$ | f = 1 MHz,                  | 60            | 70            |       | dB    |

|                |                                           |                                                                            | $T_A = 25^{\circ}C$         |               | 6             | 8     |       |

| 100            | Quiescent current (per chappel)           | $V_{CC} = \pm 5 V$                                                         | $T_A = $ full range         |               |               | 9     | mA    |

| ICC            | Quiescent current (per channel)           |                                                                            | T <sub>A</sub> = 25°C       |               | 7             | 9     |       |

|                |                                           | $V_{CC} = \pm 15 V$                                                        | T <sub>A</sub> = full range |               |               | 10    |       |

# preamp electrical characteristics, G = 2, T\_A = 25°C, R\_L = 150 $\Omega$ , (unless otherwise noted)

<sup>†</sup> Full range for the THS7002C is 0°C to 70°C. Full range for the THS7002I is -40°C to 85°C.

NOTE 3: A heatsink may be required to keep the junction temperature below absoulte maximum when an output is heavily loaded or shorted. (See absolute maximum ratings and thermal information section.)

SLOS214 - OCTOBER 1998

# preamp operating characteristics, G = 2, T\_A = 25°C, R\_L = 150 $\Omega$ , (unless otherwise noted)

|                | PARAMETER                         | TEST CON                                                  | DITIONS <sup>†</sup>                       | MIN TYP | P MAX  | UNIT   |

|----------------|-----------------------------------|-----------------------------------------------------------|--------------------------------------------|---------|--------|--------|

| SR             | Slew rate (see Note 4)            | G = -1                                                    | $V_{O} = \pm 2 V,$<br>$V_{CC} = \pm 5 V$   | 175     | 5      | - V/μs |

| SK             | Siew rate (see Note 4)            | 0=-1                                                      | $V_{O} = \pm 10 V,$<br>$V_{CC} = \pm 15 V$ | 200     | )      | v/μs   |

|                | Settling time to 0.1%             | G = -1,<br>V <sub>I</sub> = 0 V to 2 V Step               | $V_{CC} = \pm 5 V$                         | 50      | )      | ns     |

| t <sub>S</sub> |                                   | G = -1,<br>0 V to 10 V Step                               | $V_{CC} = \pm 15 V$                        | 60      | )      | 115    |

|                | Settling time to 0.01%            | G = -1,<br>0 V to 10 V Step                               | $V_{CC} = \pm 15 V$                        | 8       | 5      | ns     |

| THD            | Total harmonic distortion         | $V_{CC} = \pm 15 V,$<br>$V_O = 1 V_O(PP)$                 | $f_{C} = 1 MHz,$                           | -84     | ļ.     | dBc    |

| Vn             | Input noise voltage               | $V_{CC} = \pm 5 \text{ V or } \pm 15 \text{ V},$          | f = 10 kHz                                 | 2       | 2      | nV/√H  |

| In             | Input noise current               | $V_{CC} = \pm 5 \text{ V or } \pm 15 \text{ V},$          | f = 10 kHz                                 | 1.5     | 5      | pA/√H  |

| BW             | Small-signal bandwidth (-3 dB)    | G = 2                                                     | $V_{CC} = \pm 5 V$                         | 60      | )      | MHz    |

| DVV            |                                   | 0=2                                                       | $V_{CC} = \pm 15 V$                        | 70      | )      |        |

|                | Bandwidth for 0.1 dB flatness     | G = 2                                                     | $V_{CC} = \pm 5 V$                         | 15      | 5      | MHz    |

|                |                                   | 0-2                                                       | V <sub>CC</sub> = ±15 V                    | 20      | )      | 101112 |

|                | Full power bandwidth (see Note 5) | $V_{CC} = \pm 5 V,$                                       | $V_{O} = 5 V_{O}(PP)$                      | 11      |        | MHz    |

|                |                                   | $V_{CC} = \pm 15 V,$                                      | V <sub>O</sub> = 20 V <sub>O(PP)</sub>     | 3.2     | 2      | 101112 |

| AD             | Differential gain error           | G = 2, ±100 IRE,                                          | $V_{CC} = \pm 5 V$                         | 0.02%   | D      |        |

| ~D             | Dinoronital gain orion            | NTSC                                                      | V <sub>CC</sub> = ±15 V                    | 0.06%   | ,<br>) |        |

| фD             | Differential phase error          | G = 2, ±100 IRE,                                          | $V_{CC} = \pm 5 V$                         | 0.10    | >      |        |

| ΨD             |                                   | NTSC                                                      | $V_{CC} = \pm 15 V$                        | 0.20    | 0      |        |

|                |                                   | $V_{CC} = \pm 5 V,$<br>$V_{O} = \pm 2.5 V,$               | $T_A = 25^{\circ}C$                        | 15 35   | 5      |        |

|                | Open loop gain                    | $R_L = 500 \Omega$                                        | $T_A = full range$                         | 10      |        | V/m\   |

|                |                                   | $V_{CC} = \pm 15 V_{,}$                                   | T <sub>A</sub> = 25°C                      | 18 45   | 5      | 1      |

|                |                                   | $V_0 = \pm 10 \text{ V}, \text{ R}_L = 1 \text{ k}\Omega$ |                                            | 12      |        | 1      |

<sup>†</sup> Full range for the THS7002C is 0°C to 70°C. Full range for the THS7002I is -40°C to 85°C.

NOTES: 4. Slew rate is measured from an output level range of 25% to 75%.

5. Full power bandwidth = slew rate/ $2\pi$  V(PP).

## shutdown characteristics

| PARAMETER |                                 | TEST CONDITIONS                           |                            | MIN | TYP                                           | MAX             | UNIT |  |     |   |

|-----------|---------------------------------|-------------------------------------------|----------------------------|-----|-----------------------------------------------|-----------------|------|--|-----|---|

| lO(OFF)   | Output current, disabled        | $V_{CC} = \pm 5 V \text{ or } \pm 15 V$ , | VI(SHDN) = 2.5 V           |     | 10                                            | 20              | μA   |  |     |   |

| VIH(SHDN) | Shutdown voltage for power-up   |                                           |                            |     | $\sqrt{22} - \pm 5 \sqrt{25} \pm 15 \sqrt{2}$ | Relative to GND |      |  | 0.8 | V |

| VIL(SHDN) | Shutdown voltage for power-down | $V_{CC} = \pm 5 V \text{ or } \pm 15 V,$  | Relative to GND            | 2   |                                               |                 | V    |  |     |   |

| IIH(SHDN) | Shutdown input current high     |                                           | V <sub>I(SHDN)</sub> = 5 V |     | 200                                           | 400             | μA   |  |     |   |

| IIL(SHDN) | Shutdown input current low      | $V_{CC} = \pm 5 V \text{ or } \pm 15 V,$  | $V_{I(SHDN)} = 0.5 V$      |     | 5                                             | 15              | μΑ   |  |     |   |

SLOS214 - OCTOBER 1998

|             | PARAMETER                       | TEST COND                                       | ITIONS <sup>†</sup>         | MIN   | TYP   | MAX   | UNIT  |

|-------------|---------------------------------|-------------------------------------------------|-----------------------------|-------|-------|-------|-------|

| Vcc         | Supply voltage range            | Split supply                                    |                             | ±4.5‡ |       | ±16.5 | V     |

|             |                                 | D 010                                           | $V_{CC} = \pm 5 V$          | ±3.4  | ±3.8  |       |       |

| N/          |                                 | $R_L = 2 k\Omega$                               | V <sub>CC</sub> = ±15 V     | ±13   | ±13.5 |       | v     |

| VOM         | Maximum output voltage swing    | $R_{I} = 1 k\Omega$                             | V <sub>CC</sub> = ±5 V      | ±2.9  | ±3.3  |       | v     |

|             |                                 |                                                 | V <sub>CC</sub> = ±15 V     | ±12   | ±13.5 |       |       |

| VIO         | Input offect voltage            | V <sub>CC</sub> = ±5 V or ±15 V                 | $T_A = 25^{\circ}C$         |       | 3     | 8     | mV    |

| VIO         | Input offset voltage            | $vCC = \pm 3 \circ 01 \pm 13 \circ$             | T <sub>A</sub> = full range |       |       | 10    | IIIV  |

|             | Input offset voltage drift      |                                                 |                             |       | 10    |       | μV/°C |

| lip         | Input bias current              | $V_{CC} = \pm 5 \text{ V or } \pm 15 \text{ V}$ | $T_A = 25^{\circ}C$         |       | 3     | 6     | μA    |

| lΒ          | input bias current              |                                                 | $T_A = $ full range         |       |       | 8     | μΛ    |

| lio         | Input offset current            | $V_{CC} = \pm 5 \text{ V or } \pm 15 \text{ V}$ | $T_A = 25^{\circ}C$         |       | 30    | 175   | nA    |

| νiO         | input onset current             | VCC = 72 V 01 712 V                             | $T_A = full range$          |       |       | 400   | 114   |

|             | Input offset current drift      |                                                 |                             |       | 0.3   |       | nA/°C |

|             | Common-mode rejection ratio     | $V_{CC} = \pm 5 V,$                             | $T_A = 25^{\circ}C$         | 75    | 85    |       |       |

| CMMR        |                                 | $V_{IC} = \pm 2.5 V$                            | T <sub>A</sub> = full range | 70    |       |       | dB    |

| Oliviivii ( |                                 | $V_{CC} = \pm 15 V,$                            | $T_A = 25^{\circ}C$         | 85    | 95    |       | üD    |

|             |                                 | V <sub>IC</sub> = ±10 V                         | T <sub>A</sub> = full range | 80    |       |       |       |

| ю           | Output current                  | R <sub>L</sub> = 150 Ω                          | $V_{CC} = \pm 5 V$          | 13    | 23    |       | mA    |

| 0           |                                 | INC = 100 32                                    | $V_{CC} = \pm 15 V$         | 15    | 25    |       | IIIA  |

| los         | Short-circuit output current    | V <sub>CC</sub> = ±15 V,                        | RL = 5 Ω                    |       | 55    |       | mA    |

|             | Power supply rejection ratio    | $V_{CC} = \pm 5 \text{ V or } \pm 15 \text{ V}$ | $T_A = 25^{\circ}C$         | 78    | 90    |       | dB    |

|             |                                 |                                                 | $T_A = $ full range         | 73    |       |       | üD    |

| RI          | Input resistance                | Gain = 20 dB                                    |                             |       | 0.27  |       | kΩ    |

| М           | inputresistance                 | Gain = −22 dB                                   | Gain = -22 dB               |       | 3     |       | N22   |

| Cl          | Input capacitance               |                                                 |                             |       | 1.5   |       | pF    |

| RO          | dc output resistance            |                                                 |                             |       | 0.05  |       | Ω     |

|             |                                 | V <sub>CC</sub> = ±5 V                          | $T_A = 25^{\circ}C$         |       | 8     | 11    |       |

|             | Quiescent current (per channel) |                                                 | $T_A = $ full range         |       |       | 12    | mA    |

| ICC         | Quescent current (per channel)  | V <sub>CC</sub> = ±15 V                         | $T_A = 25^{\circ}C$         |       | 9     | 12    |       |

|             |                                 |                                                 | T <sub>A</sub> = full range |       |       | 13    | 1     |

## PGA electrical characteristics, $T_A = 25^{\circ}C$ , Gain = 2 dB, $R_L = 1 \text{ k}\Omega$ , (unless otherwise noted)

<sup>†</sup> Full range for the THS7002C is 0°C to 70°C. Full range for the THS7002I is –40°C to 85°C.

<sup>‡</sup>PGA minimum supply voltage **must be** less than or equal to preamp supply voltage.

SLOS214 - OCTOBER 1998

#### output limiting characteristics

| PARAMETER                | 1                                           | EST CONDITIONS                                                           | 5†                          | MIN TYP  | MAX  | UNIT |

|--------------------------|---------------------------------------------|--------------------------------------------------------------------------|-----------------------------|----------|------|------|

|                          | $V_{CC} = \pm 15 V,$                        |                                                                          |                             | ±150     | ±200 |      |

| Clamp accuracy           | $V_I = \pm 10 V$ ,<br>Gain = 2 dB           | VL = -10 V,                                                              | T <sub>A</sub> = full range |          | ±225 |      |

|                          | $V_{CC} = \pm 5 V,$                         |                                                                          | T <sub>A</sub> = 25°C       | ±100     | ±200 | mV   |

|                          | $V_I = \pm 2.5 V$ ,<br>Gain = 2 dB          | VL = -2 V,                                                               | T <sub>A</sub> = full range |          | ±225 |      |

|                          | $V_{CC} = \pm 15 V,$<br>$V_{I} = \pm 10 V,$ | VH = 10 V,<br>$t_{f}$ and $t_{f} = 1 ns$                                 | V <sub>L</sub> = 10 V,      | 10%      |      |      |

| Clamp overshoot          | $V_{CC} = \pm 5 V,$<br>$V_{I} = \pm 2.5 V,$ | VH = 2 V,<br>t <sub>r</sub> and t <sub>f</sub> = 1 ns                    | V <sub>L</sub> = 2 V,       | 7.5%     |      |      |

|                          | $V_{CC} = \pm 15 V,$<br>$V_{I} = \pm 10 V$  | VH = 10 V,                                                               | V <sub>L</sub> = 10 V,      | 5        |      |      |

| Overdrive recovery time  | $V_{CC} = \pm 5 V,$<br>$V_{I} = \pm 2.5 V$  | VH = 2 V,                                                                | V <sub>L</sub> = 2 V,       | 4        |      | nS   |

| Negotivo elementore      | V <sub>CC</sub> = ±5 V                      |                                                                          |                             | –5 to 2  |      | v    |

| Negative clamp range     | V <sub>CC</sub> = ±15 V                     |                                                                          |                             | –15 to 2 |      | V    |

|                          | V <sub>CC</sub> = ±5 V                      | $V_{CC} = \pm 5 V$                                                       |                             |          |      | v    |

| Positive clamp range     | V <sub>CC</sub> = ±15 V                     | $V_{CC} = \pm 15 V$                                                      |                             |          |      | V    |

| Clamp input bias current |                                             | $V_{CC} = \pm 5 \text{ V}, \pm 15 \text{ V}$ $T_A = \text{full results}$ |                             | 50       |      |      |

|                          | $VCC = \pm 5 V, \pm 13$                     |                                                                          |                             | 75       | μA   |      |

<sup>†</sup> Full range for the THS7002C is 0°C to 70°C. Full range for the THS7002I is –40°C to 85°C.

# PGA electrical characteristics, $T_A$ = 25°C, Gain = 2 dB, $R_L$ = 1 k $\Omega$ , (unless otherwise noted) (continued)

### digital gain characteristics

| PARAMETER       |                          | TEST CONDITIONS         | MIN | TYP | MAX | UNIT |

|-----------------|--------------------------|-------------------------|-----|-----|-----|------|

| VIH             | High-level input voltage | Relative to GND         | 2   |     |     | V    |

| VIL             | Low-level input voltage  | Relative to GND         |     |     | 0.8 | V    |

| Iн              | High-level input current | $V_{IH} = 5 V$          |     | 2   | 20  | μΑ   |

| Ι <sub>ΙL</sub> | Low-level input current  | V <sub>IL</sub> = 0.5 V |     | 1   | 10  | μΑ   |

SLOS214 - OCTOBER 1998

|                | PARAMETER                         | TEST CONDI                                               | TIONS <sup>†</sup>          | MIN | TYP   | MAX | UNIT    |  |

|----------------|-----------------------------------|----------------------------------------------------------|-----------------------------|-----|-------|-----|---------|--|

| SR             | Slow rate (and Nate 4)            | $V_{CC} = \pm 5 V,$                                      | V <sub>O</sub> = ±2 V       |     | 175   |     | 1//110  |  |

| SK             | Slew rate (see Note 4)            | $V_{CC} = \pm 15 V,$                                     | V <sub>O</sub> = ±10 V      |     | 200   |     | V/µs    |  |

|                | Cottling time to 0.10/            | 0 V to 10 V Step                                         | V <sub>CC</sub> = ±15 V     |     | 60    |     | ns      |  |

| t <sub>S</sub> | Settling time to 0.1%             | $V_I = 0 V$ to 10 V Step                                 | $V_{CC} = \pm 5 V$          |     | 50    |     |         |  |

| t <sub>S</sub> | Settling time to 0.01%            | 0 V to 10 V Step                                         | $V_{CC} = \pm 15 V$         |     | 85    |     | ns      |  |

| THD            | Total harmonic distortion         | $V_{CC} = \pm 15 V,$<br>$f_{C} = 1 MHz$                  | V <sub>O(PP)</sub> = 2 V,   |     | -80   |     | dBc     |  |

|                |                                   | Gain = 20 dB                                             | $V_{CC} = \pm 15 V$         |     | 60    |     |         |  |

|                |                                   | Gain = 20 dB                                             | $V_{CC} = \pm 5 V$          |     | 50    |     |         |  |

| BW             | Small-signal bandwidth (-3 dB)    | Gain = 2 dB                                              | $V_{CC} = \pm 15 V$         |     | 65    |     | MHz     |  |

|                | Sinair-signal bandwidth (-5 db)   | Gain = 2 dB                                              | $V_{CC} = \pm 5 V$          |     | 55    |     | MHZ     |  |

|                |                                   | Gain = −22 dB                                            | $V_{CC} = \pm 15 V$         |     | 70    |     | 1       |  |

|                |                                   |                                                          | $V_{CC} = \pm 5 V$          | 60  |       |     |         |  |

|                | Bandwidth for 0.1 dB flatness     | Gain = 2 dB                                              | $V_{CC} = \pm 15 V$         |     | 15    |     | MHz     |  |

|                |                                   |                                                          | $V_{CC} = \pm 5 V$          |     | 12    |     | 1011 12 |  |

|                | Full power bandwidth (see Note 5) | $V_O = 5 V_O(PP),$                                       | $V_{CC} = \pm 5 V$          |     | 11    |     | MHz     |  |

|                |                                   | $V_{O} = 20 V_{O(PP)},$                                  | V <sub>CC</sub> = ±15 V     |     | 3.2   |     | 101112  |  |

| AD             | Differential gain error           | G = 8 dB, ±100 IRE,                                      | $V_{CC} = \pm 5 V$          |     | 0.02% |     |         |  |

| ~D             | Differential gain error           | NTSC                                                     | $V_{CC} = \pm 15 V$         |     | 0.06% |     |         |  |

| ۹D             | Differential phase error          | G = 8 dB, ±100 IRE,                                      | $V_{CC} = \pm 15 V$         |     | 0.20° |     |         |  |

| ΨD             | Differential phase error          | NTSC                                                     | $V_{CC} = \pm 5 V$          |     | 0.10° |     |         |  |

|                | Open loop gain (see Note 6)       | Gain = $-22 \text{ dB}$ to 20 dB,<br>All 8 steps,        | $T_A = 25^{\circ}C$         | -4% | 0%    | 4%  |         |  |

|                | Open toop gain (see Note 0)       | $V_{CC} = \pm 5 \text{ V or } \pm 15 \text{ V}$          | T <sub>A</sub> = full range | -6% |       | 6%  |         |  |

|                | de ser lisserit :                 | $V_{I} = -2 \text{ to } 2 \text{ V}$                     | V <sub>CC</sub> = ±5 V      |     | 0.05% |     |         |  |

|                | dc nonlinearity                   | V <sub>I</sub> = -8 to 8 V                               | V <sub>CC</sub> = ±15 V     |     | 0.05% |     |         |  |

| Vn             | Input noise voltage               | $V_{CC} = \pm 5 V \text{ or } \pm 15 V,$<br>Gain = 20 dB | f = 10 kHz,                 |     | 10    |     | nV/√H   |  |

| In             | Input noise current               | $V_{CC} = \pm 5 V \text{ or } \pm 15 V,$<br>Gain = 20 dB | f = 10 kHz,                 |     | 1.5   |     | pA/√H   |  |

## PGA operating characteristics, $T_A = 25^{\circ}C$ , Gain = 2 dB, $R_L = 1 \text{ k}\Omega$ , (unless otherwise noted)

<sup>†</sup> Full range for the THS7002C is 0°C to 70°C. Full range for the THS7002I is –40°C to 85°C.

NOTES: 4. Slew rate is measured from an output level range of 25% to 75%.

5. Full power bandwidth = slew rate/ $2\pi$  V<sub>PEAK</sub>

6. Specified as -100 × (output voltage - (input voltage × gain))/(input voltage × gain)

#### shutdown characteristics

|                  | PARAMETER                 | TEST CONDITIONS | MIN | TYP MAX | UNIT |

|------------------|---------------------------|-----------------|-----|---------|------|

| t <sub>dis</sub> | Disable time (see Note 7) |                 |     | 100     | ns   |

| ten              | Enable time (see Note 7)  |                 |     | 50      | ns   |

|                  |                           |                 |     |         |      |

NOTE 7: Disable time and enable time are defined as the interval between application of the logic signal to SHDN and the point at which the supply current has reached half its final value.

#### digital gain characteristics

|    | PARAMETER                      | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|----|--------------------------------|-----------------|-----|-----|-----|------|

| td | Gain change delay (see Note 8) |                 |     | 1   |     | μs   |

NOTE 8: Gain change delay is the time needed to reach 90% of its final gain value.

SLOS214 - OCTOBER 1998

## **APPLICATION INFORMATION**

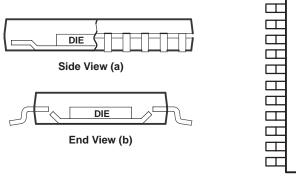

#### thermal information

The THS7002 is supplied in a thermally-enhanced PWP package, which is a member of the PowerPAD family of packages. This package is constructed using a downset leadframe upon which the die is mounted [see Figure 3(a) and Figure 3(b)]. This arrangement exposes the lead frame as a thermal pad on the underside of the package [see Figure 3(c)]. Because this pad has direct contact with the die, excellent thermal performance can be achieved by providing a good thermal path away from the pad.

The PowerPAD package allows for both assembly and thermal management in one manufacturing operation. During the surface-mount solder operation (when the leads are being soldered), the thermal pad can also be soldered to a copper area underneath the package. Through the use of thermal paths within this copper area, heat can be conducted away from the package into either a ground plane or other heat dissipating device.

The PowerPAD package represents a breakthrough in combining the small area requirement and ease of assembly of surface mount with the heretofore awkward mechanical methods of heatsinking.

Bottom View (c)

NOTE A: The thermal pad is electrically isolated from all terminals in the package.

Figure 3. Views of Thermally Enhanced PWP Package

SLOS214 - OCTOBER 1998

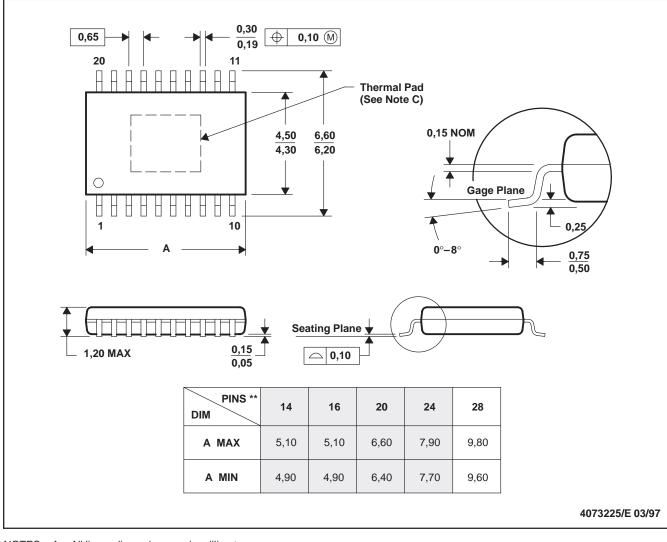

#### MECHANICAL DATA

PWP (R-PDSO-G\*\*)

20-PIN SHOWN

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. The package thermal performance may be enhanced by bonding the thermal pad to an external thermal plane. This solderable pad is electrically and thermally connected to the backside of the die and possibly selected leads. The maximum pad size on the printed circuit board should be equal to the package body size 2,0 mm.

PowerPAD is a trademark of Texas Instruments Incorporated.

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 1998, Texas Instruments Incorporated