SLVS127 - AUGUST 1995

- Pin-for-Pin Compatible With MAX734

- Programming Voltage for Flash Memory

- 2.7-V to 11-V Input Operating Range

- Output Current of 120 mA or Greater From 3.75-V or Higher Input

- 3-μA Maximum Supply Current in Shutdown

- Only 5 External Components Required

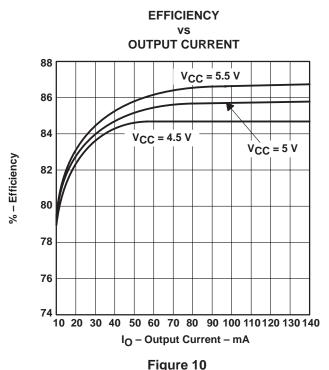

- High Efficiency . . . 85% Typical (5-V Input, 120-mA Output)

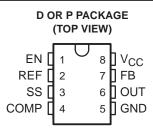

- 8-Pin SOIC and DIP Packages

- -40°C to 85°C Free-Air Operating Temperature Range

### description

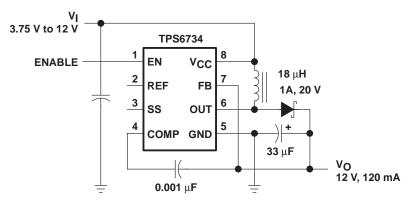

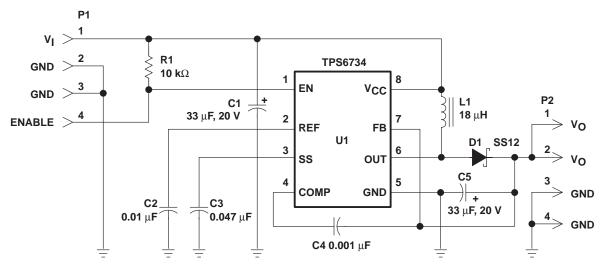

The TPS6734 is a fixed 12-V output boost converter capable of delivering 120 mA from inputs as low as 3.75 V. The device is pin-for-pin compatible with the MAX734 regulator and offers the following advantages: lower supply current, wider operating input-voltage range, and higher output currents. As shown in Figure 1, the only external components required are: an inductor, a Schottky rectifier, an output filter capacitor, an input filter capacitor for loop compensation. The entire converter occupies less than 0.7 in<sup>2</sup> of PCB space when implemented with surface-mount components. An enable input is provided to shut the converter down and reduce the supply current to 3  $\mu$ A when 12 V is not needed.

The TPS6734 is a 170-kHz current-mode PWM (pulse-width modulation) controller with an n-channel MOSFET power switch. Gate drive for the switch is derived from the 12-V output after start-up to minimize the die area needed to realize the  $0.7-\Omega$  MOSFET and improve efficiency at input voltages below 5 V. Soft start is accomplished with the addition of one small capacitor. A 1.22-V reference (pin 2) is brought out for external use.

High efficiency at low supply voltages and low supply current in shutdown make the TPS6734 particularly attractive for flash memory programming supplies, PCMCIA cards, and operational amplifiers in battery-powered equipment. The TPS6734 is available in 8-pin DIP and SOIC packages and operates over a free-air temperature range of  $-40^{\circ}$ C to  $85^{\circ}$ C.

Figure 1. Typical Operating Circuit

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright © 1995, Texas Instruments Incorporated

SLVS127 - AUGUST 1995

| AVAILABLE OPTIONS                 |                                      |  |  |  |  |  |

|-----------------------------------|--------------------------------------|--|--|--|--|--|

| PACKAGE                           |                                      |  |  |  |  |  |

| TA                                | SMALL OUTLINE PLASTIC DII<br>(D) (P) |  |  |  |  |  |

|                                   |                                      |  |  |  |  |  |

| -40°C to 85°C TPS6734ID TPS6734IP |                                      |  |  |  |  |  |

|                                   |                                      |  |  |  |  |  |

The D package is available taped and reeled. Add the suffix R to the device type (e.g., TPS6734IDR).

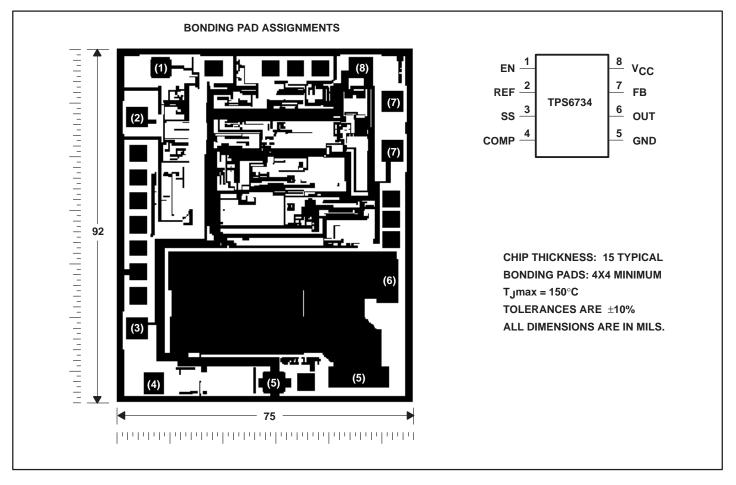

### **TPS6734** chip information

Thermal compression or ultrasonic bonding can be used on the doped-aluminum bonding pad. Chips can be mounted with conductive epoxy or a gold-silicon preform. Contact factory for die sales.

### **Terminal Functions**

| TERMI | NAL | DESCRIPTION                                                                                                             |  |  |  |

|-------|-----|-------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME  | NO. | DESCRIPTION                                                                                                             |  |  |  |

| EN    | 1   | inable. EN $\ge$ 2 V turns on the TPS6734. EN $\le$ 0.4 V turns it off and reduces the supply current to 3 $\mu$ A max. |  |  |  |

| REF   | 2   | .22-V reference voltage output. REF can source 100 μA for external loads.                                               |  |  |  |

| SS    | 3   | Soft Start. A capacitor between SS and GND brings the output voltage up slowly at power-up.                             |  |  |  |

| COMP  | 4   | Compensation connection. A 0.001-µF capacitor between COMP and FB stabilizes the feedback loop.                         |  |  |  |

| GND   | 5   | Ground                                                                                                                  |  |  |  |

| OUT   | 6   | N-channel MOSFET drain connection                                                                                       |  |  |  |

| FB    | 7   | Feedback voltage. FB is connected to the converter output for the feedback loop.                                        |  |  |  |

| VCC   | 8   | Supply voltage input                                                                                                    |  |  |  |

SLVS127 – AUGUST 1995

### detailed description

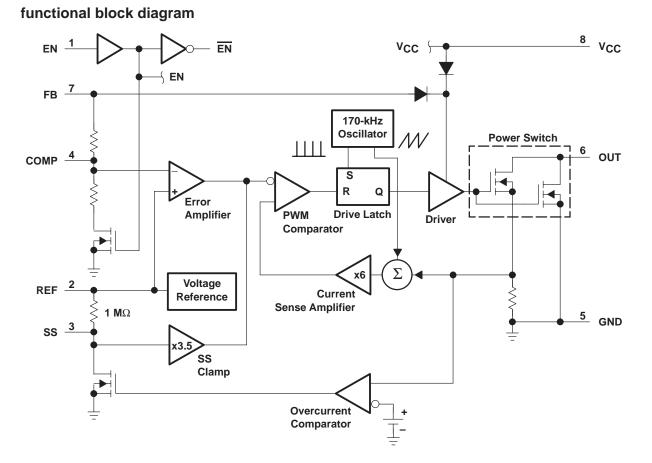

The following descriptions refer to the functional block diagram.

#### reference

The internal 1.22-V reference is brought out on REF and can source 100  $\mu$ A maximum to external loads. A 0.01- $\mu$ F to 0.1- $\mu$ F decoupling capacitor connected between REF and GND is recommended to minimize noise pickup.

#### oscillator and ramp generator

The oscillator circuit provides a 170-kHz clock, to set the converter operating frequency, and a timing ramp for slope compensation. The clock waveform is a pulse, a few hundred nanoseconds in duration, that is used to limit the maximum power-switch duty cycle to 95%. The timing ramp is summed with the current-sense signal at the input to the current-sense amplifier.

#### driver latch

The latch, which consists of a set/reset flip-flop and associated logic, is used to control the state of the power switch by turning the driver on and off. A high output from the latch turns the switch on; a low output from the latch turns it off. In normal operation, the flip-flop is set high during the clock pulse, but gating keeps the latch output low until the clock pulse is over. The latch is reset when the PWM comparator output goes high.

#### current-sense amplifier

The current-sense amplifier has a fixed gain of 6. It amplifies the slope-compensated current-sense voltage (a summation of the voltage on the current-sense resistor and the oscillator ramp) and feeds it to the PWM comparator.

#### error amplifier

The error amplifier is a high-gain differential amplifier used to regulate the converter output voltage. The amplifier generates an error signal, which is fed to the PWM comparator. The error signal is generated when a sample of the output voltage is compared to the internal reference and the difference is amplified. The output sample is obtained from a resistive divider connected between FB and GND. FB is externally connected to the converter output, and the divider output is connected to both the error amplifier input and COMP. A 0.001- $\mu$ F capacitor connected between FB and COMP stabilizes the voltage control loop.

### **PWM comparator**

The PWM comparator resets the drive latch and turns off the power switch whenever the slope-compensated current-sense signal from the current-sense amplifier exceeds the error signal.

#### power switch

The power switch is a  $0.7 \Omega$  n-channel MOSFET with current-sensing. The drain is connected to OUT and the current sense is connected to a resistor. The voltage across the resistor is proportional to the current in the power switch and is tied to the overcurrent comparator and the current-sense amplifier. In normal operation, the power switch is turned on at the start of each clock cycle and turned off when the PWM comparator resets the drive latch.

#### SS clamp

The SS (soft-start) clamp circuit limits the signal level on error-amplifier output during start-up. The voltage on SS is amplified and used to momentarily override the error-amplifier output until it rises above that output, at which point the error-amplifier takes over. This prevents the input to the PWM comparator from exceeding its common-mode range (the error-amplifier output too high to be reached by the current ramp) by limiting the maximum voltage on the error-amplifier output during start-up.

#### soft start

Soft start causes the output voltage to increase to the regulation point at a controlled rate of rise. The voltage on the charging soft-start capacitor gradually raises the clamp on the error-amplifier output voltage, limiting surge currents at power-up by increasing the current-limit threshold on a cycle-by-cycle basis. Even if SS has no capacitor installed, some distributed capacitance will always be present. A soft-start cycle is initiated when either the enable signal (EN) is switched high, or an overcurrent fault condition triggers the discharge of the soft-start capacitor.

#### overcurrent comparator

The overcurrent comparator monitors the current in the power switch. The comparator trips and initiates a soft-start cycle if the power-switch current exceeds 1.5-A peak. On each clock cycle, the power switch turns on and attempts to deliver current until the overcurrent limits are exceeded.

#### enable (EN)

A logic low on EN puts the TPS6734 in shutdown mode. In shutdown, the output power switch, voltage reference, and other functions are shut off, the supply current is reduced to 3 µA maximum, and the soft-start capacitor is discharged through a 1-M $\Omega$  resistance. The output voltage falls to a diode drop below the input voltage because of the current path from input to output through the inductor and diode.

#### DISSIPATION RATING TABLE

|         |                                       | 2.000                                          |                                       |                                       |

|---------|---------------------------------------|------------------------------------------------|---------------------------------------|---------------------------------------|

| PACKAGE | T <sub>A</sub> ≤ 25°C<br>POWER RATING | DERATING FACTOR<br>ABOVE T <sub>A</sub> = 25°C | T <sub>A</sub> = 70°C<br>POWER RATING | T <sub>A</sub> = 85°C<br>POWER RATING |

| D       | 725 mW                                | 5.8 mW/°C                                      | 464 mW                                | 377 mW                                |

| Р       | 1175 mW                               | 9.4 mW/°C                                      | 752 mW                                | 611 mW                                |

#### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)<sup>†</sup>

| Pin voltages: V <sub>CC</sub> , OUT (see Note 1)<br>SS, COMP, EN (see Note 1) |                              |

|-------------------------------------------------------------------------------|------------------------------|

| Peak switch current                                                           |                              |

| Reference current                                                             | 2.5 mA                       |

| O antinuo a successi di scienzi antina                                        |                              |

| Continuous power dissipation                                                  | See Dissipation Rating Table |

| Operating free-air temperature range, T <sub>A</sub>                          | –40°C to 85°C                |

|                                                                               | –40°C to 85°C                |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTE 1: All voltage values are with respect to network terminal ground.

SLVS127 - AUGUST 1995

### recommended operating conditions

|                                                | MIN | NOM   | MAX | UNIT |

|------------------------------------------------|-----|-------|-----|------|

| Supply voltage                                 | 2.7 | 5     | 12  | V    |

| Compensation capacitor                         |     | 0.001 |     | μF   |

| Output current at REF                          | 0   |       | 100 | μΑ   |

| Reference capacitor                            |     | 0.01  |     | μF   |

| Operating free-air temperature, T <sub>A</sub> | -40 |       | 85  | °C   |

electrical characteristics over recommended operating free-air temperature range,  $V_{CC} = 5 V$ ,  $I_{O(LOAD)} = 0 mA$ , EN = 5 V, typical values are at  $T_A = 25^{\circ}C$  (unless otherwise noted) (refer to circuit shown in Figure 13)

| PARAMETER                     |              | TEST CONDITIONS                       | MIN | TYP  | MAX | UNITS  |

|-------------------------------|--------------|---------------------------------------|-----|------|-----|--------|

|                               | Operating    | Entire circuit                        |     | 1.2  | 2.5 | mA     |

| Supply current                | Standby      | EN = 0.4 V, entire circuit            |     |      | 3   | μΑ     |

|                               | Standby      | $EN = 0.4 V$ , into $V_{CC}$          |     |      | 3   | μA     |

| High-level input threshold ve | oltage at EN |                                       | 2   |      |     | V      |

| Low-level input threshold vo  | oltage at EN |                                       |     |      | 0.4 | V      |

| Shutdown input leakage cui    | rrent at EN  |                                       | -1  |      | 1   | μA     |

| On resistance at OUT          |              | Current at OUT = 500 mA               |     | 0.7  |     | Ω      |

| Leakage current at OUT        |              | V <sub>DS</sub> = 12 V                | 1   |      | μΑ  |        |

| Reference voltage             |              |                                       |     | 1.22 |     | V      |

| Reference drift               |              | $T_A = -40^{\circ}C$ to $85^{\circ}C$ |     | 6.7  |     | ppm/°C |

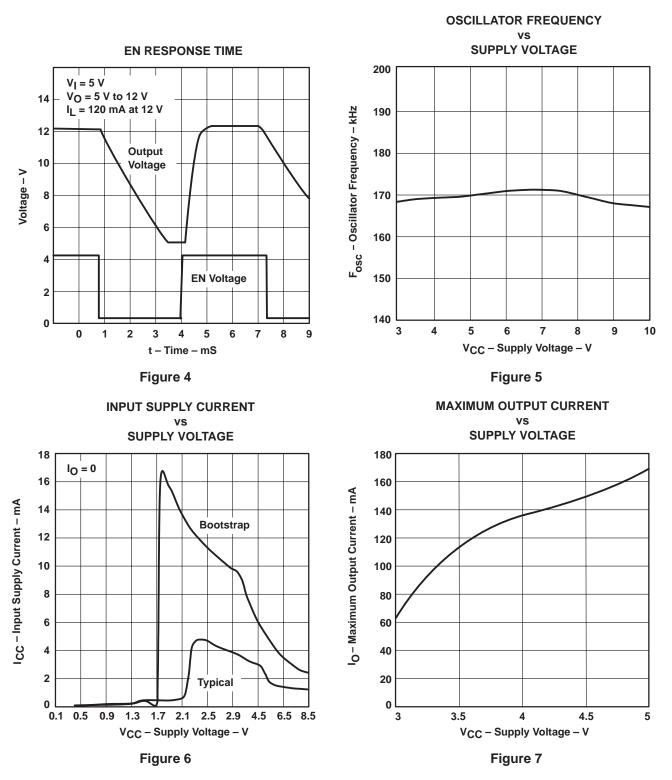

| Oscillator frequency          |              |                                       |     | 170  |     | kHz    |

| Compensation pin impedan      | се           |                                       |     | 7500 |     | Ω      |

performance characteristics over recommended operating free-air temperature range, typical circuit connected as shown in Figure 13, typical values are at  $T_A = 25^{\circ}C$  (unless otherwise noted)

| PARAMETER       | TEST CONDITIONS                               |                                      |       | TYP   | MAX  | UNITS |

|-----------------|-----------------------------------------------|--------------------------------------|-------|-------|------|-------|

| Output voltage  | V <sub>CC</sub> = 4.75 V,                     | 0 mA < I <sub>O(LOAD)</sub> < 120 mA | 11.64 | 12.12 | 12.6 | V     |

| Lood ourrept    | V <sub>CC</sub> = 3.75 V                      | V <sub>CC</sub> = 3.75 V             |       | 150   |      | mA    |

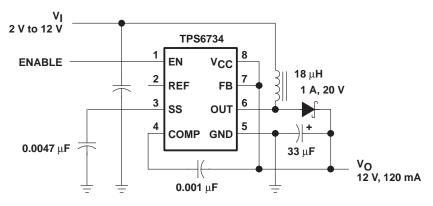

| Load current    | V <sub>CC</sub> = 3.0 V,                      | Figure 11                            | 150   |       | ША   |       |

| Line regulation | $V_{CC}$ = 5 V to 12 V,                       | I <sub>O(LOAD)</sub> = 50 mA         | 0.20% |       |      |       |

| Load regulation | I <sub>O(LOAD)</sub> = 0 mA to 120 mA 0.0042% |                                      |       |       |      |       |

| Efficiency      | $V_{CC} = 5 V,$                               | I <sub>O(LOAD)</sub> = 120 mA        | 86%   |       |      |       |

### **TYPICAL CHARACTERISTICS**

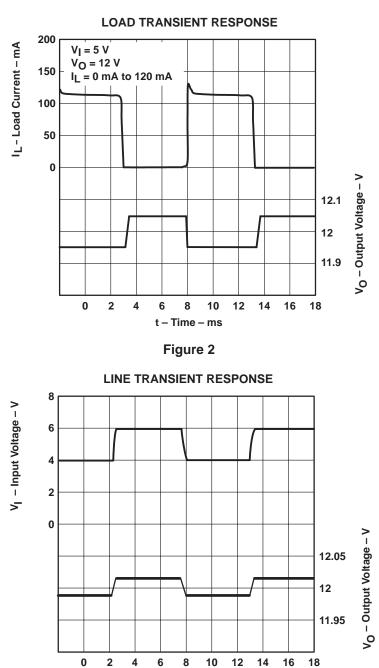

Figure 3

t – Time – ms

SLVS127 - AUGUST 1995

## **APPLICATION INFORMATION**

The TPS6734 operates in a boost circuit as shown in Figures 1 and 11. Figure 1 shows the typical application circuit, which generates 12 V from a nominal 5-V source. The circuit is ideal for processor interface for energy management, because EN can be controlled by logic signals to place the 12-V source into the shutdown mode  $(3-\mu A \text{ current drain})$  when 12 V is not needed. An example of such an application is a flash memory device that requires 12 V for the erase cycle.

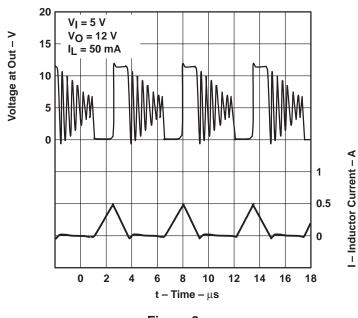

#### discontinuous mode

The circuit shown in Figure 1 operates in discontinuous mode over most of the range of input voltage and output current. In discontinuous mode, current through the inductor begins at zero, rises to a peak value, then ramps down to zero each cycle as shown by the voltage and current waveforms in Figure 8. The ringing in the voltage waveform on OUT results from a resonance between the inductor and the power switch capacitance and is normal for discontinuous operation.

DISCONTINUOUS MODE

SLVS127 – AUGUST 1995

## **APPLICATION INFORMATION**

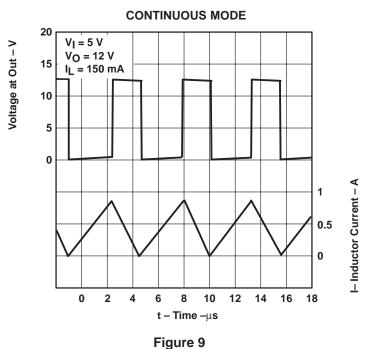

#### continuous mode

When the converter is delivering heavy loads from low voltage sources, it operates in continuous mode. As shown in Figure 9, the inductor current does not drop to zero and the ringing is gone from the OUT voltage waveform.

#### pulse-skipping mode

At very light load currents, the TPS6734 cannot generate drive pulses sufficiently narrow to maintain regulation and operate at 170 kHz. Under these circumstances, the converter operates in a pulse-skipping mode, in which cycles are skipped. In pulse-skipping mode, the waveforms are irregular and the output ripple contains a low-frequency component that may exceed 50 mV peak-to-peak.

## **APPLICATION INFORMATION**

#### efficiency

Typical efficiency for the converter circuit shown in Figure 13 is plotted in Figure 10. The efficiency falls off rapidly at very light currents because the supply current is a significant percentage of the load.

#### inductor selection

Inductance value is directly proportional to the input voltage and inversely proportional to the output power. The 18  $\mu$ H shown in the typical circuit is the proper value for operation from 5-V sources up to 2-W loads. A lower inductance value should be used when operating from 3-V sources. Operation from 7 V and higher sources may require inductance values greater than 18  $\mu$ H. The inductor's saturation current rating should be greater than three times the dc load current for 5-V inputs and five times the dc load for 3-V inputs.

#### output filter capacitor selection

The output filter capacitor should be selected for minimum ESR (equivalent series resistance). Capacitor ESR  $\times \Delta I_L$  (change in inductor current) determines the amplitude of the high-frequency ripple on the output voltage. The ESR of the capacitor should be less than 0.25  $\Omega$  to keep the output ripple less than 50 mV peak-to-peak over the entire current range (using 18-µH inductor).

#### diode

A Schottky diode or a high-speed silicon rectifier should be used. The continuous current rating of the diode should be at least 300 mA for full load (120 mA) operation.

SLVS127 - AUGUST 1995

## **APPLICATION INFORMATION**

#### soft-start capacitor

Soft-start timing is controlled by the value of the SS capacitor. Table 1 lists soft-start time intervals for selected capacitor values and circuit conditions. If the circuit starts up with no load (e.g. in flash-memory programming supplies), no soft start is needed. Omitting the soft-start capacitor provides a minimum output-voltage rise time from the shutdown state, improving the output start-up time.

| SUPPLY      | SOFT-START TIME <sup>†</sup> (ms) VERSUS CAPACITANCE ( $\mu$ F) |       |     |      |     |  |  |

|-------------|-----------------------------------------------------------------|-------|-----|------|-----|--|--|

| VOLTAGE (V) | NO. CAP                                                         | 0.047 | 0.1 | 0.47 | 1.0 |  |  |

| 5           | 0.70                                                            | 22    | 42  | 220  | 400 |  |  |

| 7           | 0.46                                                            | 15    | 37  | 185  | 225 |  |  |

| 9           | 0.38                                                            | 10    | 17  | 88   | 155 |  |  |

| Table 1. | Typical | Soft-Start | Times |

|----------|---------|------------|-------|

|----------|---------|------------|-------|

<sup>†</sup>Soft-start times are ±35%

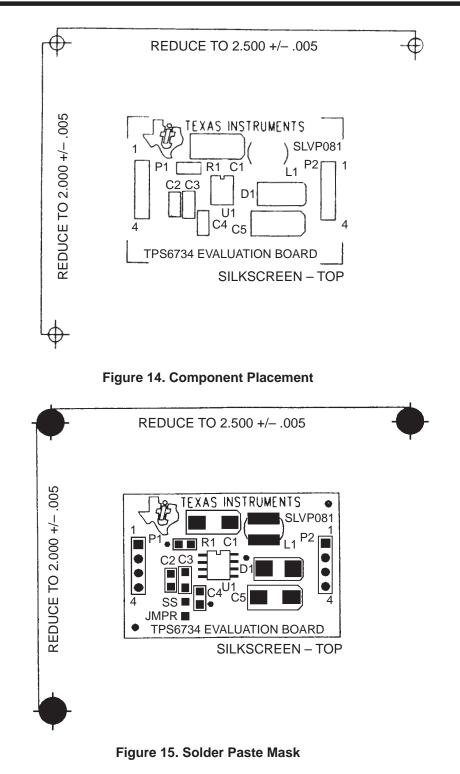

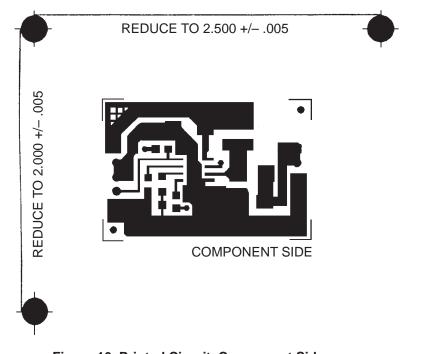

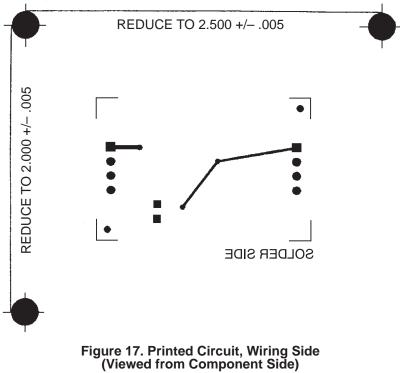

### printed-circuit layout

Printed-circuit-board (PCB) layout is critical to quiet operation. A ground plane is recommended. Special attention should be given to minimizing the lengths of the switching loops. The first loop is formed by OUT, the diode, the output capacitor, and GND, the length of which can be minimized by connecting the anode of the diode close to OUT. The output capacitor should be connected, directly between the diode cathode and GND with the shortest possible path. The second loop is formed by OUT, the inductor, the input capacitor, and GND. This loop is less critical than the first; however, the connection of OUT, the inductor and the anode of the diode must be minimized. Bypass capacitors should be located as close to the device as possible to prevent instability and noise pickup. If a large V<sub>CC</sub>-to-GND bypass capacitor cannot be placed adjacent to the IC pins, the pins should be bypassed directly with a small ceramic capacitor (e.g.,  $0.1 \ \mu$ F). The recommended layout shown in Figures 14 through 17 can provide guidance for PCB configuration (the ground plane beneath the TPS6734 and the short loops should be noted).

Plastic plug-in-type proto boards, or any construction scheme that allows long leads and the possibility of noise pickup, should not be used when assembling a breadboard or prototype application circuit implementing the TPS6734.

## APPLICATION INFORMATION

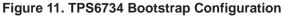

#### bootstrapped output circuit

For operation below 2.7 V, the TPS6734 may be connected in a bootstrap configuration as shown in Figure 11. The bootstrap configuration is less efficient (requires more supply current and suffers a loss in efficiency at voltages below 5 V; see Figure 12) and is not recommended except for very low voltage operating conditions. Because the output-driver stage, which benefits most from higher voltages, is diode-coupled to the output voltage (see Figure 2), the bootstrapped configuration provides no benefit except at very low voltages. In the shutdown mode (EN = low), no-load quiescent current is unchanged (3  $\mu$ A max) whether in the bootstrap or the typical configuration.

SLVS127 - AUGUST 1995

## **APPLICATION INFORMATION**

### TPS6734 converter design with recommended layout

The following schematic (Figure 13) and a required-components table are provided for a 12-V-output boost converter. The converter is capable of delivering 120 mA of output current over an input voltage range of 3.75 V to 12 V. Recommended layout and detailed artwork for a PCB are provided in Figures 14 through 17.

NOTE A: A jumper between pins P1-3 and P1-4 shuts off the TPS7634. Remove the jumper to resume normal operation.

#### Figure 13. Schematic for Printed Circuit Board (shown in Figures 14 through 17)

| QTY. | DESCRIPTION                              | REF DES | MANUFACTURER'S<br>PART NO. | MANUFACTURER        |

|------|------------------------------------------|---------|----------------------------|---------------------|

| 1    | IC, power supply, 12 V for flash memory  | U1      | TPS6734ID                  | Texas Instruments   |

| 1    | Diode, Schottky                          | D1      | SS12                       | General Instruments |

| 1    | Inductor, 18 μH, 150 mΩ, 1.23 A(DC)      | L1      | CD54180MC                  | Sumida              |

| 2    | Capacitor, 33 μF, 20 V, tantalum         | C1,5    | TAPSD336M020R0200          | AVX                 |

| 1    | Capacitor, 0.01 µF, 50 V, ceramic, 0805  | C2      |                            |                     |

| 1    | Capacitor, 0.047 µF, 50 V, ceramic, 1206 | C3      |                            |                     |

| 1    | Capacitor, 0.001 μF, 50 V, ceramic, 0805 | C4      |                            |                     |

| 2    | Connector, header, 4-pin                 | P1,2    |                            | Molex               |

| 1    | PCB, TPS6734                             |         |                            |                     |

#### **Required Components**

SLVS127 - AUGUST 1995

SLVS127 - AUGUST 1995

Figure 16. Printed Circuit, Component Side

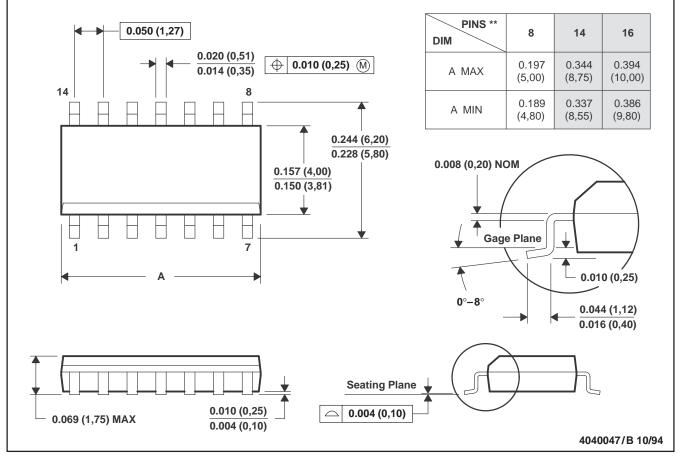

### MECHANICAL DATA

#### PLASTIC SMALL-OUTLINE PACKAGE

D (R-PDSO-G\*\*) 14 PIN SHOWN

NOTES: A. All linear dimensions are in inches (millimeters).

B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion not to exceed 0.006 (0,15).

- D. Four center pins are connected to die mount pad

- E. Falls within JEDEC MS-012

SLVS127 - AUGUST 1995

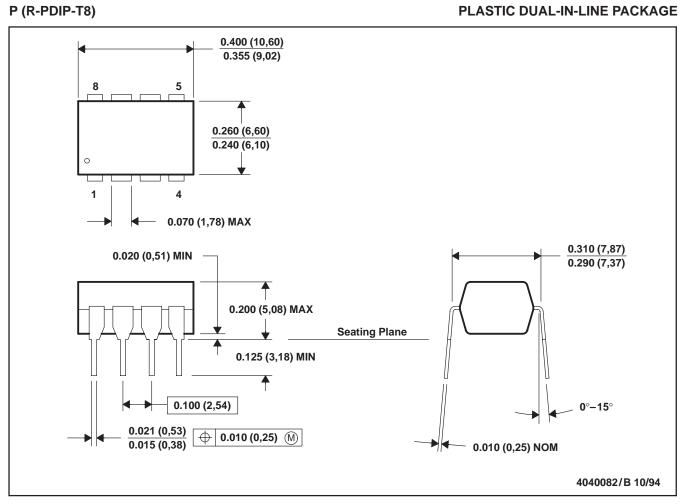

MECHANICAL DATA

- NOTES: A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- C. Falls within JEDEC MS-001

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 1998, Texas Instruments Incorporated