### TCM8030 Analog Baseband Processor User's Guide

SLWU002 JULY 1997

#### **IMPORTANT NOTICE**

Texas Instruments (TI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

TI warrants performance of its semiconductor products and related software to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Certain applications using semiconductor products may involve potential risks of death, personal injury, or severe property or environmental damage ("Critical Applications").

TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

Inclusion of TI products in such applications is understood to be fully at the risk of the customer. Use of TI products in such applications requires the written approval of an appropriate TI officer. Questions concerning potential risk applications should be directed to TI through a local SC sales office.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards should be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

Copyright © 1997, Texas Instruments Incorporated

### Preface

### **Read This First**

### About This Manual

This manual provides design information for the TCM8030 analog cellular telephone baseband processor. The manual is written for senior engineers, junior engineers, and support staff who design and develop analog cellular telephone baseband processors and applications.

You should be familiar with basic telecommunications concepts, analog theory, and cellular applications.

### How to Use This Manual

This document contains generic and specific information about the TCM8030 baseband processor.

**Chapter 1** Provides an overview of TCM8030 analog cellular telephone baseband processing

**Chapter 2** Describes the principles that apply during operation of the TCM8030 analog cellular telephone processor

**Chapter 3** Describes the receive processing procedure for the forward control channel (FOCC) and the forward voice channel (FVC)

**Chapter 4** Provides AMPS wideband data reverse channel transmission processing procedures for both the reverse control channel (RECC) and reverse voice channel (RVC)

**Chapter 5** Describes TCM8030 wideband data transmissions and provides wideband data transmission examples

**Chapter 6** Describes the process and methods used during reverse control channel arbitration

**Chapter 7** Defines automatic frequency control and its system cycle

**Chapter 8** Provides basic information regarding the programmable expansion input/output ports, special function port keys, and read and write register definitions

**Chapter 9** Describes the baseband processing techniques to apply necessary external circuitry to the TCM8030

### Notational Conventions

- An overscored word indicates a signal that is active low.

- Words that serve to emphasize an important element, notation, or imperative in a procedure are emphasized in **bold**.

#### **Related Documentation From Texas Instruments**

The following books describe the TCM8030 and related support tools. To obtain a copy of any of these TI documents, call the Texas Instruments Literature Response Center at (800) 477–8924. When ordering, please identify the book by its title and literature number.

- TCM8030 Analog Baseband Processor Data Manual (literature number SLW033A) describes the component and electrical specifications for the TCM8030.

- TPS72xx Micropower Low-Dropout (LDO) Voltage Regulators (literature number SLVS102E) describes the components and electrical specifications for the TPS72xx family.

### FCC Warning

This equipment is intended for use in a laboratory test environment only. It generates, uses, and can radiate radio frequency energy and has not been tested for compliance with the limits of computing devices pursuant to subpart J of part 15 of FCC rules, which are designed to provide reasonable protection against radio frequency interference. Operation of this equipment in other environments may cause interference with radio communications, in which case the user at his own expense will be required to take whatever measures may be required to correct this interference.

### Trademarks

SPI is a trademark of Motorola, Inc.

TI is a trademark of Texas Instruments Incorporated.

### If You Need Assistance . . .

| If you want to                                                                                             | Contact Texas Instruments at .                                       |                                                                                                                        |

|------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| Visit TI online                                                                                            | World Wide Web:                                                      | http://www.ti.com                                                                                                      |

| Receive general information                                                                                | World Wide Web:                                                      | http://www.ti.com/sc/docs/pic/home.htm                                                                                 |

| or assistance                                                                                              | North America, South America:                                        | (214) 644–5580                                                                                                         |

|                                                                                                            | Italian:<br>German:                                                  | 33–1–3070–1165<br>33–1–3070–1164<br>33–1–3070–1167                                                                     |

|                                                                                                            | Japan (Japanese or English)<br>Domestic toll-free:<br>International: | 0120–81–0026<br>81–3–3457–0972 or<br>81–3–3457–0976                                                                    |

|                                                                                                            | Korea (Korean or English):                                           | 82–2–551–2804                                                                                                          |

|                                                                                                            | Taiwan (Chinese or English):                                         | 886–2–3771450                                                                                                          |

| Ask questions about Digital<br>Signal Processor (DSP)<br>product operation or report<br>suspected problems | Fax Europe:<br>Email:                                                | +44-2-3422-3248                                                                                                        |

| Ask questions about<br>microcontroller product<br>operation or report<br>suspected<br>problems             | Fax:<br>Email:<br>World Wide Web:<br>BBS:                            |                                                                                                                        |

| Request tool updates                                                                                       | Software:<br>Software fax:<br>Hardware:                              | (214) 638–7742                                                                                                         |

| Order Texas Instruments documentation (see Note 1)                                                         | Literature Response Center:                                          | (800) 477–8924                                                                                                         |

| Make suggestions about or                                                                                  | Email:                                                               | comments@books.sc.ti.com                                                                                               |

| report errors in documentation (see Note 2)                                                                | Mail:                                                                | Texas Instruments Incorporated<br>Technical Publications Manager, MS 702<br>P.O. Box 1443<br>Houston, Texas 77251–1443 |

Read This First

v

### Contents

| 1 |         |          |                                               |

|---|---------|----------|-----------------------------------------------|

|   | 1.1     | -        | g Cellular Telephone Baseband Processing 1-2  |

|   | 1.2     |          | 030 Features 1-3                              |

|   |         | 1.2.1    | Data Processing Features 1-3                  |

|   |         | 1.2.2    | Audio Processing Features    1-3              |

|   | 1.3     | Power    | Modes 1-4                                     |

| 2 | Princ   | iples of | f Operation                                   |

|   | 2.1     | Princip  | bles of Operation Overview                    |

|   | 2.2     | Receiv   | ve Audio Path                                 |

|   | 2.3     | Transr   | nit Audio Path                                |

|   | 2.4     | Data F   | Processor                                     |

|   | 2.5     | Miscel   | laneous Circuits                              |

|   | 2.6     | Clocks   | 3 2-12                                        |

|   | 2.7     | Power    | Modes                                         |

|   |         | 2.7.1    | Total Power-Down Mode                         |

|   |         | 2.7.2    | Shutdown Mode                                 |

|   |         | 2.7.3    | Idle Mode                                     |

|   |         | 2.7.4    | Tone Mode                                     |

|   |         | 2.7.5    | Full Operation Mode, DTMF TX Off 2-20         |

|   |         | 2.7.6    | Full Operation Mode, DTMF TX On 2-20          |

|   |         | 2.7.7    | Independent Circuits                          |

|   | 2.8     | Circuit  | Definitions                                   |

|   |         | 2.8.1    | Transmit Path Audio Processing Functions 2-21 |

|   |         | 2.8.2    | Receive Path Audio Processing Functions 2-22  |

|   |         | 2.8.3    | Transmit Path Data Processing Functions 2-24  |

|   |         | 2.8.4    | Receive Path Data Processing Functions 2-25   |

|   |         | 2.8.5    | Transmit Path SAT Processing Functions 2-26   |

|   |         | 2.8.6    | Receive Path SAT Processing Functions 2-27    |

|   | 2.9     | Miscel   | laneous Functions                             |

| 3 | Rece    | ive Pro  | cessing                                       |

| - | 3.1     |          | /e Processing Overview                        |

|   | 3.2     |          | rd Control Channel (FOCC) Receive Processing  |

|   | <i></i> | 3.2.1    | Frame Description                             |

|   |         | 3.2.2    | Synchronization                               |

|   | 3.3  | 3.2.4       Nor         3.2.5       Les         3.2.6       Mor         3.2.7       Sin         Forward Vo       3.3.1         3.3.2       Fra         3.3.3       Maj         3.3.4       Nor         3.3.5       Les         3.3.6       Mor | jority Voting<br>rmal Operation<br>ss Than Five Word Syncs Missing<br>re Than Five Word Syncs Missing<br>gle Word Sync Detected<br>bice Channel (FVC) Receive Processing<br>ssage Stream<br>ime Timer<br>jority Voting<br>rmal Operation<br>ss Than Five Word Syncs Missed<br>re Than Five Word Syncs Missed<br>e Word Received | 3-6<br>3-6<br>3-7<br>3-8<br>3-8<br>3-8<br>3-9<br>3-9<br>3-10<br>3-11 |

|---|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| 4 | Wide | oand Data R                                                                                                                                                                                                                                    | Reverse Channel Transmission Processing                                                                                                                                                                                                                                                                                         | 4-1                                                                  |

|   | 4.1  | Wideband [                                                                                                                                                                                                                                     | Data Reverse Channel Transmission Processing Overview                                                                                                                                                                                                                                                                           | 4-2                                                                  |

|   | 4.2  |                                                                                                                                                                                                                                                | ontrol Channel Message Stream Description                                                                                                                                                                                                                                                                                       |                                                                      |

|   | 4.3  |                                                                                                                                                                                                                                                | tal Color Code (DCC)                                                                                                                                                                                                                                                                                                            |                                                                      |

|   | 4.4  |                                                                                                                                                                                                                                                | d Format                                                                                                                                                                                                                                                                                                                        |                                                                      |

|   | 4.5  |                                                                                                                                                                                                                                                | bice Channel Message Stream Description                                                                                                                                                                                                                                                                                         |                                                                      |

|   | 4.6  | RVC Word                                                                                                                                                                                                                                       | Format                                                                                                                                                                                                                                                                                                                          | 4-7                                                                  |

| 5 |      |                                                                                                                                                                                                                                                | ransmission                                                                                                                                                                                                                                                                                                                     |                                                                      |

|   | 5.1  |                                                                                                                                                                                                                                                | Transmission Overview                                                                                                                                                                                                                                                                                                           |                                                                      |

|   | 5.2  |                                                                                                                                                                                                                                                | ontrol Channel (RECC) Wideband Data Transmission                                                                                                                                                                                                                                                                                |                                                                      |

|   |      |                                                                                                                                                                                                                                                | up Procedures                                                                                                                                                                                                                                                                                                                   |                                                                      |

|   |      |                                                                                                                                                                                                                                                | ite to TX Buffer                                                                                                                                                                                                                                                                                                                |                                                                      |

|   |      |                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                 |                                                                      |

|   |      |                                                                                                                                                                                                                                                | gle-Word Transmission                                                                                                                                                                                                                                                                                                           |                                                                      |

|   |      |                                                                                                                                                                                                                                                | Itiple-Word Transmission                                                                                                                                                                                                                                                                                                        |                                                                      |

|   |      |                                                                                                                                                                                                                                                | gle-Word Transmission Example                                                                                                                                                                                                                                                                                                   |                                                                      |

|   | 5.3  |                                                                                                                                                                                                                                                | pice Channel (RVC) Wideband Data Transmission                                                                                                                                                                                                                                                                                   |                                                                      |

|   | 0.0  |                                                                                                                                                                                                                                                | up Procedures                                                                                                                                                                                                                                                                                                                   |                                                                      |

|   |      |                                                                                                                                                                                                                                                | ite to TX Buffer                                                                                                                                                                                                                                                                                                                |                                                                      |

|   |      |                                                                                                                                                                                                                                                | mmence Transmission                                                                                                                                                                                                                                                                                                             |                                                                      |

|   |      |                                                                                                                                                                                                                                                | gle-Word Transmission                                                                                                                                                                                                                                                                                                           |                                                                      |

|   |      |                                                                                                                                                                                                                                                | Itiple-Word Transmission                                                                                                                                                                                                                                                                                                        |                                                                      |

|   |      | 5.3.6 RV                                                                                                                                                                                                                                       | C Single-Word Transmission Example                                                                                                                                                                                                                                                                                              | 5-11                                                                 |

|   |      |                                                                                                                                                                                                                                                | C Multiple-Word Transmission Examples                                                                                                                                                                                                                                                                                           |                                                                      |

|   | 5.4  | Wideband [                                                                                                                                                                                                                                     | Data Transmission Precautions                                                                                                                                                                                                                                                                                                   | 5-15                                                                 |

| 6 | Reve | se Control                                                                                                                                                                                                                                     | Channel Arbitration Processing                                                                                                                                                                                                                                                                                                  | 6-1                                                                  |

|   | 6.1  |                                                                                                                                                                                                                                                | ontrol Channel Arbitration Processing Overview                                                                                                                                                                                                                                                                                  |                                                                      |

|   | 6.2  | RECC Arbit                                                                                                                                                                                                                                     | tration Methods                                                                                                                                                                                                                                                                                                                 | 6-3                                                                  |

|   |       | 6.2.1   | Software Control Arbitration                                    | 6-3 |

|---|-------|---------|-----------------------------------------------------------------|-----|

|   |       | 6.2.2   | Hardware Control Arbitration                                    | 6-3 |

|   |       | 6.2.3   | One or Two Busy/Idle Bits Observed                              | 6-3 |

| 7 | Auto  | matic F | requency Control                                                | 7-1 |

|   | 7.1   | Autom   | atic Frequency Control Overview                                 | 7-2 |

|   | 7.2   | AFC R   | eference                                                        | 7-3 |

|   | 7.3   | AFC S   | ystem Concept                                                   | 7-4 |

|   | 7.4   | AFC S   | ample Cycle Detailed Description                                | 7-5 |

| 8 | Keyb  |         | terface and Set Monitoring                                      |     |

|   | 8.1   | Keybo   | ard Interface and Set Monitoring Overview                       | 8-2 |

|   | 8.2   | Keybo   | ard Interrupt Inputs [KEY3:KEY0]                                |     |

|   |       | 8.2.1   | PIO Control Word (PIOC3 – Write Address 19H)                    |     |

|   |       | 8.2.2   | PIO3 Pullup Enabling (PI3PULL – Write Address 1BH)              | 8-3 |

|   |       | 8.2.3   | PIO3 Interrupt Control (PI3INT – Write Address 1CH)             | 8-3 |

|   |       | 8.2.4   | Event Register 2 (E2 – Read Address 06) Bit 6                   |     |

|   | 8.3   |         | 030 8-Bit Programmable Expansion I/O Ports                      |     |

|   |       | 8.3.1   | PIO Control Words (PIOC1 and PIOC2 – Write Address 15H and 17H) |     |

|   |       | 8.3.2   | PIO Output Words (PIO1 and PIO2 – Write Address 16H and 18H)    | 8-5 |

| 9 | Туріс |         | og Cellular Telephone Processing                                |     |

|   | 9.1   |         | I Analog Cellular Telephone System Overview                     |     |

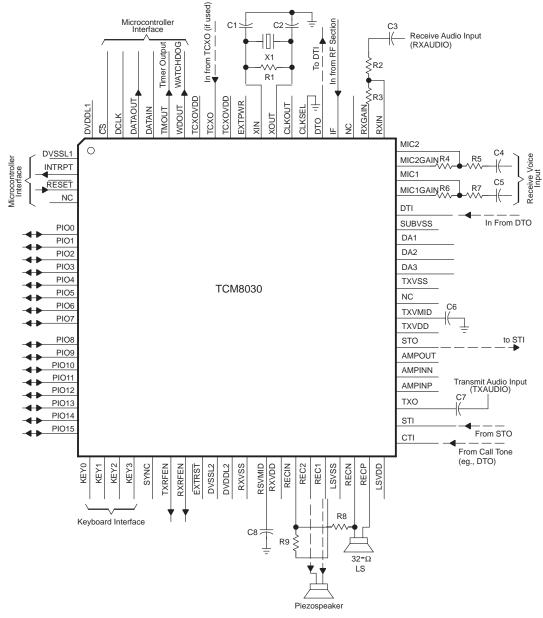

|   | 9.2   |         | Description                                                     |     |

|   |       | 9.2.1   | Parts List                                                      |     |

|   |       | 9.2.2   | Clock and Control                                               |     |

|   |       | 9.2.3   | Transmit Path                                                   |     |

|   |       | 9.2.4   | Receive Path                                                    |     |

|   |       | 9.2.5   | Digital-to-Analog Converters                                    |     |

|   |       | 9.2.6   | Timers                                                          |     |

|   |       | 9.2.7   | Keyboard Scan                                                   |     |

|   |       | 9.2.8   | I/O Expansion                                                   |     |

|   | 9.3   |         | pling on Supply Lines                                           |     |

|   | 9.4   |         | pling TXVMID and RXVMID                                         |     |

|   | 9.5   |         | hone Grounding                                                  |     |

|   | 9.6   |         | sted Trim Adjustment Sequence                                   |     |

|   |       | 9.6.1   | Transmit Adjustment Procedure                                   |     |

|   |       | 9.6.2   | Receive Adjustment Procedure                                    |     |

|   |       | 9.6.3   | Muting the Audio Path                                           |     |

|   |       | 9.6.4   | RF Stage Adjustment Procedure                                   |     |

| Α | Glos  | sary …  |                                                                 | A-1 |

# Figures

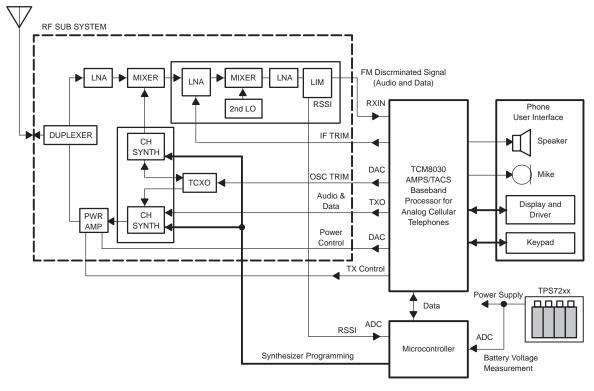

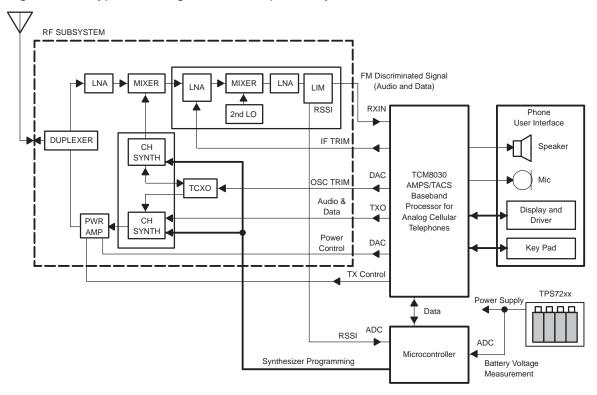

| 1–1  | TCM8030 Typical Analog Cellular Processing 1-2                                       |

|------|--------------------------------------------------------------------------------------|

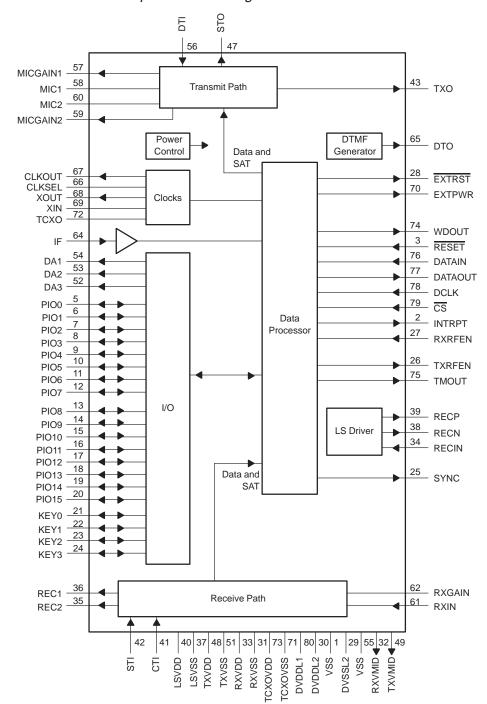

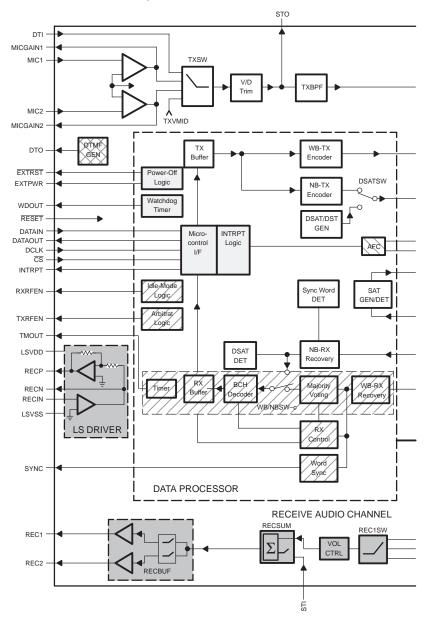

| 2–1  | TCM8030 Simplified Block Diagram 2-3                                                 |

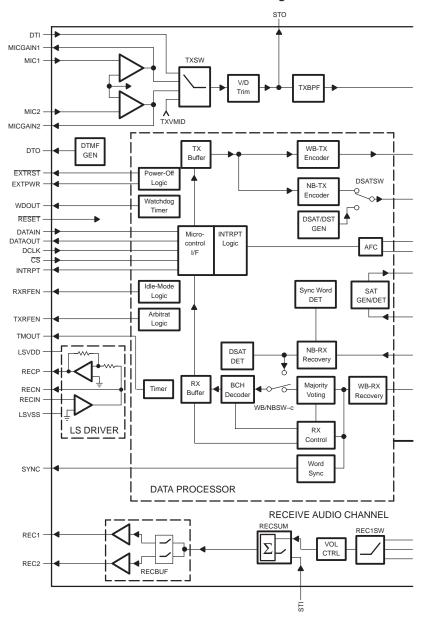

| 2–2  | TCM8030 Detailed Functional Block Diagram 2-4                                        |

| 2–3  | Receive Audio Path                                                                   |

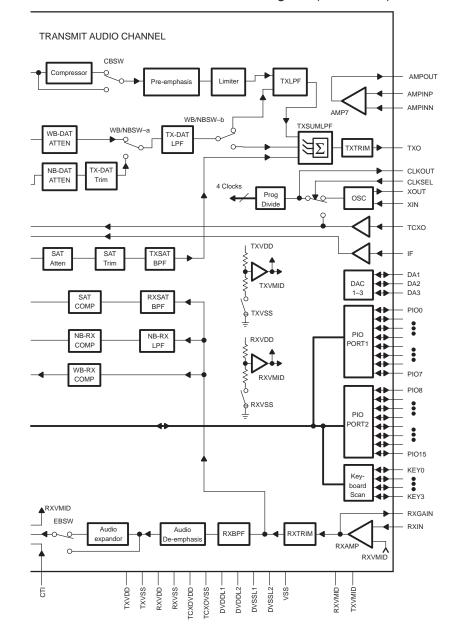

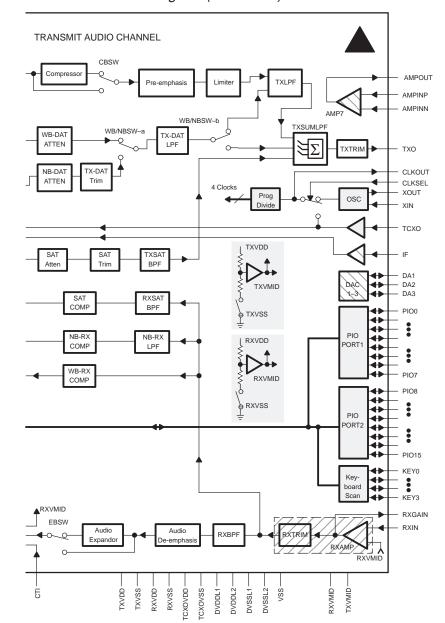

| 2–4  | Transmit Audio Path 2-7                                                              |

| 2–5  | Data Processor Block Diagram 2-9                                                     |

| 2–6  | Miscellaneous Circuit Block Diagrams 2-11                                            |

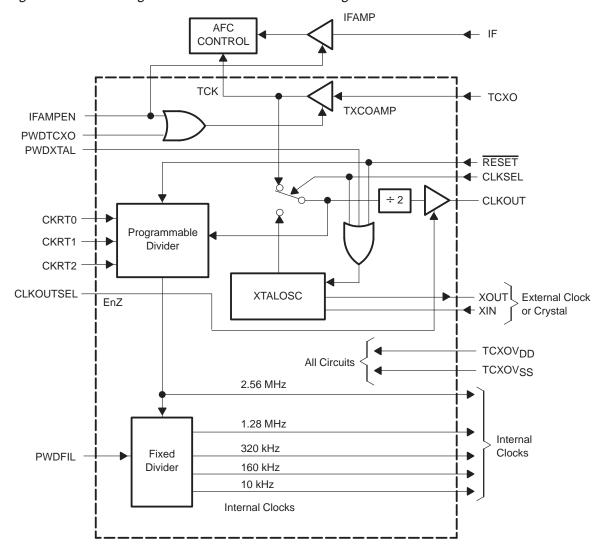

| 2–7  | Clocking Scheme Functional Block Diagram 2-14                                        |

| 2–8  | Power Modes Block Diagram                                                            |

| 3–1  | FOCC Frame Format                                                                    |

| 3–2  | Simplified FOCC Frame Format                                                         |

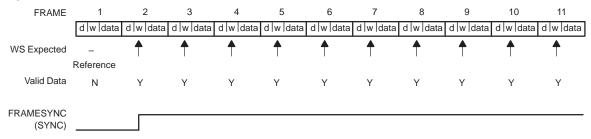

| 3–3  | FOCC Normal Operation                                                                |

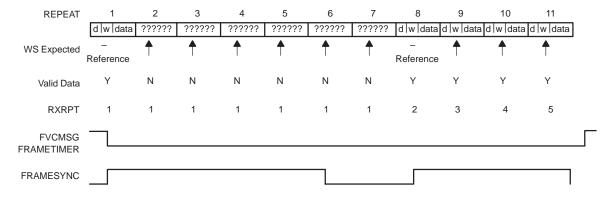

| 3–4  | FOCC Less Than Five Word Syncs Missing                                               |

| 3–5  | FOCC More Than Five Word Syncs Missing 3-7                                           |

| 3–6  | FOCC Single Word Sync Detected 3-7                                                   |

| 3–7  | FVC Message Stream                                                                   |

| 3–8  | FVC Normal Operation                                                                 |

| 3–9  | FVC Less Than Five Word Syncs Missed                                                 |

| 3–10 | FVC More Than Five Word Syncs Missed 3-11                                            |

| 3–11 | FVC One Word Received                                                                |

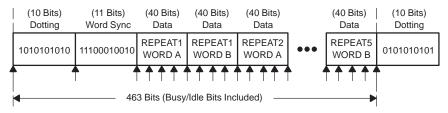

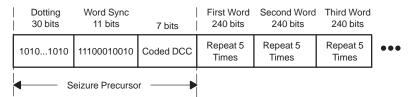

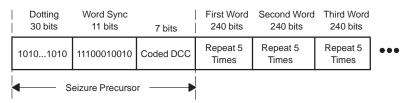

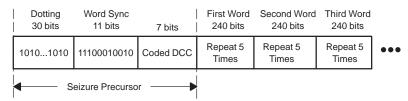

| 4–1  | RECC Message Stream 4-3                                                              |

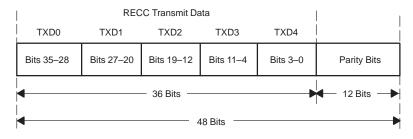

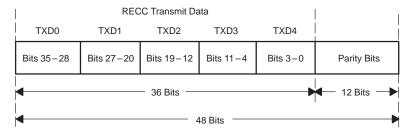

| 4–2  | RECC Word Format 4-5                                                                 |

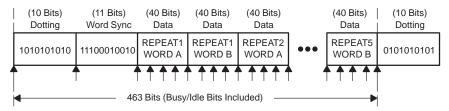

| 4–3  | RVC Message Stream 4-6                                                               |

| 4–4  | RVC Word Format                                                                      |

| 5–1  | RECC Message Stream                                                                  |

| 5–2  | RVC Message Stream                                                                   |

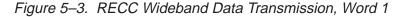

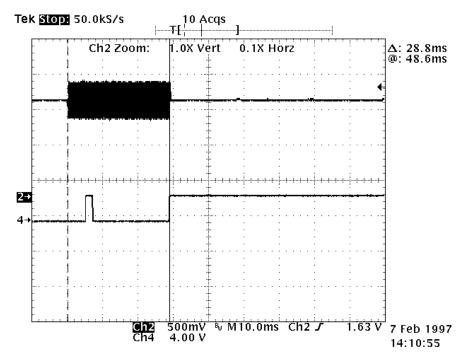

| 5–3  | RECC Wideband Data Transmission, Word 1 5-6                                          |

| 5–4  | RECC Wideband Data Transmission, Words 1 and 2 (Multiple-Word Transmission) 5-7      |

| 5–5  | RECC Wideband Data Transmission, Words 1, 2, and 3 (Multiple-Word Transmission) 5-8  |

| 5–6  | RVC Wideband Data Transmission, Word 1 5-12                                          |

| 5–7  | RVC Wideband Data Transmission, Words 1 and 2 (Multiple-Word Transmission) 5-13      |

| 5–8  | RVC Wideband Data Transmssion, Words 1, 2, and 3 (Multiple-Word Transmission) . 5-14 |

| 6–1  | RECC Message Stream (Arbitration)                                                    |

| 6–2  | FOCC Message Stream                                                                  |

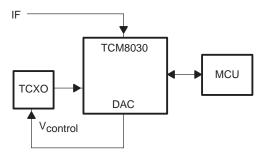

| 7–1  | AFC Closed-Loop System Block Diagram                                                 |

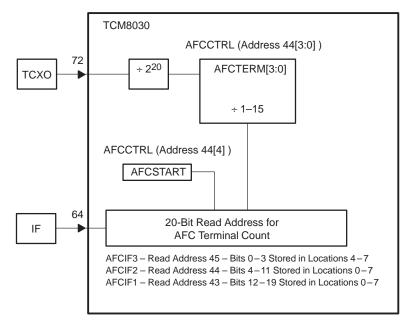

| 7–2  | AFC Diagram                                                                          |

х

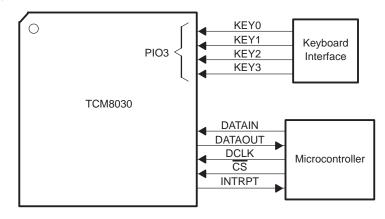

|     | TCM8030 Keyboard and Microcontroller Interface |     |

|-----|------------------------------------------------|-----|

|     | Analog Cellular Telephone Baseband Schematic   |     |

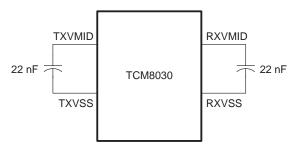

| 9–3 | Decoupling TXVMID and RXVMID                   | 9-8 |

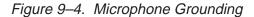

| 9–4 | Microphone Grounding                           | 9-9 |

# **Tables**

| 2–1 | Clock Sources                                             | 2-12 |

|-----|-----------------------------------------------------------|------|

| 2-2 | Master Clock Input Frequency and CLKOUT Select            |      |

| 2–3 | Power Modes Block Diagram Legend                          |      |

| 3–1 | Read/Write Address Information for Receive Processing     |      |

| 4–1 | Coded Digital Color Code                                  |      |

| 5–1 | Setup Procedures for Wide-Band Data Transmission on RECC  |      |

| 5–2 | Write to TX Buffer                                        |      |

| 5–3 | Commence Transmission                                     | 5-4  |

| 5–4 | Write to TX Buffer                                        | 5-5  |

| 5–5 | Setup Procedures for Wideband Data Transmission on RVC    | 5-9  |

| 5–6 | Write to TX Buffer                                        | 5-9  |

| 5–7 | Commence Transmission                                     | 5-10 |

| 5–8 | Write to TX Buffer                                        | 5-11 |

| 7–1 | AFC 20-Bit Terminal Count Read Address Control Execution  | 7-7  |

| 8–1 | PIO Control Word – PIOC3                                  | 8-3  |

| 8–2 | PIO3 Interrupt Control (PI3INT, Bits 3–0) Definition      | 8-3  |

| 8–3 | PIO3 Interrupt Control (PI3INT, Bits 7–4) Definition      |      |

| 8–4 | PIO Control Words – PIOC1 and PIOC2                       | 8-5  |

| 9–1 | Analog Cellular Telephone Components List                 |      |

| 9–2 | Typical Tranmsit Signal Levels AMPS Mode (3-V Operation)  | 9-12 |

| 9–3 | Typical Transmit Signal Levels NAMPS Mode (3-V Operation) |      |

| 9–4 | Typical Transmit Signal Levels TACS Mode (3-V Operation)  | 9-13 |

| 9–5 | Typical Transmit Signal Levels NTACS Mode (3-V Operation) | 9-13 |

| 9–6 | Typical Receive Signal Levels AMPS Mode (3-V Operation)   | 9-13 |

| 9–7 | Typical Receive Signal Levels NAMPS Mode (3-V Operation)  | 9-14 |

| 9–8 | Typical Receive Signal Levels TACS Mode (3-V Operation)   | 9-14 |

| 9–9 | Typical Receive Signal Levels NTACS Mode (3-V Operation)  | 9-14 |

### Chapter 1

### Introduction

This chapter provides an overview of TCM8030 analog cellular telephone baseband processing. It describes TCM8030 features and the power modes used in generic and specific processing applications, as detailed in later chapters.

| Торі | c Page                                        |

|------|-----------------------------------------------|

| 1.1  | Analog Cellular Telephone Baseband Processing |

| 1.2  | TCM8030 Features 1-3                          |

| 1.3  | Power Modes 1-4                               |

### 1.1 Analog Cellular Telephone Baseband Processing

The TCM8030 baseband processor provides a unique low-power solution for advanced mobile phone services (AMPS), narrowband advanced mobile phone services (NAMPS), total access communication systems (TACS), extended total access communication systems (ETACS), narrowband total access communication systems (NTACS), and Japanese total access communication systems (JTACS) baseband processing.

Figure 1–1 shows the TCM8030 in a typical telecommunications application.

**Note:** The TPS72xx family of the micropower low-dropout (LDO) voltage regulators provides the necessary power supply management for a typical analog cellular application using the TCM8030.

### 1.2 TCM8030 Features

The TCM8030 provides all data and audio processing functions for AMPS, NAMPS, TACS, ETACS, NTACS, and JTACS in a compact, low-power, baseband processor enclosed in an 80-pin TQFP package.

### 1.2.1 Data Processing Features

The TCM8030 provides data transceiver, data processing, and supervisory audio tone (SAT) functions, and includes the following data processing features:

- □ Single-chip processing for AMPS, NAMPS, TACS, ETACS, NTACS, JTACS, SAT, and digital supervisory audio tone (DSAT)

- 2.7-V to 5.5-V operation

- Serial interface

- User-configurable interrupt structure

- Transmit (TX) and receive (RX) data buffers

- Integrated RX and TX data filters

- TX wideband (WB) SAT filter

- RX WB and narrowband (NB) SAT filters

- **RX WB and NB data comparator**

- Programmable timer

- Independent watchdog timer

- RX/TX automatic mute functions

- Arbitration processing

- Twenty programmable expansion I/O ports

- U WB and NB-RX recovery

- Automatic frequency control (AFC)

- Multiple power-saving mode implementation

- Separate encoder for WB-TX and NB-TX

### 1.2.2 Audio Processing Features

The TCM8030 provides the following audio processing features:

- AMPS, NAMPS, TACS, ETACS, NTACS, and JTACS operation

- □ Integrated RX and TX voice filters

- Microphone amplifiers and loud speaker drivers

- Pre-emphasis and de-emphasis filtering

- Digitally-controlled gains and signal selection or muting

- Adjustable TX limiter

- Three 8-bit digital-to-analog converters (DAC) with output buffers

- Dual-tone multifrequency (DTMF) generator

- On-chip compandor

- Flexible clock and oscillator operation

### 1.3 Power Modes

The TCM8030 power mode structure provides independent powering of various on-chip circuits, thereby enabling the creation of low-power designs that are ideal for frequency modulation (FM) analog cellular telephones. The power modes are as follows:

- Total power-down mode

- □ Shutdown mode

- □ Idle mode

- Tonemode

- Full operation (DTMF TX off) mode

- □ Full operation (DTMF TX on) mode

### Chapter 2

# **Principles of Operation**

This chapter describes the principles that apply during operation of the TCM8030 analog cellular telephone processor.

### Topic

### Page

| 2.1 | Principles of Operation Overview 2-2 |

|-----|--------------------------------------|

| 2.2 | Receive Audio Path 2-6               |

| 2.3 | Transmit Audio Path 2-7              |

| 2.4 | Data Processor 2-9                   |

| 2.5 | Miscellaneous Circuits 2-11          |

| 2.6 | Clocks                               |

| 2.7 | Power Modes                          |

| 2.8 | Circuit Definitions 2-21             |

| 2.9 | Miscellaneous Functions 2-28         |

### 2.1 Principles of Operation Overview

The TCM8030 provides a complete, low-power, integrated solution for FM analog cellular telephones by integrating the analog processing and digital data processing functions onto one chip.

The TCM8030 contains transmit (TX) and receive (RX) analog paths, a digital data processor with filters, a compressor and expandor, routing switches, data input/output (I/O), an audio power amplifier, an uncommitted operational amplifier, and a DTMF generator. With these circuits, the TCM8030 applies appropriate signal levels for AMPS, NAMPS, TACS, ETACS, JTACS, and NTACS standards. In addition, both analog paths are software configurable such that all audio trimming functions can be achieved without manual intervention.

The TCM8030 data processor has several functional features: it performs transmit encoding and receive decoding, as well as majority voting and data recovery; it generates supervisory audio tone (SAT) and digital supervisory audio tone (DSAT); and it implements a number of independent circuits for arbitration logic, timers, and power logic. These features, along with a simple serial peripheral interface (SPI<sup>™</sup>) that interfaces with an external microcontroller, make the TCM8030 data processor extremely effective for all of the analog standards.

The TCM8030 provides greater integration than typical analog cellular baseband systems; thus, it reduces power consumption and increases talk and standby time. This integration, along with the other TCM8030 features, offers an efficient and effective cost solution for FM analog telephones and related applications.

Figure 2–1 shows a simplified block diagram of the device, and Figure 2–2 shows a detailed functional block diagram of the device.

Figure 2–1. TCM8030 Simplified Block Diagram

Principles of Operation 2-3

Figure 2–2. TCM8030 Detailed Functional Block Diagram

### Figure 2–2. TCM8030 Detailed Functional Block Diagram (Continued)

Principles of Operation 2-5

### 2.2 Receive Audio Path

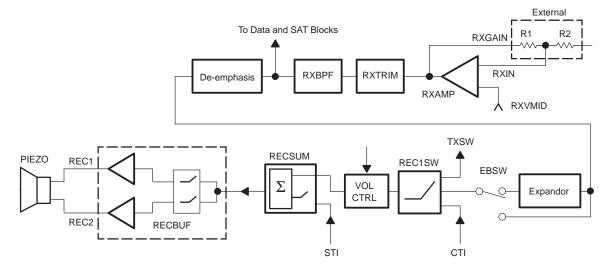

Figure 2–3 shows the receive audio path. A pair of external gain-setting resistors (R1 and R2) adjusts the input sensitivity to system requirements. A second digitally programmable gain trim is provided in RXTRIM, followed by a band-pass filter (BPF). The filter output drives the data/SAT blocks and the de-emphasis block.

Figure 2–3. Receive Audio Path

You can bypass the expandor for testing purposes or for applying linear functions. The switch REC1SW allows you to select either the transmit loop-back, the expandor output, or the call tone input (CTI) to feed into the digitally programmable volume control (VOL CTRL).

The receive summing block (RECSUM) sums (or does not sum) the sidetone input (STI) with the audio signal, based on a software command. The final stage consists of a pair of configurable receive buffers (RECBUF) that drives a piezospeaker or other light load. A separate loudspeaker driver block (LS DRIVER) is discussed later.

### 2.3 Transmit Audio Path

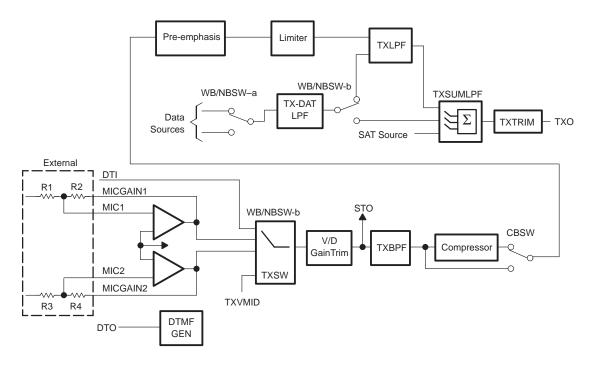

Figure 2–4 shows the block diagram for the transmit path. Here, you can select transmit inputs by using software control for the transmit switch (TXSW). The MIC1 and MIC2 inputs have operational amplifiers that you can configure with external gain-setting resistors R2/R1 and R4/R3. A selectable DTMF signaling input (DTI) is provided. You can use this with a programmable DTMF generator that has an independent output (DTO).

Figure 2–4. Transmit Audio Path

A programmable voice/DTMF gain trim stage (V/D TRIM) outputs to the sidetone output (STO) and drives the transmit band-pass filter (TXBPF). The signal from the TXBPF goes to the audio compressor. A bypass switch (CBSW) allows you to bypass the compressor for DTMF tones, as well as other uncompressed functions that might require testing.

The pre-emphasis and (deviation) limiter blocks then drive the transmit low-pass filter (TXLPF). This attenuates the harmonics caused by limiting the signal. Some data transmission modes use the TXLPF route, which inverts the signal. This requires reinversion of the data signal polarity using either inversion set/reset bits or external means. The transmit summer and low-pass filter block (TXSUMLPF) selects voice, data, or SAT signals and sums them together. It also provides a continuous-time smoothing filter that removes high-frequency products. The transmit gain-trim (TXTRIM) is the final stage that drives the output terminal (TXO).

### 2.4 Data Processor

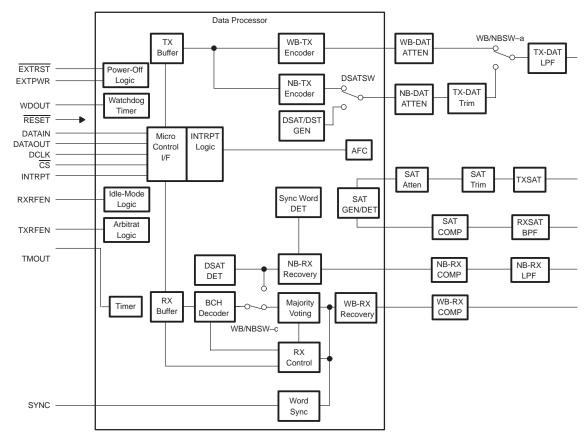

The data processor, shown in Figure 2–5, provides a large number of functions for processing cellular data streams and controlling other functions of the TCM8030. The microcontroller interface is a simple serial-shift register function that uses DATAIN, DATAOUT, DCLK, and  $\overline{CS}$  (active-low chip select), and has an interrupt output (INTRPT). This interface allows the TCM8030 to communicate with the microcontroller that is operating the telephone.

Figure 2–5. Data Processor Block Diagram

Power-off and idle-mode logic are provided, together with both standard and watchdog timers. The data processor selects incoming receive (RX) data according to standard (for example, WB/NB). The filters/comparators process the data to comply with the standard. After majority voting and/or BCH decoding, the data processor buffers the data and applies it to the microcontroller interface. On the transmit side, data moves to the TX buffer after the data processor selects the appropriate encoder. The encoded data

Principles of Operation 2-9

goes through the attenuator and/or trim stage to the transmit data low-pass filter (TX-DAT LPF) and switches to the transmit (TX) audio path.

The RXSAT filter and SAT comparator recover the SAT (supervisory audio tone) from the receive audio path and feed it to the data processor detector/ generator. The SAT GEN/DET block generates TXSAT and applies it through programmable attenuator/trim stages to the band-pass filter that feeds the transmit path.

The NB data recovery block detects a DSAT (digital supervisory audio tone) signal. The DSAT/DST GEN regenerates the DSAT signal and sends it through the normal NB-DAT path to the transmit path.

### 2.5 Miscellaneous Circuits

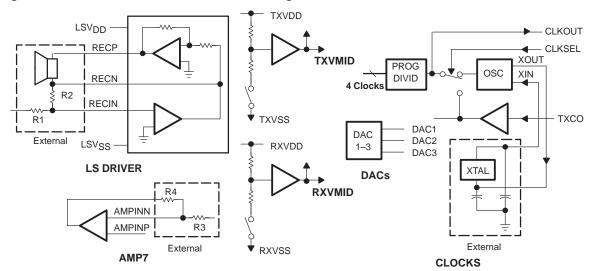

Figure 2–6 shows miscellaneous circuit block diagrams. The LS DRIVER block provides the capability to drive loudspeakers. The external resistor pair R2/R1 sets the gain. An uncommitted operational amplifier (AMP7) is provided, and the external resistor pair R4/R3 sets the gain.

Figure 2–6. Miscellaneous Circuit Block Diagrams

A separate mid-rail voltage source is provided for both the receive and transmit paths (RXVMID and TXVMID). Each is deselected when its part of the circuit powers down.

You may program the TCM8030 clocking source (oscillator signal or external clock) that applies to a programmable divide (PROG DIVID). PROG DIVID divides the clocking source into four separate internal clocking signals. The oscillator block requires only a crystal oscillator (XTAL) and a pair of capacitors for operation. Alternatively, you can connect an external clock at XIN, or you may select a TCXO, as required. A triple DAC is also provided for oscillator trim functions. When used in conjunction with the AFC control in the data processor block, the triple DAC allows you to use lower stability oscillators successfully, to save system costs.

### 2.6 Clocks

The TCM8030 oscillator and programmable divider (OSC and PROG DIVID) circuits generate internal clocks and an external clock output on the CLKOUT terminal. The circuits are shown in Figure 2–2.

The TCM8030 CLKSEL terminal selects the clocking source, as shown in Table 2–1.

| TCM8030 Clocking Scheme                                        | CLKSEL | Description                                                                                                                                                                                                                                                                                                                     |

|----------------------------------------------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| XTALOSC                                                        | LOW    | Clock Source is the internal crystal oscillator (XTALOSC).<br>An external crystal oscillator is required and is connected<br>between XIN and XOUT (terminals 69 and 68). Any<br>frequency in Table 2–2 is allowed. In addition, TCXOAMP<br>can be enabled by selecting IFAMPEN in register AUXPE<br>(write address 30H, bit 4). |

| External square wave                                           | LOW    | Clock source is an external square wave frequency with a<br>standard CMOS logic level input applied to XIN<br>(terminal 69). Any frequency in Table 2–2 is allowed. In<br>addition, TCXOAMP can be enabled by selecting<br>IFAMPEN in register AUXPE (write address 30H, bit 4).                                                |

| External TCXO (temperature-<br>compensated crystal oscillator) | HIGH   | Clock source is an external TCXO with a minimum<br>amplitude of 0.5-Vp-p applied to TCXO (terminal 72). Any<br>frequency in Table 2–2 is allowed. In this mode, the<br>XTALOSC block is powered down and TCXOAMP is<br>enabled independent of the settings of register AUXPE<br>(write address 30H).                            |

Table 2–1. Clock Sources

The TCM8030 has an automatic frequency control (AFC)circuit that maintains the accuracy of an external temperature-compensated crystal oscillator (TCXO). For the first two clock sources (XTALOSC or external square wave), the AFC circuit operates with any TCXO operating at a frequency less than 20 MHz. However, for the third clock source (external TCXO), the AFC operates with a TCXO at a frequency associated with CKRT (write address 31H, bits 0–2), as shown in Table 2–2.

| Bit 2<br>CKRT2 | Bit 1<br>CKRT1 | Bit 0<br>CKRT0 | Bit 3<br>CLKOUTSEL | Frequency<br>Selected | Terminal<br>CLKOUT |

|----------------|----------------|----------------|--------------------|-----------------------|--------------------|

| 0              | 0              | 0              | Х                  | 5.12 MHz              | Х                  |

| 0              | 0              | 1              | Х                  | 7.68 MHz              | Х                  |

| 0              | 1              | 0              | Х                  | 10.24 MHz             | Х                  |

| 0              | 1              | 1              | Х                  | 12.8 MHz              | Х                  |

| 1              | 0              | 0              | Х                  | 15.36 MHz             | Х                  |

| 1              | 0              | 1              | Х                  | 17.92 MHz             | Х                  |

| 1              | 1              | 0              | Х                  | †                     | Х                  |

| 1              | 1              | 1              | Х                  | †                     | Х                  |

| Х              | Х              | Х              | 0                  | Х                     | Active             |

| Х              | Х              | Х              | 1                  | Х                     | Hi-Z               |

Table 2–2. Master Clock Input Frequency and CLKOUT Select

+ CKRT(bits 0–2) = 110 and 111 are not allowed.

The TCM8030 also provides an external divide-by-two counter clock (CLKOUT). If CLKSEL is high, the internal XTALOSC or external square wavefrequency signal source routes through a divide-by-two counter to CLKOUT. If CLKSEL is low, the external TCXO frequency routes through the divide-bytwo counter to CLKOUT. CLKOUTSEL is low after reset. CLKOUT is active.

The TCM8030 also possesses a frequency divider circuit that derives the internal and external reference clocks (2.56 MHz to the data processor and 1.28 MHz, 320 kHz, 160 kHz, and 10 kHz to the audio processor).

The internal crystal oscillator (XTALOSC), TCXO input recovery circuit (TCXOAMP), and internal dividers (PROG DIVID) share their own dedicated power supply terminals. This minimizes crosstalk from the rest of the circuit, therefore reducing the amount of clock jitter.

All the clock circuits power down in the TCM8030 power-down mode. In all other modes, the clock circuits stay active. Program the appropriate external clock or crystal frequencies using the clock source frequency-select, write address 31H, CLKSRC. Use CKRT0 – CKRT2 (CLKSRC bits 0–2) to program the frequency, and CLKOUTSEL (CLKSCR bit 3) to enable or disable CLKOUT. A reset will select, by default, a 5.12-MHz frequency (CKRT0 – CKRT2 = 000) and CLKOUT will become active (CLKOUTSEL = 0) (see Table 2–2). Figure 2–7 illustrates the TCM8030 clocking scheme.

Figure 2–7. Clocking Scheme Functional Block Diagram

Clocks

### 2.7 Power Modes

The TCM8030 contains power-off logic circuitry that implements six modes of operation, as shown in Table 2–3 and Figure 2–8. These modes are selected by control word 4. In total power-down mode, all internal circuits, including the crystal oscillator (XTALOSC), are disabled.

| Power Modes                                          | Description                                                                                                                                                                                                                                                                                                             |              | Coding |              |

|------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------|--------------|

| 1. Total power-down<br>mode                          | Power is applied to the TCM8030, but all circuits are powered down.<br>EXTPWR is low to disable power supply to the rest of the phone. Only<br>a static power-up using one of the keyboard interrupt ports allows the<br>TCM8030 to exit total power-down mode. When this happens, the<br>TCM8030 enters shutdown mode. |              |        |              |

| 2. Shutdown mode                                     | Power is applied to the TCM8030, but the phone is unable to receive calls. The microcontroller may access internal registers, but it may not issue commands. Only the circuits with the following coding are on.                                                                                                        |              |        |              |

| 3. Idle mode                                         | Power is applied to the TCM8030, and the phone is monitoring the forward control channel (FOCC) from the base station. Only the circuits with the following coding are on.                                                                                                                                              |              |        |              |

| 4. Tone mode                                         | Power is applied to the TCM8030, but the phone is not in communication with the base station. The user interface (via the $I/O$ ports) is enabled. Only the circuits with the following coding are on.                                                                                                                  |              |        | $\bigotimes$ |

| 5. Full operation mode,<br>DTMF off                  | Power is applied to the TCM8030. The phone is in conversation mode, but the DTMF generator is not enabled. All circuits except the circuit with the following coding are on.                                                                                                                                            | $\bigotimes$ |        |              |

| 6. Full operation mode,<br>DTMF on                   | Power is applied to the TCM8030. The phone is in conversation mode, but the DTMF generator is enabled. All circuits are on.                                                                                                                                                                                             |              |        |              |

| Auxiliary Circuits<br>Power enabled<br>independently | Independent enabling can be applied to IFAMP, DAC1–3, and AMP7.<br>Only the circuits with the following coding have this feature. In total<br>power-down mode, this feature and these circuits are disabled.                                                                                                            |              |        |              |

Table 2–3. Power Modes Block Diagram Legend

Figure 2–8. Power Modes Block Diagram

Figure 2–8. Power Modes Block Diagram (Continued)

Principles of Operation 2-17

### 2.7.1 Total Power-Down Mode

In this mode, power is still applied to the TCM8030, but the device is in total power-down mode. All circuits, including CLOCK, bias circuits, PIOs, and the watchdog timer, power down. The TCM8030 stops so it draws minimal leakage current, as illustrated in Figure 2–8. The EXTPWR output terminal is low to disable the power supply to the rest of the telephone (including the MCU). The EXTRST terminal is also low, and the TCM8030 microcontroller interface is disabled.

The TCM8030 is the only device in the telephone with its power supply enabled in total power-down mode. Static power-up logic, implemented using one of the keyboard interrupt ports, waits for the power-on key to be pressed. After the key is pressed, the TCM8030 exits the total power-down mode, reactivates the oscillator, enables the regulators to the rest of the telephone (using the EXTPWR enable signal), and holds the EXTRST terminal low for 0.1 to 0.2 second, to allow the rest of the telephone to go to power-up reset mode when the system is stable.

The TCM8030 goes into total power-down mode by writing to control word 4, (write address 03H, C4 bits 4-0). You must toggle both control word 4 (C4) bits 1-0, with this write transaction. The security bit, C4 bit 1, reduces the probability that the total power-down mode is entered erroneously, for example, by RFI (radio frequency interference).

The independent analog circuits IFAMP, AMP7, and DAC1–3 also power down in total power-down mode, independent of the status of their own power-down control bits in register AUXPE (write address 30H).

The cellular telephone uses the total power-down mode from the first connection of the battery as follows:

- The telephone receives power for the first time when the battery is connected. Only TCM8030 initially connects to its power supply, powering up in shutdown mode. In this mode, CLKSEL sets the TCM8030 master clock source (see Section 2.6, *Clocks*), and it immediately sets EXTPWR high.

- The power-up RESET input to the TCM8030 is held low during the operation of the external power-on-reset (RC) circuit. This also holds EXTRST at low.

- 3) When the external power-on reset mode finishes, EXTRST transitions to high, the TCM8030 microcontroller interface enables, and the MCU starts its boot routine. Because the TCM8030 INTRPT terminal is not set to one, the MCU knows that it was reset by a battery connect power up. (In this

situation the telephone should appear to be off until the power-on key is pressed). The MCU then writes to the TCM8030 to:

- Enable a keypad interrupt on the appropriate KEY pin. This requires four write transactions to TCM8030 registers:

- PI3INT (write address 1CH) to enable the pin interrupt

- PI3PULL (write address 1BH) to enable or disable the pullup as required

- PIOC3 (write address 19H) to set direction as input

- IE2 (write address 06H) to enable interrupts from the PIO3, keypad port

- Set the C4 bits 4–0 to 02H to enter total power-down mode.

The MCU must first enable the keypad port terminal connected to the power-on key before entering total power-down mode. If the MCU does not, only a RESET to the TCM8030 will re-enable it.

- At this point the clock stops, EXTPWR transitions to low, EXTRST transitions to low, and the MCU and other parts of the system power off, waiting for the power-on key to be pressed.

- 5) When you press the power-on key, it is sensed on one of the KEY inputs. Asynchronous logic, which does not need the clock, reads the power-on key, forces TCM8030 back into shutdown mode, and turns EXTPWR back on. The TCM8030 event register also records the fact that a keypad interrupt was received.

- 6) EXTPWR transitions to high and powers up the microcontroller, and after a timed interval of between 0.1 and 0.2 second, including the XTALOSC warm-up time, TCM8030 releases EXTRST, allowing the rest of the system to power up and reset when the system is stable. The MCU then executes its boot routine.

- 7) At this time, the INTRPT terminal from the TCM8030 is in active mode, and the microcontroller checks the TCM8030 event register and determines it was awakened by a keypad event, such as a pressed power-on key. When the MCU is awakened, the microcontroller starts to initialize the entire system, as appropriate.

### 2.7.2 Shutdown Mode

The microcontroller interface, clock, bias circuits, watchdog timer blocks, and all three PIOs remain operational in the shutdown mode, as illustrated in

Figure 2–8. The shutdown mode can be used when the telephone is switched on but cannot receive calls, for example, while the battery is recharging. The microcontroller interface may access all internal registers during shutdown mode, but may not issue commands (addresses 08H to 0EH).

### 2.7.3 Idle Mode

In addition to the circuits that are operational in shutdown mode, the wideband receive data path is enabled, as illustrated in Figure 2–8. This corresponds to the telephone being in idle mode, on a forward-control channel (FOCC). Two submodes also activate within the idle mode to further minimize power consumption in the telephone. First, the MCU idle submode (see the *TCM8030 Analog Baseband Data Manual* description for register E2 in read address map – read address 06H) enables the MCU to go to sleep when it does not receive any new messages, and the RXRF idle submode (see the *TCM8030 Analog Baseband Data Manual* description for register RXRFTIM in write address map – write address 20H) powers down the RF receiver when it is not needed.

### 2.7.4 Tone Mode

In addition to the circuits in shutdown mode, the DTMF generator and the section of the RX audio path that follows the call tone input (CTI) power up in tone mode, as illustrated in Figure 2–8. This mode is used when the telephone powers up, and when the user interface, such as the keypad and user memories, is enabled but the telephone does not communicate with the base station.

#### 2.7.5 Full Operation Mode, DTMF TX Off

This mode corresponds to a telephone conversation in progress. All circuits are on, except the DTMF generator, as illustrated in Figure 2–8.

#### 2.7.6 Full Operation Mode, DTMF TX On

This mode is enabled so that a DTMF tone can be transmitted during a telephone conversation. All circuits are on, as illustrated in Figure 2–8.

#### 2.7.7 Independent Circuits

The IFAMP, DAC1–3, and AMP7 blocks can be individually powered down as described in the AUXPE register (write address 30H). These bits are overridden, and all circuits power down in total power-down mode, as illustrated in Figure 2–8.

# 2.8 Circuit Definitions

Within the TCM8030, certain circuits control specific analog baseband processor operations. Below is a list of these circuits and a description of their function.

#### 2.8.1 Transmit Path Audio Processing Functions

The TCM8030 audio transmit path is composed of the following circuits, as shown in Figure 2–2. A brief functional description is given for each circuit.

MIC1 and MIC2 amplifier

A pair of single-ended microphone amplifiers accept two input signals (MIC1 and MIC2). Gains for MIC1 and MIC2 are set using external resistors. Output from each amplifier is fed back through terminals MICGAIN1 and MICGAIN2.

TXSW

The transmit switch (TXSW) selects one of four transmit audio sources. It selects either the voice signal from MICAMP1 or MICAMP2; the input pin DTI, which connects externally to the DTMF generator; or connects to TXVMID to mute the transmit path.

U/D Trim

The voice or DTMF trim (V/D TRIM) circuit uses an antialiasing filter to process the audio signal before it is applied to the transmit band-pass filter. This circuit block also provides a means to trim the voice and DTMF signal levels.

☐ TXBPF

The transmit band-pass filter (TXBPF) is a switched capacitor band-pass filter that passes only the transmit audio frequencies from 300 Hz to 3 kHz.

Compressor

The compressor circuit compresses the audio signal and outputs a signal with a change of 1 dB for an input signal change of 2 dB.

CBSW

The compressor bypass switch (CBSW) permits the routing of the audio signal around the audio compressor circuit when testing the audio channel or passing DTMF signals.

Pre-emphasis

As audio frequencies increase, the pre-emphasis circuit increases the signal gain at a rate of 6 dB per octave across the 300-Hz to 3-kHz audio passband.

Limiter

The limiter circuit limits the transmit signal deviation within an acceptable range. The limiter has a set gain of +6.0 dB. The limiter also maintains a software programmable trim with a trim range from -10.97 dB to 7.5 dB.

TXLPF

The transmit low-pass filter (TXLPF) is a switched-capacitor filter that removes harmonics caused by the (deviation) limiter. Linear-phase design prevents overshoots. This circuit is also used in narrowband mode to filter switched-capacitor output noise from TX-DAT LPF.

TXSUMLPF

The transmit-summing and low-pass filter (TXSUMLPF) is a switchedcapacitor filter that selectively sums voice, data, or SAT into the audio output. It also includes a low-pass switched-capacitor filter to reduce spurious output emissions above 10 kHz.

□ TXTRIM

The transmit trim stage (TXTRIM) trims the FM deviation by transmitting either ST or wideband data prior to its output on the TXO terminal. This stage has a continuous second-order smoothing filter that removes noise.

## 2.8.2 Receive Path Audio Processing Functions

The TCM8030 audio receive path is composed of the following circuits, as shown in Figure 2–2. A brief functional description is given for each circuit.

□ RXAMP

The receive amplifier circuit (RXAMP) receives its input from the RXIN terminal. A portion of the RXAMP output is applied, through the RXGAIN terminal, to a pair of external resistors that set the stage gain. The RXAMP noninverting input internally connects to the RXVMID reference level.

□ RXTRIM

The receive trim (RXTRIM) stage compensates for FM discriminator variations. This block also contains a switched-capacitor filter to perform antialiasing.

## RXBPF

The receive band-pass filter (RXBPF) is a switched-capacitor filter with a passband from 300 Hz to 3 kHz.

#### DE-EMPHASIS

As audio frequencies increase, the de-emphasis circuit decreases the signal gain at a rate of 6 dB per octave across the 300-Hz to 3-kHz audio passband.

#### □ EXPANDOR

The audio expandor circuit expands the audio signal and outputs the signal with a change of 2 dB for an input signal change of 1 dB.

#### EBSW

The expandor bypass switch (EBSW) permits the routing of the received audio signal around the expandor during testing.

#### REC1SW

The receive 1 switch (REC1SW) selects one of three receive sources. REC1SW selects either the output from the expandor circuit (expanded or bypassed), the call tone (CTI) input, or selects and connects REC1SW to RXVMID to mute the receive path.

#### VOL CTRL

The volume control (VOL CTRL) circuit can be programmed to provide a nominal gain of -20 dB to 17.5 dB for the outputs REC1 and REC2.

#### RECSUM

The receiver summing circuit and switch (RECSUM) provide the means for adding sidetone (STI) input into the receive audio path.

#### RECBUF

The receiver buffer (RECBUF) switches or mutes two output buffers independently, or it connects these buffers in differential mode so that a piezo-speaker can be connected to REC1 and REC2 terminals. Independent control of the two audio outputs allows one to be used for external hands-free operation.

#### LS DRIVER

The loudspeaker driver (LS DRIVER) circuit is a selectable differential or single-ended output earpiece amplifier. It drives a 32  $\Omega$  dynamic earpiece (or a piezoearpiece).

#### 2.8.3 Transmit Path Data Processing Functions

The TCM8030 data processing functions associated with the transmit path are performed by the following circuits as shown in Figure 2–2. A brief functional description is given for each circuit.

#### TX BUFFER

The transmit buffer (TX BUFFER) buffers both narrowband and wideband data that is loaded from the five transmit-data word registers (TXD0 – TXD4, write addresses 10H–14H).

#### WB-TX ENCODER

The wideband transmit data encoder circuit (WB-TX ENCODER) receives the data from the transmit buffer and performs all the necessary operations for both the reverse control channel (RECC) and reverse voice channel (RVC) data transmission. It calculates and adds BCH parity bits to the data, along with word sync and dotting. The data is repeated as specified for analog cellular. The wideband signaling tone (ST) is generated when required.

#### NB-TX ENCODER

The narrowband transmit data encoder circuit (NB-TX ENCODER) calculates the BCH encoding parity bits from the data in the transmit buffer and adds the 30-bit synch word to synchronize the transmission of RVC data to the DSAT.

#### DSATSW

The digital supervisory audio tone switch (DSATSW) selects either narrowband data or the output from the DSAT/DST GEN stage for application to the NB-DAT ATTEN stage. The fifth and sixth bits of the operational control word C1 (write address 00H) control the operation of the DSATSW. When bits 5 and 6 are set to zero, the switch connects to the NB-TX encoder input.

□ WS/NBSW-a, -b, and -c

The wideband and narrowband switches (WB/NBSW -a through -c), grouped together, select either narrowband or wideband transmission operation. The switch position is controlled by the value in bit one of the operational control word C1 (write address 00H).

#### DSAT/DST GEN

The digital supervisory audio tone/digital signaling tone generator (DSAT/DST GEN) circuit generates the narrowband DSAT and DST signals.

#### □ NB-DAT ATTEN and WB-DAT ATTEN

These two circuits are fixed narrowband and wideband data attenuators (NB-DAT ATTEN AND WB-DAT ATTEN) that set a fixed attenuation to provide the correct data signal levels.

#### TX-DAT TRIM

The transmit data trim circuit (TX-DAT TRIM) trims the DSAT, DST, and narrowband data levels.

TX-DAT LPF

The transmit data low-pass filter circuit (TX-DAT LPF) provides low-pass switched-capacitor filtering of the DSAT and DST. It also transmits narrowband and wideband data to minimize output harmonics and correct narrowband transmitted data eye patterns.

# 2.8.4 Receive Path Data Processing Functions