## TMS320FLEX Family

Messaging System Solutions With Alphanumeric Roaming Decoder

# Design Manual

Wireless Communications Business Unit

1997

TEXAS

## TMS320FLEX Family Messaging System Solutions With Alphanumeric Roaming Decoder Design Manual

This product is manufactured under a license from Motorola Inc. to Motorola's applicable FLEX<sup>™</sup> protocol patent rights, and you benefit from this license except in the event that you assert against Motorola<sup>™</sup> or its customers a patent essential to products compatible with the FLEX<sup>™</sup> protocol.

> SPRA193 June 1997

#### **IMPORTANT NOTICE**

Texas Instruments (TI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

TI warrants performance of its semiconductor products and related software to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Certain applications using semiconductor products may involve potential risks of death, personal injury, or severe property or environmental damage ("Critical Applications").

TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

Inclusion of TI products in such applications is understood to be fully at the risk of the customer. Use of TI products in such applications requires the written approval of an appropriate TI officer. Questions concerning potential risk applications should be directed to TI through a local SC sales office.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards should be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

Copyright © 1997, Texas Instruments Incorporated

#### Preface

## **Read This First**

#### About This Manual

The Texas Instruments (TI<sup>m</sup>) *TMS320FLEX Family Messaging System Solutions With Alphanumeric Roaming Decoder Design Manual* describes the products that can be used to design embedded messaging functionality into computers, automobiles, and smart home electronics. This manual is part of a set of three manuals developed for this purpose (see *Related Documentation*).

This set of documents provides detailed information on the TLV5590 decoder and the analog-to-digital converters that enable you to develop embedded messaging functions that implement the FLEX protocol. Interfacing these components to your existing receivers and microcontrollers means that your application will required little, if any, hardware redesign.

The following decoders can be used with either the TLV5590 or TLV5592 converter to create a customized application.

- TLV5591BVF Alphanumeric Decoder

- □ TLV5594VF Numeric

- TLV5593VF Alphanumeric Roaming

Common features of the three decoders include:

- FLEX messaging protocol signal processor

- Decoding at 1600, 3200, or 6400 bits per second (bps)

- Real-time clock time base

- Low battery indication (external detector)

- Standard serial peripheral interface (SPI) in slave mode

- Highly programmable receiver control

- Compatible with synthesized receivers

- Low-current STOP mode operation of host processor

Features specific to each decoder include:

- TLV5591BVF Alphanumeric Decoder

- 16 programmable user-address words

- 16 fixed-temporary addresses

- Any-phase decoding

- □ TLV5594VF Numeric

- 4 programmable user-address words

- Single-phase decoding

- TLV5593VF Alphanumeric Roaming

- 16 programmable user-address words

- 16 fixed temporary addresses

- 16 operator messaging addresses

- Any-phase or single-phase decoding

- FLEX fragmentation and group messaging support

- Real-time clock over-the-air update support

- Simulcast system identifier (SSID) and network ID (NID) roaming support

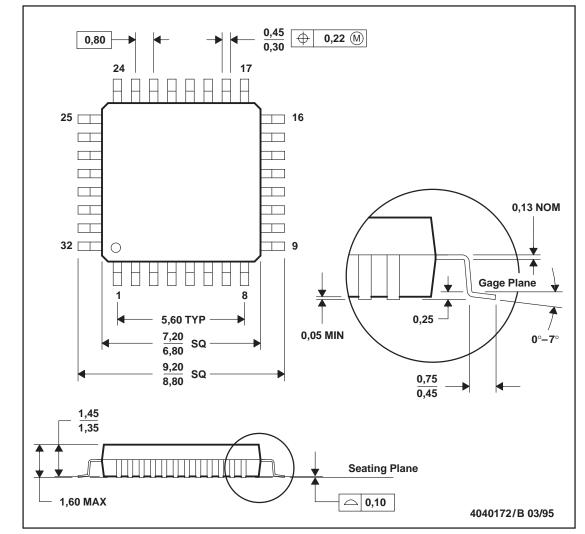

- 28 used pins (32-pin thin quad flatpack (TQFP) standard)

- Pin-compatible with all other FLEX decoder signal processors

See Appendix C, *Mechanical Data*, for the package diagram that applies to each of the decoders.

#### How to Use This Manual

This manual contains the following chapters:

| Chapter 1  | Introduction<br>Presents an overview of FLEX <sup>™</sup> messaging protocol and a general description<br>of the TMS320FLEX Family chipset |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| Chapter 2  | FLEX Signal Structure<br>Describes the TLV5593VF FLEX signal structure                                                                     |

| Chapter 3  | TLV5593VF FLEX Decoder<br>Describes the TLV5593VF FLEX decoder                                                                             |

| Appendix A | TLV5590 Data Sheet<br>Presents a complete TLV5590 converter data sheet with its own page<br>numbering                                      |

| Appendix B | <b>Timing Diagrams</b><br>Presents the timing diagrams for the TLV5593VF decoder                                                           |

| Appendix C | Mechanical Data<br>Presents the mechanical data for the TLV5593VF decoder                                                                  |

#### **Related Documentation From Texas Instruments**

The following books describe the TMS320FLEX Family Decoders and related tools. To obtain a copy of any of these TI documents, call the Texas Instruments Literature Response Center at (800) 477–8924. When ordering, please identify the book by its title and literature number.

TMS320FLEX1 Messaging System Solutions Design Manual (literature number SPRA086)

TMS320FLEX Family Messaging System Solutions With Numeric Decoder Design Manual (literature number SPRA183)

TMS320FLEX Family Messaging System Solutions With Alphanumeric Roaming Decoder Design Manual (literature number SPRA193)

#### Trademarks

FLEX, FLEXstack, and Motorola are trademarks of Motorola Inc.

TI is a trademark of Texas Instruments Incorporated.

## Contents

| 1 | Introd |        |                                                         |      |

|---|--------|--------|---------------------------------------------------------|------|

|   | 1.1    |        | Messaging Overview                                      |      |

|   | 1.2    | Chipse | et Description                                          |      |

|   |        | 1.2.1  | TLV5593VF FLEX Roaming Decoder                          |      |

|   |        | 1.2.2  | TLV5590 A/D Converter                                   | 1-3  |

| 2 | FLEX   | Signal | Structure                                               | 2-1  |

|   | 2.1    |        | ronization                                              |      |

|   |        | 2.1.1  | Block Information Field                                 | 2-2  |

|   |        | 2.1.2  | Address Field                                           | 2-2  |

|   |        | 2.1.3  | Vector Field                                            | 2-3  |

|   |        | 2.1.4  | Message Field                                           | 2-3  |

|   | 2.2    | FLEX N | Message Word Definitions                                | 2-4  |

|   |        | 2.2.1  | Numeric Data Message                                    | 2-4  |

|   |        | 2.2.2  | Bit Definitions                                         | 2-4  |

|   |        | 2.2.3  | Message Fill Rules                                      | 2-5  |

|   |        | 2.2.4  | Special Format Numeric                                  | 2-5  |

|   | 2.3    | Hex/Bi | nary Message                                            | 2-6  |

|   |        | 2.3.1  | Bit Definitions                                         | 2-6  |

|   |        | 2.3.2  | Message Content                                         | 2-8  |

|   |        | 2.3.3  | Fragment Termination                                    | 2-8  |

|   |        | 2.3.4  | Message Header                                          | 2-8  |

|   | 2.4    | Alphan | numeric Message                                         | 2-9  |

|   |        | 2.4.1  | Bit Definitions                                         | 2-9  |

|   |        | 2.4.2  | Message Content                                         | 2-11 |

|   |        | 2.4.3  | Message Termination                                     | 2-11 |

|   |        | 2.4.4  | Alphanumeric Message Rules for Symbolic Characters Sets | 2-11 |

|   |        | 2.4.5  | Enhanced Fragmentation Rules                            | 2-11 |

|   | 2.5    | Secure | e Message                                               | 2-13 |

|   |        | 2.5.1  | Bit Definitions                                         | 2-13 |

|   |        | 2.5.2  | Message Content                                         | 2-14 |

|   |        | 2.5.3  | Message Termination                                     | 2-14 |

|   | 2.6    | FLEX E | Encoding and Decoding Rules                             | 2-15 |

|   |        | 2.6.1  | FLEX Encoding Rules                                     | 2-15 |

|   |        | 2.6.2  | FLEX Decoding Rules                                     | 2-16 |

|   | 2.7    | FLEX ( | Character Sets and Rules                                | 2-17 |

|   |        | 2.7.1  | Alphanumeric Character Set                              | 2-17 |

|   |        | 2.7.2  | Numeric Character Set                                   | 2-17 |

|   | 2.8    | FLEX L | Local Time and Date                                     | 2-19 |

|   |      | 2.8.1    | Month/Day/Year                                     | 2-19 |

|---|------|----------|----------------------------------------------------|------|

|   |      | 2.8.2    | Second/Minute/Hour                                 | 2-19 |

|   |      | 2.8.3    | Accurate Seconds/Daylight Savings Time/Time Zone   | 2-19 |

|   | 2.9  | FLEX (   | CAPCODE                                            | 2-21 |

|   |      | 2.9.1    | САРСОДЕ Туре                                       | 2-22 |

|   |      | 2.9.2    | Standard Frame and Phase Embedding Rule            | 2-23 |

|   |      | 2.9.3    | CAPCODE Alpha Character Definition                 | 2-24 |

|   |      | 2.9.4    | CAPCODE to Binary Conversion                       | 2-25 |

|   |      | 2.9.5    | Binary to CAPCODE Conversion                       | 2-26 |

|   |      | 2.9.6    | CAPCODE Assignments                                | 2-27 |

| 3 | TLV5 | 593VF F  | ELEX Decoder                                       | 3-1  |

| Č | 3.1  |          | es                                                 |      |

|   |      | 3.1.1    | Support                                            |      |

|   |      | 3.1.2    | Functional Description                             |      |

|   |      | 3.1.3    | Powerdown                                          |      |

|   |      | 3.1.4    | Terminal Functions                                 |      |

|   | 3.2  | SPI Pa   | ckets                                              | 3-6  |

|   |      | 3.2.1    | Packet Communication Initiated by the Host         | 3-6  |

|   |      | 3.2.2    | Packet Communication Initiated by the FLEX Decoder |      |

|   |      | 3.2.3    | Host-To-Decoder Packet Map                         |      |

|   |      | 3.2.4    | Decoder-To-Host Packet Map                         | 3-9  |

|   | 3.3  | Host-To  | o-Decoder Packet Descriptions                      | 3-10 |

|   |      | 3.3.1    | Checksum Packet                                    | 3-10 |

|   |      | 3.3.2    | Configuration Packet                               | 3-12 |

|   |      | 3.3.3    | Control Packet                                     | 3-14 |

|   |      | 3.3.4    | All Frame Mode Packet                              | 3-16 |

|   |      | 3.3.5    | Operator Messaging Address Enable Packet           | 3-17 |

|   |      | 3.3.6    | Roaming Control Packet                             | 3-17 |

|   |      | 3.3.7    | Timing Control Packet                              | 3-20 |

|   |      | 3.3.8    | Receiver Line Control Packet                       |      |

|   |      | 3.3.9    | Receiver Control Configuration Packets             |      |

|   |      | 3.3.10   | Receiver Off Setting Packet                        |      |

|   |      | 3.3.11   | Receiver Warm Up Setting Packets                   |      |

|   |      | 3.3.12   |                                                    |      |

|   |      |          | Receiver On Setting Packets                        |      |

|   |      |          | Receiver Shutdown Setting Packets                  |      |

|   |      |          | Frame Assignment Packets                           |      |

|   |      |          | User Address Enable Packet                         |      |

|   |      |          | User Address Assignment Packets                    |      |

|   | 3.4  |          | er-To-Host Packet Descriptions                     |      |

|   |      | 3.4.1    | Block Information Word Packet                      |      |

|   |      | 3.4.2    | Address Packet                                     |      |

|   |      | 3.4.3    | Vector Packet                                      |      |

|   |      | 3.4.4    | Message Packet                                     |      |

|   |      | 3.4.5    | Roaming Status Packet                              |      |

|   |      | 3.4.6    | Receiver Shutdown Packet                           |      |

|   |      | 3.4.7    | Status Packet                                      |      |

|   | 0 5  | 3.4.8    | Part ID Packet                                     |      |

|   | 3.5  | Electric | cal Characteristics                                | 3-42 |

|   | 3.6   | Receiver Control                                 |

|---|-------|--------------------------------------------------|

|   |       | 3.6.1 Receiver Settings at Reset 3-44            |

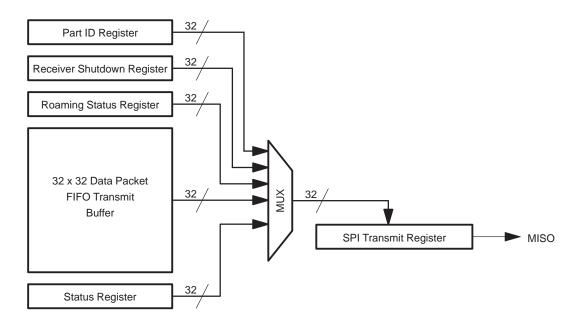

|   |       | 3.6.2 Automatic Receiver Warm-Up Sequence        |

|   |       | 3.6.3 Host-Initiated Receiver Warm-Up Sequence   |

|   |       | 3.6.4 Receiver Shut-Down Sequence                |

|   |       | 3.6.5 Miscellaneous Receiver States 3-46         |

|   |       | 3.6.6 Low Battery Detection                      |

|   | 3.7   | Message Building 3-48                            |

|   | 3.8   | Building a Fragmented Message 3-50               |

|   | 3.9   | Operation of a Temporary Address—Group Messaging |

|   | 3.10  | Using the Receiver Shutdown Packet 3-54          |

|   |       | 3.10.1 Calculating Remaining Time 3-54           |

|   |       | 3.10.2 Calculating Task Time 3-54                |

| Α | TLV5  | 5590 Data Sheet A-1                              |

| в | Timir | ng DiagramsB-1                                   |

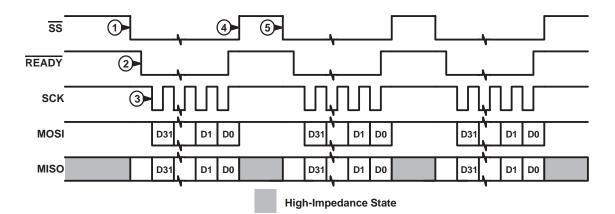

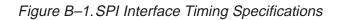

|   | B.1   | SPI Timing                                       |

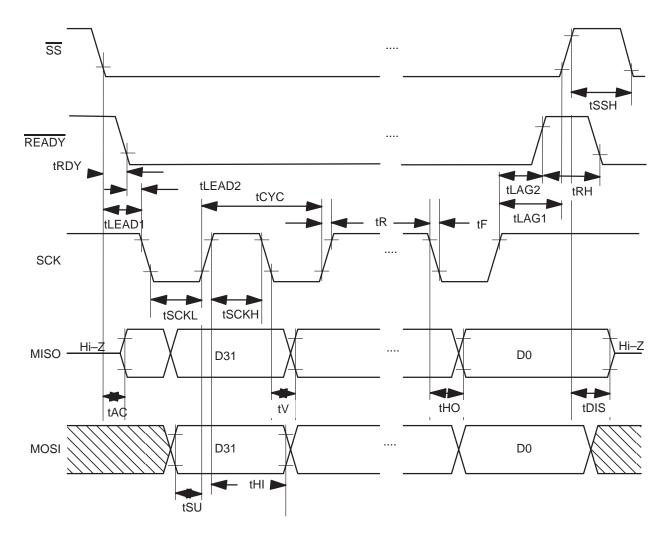

|   | B.2   | Startup Timing B-4                               |

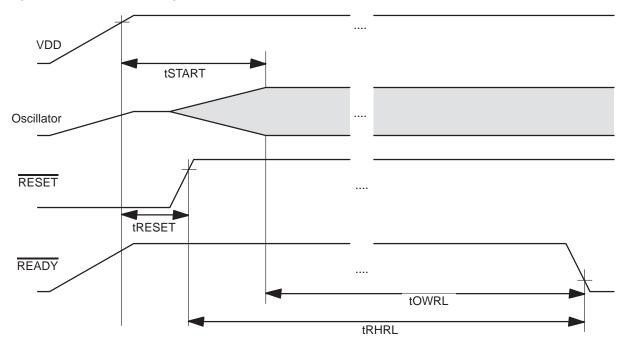

|   | B.3   | Reset Timing B-5                                 |

| С | Mech  | hanical Data C-1                                 |

## Figures

| 1–1  | FLEX Messaging Device 1-2                                                         |

|------|-----------------------------------------------------------------------------------|

| 2–1  | FLEX Signal Structure                                                             |

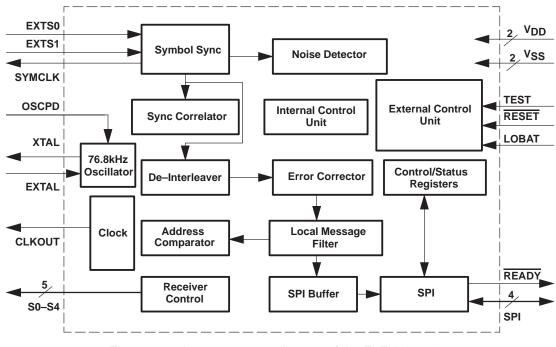

| 3–1  | Functional Block Diagram 3-3                                                      |

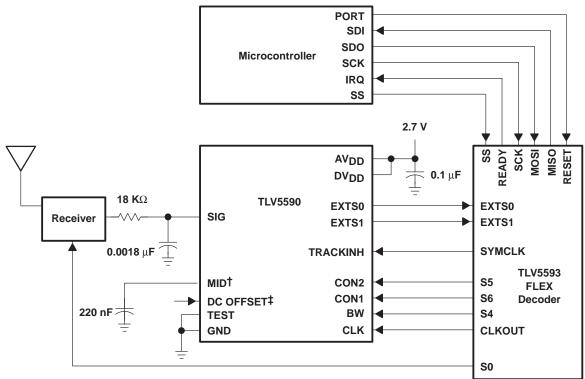

| 3–2  | System Diagram                                                                    |

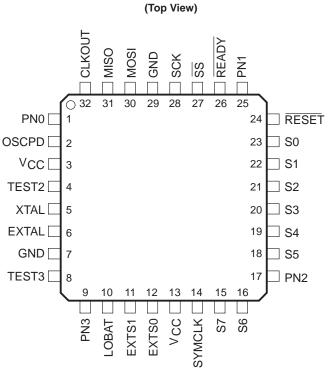

| 3–3  | Terminal Assignments 3-4                                                          |

| 3–4  | Typical Multiple Packet Communications Initiated by the Host                      |

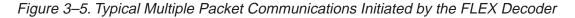

| 3–5  | Typical Multiple Packet Communications Initiated by the FLEX Decoder 3-7          |

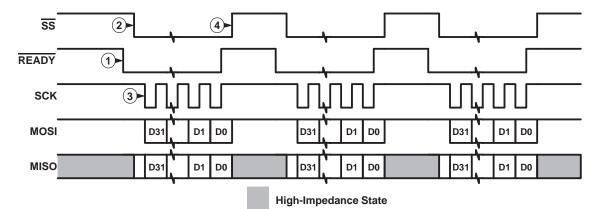

| 3–6  | Multiple Packet Communications Initiated by the FLEX Decoder With No Deselect 3-7 |

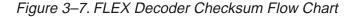

| 3–7  | FLEX Decoder Checksum Flow Chart 3-11                                             |

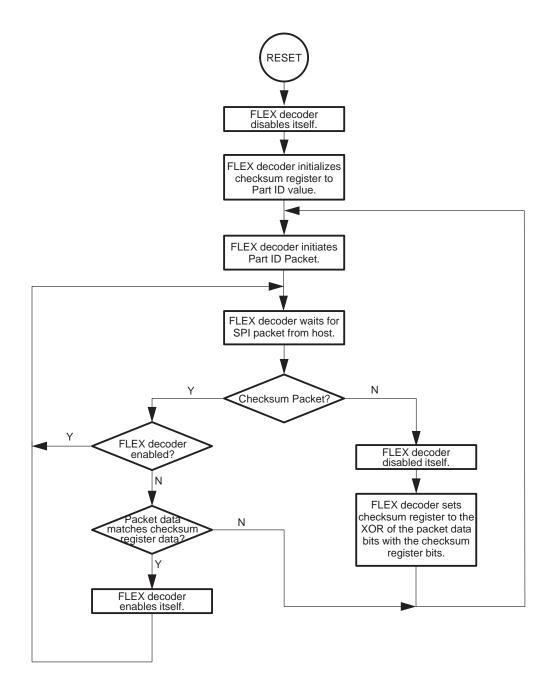

| 3–8  | FLEX Decoder SPI Transmit Functional Block Diagram 3-28                           |

| 3–9  | Automatic Warm-Up Sequence 3-45                                                   |

| 3–10 | Host-Initiated Warm-Up Sequence 3-45                                              |

| 3–11 | Receiver Shut-Down Sequence 3-46                                                  |

| 3–12 | Examples of Receiver Control Transitions 3-47                                     |

| B–1  | SPI Interface Timing Specifications B-2                                           |

| B–2  | Startup Timing B-4                                                                |

| B–3  | Reset Timing B-5                                                                  |

## **Tables**

| 2–1  | Standard (V = 011) or Special (V = 100)<br>Format: 4, 10, 15, 20, 25, 31, 36, or 41 Characters |

|------|------------------------------------------------------------------------------------------------|

| 2–2  | Numbered (V = 111) Format: 2, 8, 13, 18, 23, 29, 34, or 39 Numeric Characters 2-4              |

| 2-3  | Vector Type V = 110, First Only Fragment $\dots 2-6$                                           |

| 2-4  | Vector Type V =110, All Other Fragments                                                        |

| 2-5  | Vector Type V = 101, First Only Fragment                                                       |

| 2-6  | Vector Type V = 101, Other Fragment $2-9$                                                      |

| 2-7  | Vector Type V = 101, Other Fragment $2-12$                                                     |

| 2-8  | Vector Type V = 000, All Fragments                                                             |

| 2-9  | Alphanumeric Character Set                                                                     |

| 2–10 | Standard Character Set (Peoples Republic of China Option Off)                                  |

| 2–11 | Alternate Character Set (Peoples Republic of China Option On)                                  |

| 2–12 | Month/Day/Year Block Information Word Definition                                               |

| 2–13 | Second/Minute/Hour Block Information Word Definition                                           |

| 2–14 | System Message Block Information Word Definition                                               |

| 2–15 | Time Zone Values                                                                               |

| 2–16 | Address Word Range Definitions                                                                 |

| 2–17 | Long Address Sets                                                                              |

| 2–18 | FLEX CAPCODE Examples                                                                          |

| 2–19 | Alpha Character Codes                                                                          |

| 2–20 | CAPCODE Assignments                                                                            |

| 3–1  | Terminal Functions                                                                             |

| 3–2  | Host-To-Decoder Packet ID Map                                                                  |

| 3–3  | Decoder-To-Host Packet ID Map                                                                  |

| 3–4  | Checksum Packet Bit Assignments 3-12                                                           |

| 3–5  | Configuration Packet Bit Assignments 3-12                                                      |

| 3–6  | Oscillator Frequency Difference                                                                |

| 3–7  | Signal Polarity                                                                                |

| 3–8  | Control Packet Bit Assignments 3-14                                                            |

| 3–9  | Phase Select                                                                                   |

| 3–10 | All Frame Mode Packet Bit Assignments 3-16                                                     |

| 3–11 | System Address Enable Packet Bit Assignments 3-17                                              |

| 3–12 | Roaming Control Packet Bit Assignments 3-17                                                    |

| 3–13 | Missing Frame Data 3-20                                                                        |

| 3–14 | Timing Control Packet Bit Assignments 3-20                                                     |

| 3–15 | Receiver Line Control Packet Bit Assignments 3-21                                              |

| 3–16 | Receiver Off Setting Packet Bit Assignments 3-21                                               |

| 3–17 | Receiver Warm Up Setting Packet Bit Assignments 3-22                                           |

| 3–18 | Receiver Control Setting 3-22                                                                  |

| 3–19 | 3200 sps Sync Setting Packet Bit Assignments                                | 3-23 |

|------|-----------------------------------------------------------------------------|------|

| 3–20 | Receiver On Setting Packet Bit Assignments                                  | 3-23 |

| 3–21 | Receiver On Setting Names                                                   | 3-23 |

| 3–22 | Receiver Shut Down Setting Packet Bit Assignments                           | 3-24 |

| 3–23 | Receiver Shut Down Setting Names                                            | 3-24 |

| 3–24 | Frame Assignment Packet Bit Assignments                                     | 3-25 |

| 3–25 | Frame Range Packet Bit Assignments                                          | 3-25 |

| 3–26 | User Address Enable Packet Bit Assignments                                  | 3-26 |

| 3–27 | User Address Assignment Packet Bit Assignments                              | 3-26 |

| 3–28 | Block Information Word Packet Bit Assignments                               | 3-29 |

| 3–29 | Block Information Word Definitions                                          | 3-30 |

| 3–30 | Address Packet Bit Assignments                                              | 3-30 |

| 3–31 | Numeric Vector Packet Bit Assignments                                       |      |

| 3–32 | Numeric Vector Definitions                                                  |      |

| 3–33 | Short Message/Tone Only Vector Packet Bit Assignments                       | 3-33 |

| 3–34 | Short Message/Tone Only Vector Definitions                                  | 3-33 |

| 3–35 | Hex/Binary, Alphanumeric, and Secure Message Vector Packet Bit              |      |

|      | Assignments                                                                 |      |

| 3–36 | Vector Type Identifiers                                                     |      |

| 3–37 | Short Instruction Vector Packet Bit Assignments                             |      |

| 3–38 | Short Instruction Vector Definitions                                        |      |

| 3–39 | Message Packet Bit Assignments                                              |      |

| 3–40 | Roaming Status Packet Bit Assignments                                       |      |

| 3–41 | Noise Detection Results                                                     |      |

| 3–42 | Receiver Shutdown Packet Bit Assignments                                    |      |

| 3–43 | Status Packet Bit Assignments                                               |      |

| 3–44 | Part ID Packet Bit Assignments                                              |      |

| 3–45 | FLEX Decoder Revisions                                                      |      |

| 3–46 | Absolute Maximum Ratings Over Operating Temperature Ranges                  |      |

| 3–47 | Recommended Operating Conditions                                            |      |

| 3–48 | Electrical Characteristics Over Recommended Operating Conditions            |      |

| 3–49 | FLEX Signal                                                                 | 3-48 |

| 3–50 | FLEX Decoder Packet Sequence                                                | 3-49 |

| 3–51 | Alphanumeric Message Without Fragmentation                                  |      |

| 3–52 | Alphanumeric Message With Fragmentation                                     | 3-52 |

| B–1  | SPI Timing                                                                  |      |

| B–2  | Startup Timing (VDD = 1.8 V to 3.3 V, TA = $0^{\circ}$ C to $70^{\circ}$ C) |      |

| B–3  | Reset Timing (VDD = 1.8 V to 3.3 V, TA = $0^{\circ}$ C to $70^{\circ}$ C)   | B-5  |

|      |                                                                             |      |

### **Chapter 1**

## Introduction

The Texas Instruments (TI<sup>™</sup>) TMS320FLEX Family Chipset With Alphanumeric Roaming Decoder simplifies implementation of the FLEX<sup>™</sup> protocol in a messaging application by interfacing directly with most popular off-the-shelf messaging receivers and microcontrollers. You can quickly and easily develop a FLEX-compliant product by interfacing the TLV5590 converter and the TLV5593VF decoder to your existing receivers and microcontrollers with virtually no hardware redesign.

Purchase of the TMS320FLEX Family Chipset With Alphanumeric Roaming Decoder satisfies all licensing requirements for the FLEX protocol. No separate license agreement with Motorola is required.

#### Topic

| 1.1 | FLEX Messaging Overview 1-2 |  |

|-----|-----------------------------|--|

| 1.2 | Chipset Description 1-3     |  |

#### 1.1 FLEX Messaging Overview

FLEX messaging protocol was developed by Motorola to provide a robust form of text and data messaging not previously available. Figure 1–1 shows a block diagram of a FLEX messaging device. The FLEX protocol brings new levels of functionality and service to pagers while providing you with the following benefits:

- Longer battery life than existing standards

- Support for numeric and alphanumeric messages

- High signal integrity for error protection and positive message termination

- Advanced features, such as group pages between systems

- Support for 1600-, 3200-, or 6400-bps transmissions

- Low upgrade costs by allowing gradual migration from FLEX 1600 to FLEX 3200 to FLEX 6400

- Increased number of subscribers per channel, thereby reducing infrastructure costs

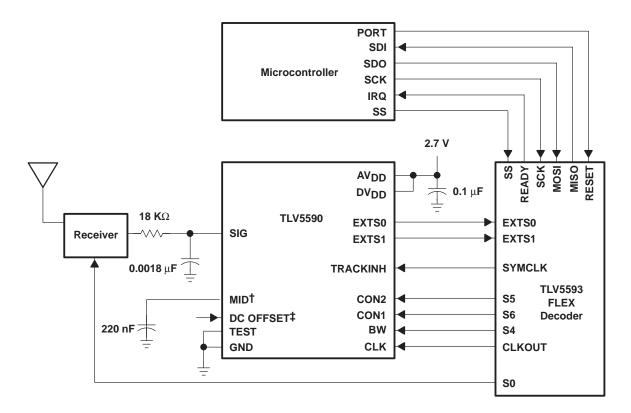

Figure 1–1. FLEX Messaging Device

<sup>†</sup> The voltage on the MID terminal is nominally AV<sub>DD</sub>/2.

<sup>‡</sup>The voltage applied to the DC OFFSET terminal is set to the dc offset voltage of the input signal applied to the SIG terminal.

#### 1.2 Chipset Description

The TMS320FLEX Family Chipset with Numeric Decoder consists of a TLV5593VF signal processor that decodes the FLEX messaging protocol transmission and the TLV5590 analog-to-digital (A/D) converter that converts the analog signal from the receiver into a digital signal for decoding by the TLV5593VF. FLEXstack<sup>™</sup> system software to facilitate application development is also included. This software runs on a host processor and is specifically designed to support the TLV5593VF FLEX roaming decoder. It handles communications with the TLV5593VF decoder.

The flexible architecture of the TMS320FLEX chipset offers a variety of possibilities in application design.

#### 1.2.1 TLV5593VF FLEX Roaming Decoder

The TLV5593VF FLEX roaming decoder has the following features:

- FLEX messaging protocol signal processor

- □ 16 programmable user-address words

- □ 16 fixed temporary addresses

- □ 16 operator messaging addresses

- Decoding at 1600, 3200, or 6400 bps

- Any-phase or single-phase decoding

- Standard serial peripheral interface (SPI) in slave mode

- Low-current STOP mode operation of host processor

- Highly programmable receiver control

- Real-time clock time base

- □ FLEX fragmentation and group messaging support

- Real-time clock over-the-air update support

- Compatibility with synthesized receivers

- SSID and NID roaming support

- Low battery indication (external detector)

- □ 28 used pins (32-pin package standard)

- Pin-compatible with all other FLEX decoder signal processors

#### 1.2.2 TLV5590 A/D Converter

The TLV5590 A/D converter has the following features:

- Selectable dual-bandwidth audio filter

- Three-pole Butterworth low-pass

- BW 1 = 1 KHz +/-5% (-3 db)

- BW 2 = 2 KHz +/-5% (-3 db)

- Peak and valley detectors

- □ Two-bit A/D converter

- Four modes of operation: fast track, slow track, hold, and standby

- Operation at 2.7-V to 3.3-V with a single power supply

See Appendix A, TLV5590 Data Sheet, for more information.

### **Chapter 2**

## **FLEX Signal Structure**

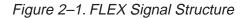

The FLEX signal transmitted on the radio channel consists of a series of four-minute cycles, each cycle having 128 frames at 1.875 seconds per frame. A pager may be assigned to process any number of the frames. Battery saving is performed for frames that are not assigned. The FLEX signal can assign additional frames to the pager using collapse, fragmentation, temporary addressing, or carry-on information within the FLEX signal. This chapter discusses the FLEX signal structure.

#### Topic

#### Page

| 2.1 | Synchronization                       |

|-----|---------------------------------------|

| 2.2 | FLEX Message Word Definitions 2-4     |

| 2.3 | Hex/Binary Message 2-6                |

| 2.4 | Alphanumeric Message 2-9              |

| 2.5 | Secure Message 2-13                   |

| 2.6 | FLEX Encoding and Decoding Rules 2-15 |

| 2.7 | FLEX Character Sets and Rules 2-17    |

| 2.8 | FLEX Local Time and Date 2-19         |

| 2.9 | FLEX CAPCODE 2-21                     |

|     |                                       |

#### 2.1 Synchronization

Figure 2–1 shows the FLEX signal structure.

Each FLEX frame has a synchronization portion followed by an 11-block data portion, each block lasting 160 milliseconds. The synchronization portion indicates the rate at which the data portion is transmitted, 1600, 3200, or 6400 bits per second (bps). The 1600 bps rate is transmitted at 1600 symbols per second (sps) using 2-level frequency shift key (FSK) modulation and consists of a single phase of information at 1600 bps called *phase A*. The 3200 bps rate is transmitted at either 1600 sps using 4-level FSK modulation or 3200 sps using 2-level FSK modulation and consists of two concurrent phases of information at 1600 bps called *phase B*. The 6400 bps rate is transmitted at 3200 sps using 4-level FSK modulation and consists of four concurrent phases of information at 1600 bps called *phase A* and *phase B*. The 6400 bps rate is transmitted at 3200 sps using 4-level FSK modulation and consists of four concurrent phases of information at 1600 bps called *phase A* and *phase B*. The 6400 bps rate is transmitted at 3200 sps using 4-level FSK modulation and consists of four concurrent phases of information at 1600 bps called *phase A* and *phase B*. The 6400 bps rate is transmitted at 3200 sps using 4-level FSK modulation and consists of four concurrent phases of information at 1600 bps called *phase A*, *phase B*, *phase C*, and *phase D*.

Each block has eight interleaved words per phase; there are eighty-eight words, numbered 0-87, per phase in every frame. Each word has information contained within an error correcting code that allows for bit error correction and detection. The eighty-eight words in each phase are organized into a block information field, an address field, a vector field, a message field, and an idle field. The boundaries between the fields are independent of the block boundaries. Furthermore, at 3200 and 6400 bps, the information in one phase is independent of the information in a concurrent phase, and the boundaries between the fields in a concurrent phase.

The synchronization portion consists of a first sync signal at 1600 bps; a Frame Information Word having the Frame Number 0 - 127 (7 bits) and the Cycle Number 0 - 14 (4 bits); and a second sync signal at the data rate of the interleaved portion.

#### 2.1.1 Block Information Field

The block information field may contain block information words for determining time and date information and certain paging system information.

#### 2.1.2 Address Field

The address field contains addresses assigned to paging devices. Addresses are used to identify information sent to individual paging devices and/or groups of paging devices. An address may be either a short one-word address or a long two-word address. Information in the FLEX signal may indicate that an address is a priority address. An address may be a *tone-only* address in which case there is no additional information associated with the address. If an address is not a tone-only address, then there is an associated vector word in the vector field. Information in the FLEX signal indicates the location of the vector word in the vector field associated with the address. Short addresses have one associated vector word, and long addresses have two associated vector words. A pager may battery save at the end of the address field when its address is not detected.

#### 2.1.3 Vector Field

The vector field consists of a series of vector words. Depending upon the type of message, a vector word (or words in the case of a long address) may either contain all of the information necessary for the message, or indicate the location of message words in the message field comprising the message information.

#### 2.1.4 Message Field

The message field consists of a series of information words containing message information. The message information may be formatted in ASCII, binary coded decimal (BCD), or binary, depending upon the message type.

#### 2.2 FLEX Message Word Definitions

FLEX message word definitions are discussed in this section.

#### 2.2.1 Numeric Data Message

Table 2–1 and Table 2–2 describe the bit format of the numeric messages. The 4-bit numeric characters of the message are designated as lowercase letters a, b, c, d, etc.

Table 2–1. Standard (V = 011) or Special (V = 100) Format: 4, 10, 15, 20, 25, 31, 36, or 41 Characters

| Message Word | i0             | i1             | i2             | i3             | i4             | i5             | i6             | i7             | ig             | ig             | <sup>i</sup> 10 | <sup>i</sup> 11 | i12            | i13            | i14            | i15            | <sup>i</sup> 16 | İ17            | i18            | i19            | i <sub>20</sub> |

|--------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|-----------------|-----------------|----------------|----------------|----------------|----------------|-----------------|----------------|----------------|----------------|-----------------|

| 1st          | K4             | К <sub>5</sub> | a0             | a <sub>1</sub> | a2             | аз             | b0             | b <sub>1</sub> | b2             | b3             | c0              | c1              | c2             | сз             | d <sub>0</sub> | d <sub>1</sub> | d2              | d3             | e0             | e <sub>1</sub> | e2              |

| 2nd          | e3             | f <sub>0</sub> | f1             | f <sub>2</sub> | f3             | 90             | 91             | g2             | <b>9</b> 3     | hŋ             | h <sub>1</sub>  | h <sub>2</sub>  | hȝ             | i0             | i1             | i2             | iз              | jo             | j1             | j2             | jз              |

| 3rd          | k <sub>0</sub> | k <sub>1</sub> | k <sub>2</sub> | k3             | 1 <sub>0</sub> | I <sub>1</sub> | $I_2$          | l <sub>3</sub> | m <sub>0</sub> | m <sub>1</sub> | m2              | m3              | n <sub>0</sub> | n <sub>1</sub> | n <sub>2</sub> | n <sub>3</sub> | o <sub>0</sub>  | °1             | °2             | 03             | 90              |

| 4th          | 91             | q2             | q3             | r <sub>0</sub> | r <sub>1</sub> | r <sub>2</sub> | rз             | s <sub>0</sub> | s <sub>1</sub> | s <sub>2</sub> | sვ              | to              | t <sub>1</sub> | t2             | t3             | u0             | u1              | u <sub>2</sub> | uз             | v <sub>0</sub> | ٧1              |

| 5th          | v2             | ٧3             | wo             | W1             | w2             | wз             | УО             | У1             | У2             | УЗ             | z <sub>0</sub>  | z1              | z2             | z3             | A <sub>0</sub> | A <sub>1</sub> | A <sub>2</sub>  | A <sub>3</sub> | B <sub>0</sub> | В <sub>1</sub> | B <sub>2</sub>  |

| 6th          | B3             | C <sub>0</sub> | C <sub>1</sub> | C2             | C <sub>3</sub> | D <sub>0</sub> | $D_1$          | D <sub>2</sub> | D3             | E <sub>0</sub> | E <sub>1</sub>  | E <sub>2</sub>  | E3             | F <sub>0</sub> | F <sub>1</sub> | F <sub>2</sub> | F3              | G <sub>0</sub> | G <sub>1</sub> | G <sub>2</sub> | G3              |

| 7th          | H <sub>0</sub> | H <sub>1</sub> | H <sub>2</sub> | H <sub>3</sub> | I <sub>0</sub> | $I_1$          | I <sub>2</sub> | lз             | J <sub>0</sub> | J <sub>1</sub> | J <sub>2</sub>  | J3              | V <sub>0</sub> | $V_1$          | $V_2$          | V <sub>3</sub> | L <sub>0</sub>  | L <sub>1</sub> | L <sub>2</sub> | L <sub>3</sub> | M <sub>0</sub>  |

| 8th          | M <sub>1</sub> | M2             | M <sub>3</sub> | 00             | 01             | 02             | 03             | P <sub>0</sub> | P1             | P2             | P <sub>3</sub>  | Q <sub>0</sub>  | Q <sub>1</sub> | Q <sub>2</sub> | Q3             | T <sub>0</sub> | T <sub>1</sub>  | Т2             | Тз             | U <sub>0</sub> | U <sub>1</sub>  |

Table 2–2. Numbered (V = 111) Format: 2, 8, 13, 18, 23, 29, 34, or 39 Numeric Characters

| Message Word | i0             | i1             | i2             | i3             | i4             | i5             | i <sub>6</sub> | i7             | i8             | ig             | <sup>i</sup> 10 | i11            | i12            | i <sub>13</sub> | i14            | i <sub>15</sub> | <sup>i</sup> 16 | i17            | i <sub>18</sub> | i19            | i <sub>20</sub> |

|--------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|-----------------|----------------|----------------|-----------------|----------------|-----------------|-----------------|----------------|-----------------|----------------|-----------------|

| 1st          | K4             | K5             | N <sub>0</sub> | N1             | $N_2$          | N <sub>3</sub> | N4             | $N_5$          | R <sub>0</sub> | S <sub>0</sub> | a <sub>0</sub>  | a <sub>1</sub> | a2             | аз              | b0             | b <sub>1</sub>  | b2              | b3             | c0              | c <sub>1</sub> | c <sub>2</sub>  |

| 2nd          | сз             | d <sub>0</sub> | d <sub>1</sub> | d2             | d3             | e0             | e <sub>1</sub> | e2             | ез             | f <sub>0</sub> | f <sub>1</sub>  | f2             | f3             | <b>g</b> 0      | 91             | g2              | <b>g</b> 3      | hŋ             | h <sub>1</sub>  | h <sub>2</sub> | hვ              |

| 3rd          | i <sub>0</sub> | i <sub>1</sub> | i2             | iз             | jo             | j1             | j2             | jз             | k <sub>0</sub> | k <sub>1</sub> | k <sub>2</sub>  | kз             | I <sub>0</sub> | I <sub>1</sub>  | $I_2$          | lз              | m <sub>0</sub>  | m <sub>1</sub> | m <sub>2</sub>  | m3             | no              |

| 4th          | n <sub>1</sub> | n <sub>2</sub> | n3             | 00             | <sup>0</sup> 1 | 02             | 03             | 90             | <b>q</b> 1     | q2             | q3              | r <sub>0</sub> | r <sub>1</sub> | r <sub>2</sub>  | rз             | s <sub>0</sub>  | s <sub>1</sub>  | s <sub>2</sub> | s3              | t <sub>0</sub> | t <sub>1</sub>  |

| 5th          | t2             | t3             | u0             | u1             | u2             | uз             | v <sub>0</sub> | V1             | v <sub>2</sub> | ٧3             | w <sub>0</sub>  | W1             | w <sub>2</sub> | w3              | УО             | У1              | У2              | УЗ             | z <sub>0</sub>  | z1             | z2              |

| 6th          | z3             | A <sub>0</sub> | A <sub>1</sub> | A <sub>2</sub> | A3             | B <sub>0</sub> | В <sub>1</sub> | B2             | B3             | C <sub>0</sub> | C <sub>1</sub>  | C2             | C <sub>3</sub> | D <sub>0</sub>  | $D_1$          | D <sub>2</sub>  | D3              | E <sub>0</sub> | E <sub>1</sub>  | E <sub>2</sub> | E3              |

| 7th          | F <sub>0</sub> | F <sub>1</sub> | F <sub>2</sub> | F <sub>3</sub> | G <sub>0</sub> | G <sub>1</sub> | G <sub>2</sub> | G <sub>3</sub> | H <sub>0</sub> | H <sub>1</sub> | H <sub>2</sub>  | H <sub>3</sub> | I <sub>0</sub> | I <sub>1</sub>  | I <sub>2</sub> | l <sub>3</sub>  | J <sub>0</sub>  | J <sub>1</sub> | J <sub>2</sub>  | J3             | V               |

| 8th          | V <sub>1</sub> | V <sub>2</sub> | V <sub>3</sub> | L <sub>0</sub> | L <sub>1</sub> | L <sub>2</sub> | L <sub>3</sub> | M <sub>0</sub> | M1             | M2             | M <sub>3</sub>  | 00             | 01             | 02              | 03             | P <sub>0</sub>  | P1              | P2             | P3              | Q <sub>0</sub> | Q <sub>1</sub>  |

#### 2.2.2 Bit Definitions

**K**:

6-bit Message Check Character (First 4 bits are in the vector word). This check character is calculated by initializing the message check character (K) to zero and summing the information bits of each code word in the message, (including control information and termination characters and bits in the last message word) to a check sum register. The information bits of each word are broken into three groups: bits i<sub>0</sub> through i<sub>7</sub>, bits i<sub>8</sub> through i<sub>15</sub>, and bits i<sub>16</sub> through i<sub>20</sub>. Bits i<sub>0</sub>, i<sub>8</sub> and i<sub>16</sub> are the LSBs of each group. The binary sum is calculated and the result is shortened to the 8 least significant bits. The 2 most significant 6 bits to form a new sum. This resultant sum is 1's complemented with the 6 LSBs of the result being transmitted as the message check character.

- N: Message Number: When the system supports message retrieval, the system controller assigns message numbers (for each paging address separately) starting at 0 and progressing to a maximum of 63 in consecutive order. The actual maximum roll-over number is defined in the pager code plug to accommodate values set in the system infrastructure. When message numbers are not received in order, the subscriber should assume a message has been missed. The subscriber or the pager may determine the missing message number(s) by allowing a request to be made for retrieval. When a normal unnumbered numeric message is received (Message Retrieval Flag is equal to 0), it is not included in the missed message calculation.

- R: Message Retrieval Flag: When this bit is set to 1, the pager expects to see messages numbered in order (each address numbered separately). Detection of a missing number indicates a missed message. A message received with R = 0 is allowed to be out of order and does not cause the pager to indicate that a message has been missed.

- **S**: Special Format: In the numbered message format, this bit set to 1 indicates that a special display format should be used.

#### 2.2.3 Message Fill Rules

For numeric messages of 36 characters or less (34 characters if numbered), fewer than 8 code words on the channel are required. Only code words containing the numeric message can be transmitted. The space character (hexadecimal C) should be used to fill any unused 4-bit characters in the last word, and zeros should be read to fill any remaining partial characters. The check sum is correspondingly shortened to include only the code words comprising the shortened message along with the space and fill characters used to fill in the last word.

#### 2.2.4 Special Format Numeric

Spaces and dashes as specified by the host are inserted into the received message. This feature in certain markets saves the transmission of an additional word on the channel. For example, in the U.S. market a 10-character format (area code plus telephone number) fits into two message words. If the dashes or parentheses are included in the message, three message words on the channel are required. The actual placement can be programmed into the paging device and can vary between markets.

#### 2.3 Hex/Binary Message

Table 2–3 and Table 2–4 describe the bit format of the Hex/Binary messages. The data of the message is designated as lowercase letters a, b, c, d, etc. Hex/ Binary messages can be sent as fragments. The service provider has the option of dividing the message into several pieces and sending the separate pieces at any time within a given time period.

| Message Word | i0             | i1             | i2             | i3             | i4             | i5             | i6             | i7             | i8             | ig             | i10             | i11            | i12            | i <sub>13</sub>  | i14            | i15            | <sup>i</sup> 16 | i17            | i <sub>18</sub> | i <sub>19</sub> | i <sub>20</sub> |

|--------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|-----------------|----------------|----------------|------------------|----------------|----------------|-----------------|----------------|-----------------|-----------------|-----------------|

| 1st          | K <sub>0</sub> | K <sub>1</sub> | K <sub>2</sub> | K3             | K4             | K5             | K <sub>6</sub> | K7             | K <sub>8</sub> | Kg             | K <sub>1(</sub> | )K₁∕           | C <sub>0</sub> | F <sub>0</sub> F | -1             | N <sub>0</sub> | N <sub>1</sub>  | N <sub>2</sub> | N <sub>3</sub>  | N4              | $N_5$           |

| 2nd          | R <sub>0</sub> | Mo             | D <sub>0</sub> | H <sub>0</sub> | в0             | В <sub>1</sub> | B <sub>2</sub> | Вз             | s <sub>0</sub> | s <sub>1</sub> | s2              | sვ             | s4             | S <sub>0</sub>   | s <sub>1</sub> | S <sub>2</sub> | S3              | S4             | S5              | S <sub>6</sub>  | S7              |

| 3rd          | a <sub>0</sub> | a <sub>1</sub> | a <sub>2</sub> | a3             | b <sub>0</sub> | b <sub>1</sub> | b <sub>2</sub> | b3             | c0             | с <sub>1</sub> | c <sub>2</sub>  | сз             | d <sub>0</sub> | d <sub>1</sub>   | d <sub>2</sub> | d3             | e <sub>0</sub>  | e <sub>1</sub> | e <sub>2</sub>  | e3              | f <sub>0</sub>  |

| 4th          | f <sub>1</sub> | f <sub>2</sub> | fз             | 90             | <b>9</b> 1     | g2             | <b>g</b> 3     | h <sub>0</sub> | h <sub>1</sub> | h2             | hȝ              | i0             | i1             | i2               | iз             | j0             | j1              | j2             | jз              | k <sub>0</sub>  | k <sub>1</sub>  |

| 5th          | k <sub>2</sub> | kз             | I <sub>0</sub> | I <sub>1</sub> | $I_2$          | lз             | m <sub>0</sub> | m <sub>1</sub> | m <sub>2</sub> | m3             | n <sub>0</sub>  | n <sub>1</sub> | n <sub>2</sub> | ng               | o0             | °1             | 02              | 03             | q0              | 91              | q2              |

| 6th          | 93             | r0             | r1             | r <sub>2</sub> | rз             | s0             | s <sub>1</sub> | s2             | sვ             | t <sub>0</sub> | t <sub>1</sub>  | t2             | t3             | u0               | u <sub>1</sub> | u2             | uз              | v0             | ٧1              | v <sub>2</sub>  | v3              |

|              |                |                |                |                |                |                |                |                |                |                |                 |                |                |                  |                |                |                 |                |                 |                 |                 |

| nth          | i              | i              | i              | i              | i              | i              | i              | i              | i              | i              | i               | i              | i              | i                | i              | i              | i               | i              | i               | i               | i               |

Table 2–3. Vector Type V = 110, First Only Fragment

Table 2–4. Vector Type V = 110, All Other Fragments

| Message Word | i0             | i1             | i2             | i3             | i4             | i5             | i6             | i7             | i8             | ig             | i10             | <sup>i</sup> 11 | i12              | i <sub>13</sub> | i14            | i15            | i16            | i17            | i18            | i <sub>19</sub> | i <sub>20</sub> |

|--------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|-----------------|-----------------|------------------|-----------------|----------------|----------------|----------------|----------------|----------------|-----------------|-----------------|

| 1st          | κ <sub>0</sub> | K <sub>1</sub> | K <sub>2</sub> | K3             | K4             | К <sub>5</sub> | K <sub>6</sub> | K7             | K <sub>8</sub> | Kg             | K <sub>1(</sub> | 0K1             | 1 <sup>C</sup> 0 | F <sub>0</sub>  | $F_1$          | N <sub>0</sub> | N <sub>1</sub> | N <sub>2</sub> | N <sub>3</sub> | N <sub>4</sub>  | N <sub>5</sub>  |

| 2nd          | a <sub>0</sub> | a <sub>1</sub> | a <sub>2</sub> | a3             | b <sub>0</sub> | b <sub>1</sub> | b <sub>2</sub> | b3             | c0             | <sup>c</sup> 1 | <sup>c</sup> 2  | сз              | d <sub>0</sub>   | d <sub>1</sub>  | d <sub>2</sub> | d3             | e <sub>0</sub> | e <sub>1</sub> | e <sub>2</sub> | e3              | f <sub>0</sub>  |

| 3rd          | f <sub>1</sub> | f2             | f3             | 90             | 91             | 92             | <b>9</b> 3     | h <sub>0</sub> | h <sub>1</sub> | h2             | hȝ              | i0              | i1               | i2              | iз             | j0             | j1             | j2             | jз             | k <sub>0</sub>  | k <sub>1</sub>  |

| 4th          | k <sub>2</sub> | kз             | I <sub>0</sub> | $I_1$          | $I_2$          | lз             | m <sub>0</sub> | m <sub>1</sub> | m <sub>2</sub> | mз             | n <sub>0</sub>  | n <sub>1</sub>  | n <sub>2</sub>   | ng              | 00             | 01             | 02             | 03             | 90             | <b>q</b> 1      | q <sub>2</sub>  |

| 5th          | q3             | r <sub>0</sub> | r <sub>1</sub> | r <sub>2</sub> | r <sub>3</sub> | s <sub>0</sub> | s <sub>1</sub> | s <sub>2</sub> | s3             | t <sub>0</sub> | t <sub>1</sub>  | t2              | t3               | u <sub>0</sub>  | u <sub>1</sub> | u <sub>2</sub> | uз             | v <sub>0</sub> | V1             | v <sub>2</sub>  | v <sub>3</sub>  |

|              |                |                |                |                |                |                |                |                |                |                |                 |                 |                  |                 |                |                |                |                |                |                 |                 |

| nth          | i              | i              | i              | i              | i              | i              | i              | i              | i              | i              | i               | i               | i                | i               | i              | i              | i              | i              | i              | i               | i               |

#### 2.3.1 Bit Definitions

- **K**:

- 12-bit Fragment Check Sum. This Check Sum is calculated by initializing the Fragment Check Sum field (K) to zero and calculating a sum over the information bits of each code word in the message fragment (including control information and termination characters/bits in the last fragment word). This sum requires that the information bits of each word be broken into three groups: the first is the 8 bits comprising i<sub>0</sub> through i<sub>7</sub>, the second group comprises bits i<sub>8</sub> through i<sub>15</sub>, and the third group comprises bits i<sub>16</sub> through i<sub>20</sub>. Bits i<sub>0</sub>, i<sub>8</sub> and i<sub>16</sub> are the LSBs of each group. The binary sum is calculated over all code words in the fragment, the 1's complement of the sum is determined, and the 12 LSBs of the result is placed into the Fragment Check Sum field to be transmitted at the beginning of the fragment.

- **C**: 1-bit Message Continued Flag. When set to 1, indicates fragments of this message are to be expected in any or possibly all of the following frames until a fragment with C = 0 is found. The longest message which will fit into a frame is 84 code words total. Three alpha characters per word yields a maximum message of 252 characters in a frame, assuming no other traffic. Messages longer than this value must be sent as several fragments.

- F: 2-bit Message Fragment Number. This is a modulo 3 message fragment number which is incremented by 1 in successive message fragments. The initial fragment starts at 11 and each following fragment is incremented by 1 modulo 3. (11, 00, 01, 10, 00, 01, 10, 00 etc.). The 11 state (after the initial fragment) is skipped in this process to avoid confusion with the single fragment of a non-continued message. The final fragment is indicated by the Message Continued Flag being reset to 0.

- N: Message Number. When the system supports message retrieval, the system controller assigns message numbers (for each paging address separately) starting at 0 and progressing up to a maximum of 63 in consecutive order. The actual maximum rollover number is defined in the pager code plug to accommodate values set in the system infrastructure. When message numbers are not received in order, the subscriber should assume a message has been missed. The subscriber or the pager may determine the missing message number(s) allowing a request to be made for retrieval. When a normal unnumbered numeric message is received (message retrieval flag is equal to 0), it is not to be included in the missed message calculation. This number is also used to identify fragments of the same message. Multiple messages to the same address must have separate message numbers. An exception to this rule is the header message tied to a transparent message each with the same message number.

- R: Message Retrieval Flag. When this bit is set to 1, the pager expects to see messages numbered in order (each address numbered separately). Detection of a missing number indicates a missed message. A message received with R = 0 is allowed to be out of order and does not cause the pager to indicate that a message has been missed.

- M: 1-bit Mail Drop Flag. When set to 1, indicates the message is to be stored in a special area in memory. It automatically writes over existing data in that memory space.

- **D**: 1-bit Display Direction Field. D = 0 Display left to right, D = 1 Display right to left (valid only when data is sent as characters, i.e., Blocking Length not equal 0001).

- **H**: 1-bit Header Message. H = 1 Indicates that this message is a header to a following transparent message of the same message number. H = 0 implies message is not a header.

- **B**: 4-bit Blocking Length. Indicates bits per character.  $B_3B_2B_1B_0 = 0001$ = 1 bit per character (binary/transparent data), 1111 =15 bits per character, 0000 =16 bits per character. Data with blocking length other than 1 is assumed to be displayed on a character by character basis. (default value = 0001). Note that the above figures show B = 4-bit blocking length.

- s: 5-bit Field Reserved for future use. Default value = 00000

- S: 8-bit Signature Field. The signature is defined to be the 1's complement of the binary sum over the total message taken 8 bits at a time prior to formatting into fragments. It would be equivalent to a binary sum starting with the first 8 bits directly following the signature field (b<sub>3</sub>b<sub>2</sub>b<sub>1</sub>b<sub>0</sub>a<sub>3</sub>a<sub>2</sub>a<sub>1</sub>a<sub>0</sub> + d<sub>3</sub>d<sub>2</sub>d<sub>1</sub>d<sub>0</sub>c<sub>3</sub>c<sub>2</sub>c<sub>1</sub>c<sub>0</sub> and so on.) and continuing all the way to the last valid data bit in the last word of the last fragment. The 8 least significant bits of the result are inverted (1's complement) and transmitted as the message signature. (Note: This sum does not include any termination bits and should be calculated directly on the message as received by the terminal. The device generating the signature should be able to calculate this sum before the fragmenting boundaries are determined.)

Fields R through S are only transmitted in the first fragment of a message. The fields K through N make up the first word of every fragment in a long message.

#### 2.3.2 Message Content

Starting with the first character of the third word in the message (second word in the remaining fragments), each 4-bit field represents 1 of any of the 16 possible combinations with no restrictions (data may be binary).

#### 2.3.3 Fragment Termination

Unused bits in the last message word of a fragment are filled with all 0's or all 1's depending on the last valid data bit. This choice is always the opposite polarity of the last valid data bit. For first fragments and inner fragments of a multifragment message, the message is interrupted (stopped) on the last full character boundary in the last code word in the fragment. Any unused bits follow this rule. The final fragment follows the above rules except when the last character is all 1's or all 0's and it exactly fills the last code word. In this case, an additional word must be sent of opposite polarity of all 1's or all 0's to signify the position of the last character thus allowing that last character to be an all 1's or an all 0's character pattern. (This is always the case when a binary message ends in the last bit of the last word.)

#### 2.3.4 Message Header

A message header is designated by setting the H bit to 1. This is a displayable tag associated with a transparent/non-displayable data message. The tag and the associated message are complete in themselves. The pager associates the header message with the data file based on the two having the same message number and being sent in sequence (header first followed by data file).

#### 2.4 Alphanumeric Message

Table 2–5 and Table 2–6 describe the bit format of the alphanumeric messages. The 7-bit characters of the message are designated as lowercase letters a, b, c, d, etc. Alphanumeric Messages can be sent as fragments. The service provider has the option of dividing the message into several pieces and sending the separate pieces at any time within a given time period.

| Message Word | i <sub>0</sub> | i <sub>1</sub> | i <sub>2</sub> | i3 | i4             | i5         | i <sub>6</sub> | i7             | i <sub>8</sub> | ig             | <sup>i</sup> 10 | <sup>i</sup> 11 | <sup>i</sup> 12 | i <sub>13</sub> | i <sub>14</sub> | i <sub>15</sub> | i <sub>16</sub> | i <sub>17</sub> | i <sub>18</sub> | i <sub>1</sub> 9 | <sup>i</sup> 20 |

|--------------|----------------|----------------|----------------|----|----------------|------------|----------------|----------------|----------------|----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|------------------|-----------------|

| 1st          | K <sub>0</sub> | K <sub>1</sub> | K <sub>2</sub> | K3 | K4             | К <u>5</u> | K <sub>6</sub> | K7             | K8             | Kg             | C <sub>0</sub>  | F <sub>0</sub>  | $F_1$           | N <sub>0</sub>  | N <sub>1</sub>  | N <sub>2</sub>  | N3              | N4              | N <sub>5</sub>  | R <sub>0</sub>   | M <sub>0</sub>  |

| 2nd          | s <sub>0</sub> | s <sub>1</sub> | s <sub>2</sub> | S3 | s <sub>4</sub> | S5         | S <sub>6</sub> | a <sub>0</sub> | a <sub>1</sub> | a <sub>2</sub> | aз              | a <sub>4</sub>  | a5              | a <sub>6</sub>  | b <sub>0</sub>  | b <sub>1</sub>  | b <sub>2</sub>  | b3              | b4              | b5               | b <sub>6</sub>  |

| 3rd          | c0             | c1             | c2             | сз | с4             | c5         | c6             | d <sub>0</sub> | d <sub>1</sub> | d <sub>2</sub> | dз              | d4              | d5              | d <sub>6</sub>  | e0              | e <sub>1</sub>  | e2              | ез              | e4              | e5               | e <sub>6</sub>  |

| 4th          | f <sub>0</sub> | f <sub>1</sub> | f <sub>2</sub> | fз | f4             | f5         | f <sub>6</sub> | 90             | <b>9</b> 1     | 92             | 93              | <u>9</u> 4      | 95              | 96              | h <sub>0</sub>  | h <sub>1</sub>  | h2              | hȝ              | h4              | h5               | h <sub>6</sub>  |

| 5th          | i <sub>0</sub> | i1             | i2             | iз | i4             | i5         | i <sub>6</sub> | jo             | j1             | j2             | jз              | j4              | j5              | j6              | k <sub>0</sub>  | k <sub>1</sub>  | k2              | kз              | k4              | k5               | k <sub>6</sub>  |

|              |                |                |                |    |                |            |                |                |                |                |                 |                 |                 |                 |                 |                 |                 |                 |                 |                  |                 |

| nth          | i              | i              | i              | i  | i              | i          | i              | i              | i              | i              | i               | i               | i               | i               | i               | i               | i               | i               | i               | i                | i               |

Table 2–5. Vector Type V = 101, First Only Fragment

Table 2–6. Vector Type V = 101, Other Fragment

| Message Word | i0             | i1             | i2             | i3         | i4             | i5 | i <sub>6</sub> | i7             | i8             | ig             | i10            | i11            | i <sub>12</sub> | i <sub>13</sub> | i14            | i15            | i16            | i17            | i <sub>18</sub> | i <sub>19</sub> | i <sub>20</sub> |

|--------------|----------------|----------------|----------------|------------|----------------|----|----------------|----------------|----------------|----------------|----------------|----------------|-----------------|-----------------|----------------|----------------|----------------|----------------|-----------------|-----------------|-----------------|

| 1st          | K <sub>0</sub> | K <sub>1</sub> | K <sub>2</sub> | Кз         | K4             | K5 | K <sub>6</sub> | K7             | K8             | Kg             | C <sub>0</sub> | F <sub>0</sub> | F <sub>1</sub>  | N <sub>0</sub>  | N <sub>1</sub> | $N_2$          | N <sub>3</sub> | N4             | N5              | U <sub>0</sub>  | V <sub>0</sub>  |

| 2nd          | a <sub>0</sub> | a <sub>1</sub> | a <sub>2</sub> | a3         | a <sub>4</sub> | a5 | a <sub>6</sub> | b <sub>0</sub> | b <sub>1</sub> | b <sub>2</sub> | b3             | b4             | b5              | b <sub>6</sub>  | c0             | <sup>c</sup> 1 | c <sub>2</sub> | сз             | c4              | c5              | c <sub>6</sub>  |

| 3rd          | d <sub>0</sub> | d <sub>1</sub> | d <sub>2</sub> | d3         | d4             | d5 | d <sub>6</sub> | e0             | e <sub>1</sub> | e2             | ез             | e4             | e5              | e <sub>6</sub>  | fo             | f <sub>1</sub> | f <sub>2</sub> | fз             | f4              | f5              | f <sub>6</sub>  |

| 4th          | 90             | <b>9</b> 1     | g2             | <b>9</b> 3 | <b>9</b> 4     | 95 | 96             | h <sub>0</sub> | h <sub>1</sub> | h <sub>2</sub> | hȝ             | h4             | h5              | h <sub>6</sub>  | i0             | i <sub>1</sub> | i <sub>2</sub> | iз             | i4              | i5              | <sup>i</sup> 6  |

| 5th          | jo             | j1             | j2             | jз         | j4             | j5 | j6             | k <sub>0</sub> | k <sub>1</sub> | k <sub>2</sub> | kз             | k <sub>4</sub> | k5              | k <sub>6</sub>  | l <sub>0</sub> | I <sub>1</sub> | $I_2$          | ١ <sub>3</sub> | $I_4$           | l5              | I <sub>6</sub>  |

|              |                |                |                |            |                |    |                |                |                |                |                |                |                 |                 |                |                |                |                |                 |                 |                 |

| nth          | i              | i              | i              | i          | i              | i  | i              | i              | i              | i              | i              | i              | i               | i               | i              | i              | i              | i              | i               | i               | i               |

#### 2.4.1 Bit Definitions

- K: 10-bit Fragment Check Character. This check character is calculated by initializing the fragment check character (K) to zero and summing the information bits of each code word in the message fragment (including control information and termination characters and bits in the last message word) to a check sum register. The information bits of each word are broken into three groups: the first is the 8 bits comprising i<sub>0</sub> through i<sub>7</sub>, the second group comprises bits i<sub>8</sub> through i<sub>15</sub>, and the third group comprises bits i<sub>16</sub> through i<sub>20</sub>. Bits i<sub>0</sub>, i<sub>8</sub>, and i<sub>16</sub> are the LSBs of each group. The binary sum is calculated, the 1's complement of the sum is determined and the 10 LSBs of the result is transmitted as the message check character.

- C: 1-bit Message Continued Flag. When set (= 1) indicates fragments of this message are to be expected in following frames. The longest message which will fit into a frame is 84 code words total. Three alpha characters per word yields a maximum message of 252 characters in a frame assuming no other traffic. Messages longer than this value must be sent as several fragments.

- F: 2-bit Message Fragment Number. This is a modulo 3 message fragment number which is incremented by 1 in successive message fragments. Initial fragments start at 11 and increment 1 for each successive fragment. The 11 state (after the start fragment) is skipped in this process to avoid confusion with an initial fragment of a non-continued message. The final fragment is indicated by Message Continued Flag being reset (= 0).

- N: Message Number. When the system supports message retrieval, the system controller assigns message numbers (for each paging address separately) starting at 0 and progressing up to a maximum of 63 in consecutive order. The actual maximum rollover number is defined in the pager code plug to accommodate values set in the system infrastructure. When message numbers are not received in order, the subscriber should assume a message has been missed. The subscriber or the pager may determine the missing message number(s) allowing a request to be made for retrieval. When a normal unnumbered numeric message is received (message retrieval flag is equal to 0), it is not to be included in the missed message calculation. This number is also used to identify fragments of the same message. Multiple messages to the same address must have separate message numbers.

- R: Message Retrieval Flag. When this bit is set to 1, the pager expects to see messages numbered in order (each address numbered separately). Detection of a missing number indicates a missed message. A message received with R = 0 is allowed to be out of order and does not cause the pager to indicate that a message has been missed.

- M: 1-bit Mail Drop Flag. When set (= 1) indicates the message is to be stored in a special area in memory. It automatically writes over existing data in that memory space.

- S: 7-bit Signature Field. The signature is defined to be the 1's complement of the binary sum over the total message (all fragments) taken 7 bits at a time (on alpha character boundary) starting with the first 7 bits directly following the signature field (a<sub>6</sub>a<sub>5</sub>a<sub>4</sub>a<sub>3</sub>a<sub>2</sub>a<sub>1</sub>a<sub>0</sub>, b<sub>6</sub>b<sub>5</sub>b<sub>4</sub>b<sub>3</sub>b<sub>2</sub>b<sub>1</sub>b<sub>0</sub>, etc.). The 7 least significant bits of the result is transmitted as the message signature.

- U, V: Fragmentation Control Bits. This field exists in all fragments except the first fragment. It is used to support character position tracking in each fragment when symbolic characters (characters made up of 1, 2, or 3 ASCII characters) are transmitted using the Alphanumeric message type. The default value is 0,0. See subsection 2.4.5, *Enhanced Fragmentation Rules*, for more information.

#### 2.4.2 Message Content

Starting with the second character of the second word in the message (first character of the second word in all remaining fragments), each 7-bit field represents Standard ASCII (ISO 646–1983E) characters with options for certain International characters.

#### 2.4.3 Message Termination

The ASCII character ETX (03) should be used to fill any unused 7-bit characters in a word. In the case where symbolic characters are being transmitted special rules for fragment and message termination are defined in 2.4.4, *Alphanumeric Message Rules for Symbolic Characters Sets*.

#### 2.4.4 Alphanumeric Message Rules for Symbolic Characters Sets

In the past, paging protocols have supported symbolic characters like Chinese, Kanji, etc., using a 7-bit ASCII protocol. When the FLEX alphanumeric mode is used to carry this same signaling format, special fragmenting rules are required to maintain character boundaries so performance is optimized under poor signal conditions. The following rules allow character positions within a fragment to be determined when prior fragments are missing.

#### 2.4.5 Enhanced Fragmentation Rules

- The pager must recognize <NUL> characters only at the end of fragments where they are used as fill characters. The pager must remove these characters so that the displayed message is not affected. In all other positions the NUL character must be considered a result of channel errors. (This provides a method to end each fragment with a complete character and does not disrupt the pager, which is not capable of following all of the EF (Enhanced Fragmenting) rules.)

- □ The last fragment is to be completed by filling unused character positions with <ETX> characters or <NUL> characters. (Original FLEX alphanumeric message definition (<ETX>) plus the new <NUL> requirement. When message ends exactly in the last character position in the last BCH code word, no additional <ETX> is required).

- □ The U and V bits in the message header are available in all fragments following the initial fragment to aid in decoding. In the first fragment, the pager must assume the message starts in the default character mode. For the second and remaining fragments, the definition of the (U,V) field is as shown in Table 2–7.

#### Table 2–7. Vector Type V = 101, Other Fragment

| U <sub>0</sub> | V <sub>0</sub> | Definition                                       |

|----------------|----------------|--------------------------------------------------|

| 0              | 0              | EF not supported in controller                   |

| 0              | 1              | Reserved (for a second alternate character mode) |

| 1              | 0              | Default Character Mode – start position 1        |

| 1              | 1              | Alternate Character Mode – start position 1      |

When the EF field is 0 0, the pager decodes messages, allowing characters to be split between fragments. When the U,V field is not 0 0, each fragment starts on a character boundary with the character mode defined by the above table.

#### 2.5 Secure Message

Table 2–8 describes the bit format of the secure messages. The 7-bit characters of the message are designated as lowercase letters a, b, c, d, etc. Secure Messages can be sent as fragments. The service provider has the option of dividing the message into several pieces and sending the separate pieces at any time within a given time period.

| Message Word | i <sub>0</sub> | i <sub>1</sub> | i2             | i3 | i4         | i5    | i6             | i7             | ig             | ig             | i10            | i11            | i <sub>12</sub> | i <sub>13</sub> | i14            | i15            | <sup>i</sup> 16 | i17 | i <sub>18</sub> | i <sub>19</sub> | i <sub>20</sub> |

|--------------|----------------|----------------|----------------|----|------------|-------|----------------|----------------|----------------|----------------|----------------|----------------|-----------------|-----------------|----------------|----------------|-----------------|-----|-----------------|-----------------|-----------------|

| 1st          | K <sub>0</sub> | K <sub>1</sub> | K <sub>2</sub> | Кз | K4         | $K_5$ | K <sub>6</sub> | K7             | K <sub>8</sub> | Kg             | C <sub>0</sub> | F <sub>0</sub> | F <sub>1</sub>  | N <sub>0</sub>  | N <sub>1</sub> | N <sub>2</sub> | N <sub>3</sub>  | N4  | N <sub>5</sub>  | s0              | s <sub>1</sub>  |

| 2nd          | a <sub>0</sub> | a <sub>1</sub> | a2             | аз | a4         | a5    | a <sub>6</sub> | b0             | b <sub>1</sub> | b2             | bз             | b4             | b5              | b6              | c0             | c1             | c2              | сз  | c4              | С5              | c <sub>6</sub>  |

| 3rd          | d <sub>0</sub> | d <sub>1</sub> | d2             | d3 | d4         | d5    | d6             | e0             | e <sub>1</sub> | e2             | ез             | e4             | e5              | e6              | f <sub>0</sub> | f <sub>1</sub> | f2              | f3  | f4              | f5              | f <sub>6</sub>  |

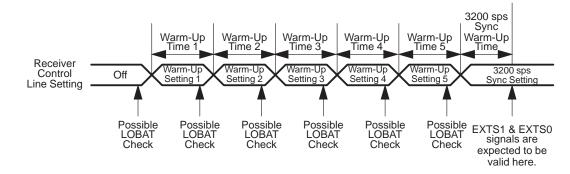

| 4th          | g0             | 91             | g2             | g3 | <b>9</b> 4 | 95    | 96             | h <sub>0</sub> | h <sub>1</sub> | h <sub>2</sub> | hз             | h4             | h5              | h <sub>6</sub>  | i <sub>0</sub> | i <sub>1</sub> | i <sub>2</sub>  | iз  | i4              | i5              | <sup>i</sup> 6  |