XCPS012 - DECEMBER 1997

- Supports PCI Local Bus Specification 2.1 and PCI-to-PCI Bridge Specification 1.0

- 3.3-V Core Logic With Universal PCI Interfaces Compatible With 3.3-V and 5-V PCI Signaling Environments

- Supports Two 32-Bit, 33-MHz PCI Buses

- Provides Internal Arbitration for Up to Six Secondary Bus Masters With Programmable Control

- Provides Six Secondary PCI Bus Clock Outputs

- Supports Burst Transfers to Maximize Data Throughput on Both PCI Buses

- Provides Two Extension Windows

- EEPROM Interface for Loading Texas Instruments (TI™) Subsystem ID and Subsystem Vendor ID

- Four Primary and Four Secondary General-Purpose I/Os

- Independent Read and Write Buffers for Each Direction

- Secondary Positive Decode

- Predictable Latency: Compliant With PCI Local Bus Specification 2.1

- External Arbiter Option

- Provides Concurrent Operation

- Serial IRQ Bridging

- Propagates Bus Locking

- Supports PCI Clock Run

- Secondary Bus Driven Low During Reset

- Docking Connect Detects

- PCI Local Bus Specification 2.0-Compliant Device Optimization

- Advanced Submicron, Low-Power CMOS Technology

- Provides VGA/Palette Memory and I/O, and Subtractive Decoding Options

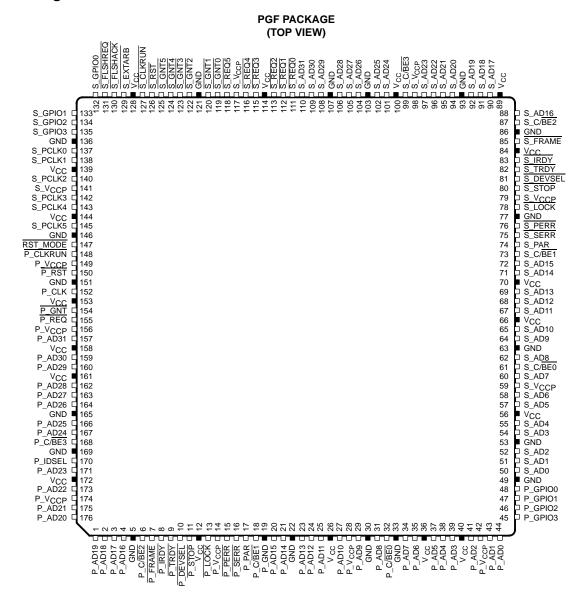

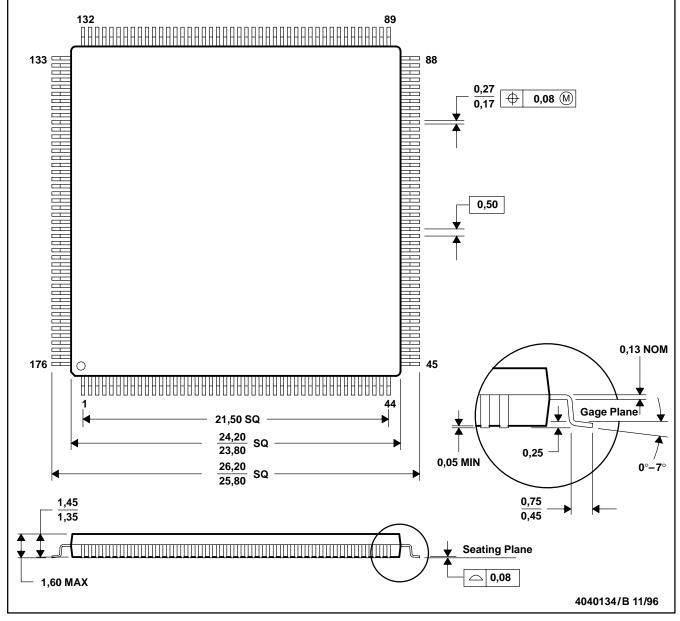

- Packaged in 176-Pin Plastic Quad Flatpack

#### **Table of Contents**

| Description2ElectorSystem Block Diagram2PCITerminal Assignments3PCITerminal Functions4PartAbsolute Maximum Ratings9PCIRecommended Operating Conditions9MedRecommended Operating Conditions for PCI Interface9 | I Clock/Reset Timing Requirements 10   I Timing Requirements 10   rameter Measurement Information 11   I Bus Parameter Measurement Information 12 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

TI is a trademark of Texas Instruments Incorporated.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

Copyright © 1997, Texas Instruments Incorporated

XCPS012 - DECEMBER 1997

#### description

The TI PCI2030 PCI-to-PCI bridge provides a high-performance connection path between two peripheral component interconnect (PCI) buses. Transactions can occur between a master on one PCI bus and a target on another PCI bus. The bridge supports burst-mode transfers to maximize data throughput, and the two bus traffic paths through the bridge act independently.

The PCI2030 bridge is compliant with the PCI Local Bus Specification 2.1, and can be used to overcome the electrical loading limit of ten devices per PCI bus by creating hierarchical buses. Furthermore, add-in cards requiring multiple PCI devices can use the bridge to overcome the electrical loading limit of one PCI device per slot.

The PCI2030 bridge is also compliant with the PCI-to-PCI Bridge Specification 1.0, and implements many additional features that make it an ideal solution for bridging two PCI buses. It can be configured for subtractive decoding, and negative decoding can be disabled on the secondary interface. Two extension windows are also included for special decoding purposes. The serial- and parallel-port addresses can also be programmed for positive decoding on the primary interface. The bridge implements many other features, listed above, that add performance and flexibility.

An advanced CMOS process is utilized to achieve low system-power consumption while operating at PCI clock rates up to 33 MHz.

# Primary PCI Bus IDE Controller Video Controller PCI2030 PCI-To-PCI Bridge Secondary PCI Bus Add-In Card Add-In Card

#### system block diagram

#### terminal assignments

### **Terminal Functions**

# primary PCI system

| TERMINAL I/O |     | I/O  | FUNCTION                                                                                                                                                                                                                                                                                                                                                          |

|--------------|-----|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME         | NO. | TYPE | FUNCTION                                                                                                                                                                                                                                                                                                                                                          |

| P_CLK        | 152 | I    | Primary PCI bus clock. P_CLK provides timing for all transactions on the primary PCI bus. All primary PCI signals are sampled at rising edge of P_CLK.                                                                                                                                                                                                            |

| R_RST        | 150 | I    | PCI reset. When the primary PCI bus reset is asserted, $\overline{P_RST}$ causes the bridge to 3-state all output buffers and reset all internal registers. When asserted, the device is completely nonfunctional. During $\overline{P_RST}$ , the secondary interface is driven low. After $\overline{P_RST}$ is deasserted, the bridge is in its default state. |

# primary PCI address and data

| TERMINAL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | I/O                                                                                                                                                                      | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME NO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | . TYPE                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| P_AD31   15     P_AD30   15     P_AD29   16     P_AD29   16     P_AD28   16     P_AD27   16     P_AD26   16     P_AD25   16     P_AD23   17     P_AD23   17     P_AD21   17     P_AD20   17     P_AD20   17     P_AD19   1     P_AD18   2     P_AD18   2     P_AD18   2     P_AD18   2     P_AD18   2     P_AD18   2     P_AD13   23     P_AD14   24     P_AD13   25     P_AD1   26     P_AD1   25     P_AD1   26     P_AD1   27     P_AD3   37     P_AD6   37     P_AD6   37     P_AD3   38     P_AD2   47     P_AD1 | 9<br>2<br>3<br>4<br>5<br>7<br>1<br>3<br>5<br>5<br>6<br>7<br>1<br>3<br>5<br>5<br>6<br>7<br>1<br>3<br>5<br>5<br>6<br>7<br>1<br>7<br>7<br>1<br>3<br>5<br>5<br>6<br>7<br>1/O | Primary address/data bus. These signals make up the multiplexed PCI address and data bus on the primary interface. During the address phase of a primary bus PCI cycle, P_AD31–P_AD0 contain a 32-bit address or other destination information. During the data phase, P_AD31–P_AD0 contain data.                                                                                                                                                                                                                                       |

| P_C/BE3 16<br>P_C/BE2 6<br>P_C/BE1 18<br>P_C/BE0 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I/O                                                                                                                                                                      | Primary bus commands and byte enables. These signals are multiplexed on the same PCI terminals. During the address phase of a primary bus PCI cycle, P_C/BE3–P_C/BE0 define the bus command. During the data phase, this 4-bit bus is used as byte enables. The byte enables determine which byte paths of the full 32-bit data bus carry meaningful data. P_C/BE0 applies to byte 0 (P_AD7–P_AD0), P_C/BE1 applies to byte 1 (P_AD15–P_AD8), P_C/BE2 applies to byte 2 (P_AD23–P_AD16), and P_C/BE3 applies to byte 3 (P_AD31–P_AD24). |

| P_CLKRUN 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3 I/O                                                                                                                                                                    | Primary PCI bus clock run. $\overline{P_{CLKRUN}}$ is used by the central resource to request permission to stop the PCI clock or to slow it down.                                                                                                                                                                                                                                                                                                                                                                                      |

# **Terminal Functions (Continued)**

#### primary PCI interface control

| TERMINAL                                 |                      | I/O  | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------------------------------------|----------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                                     | NO.                  | TYPE | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                          |

| P_DEVSEL                                 | 10                   | I/O  | Primary device select. The bridge asserts $P_{DEVSEL}$ to claim a PCI cycle as the target device. As a PCI initiator on the primary bus, the bridge monitors $P_{DEVSEL}$ until a target responds. If no target responds before time-out occurs, then the bridge terminates the cycle with an initiator abort.                                                                                                    |

| P_FRAME                                  | 7                    | I/O  | Primary cycle frame. $P_{FRAME}$ is driven by the initiator of a primary bus cycle. $P_{FRAME}$ is asserted to indicate that a bus transaction is beginning, and data transfers continue while this signal is asserted. When $P_{FRAME}$ is deasserted, the primary bus transaction is in the final data phase.                                                                                                   |

| P_GNT                                    | 154                  | I    | Primary bus grant to bridge. $P_{GNT}$ is driven by the primary PCI bus arbiter to grant the bridge access to the primary PCI bus after the current data transaction has completed. $P_{GNT}$ may or may not follow a primary bus request, depending on the primary bus parking algorithm.                                                                                                                        |

| P_GPIO3<br>P_GPIO2<br>P_GPIO1<br>P_GPIO0 | 45<br>46<br>47<br>48 | I/O  | Primary bus general-purpose I/O terminals. These terminals are provided for general input/output use in system design.                                                                                                                                                                                                                                                                                            |

| P_IDSEL                                  | 170                  | I    | Initialization device select. P_IDSEL selects the bridge during configuration space accesses. P_IDSEL can be connected to one of the upper 24 PCI address lines on the primary PCI bus.<br>Note: There is no IDSEL signal interfacing the secondary PCI bus; thus, the entire configuration space of the                                                                                                          |

|                                          |                      |      | bridge can only be accessed from the primary bus.                                                                                                                                                                                                                                                                                                                                                                 |

| P_IRDY                                   | 8                    | I/O  | Primary initiator ready. P_IRDY indicates the primary bus initiator's ability to complete the current data phase of the transaction. A data phase is completed on a rising edge of P_CLK where both P_IRDY and P_TRDY are asserted. Until P_IRDY and P_TRDY are both sampled asserted, wait states are inserted.                                                                                                  |

| P_LOCK                                   | 13                   | I/O  | Primary PCI bus lock. PLOCK is used to lock the primary bus and gain exclusive access as an initiator.                                                                                                                                                                                                                                                                                                            |

| P_PAR                                    | 17                   | I/O  | Primary parity. In all primary bus read and write cycles, the bridge calculates even parity across the P_AD and P_C/BE buses. As an initiator during PCI write cycles, the bridge outputs this parity indicator with a one-P_CLK delay. As a target during PCI read cycles, the calculated parity is compared to the initiator's parity indicator; a misdemeanor can result in a parity error assertion (P_PERR). |

| P_PERR                                   | 15                   | I/O  | Primary parity error indicator. P_PERR is driven by a primary bus PCI device to indicate that calculated parity does not match P_PAR when P_PERR is enabled through bit 6 of the command register.                                                                                                                                                                                                                |

| P_REQ                                    | 155                  | 0    | Primary PCI bus request. P_REQ is asserted by the bridge to request access to the primary PCI bus as an initiator.                                                                                                                                                                                                                                                                                                |

| P_SERR                                   | 16                   | о    | Primary system error. Output pulsed from the bridge when enabled through the command register indicating a system error has occurred. The bridge need not be the target of the primary PCI cycle to assert P_SERR. When bit 6 is enabled in the bridge control register, P_SERR will also pulse, indicating that a system error has occurred on one of the subordinate buses downstream from the bridge.          |

| P_STOP                                   | 11                   | I/O  | Primary cycle stop signal. P_STOP is driven by a PCI target to request the initiator to stop the current primary bus transaction. P_STOP is used for target disconnects and is commonly asserted by target devices that do not support burst data transfers.                                                                                                                                                      |

| RST_MODE                                 | 147                  | I    | If $\overline{\text{RST}}$ MODE is asserted during $\overline{\text{P}}$ RST, it causes $\overline{\text{S}}$ RST to be asserted and the secondary clocks to be turned off.                                                                                                                                                                                                                                       |

| P_TRDY                                   | 9                    | I/O  | Primary target ready. P_TRDY indicates the primary bus target's ability to complete the current data phase of the transaction. A data phase is completed on a rising edge of P_CLK where both P_IRDY and P_TRDY are asserted. Until both P_IRDY and P_TRDY are asserted, wait states are inserted.                                                                                                                |

XCPS012 - DECEMBER 1997

### **Terminal Functions (Continued)**

#### secondary PCI system

| TERMIN                                                         | TERMINAL I/O                           |      | FUNCTION                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

|----------------------------------------------------------------|----------------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| NAME                                                           | NO.                                    | TYPE | FUNCTION                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| S_PCLK5<br>S_PCLK4<br>S_PCLK3<br>S_PCLK2<br>S_PCLK1<br>S_PCLK0 | 145<br>143<br>142<br>140<br>138<br>137 | ο    | Secondary PCI bus clock. Provides timing for all transactions on the secondary PCI bus. All secondary PCI signals are sampled at the rising edge of S_CLK5–S_CLK0.                                                                                                                                                                                                         |  |  |  |  |

| S_CLKRUN                                                       | 127                                    | I/O  | Secondary PCI bus clock run. $\overline{S_{CLKRUN}}$ is output by the bridge to indicate that S_CLK will be stop S_CLKRUN is driven by secondary bus PCI devices to request that S_CLK be stopped.                                                                                                                                                                         |  |  |  |  |

| S_EXTARB                                                       | 129                                    | I    | Secondary external arbiter enable. When $\overline{S\_EXTARB}$ is asserted, the secondary external arbiter is enabled.<br>When the external arbiter is enabled, $\overline{S\_REQ0}$ is reconfigured as a secondary bus grant input to the bridge and $\overline{S\_GNT0}$ is reconfigured as a secondary bus master request to the external arbiter on the secondary bus. |  |  |  |  |

| S_RST                                                          | 126                                    | 0    | Secondary PCI reset. $S\_RST$ is a logical OR of $P\_RST$ and the state of the secondary bus reset bit of the bridge control register. $S\_RST$ is asynchronous with respect to the state of the secondary interface CLK signal.                                                                                                                                           |  |  |  |  |

### **Terminal Functions (Continued)**

#### secondary PCI address and data

| TERMIN                                                                                                                                                                                                                                                                                                                                                                                                                      | ۹L                                                                                                                                                                                                     | I/O  | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                                                                                                                                                                                                                                                                                                                                                                                                                        | NO.                                                                                                                                                                                                    | TYPE | I ONOTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| S_AD31<br>S_AD30<br>S_AD29<br>S_AD28<br>S_AD27<br>S_AD26<br>S_AD25<br>S_AD24<br>S_AD23<br>S_AD22<br>S_AD24<br>S_AD23<br>S_AD22<br>S_AD24<br>S_AD23<br>S_AD22<br>S_AD21<br>S_AD20<br>S_AD19<br>S_AD18<br>S_AD17<br>S_AD16<br>S_AD15<br>S_AD14<br>S_AD13<br>S_AD12<br>S_AD11<br>S_AD10<br>S_AD9<br>S_AD8<br>S_AD7<br>S_AD6<br>S_AD5<br>S_AD4<br>S_AD3<br>S_AD2<br>S_AD4<br>S_AD3<br>S_AD2<br>S_AD1<br>S_AD2<br>S_AD1<br>S_AD2 | $\begin{array}{c} 110\\ 109\\ 108\\ 106\\ 105\\ 104\\ 102\\ 101\\ 97\\ 96\\ 95\\ 94\\ 92\\ 91\\ 90\\ 88\\ 72\\ 71\\ 69\\ 68\\ 67\\ 65\\ 64\\ 62\\ 60\\ 58\\ 57\\ 55\\ 54\\ 52\\ 51\\ 50\\ \end{array}$ | I/O  | Secondary address/data bus. These signals make up the multiplexed PCI address and data bus on the secondary interface. During the address phase of a secondary bus PCI cycle, S_AD31–S_AD0 contain a 32-bit address or other destination information. During the data phase, S_AD31–S_AD0 contain data.                                                                                                                                                                                                                                     |

| S_C/ <u>BE3</u><br>S_C/ <u>BE2</u><br>S_C/ <u>BE1</u><br>S_C/ <u>BE0</u>                                                                                                                                                                                                                                                                                                                                                    | 99<br>87<br>73<br>61                                                                                                                                                                                   | I/O  | Secondary bus commands and byte enables. These signals are multiplexed on the same PCI terminals. During the address phase of a secondary bus PCI cycle, S_C/BE3–S_C/BE0 define the bus command. During the data phase, this 4-bit bus is used as byte enables. The byte enables determine which byte paths of the full 32-bit data bus carry meaningful data. S_C/BE0 applies to byte 0 (S_AD7–S_AD0), S_C/BE1 applies to byte 1 (S_AD15–S_AD8), S_C/BE2 applies to byte 2 (S_AD23–S_AD16), and S_C/BE3 applies to byte 3 (S_AD31–S_AD24). |

| S_DEVSEL                                                                                                                                                                                                                                                                                                                                                                                                                    | 81                                                                                                                                                                                                     | I/O  | Secondary device select. The bridge asserts $\overline{S_{DEVSEL}}$ to claim a PCI cycle as the target device. As a PCI initiator on the secondary bus, the bridge monitors $\overline{S_{DEVSEL}}$ until a target responds. If no target responds before timeout occurs, then the bridge terminates the cycle with an initiator abort.                                                                                                                                                                                                     |

| S_FRAME                                                                                                                                                                                                                                                                                                                                                                                                                     | 85                                                                                                                                                                                                     | I/O  | Secondary cycle frame. $S$ _FRAME is driven by the initiator of a secondary bus cycle. $S$ _FRAME is asserted to indicate that a bus transaction is beginning and data transfers continue while S_FRAME is asserted. When S_FRAME is deasserted, the secondary bus transaction is in the final data phase.                                                                                                                                                                                                                                  |

| <u>S_GNT5</u><br><u>S_GNT4</u><br><u>S_GNT3</u><br><u>S_GNT2</u><br><u>S_GNT1</u><br><u>S_GNT0</u>                                                                                                                                                                                                                                                                                                                          | 125<br>124<br>123<br>122<br>120<br>119                                                                                                                                                                 | 0    | Secondary bus grant to the bridge. The bridge provides internal arbitration and these signals are used to grant potential secondary PCI bus masters access to the bus. Seven potential initiators (including the bridge) can be located on the secondary PCI bus.<br>When the internal arbiter is disabled, $\overline{S}$ _GNT0 is reconfigured as an external secondary bus request signal for the bridge.                                                                                                                                |

XCPS012 - DECEMBER 1997

### **Terminal Functions (Continued)**

#### secondary PCI interface control

| TERMINAL I/O                                                                                       |                                        | 1/0  |                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------------------------------------------------------------------------------------------------|----------------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                                                                                               | NO.                                    | TYPE | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                             |

| S_GPIO3<br>S_GPIO2<br>S_GPIO1<br>S_GPIO0                                                           | 135<br>134<br>133<br>132               | I/O  | Secondary general-purpose I/O terminals. These terminals are provided for general-purpose input/output use in system design.                                                                                                                                                                                                                                                                                         |

| S_IRDY                                                                                             | 83                                     | I/O  | Secondary initiator ready. $S\_IRDY$ indicates the secondary bus initiator's ability to complete the current data phase of the transaction. A data phase is completed on a rising edge of S_CLK where both $S\_IRDY$ and $S\_TRDY$ are asserted; until $S\_IRDY$ and $S\_TRDY$ are asserted, wait states are inserted.                                                                                               |

| S_LOCK                                                                                             | 78                                     | I/O  | Secondary lock S_LOCK is used to lock the secondary bus and gain exclusive access as an initiator.                                                                                                                                                                                                                                                                                                                   |

| S_PAR                                                                                              | 74                                     | I/O  | Secondary parity. In all secondary bus read and write cycles, the bridge calculates even parity across the S_AD and S_C/BE buses. As an initiator during PCI write cycles, the bridge outputs this parity indicator with a one-S_CLK delay. As a target during PCI read cycles, the calculated parity is compared to the initiator's parity indicator. A miscompare can result in a parity error assertion (S_PERR). |

| S_PERR                                                                                             | 76                                     | I/O  | Secondary parity error indicator. S_PERR is driven by a secondary bus PCI device to indicate that calculated parity does not match S_PAR when enabled through the command register.                                                                                                                                                                                                                                  |

| <u>S_REQ5</u><br><u>S_REQ4</u><br><u>S_REQ3</u><br><u>S_REQ2</u><br><u>S_REQ1</u><br><u>S_REQ0</u> | 118<br>116<br>115<br>113<br>112<br>111 | I    | Secondary PCI bus request signals. The bridge provides internal arbitration, and these signals are used as inputs from secondary PCI bus initiators requesting the bus. Seven potential initiators (including the bridge) can be located on the secondary PCI bus.<br>When the internal arbiter is disabled, S_REQ0 is reconfigured as an external secondary bus grant for the bridge.                               |

| S_SERR                                                                                             | 75                                     | I    | Secondary system error. S_SERR is passed through the primary interface by the bridge if enabled through the bridge control register. S_SERR is never asserted by the bridge.                                                                                                                                                                                                                                         |

| S_STOP                                                                                             | 80                                     | I/O  | Secondary cycle stop signal. $\underline{S\_STOP}$ is driven by a PCI target to request the initiator to stop the current secondary bus transaction. $\underline{S\_STOP}$ is used for target disconnects and is commonly asserted by target devices that do not support burst data transfers.                                                                                                                       |

| S_TRDY                                                                                             | 82                                     | I/O  | Secondary target ready. $S\_TRDY$ indicates the secondary bus target's ability to complete the current data <u>phase of</u> the transaction. A <u>data phase</u> is <u>completed</u> on a rising edge of S_CLK where both $S\_IRDY$ and $S\_TRDY$ are asserted; until $S\_IRDY$ and $S\_TRDY$ are asserted, wait states are inserted.                                                                                |

| S_FLSHREQ                                                                                          | 131                                    | I    | Flush request. When $S_{FLSHREQ}$ is asserted, it signals a request to the PCI2030 to suspend internal write posting. When the bridge is ready to suspend internal write posting, it responds by asserting $\overline{S}_{FLSHACK}$ . S_FLSHACK remains asserted until the write posting buffers are empty.                                                                                                          |

| S_FLSHACK                                                                                          | 130                                    | ο    | Flush acknowledge. S_FLSHACK is asserted by the PCI2030 to indicate that the internal write posting is suspended. S_FLSHACK remains asserted until the write posting buffers are empty.                                                                                                                                                                                                                              |

# power supply

|                    | TERMINAL                                                                                  | FUNCTION                                                                                                           |

|--------------------|-------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| NAME               | NO.                                                                                       | FUNCTION                                                                                                           |

| GND                | 5, 19, 22. 30, 33, 49, 53, 63, 77, 86, 93, 103,<br>107, 121, 136, 146, 151, 161, 165, 169 | Device ground terminals                                                                                            |

| VCC                | 12, 26, 36, 40, 56, 66, 70, 84, 89, 100, 114,<br>128, 139, 144, 153, 158, 172             | Power-supply terminal for core logic (3.3 V)                                                                       |

| P_VCCP             | 14, 28, 42, 149, 156, 174                                                                 | Primary bus-signaling environment supply. $P\_V_{CCP}$ is used in protection circuitry on primary bus I/O signals. |

| S_V <sub>CCP</sub> | 59, 79, 98, 117, 141                                                                      | Secondary bus-signaling environment supply. S_V_CCP is used in protection circuitry on primary bus I/O signals.    |

XCPS012 - DECEMBER 1997

#### absolute maximum ratings over operating temperature ranges (unless otherwise noted)<sup>†</sup>

| Supply voltage range: V <sub>CC</sub>                                                                 | –0.5 V to 4.6 V                   |

|-------------------------------------------------------------------------------------------------------|-----------------------------------|

| V <sub>CCP</sub>                                                                                      | –0.5 V to 6 V                     |

| Input voltage range, VI: Standard                                                                     | –0.5 V to V <sub>CC</sub> + 0.5 V |

| Output voltage range, V <sub>O</sub> : Standard                                                       |                                   |

| Input clamp current, $I_{IK}$ ( $V_I < 0$ or $V_I > V_{CC}$ ) (see Note 1)                            | ±20 mA                            |

| Output clamp current, $I_{OK}$ (V <sub>O</sub> < 0 or V <sub>O</sub> > V <sub>CC</sub> ) (see Note 2) | ±20 mA                            |

| Storage temperature range, T <sub>stg</sub>                                                           | –65°C to 150°C                    |

| Virtual junction temperature, $T_J$                                                                   | 150°C                             |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTES: 1. Applies to external input and bidirectional buffers.  $V_I > V_{CC}$  does not apply to fail-safe terminals.

2. Applies to external output and bidirectional buffers. VO > VCC does not apply to fail-safe terminals.

#### recommended operating conditions

|                |                                           | MIN              | NOM | MAX | UNIT |

|----------------|-------------------------------------------|------------------|-----|-----|------|

| tt             | Input transition (rise and fall) time CMC | 1OS compatible 1 |     | 4   | ns   |

| Т <sub>А</sub> | Operating ambient temperature range Com   | mmercial 0       | 25  | 70  | °C   |

| Tj‡            | Virtual junction temperature Com          | mmercial 0       | 25  | 115 | °C   |

<sup>‡</sup>These junction temperatures reflect simulation conditions. The customer is responsible for verifying junction temperature.

#### recommended operating conditions for PCI interface

|                   |                          |                   | OPERATION | MIN      | NOM  | MAX                  | UNIT |

|-------------------|--------------------------|-------------------|-----------|----------|------|----------------------|------|

| VCC               | Core voltage             | Commercial        | 3.3 V     | 3        | 3.3  | 3.6                  | V    |

| VCCP              | DCI aunaly valtage       | Commercial        | 3.3 V     | 3        | 3.3  | 3.6                  | V    |

| VCCP              | PCI supply voltage       | Commercial        | 5 V       | 4.75     | 5    | 5.25                 | v    |

| VI                | Input voltage            | 3.3 V             | 0         |          | VCCP | V                    |      |

| <u>۱</u>          | input voltage            | 5 V               | 0         |          | VCCP |                      |      |

| Vo§               | Output voltage           | 3.3 V             | 0         |          | VCCP | V                    |      |

| v03               | Output voltage           |                   | 5 V       | 0        |      | VCCP                 | v    |

| VIH¶              |                          | CMOS compatible   | 3.3 V     | 0.5 VCCP |      |                      | V    |

| VIH "             | High-level input voltage | CiviOS compatible | 5 V       | 2        |      |                      | v    |

| V. ¶              | Low-level input voltage  | CMOS compatible   | 3.3 V     |          |      | 0.3 V <sub>CCP</sub> | V    |

| V <sub>IL</sub> ¶ | Low-level input voltage  | CINOS compatible  | 5 V       |          |      | 0.8                  | v    |

§ Applies to external output buffers

$\P$  Applies to external input and bidirectional buffers without hysteresis

XCPS012 - DECEMBER 1997

#### electrical characteristics over recommended operating conditions (unless otherwise noted)

|     | PARAMETER                      | SIDE                     | TEST CONDITIONS               | OPERATION       | MIN                     | MAX                 | UNIT |      |   |

|-----|--------------------------------|--------------------------|-------------------------------|-----------------|-------------------------|---------------------|------|------|---|

| Val | Likely to a longer of the line |                          | I <sub>OH</sub> = -0.5 mA     | 3.3 V           | 0.9 V <sub>CC</sub>     |                     | V    |      |   |

| VOH | High-level output voltage      |                          | I <sub>OH</sub> = -2 mA       | 5 V             | 2.4                     |                     | v    |      |   |

| Vai |                                |                          | I <sub>OL</sub> = 1.5 mA      | 3.3 V           |                         | 0.1 V <sub>CC</sub> | V    |      |   |

| VOL | Low-level output voltage       | Low-level output voltage | Low-level output voltage      |                 | $I_{OL} = 6 \text{ mA}$ | 5 V                 |      | 0.55 | v |

|     |                                | Input pins               | bins $V_I = V_{CC}^{\dagger}$ | 3.6 V           |                         | 10                  | μΑ   |      |   |

| ı   | High-level input current       |                          |                               | 5.25 V          |                         | 20                  |      |      |   |

| ΙΗ  | righ-level input current       | UO sisst                 |                               | 3.6 V           |                         | 20                  |      |      |   |

|     |                                | I/O pins‡                | $V_I = V_{CC}^{\dagger}$      |                 |                         | 25                  |      |      |   |

| I   |                                |                          |                               | Input pins      | $V_I = GND$             | 3.6 V to 5.25 V     |      | -1   |   |

| ΙL  | Low-level input current        | I/O pins‡                | V <sub>I</sub> = GND          | 3.6 V to 5.25 V |                         | -20                 | μA   |      |   |

| Ioz | High-impedance output current  |                          | $V_{O} = V_{CCP}$ or GND      |                 |                         | ±20                 | μA   |      |   |

<sup>†</sup> For PCI pins, V<sub>CC</sub> = V<sub>CCP</sub>.

<sup>‡</sup> For I/O pins, the input leakage current includes the off-state output current I<sub>OZ</sub>.

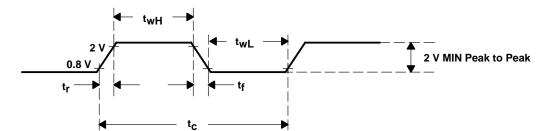

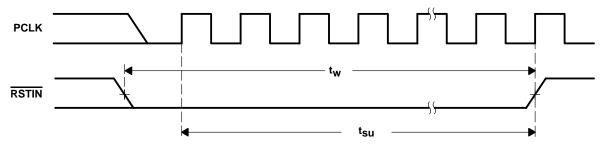

# PCI clock/reset timing requirements over recommended ranges of supply voltage and operating free-air temperature (see Figure 1, Figure 2, and Figure 3)

|                       |                                                      | ALTERNATE<br>SYMBOL             | MIN | MAX | UNIT |

|-----------------------|------------------------------------------------------|---------------------------------|-----|-----|------|

| t <sub>C</sub>        | Cycle time, PCLK                                     | t <sub>cyc</sub>                | 30  | 8   | ns   |

| <sup>t</sup> wH       | Pulse duration, PCLK high                            | <sup>t</sup> high               | 11  |     | ns   |

| <sup>t</sup> wL       | Pulse duration, PCLK low                             | tlow                            | 11  |     | ns   |

| $\Delta v / \Delta t$ | Slew rate, PCLK                                      | t <sub>r</sub> , t <sub>f</sub> | 1   | 4   | V/ns |

| tw                    | Pulse duration, RSTIN                                | <sup>t</sup> rst                | 1   |     | ms   |

| t <sub>su</sub>       | Setup time, PCLK active at end of RSTIN (see Note 3) | <sup>t</sup> rst-clk            | 100 |     | μs   |

NOTE 3: The setup and hold times for the secondary are identical to those for the primary; however, the times are relative to the secondary PCI close.

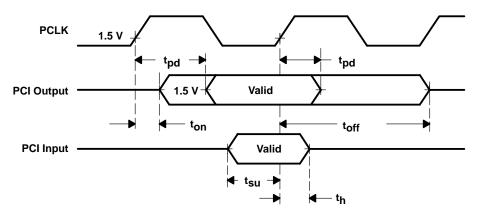

# PCI timing requirements over recommended ranges of supply voltage and operating free-air temperature (see Note 4 and Figure 1 and Figure 4)

|                  |                                              |                                          | ALTERNATE<br>SYMBOL          | TEST CONDITIONS                    | MIN | МАХ | UNIT |

|------------------|----------------------------------------------|------------------------------------------|------------------------------|------------------------------------|-----|-----|------|

| <sup>t</sup> pd  | Propagation delay time                       | PCLK to shared signal valid delay time   | <sup>t</sup> val             | C <sub>L</sub> = 50 pF, See Note 5 |     | 11  | ns   |

|                  |                                              | PCLK to shared signal invalid delay time | t <sub>inv</sub>             |                                    | 2   |     |      |

| t <sub>en</sub>  | Enable time,<br>high-impedance-to-active de  | lay time from PCLK                       | <sup>t</sup> on              |                                    | 2   |     | ns   |

| <sup>t</sup> dis | Disable time,<br>active-to-high-impedance de | lay time from PCLK                       | <sup>t</sup> off             |                                    |     | 28  | ns   |

| t <sub>su</sub>  | Setup time before PCLK valid                 |                                          | t <sub>SU</sub> , See Note 6 |                                    | 7   |     | ns   |

| th               | Hold time after PCLK high                    |                                          | t <sub>h</sub> , See Note 6  |                                    | 0   |     | ns   |

NOTES: 4. This data sheet uses the following conventions to describe time (t) intervals. The format is:  $t_A$ , where *subscript A* indicates the type of dynamic parameter being represented. One of the following is used:  $t_{pd}$  = propagation delay time,  $t_d$  = delay time,  $t_{su}$  = setup time, and  $t_h$  = hold time.

5. PCI shared signals are AD31–AD0, C/BE3–C/BE0, FRAME, TRDY, IRDY, STOP, IDSEL, DEVSEL, and PAR.

6. The setup and hold times for the secondary are identical to those for the primary; however, the times are relative to the secondary PCI close.

lol

ЮН

VLOAD

XCPS012 - DECEMBER 1997

#### PARAMETER MEASUREMENT INFORMATION

Test Point

-

CLOAD

LOAD CIRCUIT

From Output

**Under Test**

| TIMING<br>PARAMETER |                  | C <sub>LOAD</sub> †<br>(pF) | l <mark>OL</mark><br>(mA) | IOH<br>(mA) | V <sub>LOAD</sub><br>(V) |

|---------------------|------------------|-----------------------------|---------------------------|-------------|--------------------------|

| tan                 | <sup>t</sup> PZH | 50                          | 8                         | -8          | 0                        |

| ten                 | <sup>t</sup> PZL |                             |                           |             | 3                        |

| <b>*</b>            | tPHZ             | 50                          | 8                         | -8          | 1.5                      |

| <sup>t</sup> dis    | <sup>t</sup> PLZ |                             |                           | -0          | 1.5                      |

| <sup>t</sup> pd     |                  | 50                          | 8                         | -8          | ‡                        |

LOAD CIRCUIT PARAMETERS

<sup>†</sup>C<sub>LOAD</sub> includes the typical load-circuit distributed capacitance.

$\frac{V_{LOAD} - V_{OL}}{I_{OL}} = 50 \ \Omega$ , where  $V_{OL} = 0.6 \ V$ ,  $I_{OL} = 8 \ mA$

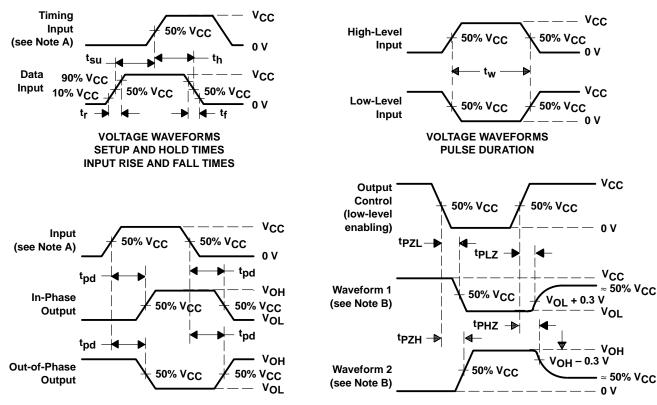

#### VOLTAGE WAVEFORMS PROPAGATION DELAY TIMES

VOLTAGE WAVEFORMS ENABLE AND DISABLE TIMES, 3-STATE OUTPUTS

- NOTES: A. Phase relationships between waveforms were chosen arbitrarily. All input pulses are supplied by pulse generators having the following characteristics: PRR = 1 MHz,  $Z_0 = 50 \Omega$ ,  $t_f \le 6$  ns.

- B. Waveform 1 is for an output with internal conditions such that the output is low except when disabled by the output control. Waveform 2 is for an output with internal conditions such that the output is high except when disabled by the output control.

- C. For tPLZ and tPHZ, VOL and VOH are measured values.

Figure 1. Load Circuit and Voltage Waveforms

XCPS012 - DECEMBER 1997

Figure 2. PCLK Timing Waveform

Figure 3. RSTIN Timing Waveforms

Figure 4. Shared-Signals Timing Waveforms

XCPS012 - DECEMBER 1997

#### MECHANICAL DATA

#### PGF (S-PQFP-G176)

#### PLASTIC QUAD FLATPACK

NOTES: A. All linear dimensions are in millimeters.

B. This drawing is subject to change without notice.

C. Falls within JEDEC MS-026

#### **IMPORTANT NOTICE**

Texas Instruments (TI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

TI warrants performance of its semiconductor products and related software to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Certain applications using semiconductor products may involve potential risks of death, personal injury, or severe property or environmental damage ("Critical Applications").

TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

Inclusion of TI products in such applications is understood to be fully at the risk of the customer. Use of TI products in such applications requires the written approval of an appropriate TI officer. Questions concerning potential risk applications should be directed to TI through a local SC sales office.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards should be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

Copyright © 1997, Texas Instruments Incorporated