XCPS016-DECEMBER 1997

- PCI Bus Power Management Interface Specification 1.0 Compliant

- ACPI 1.0 Compliant

- Fully Compatible With the Intel<sup>™</sup> 430TX (Mobile Triton II) Chipset

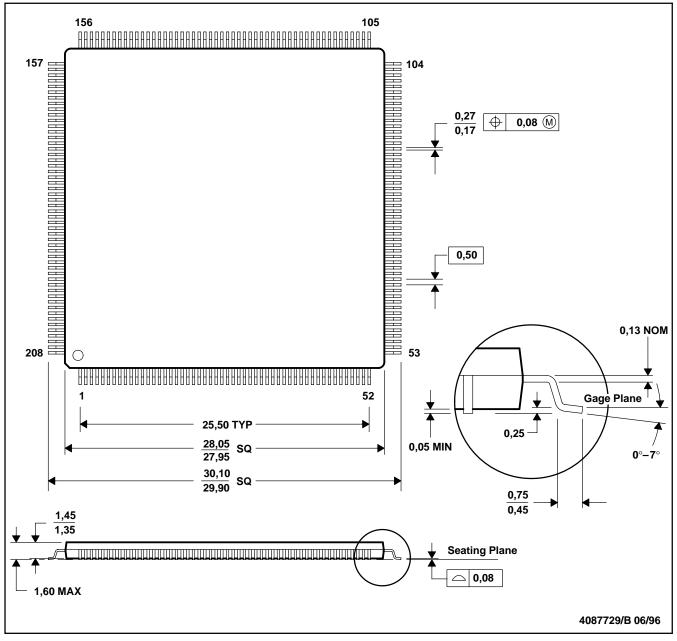

- Packaged in 208-Pin TQFP

- PCI Local Bus Specification Revision 2.1 Compliant

- 1995 PC Card<sup>™</sup> Standard Compliant

- 3.3-V Core Logic With Universal PCI Interfaces Compatible With 3.3-V and 5-V PCI Signaling Environments

- Mix-and-Match 5-V/3.3-V PC Card16 Cards and 3.3-V CardBus Cards

- Supports Two PC Card or CardBus Slots With Hot Insertion and Removal

- Uses Serial Interface to TI™ TPS2202/2206 Dual-Slot PC Card Power Switch

- Supports Burst Transfers to Maximize Data Throughput

- Supports Parallel PCI Interrupts, Parallel ISA IRQ and Parallel PCI Interrupts, Serial ISA IRQ With Parallel PCI Interrupts, and Serial ISA IRQ and PCI Interrupts

- Serial EEPROM Interface for Loading Subsystem ID and Subsystem Vendor ID

- Pipelined Architecture Allows Greater Than 130M-Bytes-Per-Second Throughput From CardBus to PCI and From PCI to CardBus

- Supports Up to Five General-Purpose I/Os

- Programmable Output Select for CLKRUN

- Multifunction PCI Device With Separate Configuration Space for Each Socket

- Five PCI Memory Windows and Two I/O Windows Available for Each PC Card16 Socket

- Two I/O Windows and Two Memory Windows Available to Each CardBus Socket

- Exchangeable Card Architecture (ExCA) Compatible Registers Are Mapped in Memory and I/O Space

- Intel 82365SL-DF Register Compatible

- Supports Distributed DMA (DDMA) and PC/PCI DMA

- Supports 16-Bit DMA on Both PC Card Sockets

- Supports Ring Indicate, SUSPEND, PCI CLKRUN, and CardBus CCLKRUN

- LED Activity Pins

- Supports PCI Bus Lock (LOCK)

- Advanced Submicron, Low-Power CMOS Technology

- For the Complete Data Sheet for PCI1220, Please See Literature #SCPS016

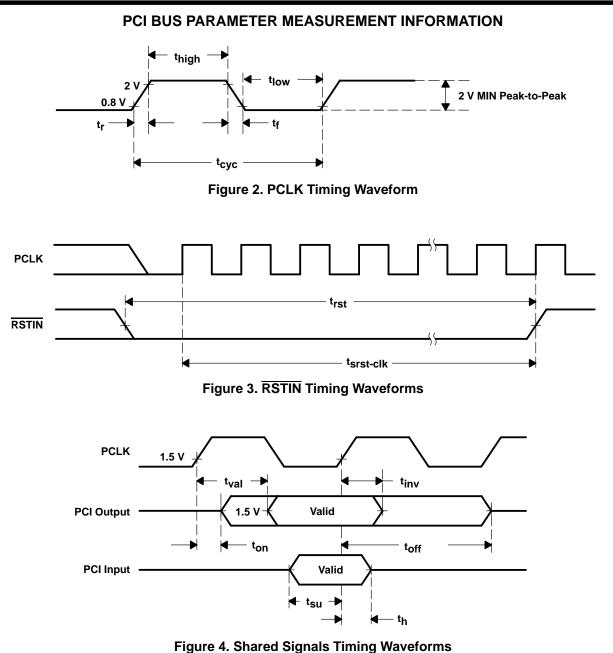

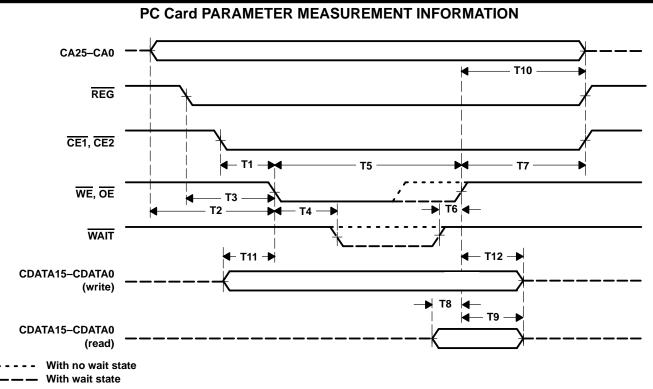

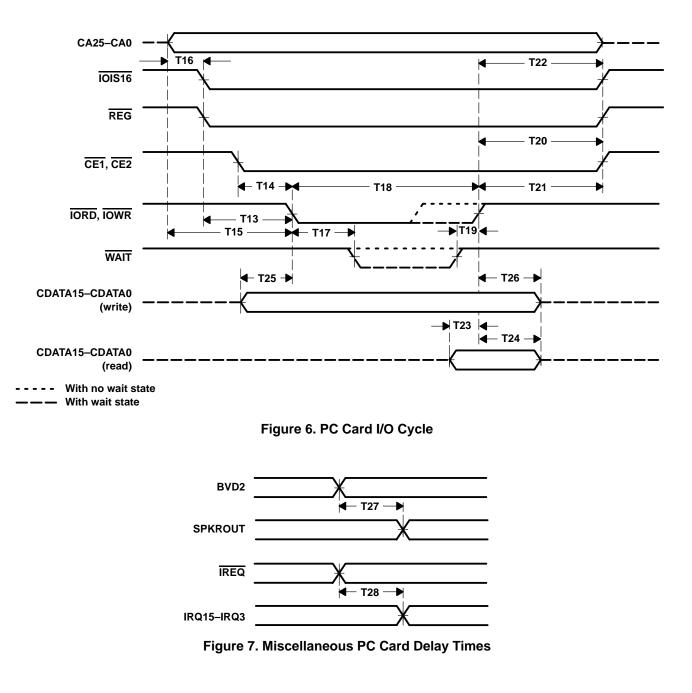

| System Block Diagram       3         Terminal Assignments       4         Terminal Functions       6 | Electrical Characteristics       18         PCI Clock/Reset Timing Requirements       19         PCI Timing Requirements       19         Parameter Measurement Information       20         PCI Burgerster Measurement Information       20 |

|------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Absolute Maximum Ratings 16                                                                          | PCI Bus Parameter Measurement Information                                                                                                                                                                                                    |

| Recommended Operating Conditions 17                                                                  | Mechanical Data                                                                                                                                                                                                                              |

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

Intel is a trademark of Intel Corporation.

PC Card is a trademark of Personal Computer Memory Card International Association (PCMCIA). TI is a trademark of Texas Instruments Incorporated.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright © 1997, Texas Instruments Incorporated

XCPS016-DECEMBER 1997

#### description

The TI PCI1220 is a high-performance PCI-to-PC Card controller that supports two independent PC Card sockets compliant with the 1995 PC Card Standard. The PCI1220 provides a rich feature set that makes it the best choice for bridging between PCI and PC Cards in both notebook and desktop computers. The 1995 PC Card Standard retains the 16-bit PC Card specification defined in PCMCIA Release 2.1, and defines the new 32-bit PC Card, CardBus, capable of full 32-bit data transfers at 33 MHz. The PCI1220 supports any combination of 16-bit and CardBus PC Cards in the two sockets, powered at 5 V or 3.3 V, as required.

The PCI1220 is compliant with the PCI Local Bus Specification 2.1, and its PCI interface can act as either a PCI master device or a PCI slave device. The PCI bus mastering is initiated during 16-bit PC Card direct memory access (DMA) transfers or CardBus PC Card bridging transactions. The PCI1220 is also compliant with the latest *PCI Bus Power Management Interface Specification*.

All card signals are internally buffered to allow hot insertion and removal without external buffering. The PCI1220 is register compatible with the Intel 82365SL-DF ExCA controller. The PCI1220 internal data path logic allows the host to access 8-, 16-, and 32-bit cards using full 32-bit PCI cycles for maximum performance. Independent buffering and a pipeline architecture provide an unsurpassed performance level with sustained bursting. The PCI1220 can also be programmed to accept fast posted writes to improve system-bus utilization.

Multiple system-interrupt signaling options are provided, including: parallel PCI, parallel ISA, serialized ISA, and serialized PCI. Furthermore, general-purpose inputs and outputs are provided for the board designer to implement sideband functions. Many other features are designed into the PCI1220, such as socket activity light-emitting diode (LED) outputs, and are discussed in detail throughout the design specification.

An advanced complementary metal-oxide semiconductor (CMOS) process is used to achieve low system-power consumption while operating at PCI clock rates up to 33 MHz. Several low-power modes enable the host power management system to further reduce power consumption.

Unused PCI1220 inputs must be pulled up using a 43 k $\Omega$  resistor.

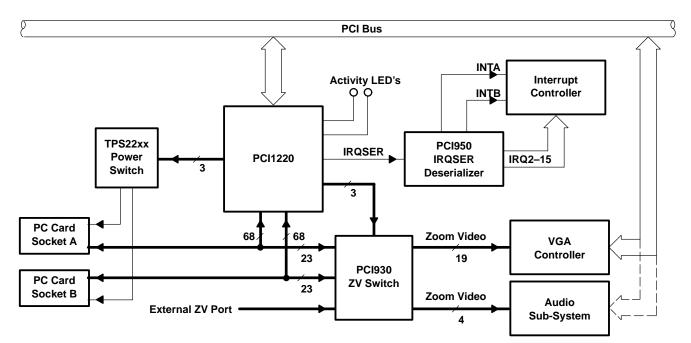

#### system block diagram

A simplified system block diagram using the PCI1220 is provided below. The PCI950 IRQ deseralizer and the PCI930 zoomed video (ZV) switch are optional functions that can be used when the system requires that capability.

The PCI interface includes all address/data and control signals for PCI protocol. The 68-pin PC Card interface includes all address/data and control signals for CardBus and 16-bit (R2) protocols. When zoomed video (ZV) is enabled (in 16-bit PC Card mode) 23 of the 68 signals are redefined to support the ZV protocol.

The interrupt interface includes terminals for parallel PCI, parallel ISA, and serialized PCI and ISA signaling. Other miscellaneous system interface terminals are available on the PCI1220 that include:

- Programmable multifunction terminals

- SUSPEND, RI\_OUT/PME (power management control signal)

- SPKROUT.

NOTE: The PC Card interface is 68 pins for CardBus and 16-bit PC Cards. In zoomed-video mode 23 pins are used for routing the zoomed video signals too the VGA controller.

XCPS016-DECEMBER 1997

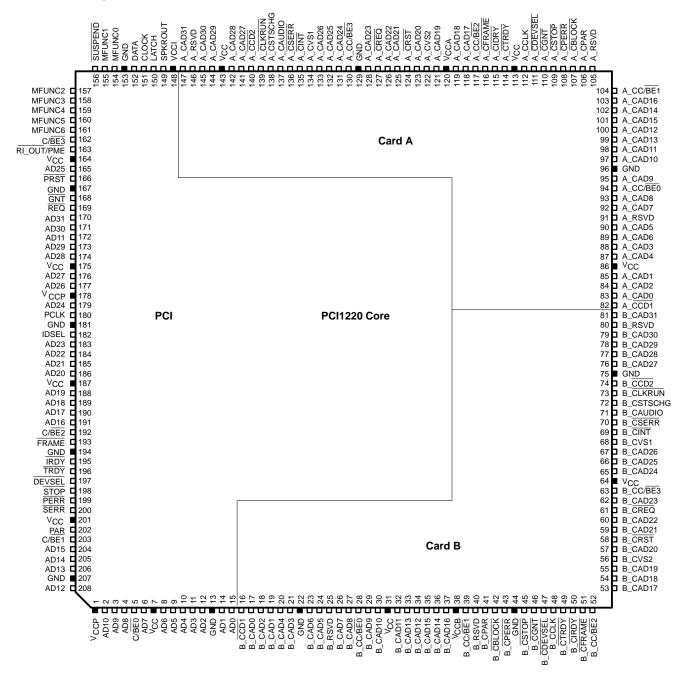

#### terminal assignments

PCI-to-CardBus Pin Diagram

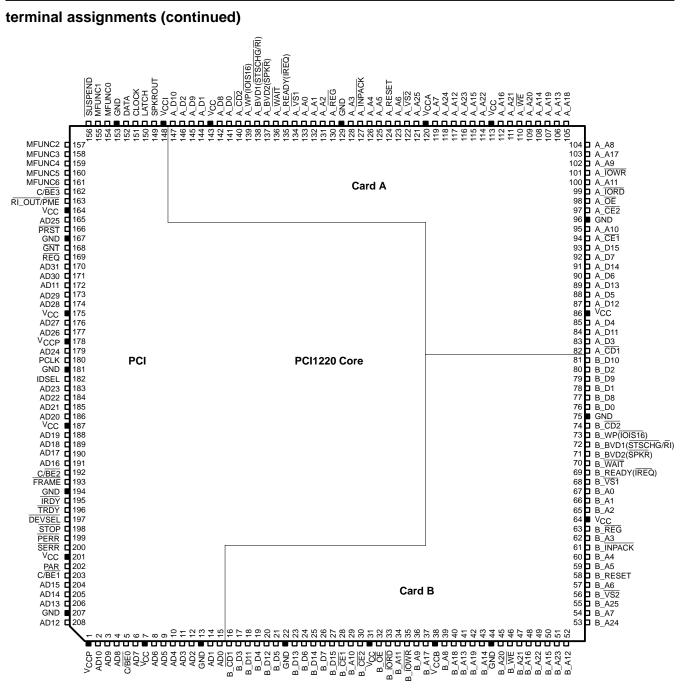

PCI-to-PC Card (16-Bit) Diagram

#### 5

### PCI1220 PC CARD CONTROLLER

XCPS016-DECEMBER 1997

XCPS016-DECEMBER 1997

#### **Terminal Functions**

The terminals are grouped in tables by functionality, such as PCI system function, power-supply function, etc. The terminal numbers are also listed for convenient reference.

#### power supply

|                  | TERMINAL                                            | FUNCTION                                                                                        |  |  |

|------------------|-----------------------------------------------------|-------------------------------------------------------------------------------------------------|--|--|

| NAME             | NO.                                                 | FUNCTION                                                                                        |  |  |

| GND              | 13, 22, 44, 75, 96, 129, 153,<br>167, 181, 194, 207 | Device ground terminals                                                                         |  |  |

| VCC              | 7, 31, 64, 86, 113, 143, 164,<br>175, 187, 201      | Power supply terminal for core logic (3.3 V)                                                    |  |  |

| VCCA             | 120                                                 | Rail power input for PC Card A interface. Indicates Card A signaling environment, 5 V or 3.3 V. |  |  |

| V <sub>CCB</sub> | 38                                                  | Rail power input for PC Card B interface. Indicates Card B signaling environment, 5 V or 3.3 V. |  |  |

| VCCI             | 148                                                 | Rail power input for interrupt subsystem interface and miscellaneous I/O. (5 V or $3.3$ V)      |  |  |

| VCCP             | 1, 178                                              | Rail power input for PCI signaling (5 V or 3.3 V)                                               |  |  |

#### PC Card power switch

| TERMI<br>NAME | NAL<br>NO. | I/O<br>TYPE | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------------|------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLOCK         | 151        | I/O         | <ul> <li>3-Line Power Switch Clock. Information on the DATA line is sampled at the rising edge of CLOCK.</li> <li>CLOCK defaults to an input, but can be changed to a PCI1220 output by using the P2CCLK bit in the System Control Register. The TPS2206 defines the maximum frequency of this signal to be 2MHz.</li> <li>If a system design defines this terminal an output, then this terminal requires an external pullup resister.</li> <li>The frequency of the PCI1220 output CLOCK is derived from dividing the PCI CLK by 36.</li> </ul> |

| DATA          | 152        | 0           | 3-Line Power Switch Data. DATA is used to serially communicate socket power control information to the power switch.                                                                                                                                                                                                                                                                                                                                                                                                                              |

| LATCH         | 150        | 0           | 3-Line Power Switch Latch. LATCH is asserted by the PCI1220 to indicate to the PC Card power switch that the data on the DATA line is valid. When a pulldown resitor is implemented on this terminal, the MFUNC4 and MFUNC1 terminals provide the serial EEPROM SCL and SDA interface.                                                                                                                                                                                                                                                            |

#### **PCI system**

| TERMI | NAL | I/O  | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------|-----|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME  | NO. | TYPE | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| PCLK  | 180 | Ι    | PCI bus clock. PCLK provides timing for all transactions on the PCI bus. All PCI signals are sampled at the rising edge of PCLK.                                                                                                                                                                                                                                                                                                                                                                                  |

| PRST  | 166 | I    | PCI reset. When the PCI bus reset is asserted, PRST causes the PCI1220 to place all output buffers in a high-impedance state and reset all internal registers. When PRST is asserted, the device is completely nonfunctional. After PRST is deasserted, the PCI1220 is in its default state.<br>When the SUSPEND and PRST are asserted, the device is protected from the PRST clearing the internal registers. All outputs are placed in a high-impedance state, but the contents of the registers are preserved. |

XCPS016-DECEMBER 1997

### **Terminal Functions (Continued)**

#### PCI address and data

| TERM                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | TERMINAL I/O                                                                                                                                                                                                |      | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | NO.                                                                                                                                                                                                         | TYPE |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| AD31<br>AD30<br>AD29<br>AD28<br>AD27<br>AD26<br>AD25<br>AD24<br>AD23<br>AD22<br>AD21<br>AD20<br>AD19<br>AD18<br>AD17<br>AD16<br>AD15<br>AD14<br>AD13<br>AD12<br>AD11<br>AD10<br>AD9<br>AD8<br>AD7<br>AD6<br>AD5<br>AD4<br>AD3<br>AD2<br>AD1<br>AD0<br>AD5<br>AD4<br>AD3<br>AD2<br>AD1<br>AD0<br>AD5<br>AD4<br>AD3<br>AD2<br>AD1<br>AD0<br>AD5<br>AD4<br>AD3<br>AD2<br>AD1<br>AD3<br>AD2<br>AD1<br>AD3<br>AD2<br>AD1<br>AD1<br>AD1<br>AD1<br>AD1<br>AD1<br>AD1<br>AD1<br>AD1<br>AD1 | 170<br>171<br>173<br>174<br>176<br>177<br>165<br>179<br>183<br>184<br>185<br>186<br>188<br>189<br>190<br>191<br>204<br>205<br>206<br>208<br>172<br>2<br>3<br>4<br>6<br>8<br>9<br>10<br>11<br>12<br>14<br>15 | I/O  | PCI address/data bus. These signals make up the multiplexed PCI address and data bus on the primary interface.<br>During the address phase of a primary bus PCI cycle, AD31–AD0 contain a 32-bit address or other destination<br>information. During the data phase, AD31–AD0 contain data.                                                                                                                                                                                                             |

| C/ <u>BE3</u><br>C/ <u>BE2</u><br>C/ <u>BE1</u><br>C/BE0                                                                                                                                                                                                                                                                                                                                                                                                                           | 162<br>192<br>203<br>5                                                                                                                                                                                      | I/O  | PCI bus commands and byte enables. These signals are multiplexed on the same PCI terminals. During the address phase of a primary bus PCI cycle, C/BE3–C/BE0 define the bus command. During the data phase, this 4-bit bus is used as byte enables. The byte enables determine which byte paths of the full 32-bit data bus carry meaningful data. C/BE0 applies to byte 0 (AD7–AD0), C/BE1 applies to byte 1 (AD15–AD8), C/BE2 applies to byte 2 (AD23–AD16), and C/BE3 applies to byte 3 (AD31–AD24). |

| PAR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 202                                                                                                                                                                                                         | I/O  | PCI bus parity. In all PCI bus read and write cycles, the PCI1220 calculates even parity across the AD31–AD0 and C/BE3–C/BE0 buses. As an initiator during PCI cycles, the PCI1220 outputs this parity indicator with a one-PCLK delay. As a target during PCI cycles, the calculated parity is compared to the initiator's parity indicator. A compare error results in the assertion of a parity error (PERR).                                                                                        |

XCPS016-DECEMBER 1997

### **Terminal Functions (Continued)**

### **PCI** interface control

| TERMIN | TERMINAL |      | FUNCTION                                                                                                                                                                                                                                                                                                                                                                             |

|--------|----------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME   | NO.      | TYPE | FUNCTION                                                                                                                                                                                                                                                                                                                                                                             |

| DEVSEL | 197      | I/O  | PCI device select. The PCI1220 asserts DEVSEL to claim a PCI cycle as the target device. As a PCI initiator on the bus, the PCI1220 monitors DEVSEL until a target responds. If no target responds before timeout occurs, the PCI1220 terminates the cycle with an initiator abort.                                                                                                  |

| FRAME  | 193      | I/O  | PCI cycle frame. FRAME is driven by the initiator of a bus cycle. FRAME is asserted to indicate that a bus transaction is beginning, and data transfers continue while this signal is asserted. When FRAME is deasserted, the PCI bus transaction is in the final data phase.                                                                                                        |

| GNT    | 168      | I    | PCI bus grant. GNT is driven by the PCI bus arbiter to grant the PCI1220 access to the PCI bus after the current data transaction has completed. GNT may or may not follow a PCI bus request, depending on the PCI bus parking algorithm.                                                                                                                                            |

| IDSEL  | 182      | I    | Initialization device select. IDSEL selects the PCI1220 during configuration space accesses. IDSEL can be connected to one of the upper 24 PCI address lines on the PCI bus.                                                                                                                                                                                                         |

| IRDY   | 195      | I/O  | PCI initiator ready. IRDY indicates the PCI bus initiator's ability to complete the current data phase of the transaction. A data phase is completed on a rising edge of PCLK where both IRDY and TRDY are asserted. Until IRDY and TRDY are both sampled asserted, wait states are inserted.                                                                                        |

| PERR   | 199      | I/O  | PCI parity error indicator. PERR is driven by a PCI device to indicate that calculated parity does not match PAR when PERR is enabled through bit 6 of the command register.                                                                                                                                                                                                         |

| REQ    | 169      | 0    | PCI bus request. REQ is asserted by the PCI1220 to request access to the PCI bus as an initiator.                                                                                                                                                                                                                                                                                    |

| SERR   | 200      | ο    | PCI system error. SERR is an output that is pulsed from the PCI1220 when enabled through the command register indicating a system error has occurred. The PCI1220 need not be the target of the PCI cycle to assert this signal. When SERR is enabled in the control register, this signal also pulses, indicating that an address parity error has occurred on a CardBus interface. |

| STOP   | 198      | I/O  | PCI cycle stop signal. STOP is driven by a PCI target to request the initiator to stop the current PCI bus transaction. STOP is used for target disconnects and is commonly asserted by target devices that do not support burst data transfers.                                                                                                                                     |

| TRDY   | 196      | I/O  | PCI target ready. TRDY indicates the primary bus target's ability to complete the current data phase of the transaction. A data phase is completed on a rising edge of PCLK when both IRDY and TRDY are asserted. Until both IRDY and TRDY are asserted, wait states are inserted.                                                                                                   |

XCPS016-DECEMBER 1997

#### **Terminal Functions (Continued)**

#### multifunction and miscellaneous pins

| TERMINA<br>NAME | NO. | I/O<br>TYPE | FUNCTION                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                               |

|-----------------|-----|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MFUNC6          | 161 | I/O         | Multifunction Terminal 6. MFUNC6 can be configured as a PCI CLKRUN or a parallel IRQ.                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                               |

| MFUNC5          | 160 | I/O         | Multifunction Terminal 5. MFUNC5 can be configured as PC/PCI DMA Grant, GPI4, GPO4, socket activity LED output, ZV switching outputs, CardBus audio PWM, GPE, or a parallel IRQ.                                                                                                                                              |                                                                                                                                                                                                                                                                                               |

|                 |     |             | Multifunction Terminal 4. MFUNC4 can be configured as PCI LOCK, GPI3, GPO3, socket activity LED output, ZV switching outputs, CardBus audio PWM, GPE, or a parallel IRQ.                                                                                                                                                      |                                                                                                                                                                                                                                                                                               |

| MFUNC4          | 159 | I/O         | Serial Clock (SCL). When the serial bus mode is implemented by pulling the LATCH terminal low, the MFUNC4 terminal provides the SCL signaling. The two pin serial interface is used to load the subsystem identification and other register defaults from an EEPROM after a PCI reset.                                        |                                                                                                                                                                                                                                                                                               |

| MFUNC3          | 158 | I/O         | Multifunction Terminal 3. MFUNC3 can be configured as a parallel IRQ or the serialized interrupt signal IRQSER.                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                               |

| MFUNC2          | 157 | I/O         | Multifunction Terminal 2. MFUNC2 can be configured as PC/PCI DMA Request, GPI2, GPO2, socket activity LED output, ZV switching outputs, CardBus audio PWM, GPE, or a parallel IRQ.                                                                                                                                            |                                                                                                                                                                                                                                                                                               |

| MFUNC1          | 155 | 155         | I/O                                                                                                                                                                                                                                                                                                                           | Multifunction Terminal 1. MFUNC1 can be configured as parallel PCI interrupt INTB, GPI1, GPO1, socket activity LED output, ZV switching outputs, CardBus audio PWM, GPE, or a parallel IRQ. Serial Data (SDA). When the serial bus mode is implemented by pulling the LATCH terminal low, the |

|                 |     |             | MFUNC1 terminal provides the SDA signaling. The two pin serial interface is used to load the subsystem identification and other register defaults from an EEPROM after a PCI reset.                                                                                                                                           |                                                                                                                                                                                                                                                                                               |

| MFUNC0          | 154 | I/O         | Multifunction Terminal 0. MFUNC0 can be configured as parallel PCI interrupt INTA, GPI0, GPO0, socket activity LED output, ZV switching outputs, CardBus audio PWM, GPE, or a parallel IRQ.                                                                                                                                   |                                                                                                                                                                                                                                                                                               |

| RI_OUT/PME      | 163 | 0           | Ring Indicate Output and Power Management Event. When configured by the <i>Card Control Register</i> as PME, this terminal is used to indicate that a power management event is occuring. If the ring indicate function is enabled by the <i>Card Control Register</i> , the ring indicate signal is output on this terminal. |                                                                                                                                                                                                                                                                                               |

| SUSPEND         | 156 | I           | Suspend. SUSPEND is used to protect the internal registers from clearing when the PRST signal is asserted.                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                               |

| SPKROUT         | 149 | 0           | Speaker output. SPKROUT is the output to the host system that can carry SPKR or CAUDIO through the PCI1220 from the PC Card interface. SPKROUT is driven as the exclusive-OR combination of card SPKR//CAUDIO inputs.                                                                                                         |                                                                                                                                                                                                                                                                                               |

XCPS016 - DECEMBER 1997

#### **Terminal Functions (Continued)**

| TE         | RMINAL     | _        |      |                                                                                 |

|------------|------------|----------|------|---------------------------------------------------------------------------------|

|            | N          | o.       | I/O  | FUNCTION                                                                        |

| NAME       | SLOT       |          | TYPE | FUNCTION                                                                        |

|            | <b>A</b> † | в‡       |      |                                                                                 |

| A25        | 121        | 55       |      |                                                                                 |

| A24<br>A23 | 118<br>116 | 53<br>51 |      |                                                                                 |

| A23<br>A22 | 114        | 49       |      |                                                                                 |

| A21        | 111        | 47       |      |                                                                                 |

| A20        | 109        | 45       |      |                                                                                 |

| A19        | 107        | 42       |      |                                                                                 |

| A18        | 105        | 40       |      |                                                                                 |

| A17        | 103        | 37       |      |                                                                                 |

| A16        | 112        | 48       |      |                                                                                 |

| A15        | 115        | 50       |      |                                                                                 |

| A14        | 108        | 43       | ο    |                                                                                 |

| A13<br>A12 | 106<br>117 | 41<br>52 |      | PC Card address. 16-bit PC Card address lines. A25 is the most-significant bit. |

| A12<br>A11 | 100        | 32<br>34 |      |                                                                                 |

| A10        | 95         | 29       |      |                                                                                 |

| A9         | 102        | 36       |      |                                                                                 |

| A8         | 104        | 39       |      |                                                                                 |

| A7         | 119        | 54       |      |                                                                                 |

| A6         | 123        | 57       |      |                                                                                 |

| A5         | 125        | 59       |      |                                                                                 |

| A4         | 126        | 60<br>60 |      |                                                                                 |

| A3<br>A2   | 128<br>131 | 62<br>65 |      |                                                                                 |

| A2<br>A1   | 132        | 66       |      |                                                                                 |

| AO         | 133        | 67       |      |                                                                                 |

| D15        | 93         | 27       |      |                                                                                 |

| D14        | 91         | 25       |      |                                                                                 |

| D13        | 89         | 23       |      |                                                                                 |

| D12        | 87         | 20       |      |                                                                                 |

| D11        | 84         | 18       |      |                                                                                 |

| D10        | 147        | 81       |      |                                                                                 |

| D9<br>D8   | 145<br>142 | 79<br>77 |      |                                                                                 |

| D8<br>D7   | 92         | 77<br>26 | I/O  | PC Card data. 16-bit PC Card data lines. D15 is the most-significant bit.       |

| D6         | 92<br>90   | 20       |      |                                                                                 |

| D5         | 88         | 21       |      |                                                                                 |

| D4         | 85         | 19       |      |                                                                                 |

| D3         | 83         | 17       |      |                                                                                 |

| D2         | 146        | 80       |      |                                                                                 |

| D1         | 144        | 78       |      |                                                                                 |

| D0         | 141        | 76       |      |                                                                                 |

#### 16-bit PC Card address and data (slots A and B)

<sup>†</sup> Terminal name for slot A is preceded with A\_. For example, the full name for terminal 121 is A\_A25.

<sup>‡</sup> Terminal name for slot B is preceded with B\_. For example, the full name for terminal 55 is B\_A25.

XCPS016-DECEMBER 1997

#### **Terminal Functions (Continued)**

#### 16-bit PC Card interface control (slots A and B)

| TERMINAL            |           |            |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------------------|-----------|------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                |           | O.<br>SLOT | I/O<br>TYPE | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                     | AT        | B‡         |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| BVD1<br>(STSCHG/RI) | 138       | 72         | I           | Battery voltage detect 1. BVD1 is generated by 16-bit memory PC Cards that include batteries.<br>BVD1 is used with BVD2 as an indication of the condition of the batteries on a memory PC Card.<br>Both BVD1 and BVD2 are kept high when the battery is good. When BVD2 is low and BVD1 is high,<br>the battery is weak and should be replaced. When BVD1 is low, the battery is no longer serviceable<br>and the data in the memory PC Card is lost. |

|                     |           |            |             | Status change. STSCHG is used to alert the system to a change in the READY, write protect, or battery voltage dead condition of a 16-bit I/O PC Card.                                                                                                                                                                                                                                                                                                 |

|                     |           |            |             | Ring indicate. RI is used by 16-bit modem cards to indicate a ring detection.                                                                                                                                                                                                                                                                                                                                                                         |

| BVD2                | 407       | 71         |             | Battery voltage detect 2. BVD2 is generated by 16-bit memory PC Cards that include batteries.<br>BVD2 is used with BVD1 as an indication of the condition of the batteries on a memory PC Card.<br>Both BVD1 and BVD2 are high when the battery is good. When BVD2 is low and BVD1 is high, the<br>battery is weak and should be replaced. When BVD1 is low, the battery is no longer serviceable<br>and the data in the memory PC Card is lost.      |

| (SPKR)              | 137       | 71         | I           | Speaker. SPKR is an optional binary audio signal available only when the card and socket have been configured for the 16-bit I/O interface. The audio signals from cards A and B are combined by the PCI1220 and are output on SPKROUT.                                                                                                                                                                                                               |

|                     |           |            |             | DMA request. BVD2 can be used as the DMA request signal during DMA operations to a 16-bit PC Card that supports DMA. The PC Card asserts BVD2 to indicate a request for a DMA operation.                                                                                                                                                                                                                                                              |

| CD1<br>CD2          | 82<br>140 | 16<br>74   | I           | PC Card detect 1 and PC Card detect 2. CD1 and CD2 are internally connected to ground on the PC Card. When a PC Card is inserted into a socket, CD1 and CD2 are pulled low. For signal status, see <i>interface status register</i> .                                                                                                                                                                                                                 |

| CE1<br>CE2          | 94<br>97  | 28<br>30   | 0           | Card enable 1 and card enable 2. CE1 and CE2 enable even- and odd-numbered address bytes. CE1 enables even-numbered address bytes, and CE2 enables odd-numbered address bytes.                                                                                                                                                                                                                                                                        |

| INPACK              | 127       | 61         | I           | Input acknowledge. INPACK is asserted by the PC Card when it can respond to an I/O read cycle at the current address.<br>DMA request. INPACK can be used as the DMA request signal during DMA operations from a 16-bit PC Card that supports DMA. If used as a strobe, the PC Card asserts this signal to indicate a                                                                                                                                  |

|                     |           |            |             | request for a DMA operation.                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                     |           |            |             | I/O read. IORD is asserted by the PCI1220 to enable 16-bit I/O PC Card data output during host I/O read cycles.                                                                                                                                                                                                                                                                                                                                       |

| IORD                | 99        | 33         | 0           | DMA write. IORD is used as the DMA write strobe during DMA operations from a 16-bit PC Card that supports DMA. The PCI1220 asserts IORD during DMA transfers from the PC Card to host memory.                                                                                                                                                                                                                                                         |

| IOWR                | 101       | 35         | 0           | I/O write. IOWR is driven low by the PCI1220 to strobe write data into 16-bit I/O PC Cards during host I/O write cycles.<br>DMA read. IOWR is used as the DMA write strobe during DMA operations from a 16-bit PC Card                                                                                                                                                                                                                                |

|                     |           |            |             | that supports DMA. The PCI1220 asserts IOWR during transfers from host memory to the PC Card.                                                                                                                                                                                                                                                                                                                                                         |

| OE 98               | 98        | 32         | 0           | Output enable. $\overline{OE}$ is driven low by the PCI1220 to enable 16-bit memory PC Card data output during host memory read cycles.                                                                                                                                                                                                                                                                                                               |

|                     |           |            |             | DMA terminal count. OE is used as terminal count (TC) during DMA operations to a 16-bit PC Card that supports DMA. The PCI1220 asserts OE to indicate TC for a DMA write operation.                                                                                                                                                                                                                                                                   |

<sup>†</sup> Terminal name for slot A is preceded with A\_. For example, the full name for terminal 127 is A\_INPACK. <sup>‡</sup> Terminal name for slot B is preceded with B\_. For example, the full name for terminal 61 is B\_INPACK.

XCPS016-DECEMBER 1997

#### **Terminal Functions (Continued)**

#### 16-bit PC Card interface control (slots A and B) (continued)

| TER             | TERMINAL               |                        |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----------------|------------------------|------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 | -                      | IBER                   |      | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| NAME            | SLOT<br>A <sup>†</sup> | SLOT<br>B <sup>‡</sup> | TYPE |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| READY<br>(IREQ) | 135                    | 69                     | -    | Ready. The ready function is provided by READY when the 16-bit PC Card and the host socket are configured for the memory-only interface. READY is driven low by the 16-bit memory PC Cards to indicate that the memory card circuits are busy processing a previous write command. READY is driven high when the 16-bit memory PC Card is ready to accept a new data transfer command. Interrupt request. IREQ is asserted by a 16-bit I/O PC Card to indicate to the host that a device on the 16-bit I /O PC Card requires service by the host software. IREQ is high (deasserted) when no interrupt is requested.                                                                                         |

| REG             | 130                    | 63                     | 0    | Attribute memory select. REG remains high for all common memory accesses. When REG is asserted, access is limited to attribute memory (OE or WE active) and to the I/O space (IORD or IOWR active). Attribute memory is a separately accessed section of card memory and is generally used to record card capacity and other configuration and attribute information.<br>DMA acknowledge. REG is used as a DMA acknowledge (DACK) during DMA operations to a 16-bit PC Card that supports DMA. The PCI1220 asserts REG to indicate a DMA operation. REG is used in conjunction with the DMA read (IOWR) or DMA write (IORD) strobes to transfer data.                                                        |

| RESET           | 124                    | 58                     | 0    | PC Card reset. RESET forces a hard reset to a 16-bit PC Card.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| WAIT            | 136                    | 70                     | Ι    | Bus cycle wait. $\overline{\text{WAIT}}$ is driven by a 16-bit PC Card to delay the completion of (i.e., extend) the memory or I/O cycle in progress.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| WE              | 110                    | 46                     | 0    | Write enable. WE is used to strobe memory write data into 16-bit memory PC Cards. WE is also used for memory PC Cards that employ programmable memory technologies.<br>DMA terminal count. WE is used as TC during DMA operations to a 16-bit PC Card that supports DMA. The PC1220 asserts WE to indicate TC for a DMA read operation.                                                                                                                                                                                                                                                                                                                                                                      |

| WP<br>(IOIS16)  | 139                    | 73                     | I    | <ul> <li>Write protect. WP applies to 16-bit memory PC Cards. WP reflects the status of the write-protect switch on 16-bit memory PC Cards. For 16-bit I/O cards, WP is used for the 16-bit port (IOIS16) function.</li> <li>I/O is 16 bits. IOIS16 applies to 16-bit I/O PC Cards. IOIS16 is asserted by the 16-bit PC Card when the address on the bus corresponds to an address to which the 16-bit PC Card responds, and the I/O port that is addressed is capable of 16-bit accesses.</li> <li>DMA request. WP can be used as the DMA request signal during DMA operations to a 16-bit PC Card that supports DMA. If used, the PC Card asserts WP to indicate a request for a DMA operation.</li> </ul> |

| VS1<br>VS2      | 134<br>122             | 68<br>56               | I/O  | Voltage sense 1 and voltage sense 2. $\overline{VS1}$ and $\overline{VS2}$ , when used in conjunction with each other, determine the operating voltage of the 16-bit PC Card.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

<sup>†</sup> Terminal name for slot A is preceded with A\_. For example, the full name for terminal 110 is A<u>WE</u>.

<sup>+</sup> Terminal name for slot B is preceded with B\_. For example, the full name for terminal 46 is B\_WE.

XCPS016-DECEMBER 1997

#### **Terminal Functions (Continued)**

#### CardBus PC Card interface system (slots A and B)

| TER     | MINAL                  |            |      |                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------|------------------------|------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | N                      | NO.        |      | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                        |

| NAME    | SLOT<br>A <sup>†</sup> | slot<br>b‡ | TYPE | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                        |

| CCLK    | 112                    | 48         | 0    | CardBus PC Card clock. CCLK provides synchronous timing for all transactions on the CardBus interface. All signals except CRST, CCLKRUN, CINT, CSTSCHG, CAUDIO, CCD2:1, and CVS2–CVS1 are sampled on the rising edge of CCLK, and all timing parameters are defined with the rising edge of this signal. CCLK operates at the PCI bus clock frequency, but it can be stopped in the low state or slowed down for power savings. |

| CCLKRUN | 139                    | 73         | 0    | CardBus PC Card clock run. CCLKRUN is used by a CardBus PC Card to request an increase in the CCLK frequency, and by the PCI1220 to indicate that the CCLK frequency is going to be decreased.                                                                                                                                                                                                                                  |

| CRST    | 124                    | 58         | I/O  | CardBus PC Card reset. CRST is used to bring CardBus PC Card-specific registers, sequencers, and signals to a known state. When CRST is asserted, all CardBus PC Card signals must be 3-stated, and the PCI1220 drives these signals to a valid logic level. Assertion can be asynchronous to CCLK, but deassertion must be synchronous to CCLK.                                                                                |

<sup>†</sup> Terminal name for slot A is preceded with A\_. For example, the full name for terminal 112 is A\_CCLK.

<sup>‡</sup> Terminal name for slot B is preceded with B\_. For example, the full name for terminal 48 is B\_CCLK.

XCPS016 - DECEMBER 1997

#### **Terminal Functions (Continued)**

| TERMINAL       |                                                                 |                        |          |                                                                                                                                                                                                          |  |  |  |  |  |

|----------------|-----------------------------------------------------------------|------------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| NO.            |                                                                 | 1/O                    | TUNCTION |                                                                                                                                                                                                          |  |  |  |  |  |

| NAME           | SLOT<br>A <sup>†</sup>                                          | SLOT<br>B <sup>‡</sup> | TYPE     | FUNCTION                                                                                                                                                                                                 |  |  |  |  |  |

| CAD31<br>CAD30 | 147<br>145                                                      | 81<br>79               |          |                                                                                                                                                                                                          |  |  |  |  |  |

| CAD29          | 144                                                             | 78                     |          |                                                                                                                                                                                                          |  |  |  |  |  |

| CAD28          | 142                                                             | 77                     |          |                                                                                                                                                                                                          |  |  |  |  |  |

| CAD27          | 141                                                             | 76                     |          |                                                                                                                                                                                                          |  |  |  |  |  |

| CAD26          | 133                                                             | 67                     |          |                                                                                                                                                                                                          |  |  |  |  |  |

| CAD25          | 132                                                             | 66                     |          |                                                                                                                                                                                                          |  |  |  |  |  |

| CAD24          | 131                                                             | 65                     |          |                                                                                                                                                                                                          |  |  |  |  |  |

| CAD23          | 128                                                             | 62                     |          |                                                                                                                                                                                                          |  |  |  |  |  |

| CAD22          | 126                                                             | 60                     |          |                                                                                                                                                                                                          |  |  |  |  |  |

| CAD21          | 125                                                             | 59                     |          |                                                                                                                                                                                                          |  |  |  |  |  |

| CAD20          | 123                                                             | 57                     |          |                                                                                                                                                                                                          |  |  |  |  |  |

| CAD19          | 121                                                             | 55                     |          |                                                                                                                                                                                                          |  |  |  |  |  |

| CAD18          | 119                                                             | 54                     |          |                                                                                                                                                                                                          |  |  |  |  |  |

| CAD17          | 118                                                             | 53                     |          | PC Card address and data. These signals make up the multiplexed CardBus address and data bus on                                                                                                          |  |  |  |  |  |

| CAD16          | 103                                                             | 37                     | I/O      | the CardBus interface. During the address phase of a CardBus cycle, CAD31-CAD0 contain a 32-bit                                                                                                          |  |  |  |  |  |

| CAD15          | 101                                                             | 35                     | 1/0      | address. During the data phase of a CardBus cycle, CAD31–CAD0 contain data. CAD31 i                                                                                                                      |  |  |  |  |  |

| CAD14          | 102                                                             | 36                     |          | most-significant bit.                                                                                                                                                                                    |  |  |  |  |  |

| CAD13          | 99                                                              | 33                     |          |                                                                                                                                                                                                          |  |  |  |  |  |

| CAD12          | 100                                                             | 34                     |          |                                                                                                                                                                                                          |  |  |  |  |  |

| CAD11          | 98                                                              | 32                     |          |                                                                                                                                                                                                          |  |  |  |  |  |

| CAD10          | 97                                                              | 30                     |          |                                                                                                                                                                                                          |  |  |  |  |  |

| CAD9           | 95                                                              | 29                     |          |                                                                                                                                                                                                          |  |  |  |  |  |

| CAD8           | 93                                                              | 27                     |          |                                                                                                                                                                                                          |  |  |  |  |  |

| CAD7           | 92                                                              | 26                     |          |                                                                                                                                                                                                          |  |  |  |  |  |

| CAD6           | 89                                                              | 23                     |          |                                                                                                                                                                                                          |  |  |  |  |  |

| CAD5           | 90                                                              | 24                     |          |                                                                                                                                                                                                          |  |  |  |  |  |

| CAD4           | 87                                                              | 20                     |          |                                                                                                                                                                                                          |  |  |  |  |  |

| CAD3           | 88                                                              | 21                     |          |                                                                                                                                                                                                          |  |  |  |  |  |

| CAD2           | 84                                                              | 18                     |          |                                                                                                                                                                                                          |  |  |  |  |  |

| CAD1           | 85                                                              | 19                     |          |                                                                                                                                                                                                          |  |  |  |  |  |

| CAD0           | 83                                                              | 17                     |          |                                                                                                                                                                                                          |  |  |  |  |  |

| CC/BE3         | 130                                                             | 63                     |          | CardBus bus commands and byte enables. CC/BE3–CC/BE0 are multiplexed on the same CardBus terminals. During the address phase of a CardBus cycle, CC/BE3–CC/BE0 defines the bus command.                  |  |  |  |  |  |

| CC/BE2         | 117                                                             | 52                     |          | During the data phase, this 4-bit bus is used as byte enables. The byte enables determine which byte                                                                                                     |  |  |  |  |  |

| CC/BE1         | 104                                                             | 39                     | I/O      | paths of the full 32-bit data bus carry meaningful data. CC/BE0 applies to byte 0 (CAD7–CAD0), CC/BE1                                                                                                    |  |  |  |  |  |

| CC/BE0         | 94                                                              | 28                     |          | applies to byte 1 (CAD15–CAD8), CC/BE2 applies to byte 2 (CAD23–CAD8), and CC/BE3 applies to                                                                                                             |  |  |  |  |  |