### TMS320C5000

# How do I work with TI's 'C5000?

#### How do I get my performance?

What performance can I expect?

How do I interface easily?

What are the new 'C5000 devices?

How do I minimize power consumption?

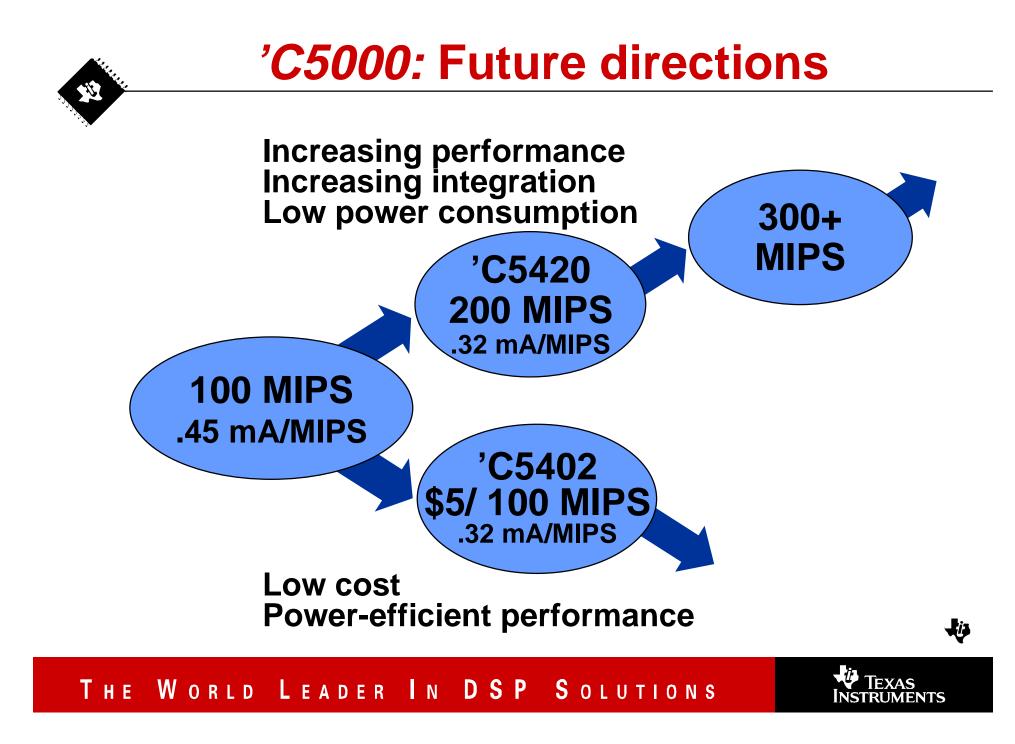

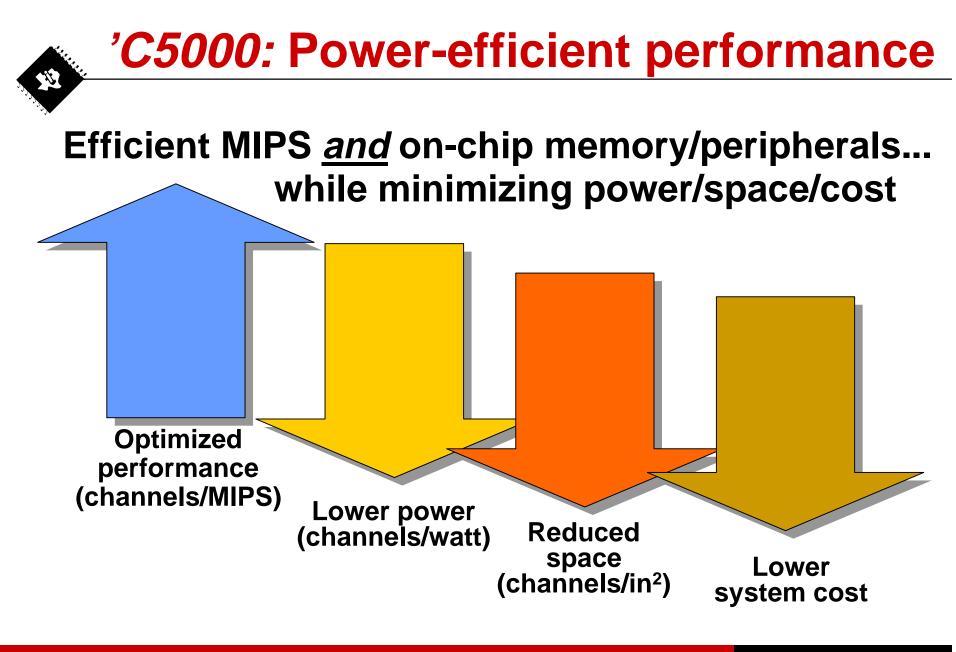

How does TI enable power-efficient performance at lower cost?

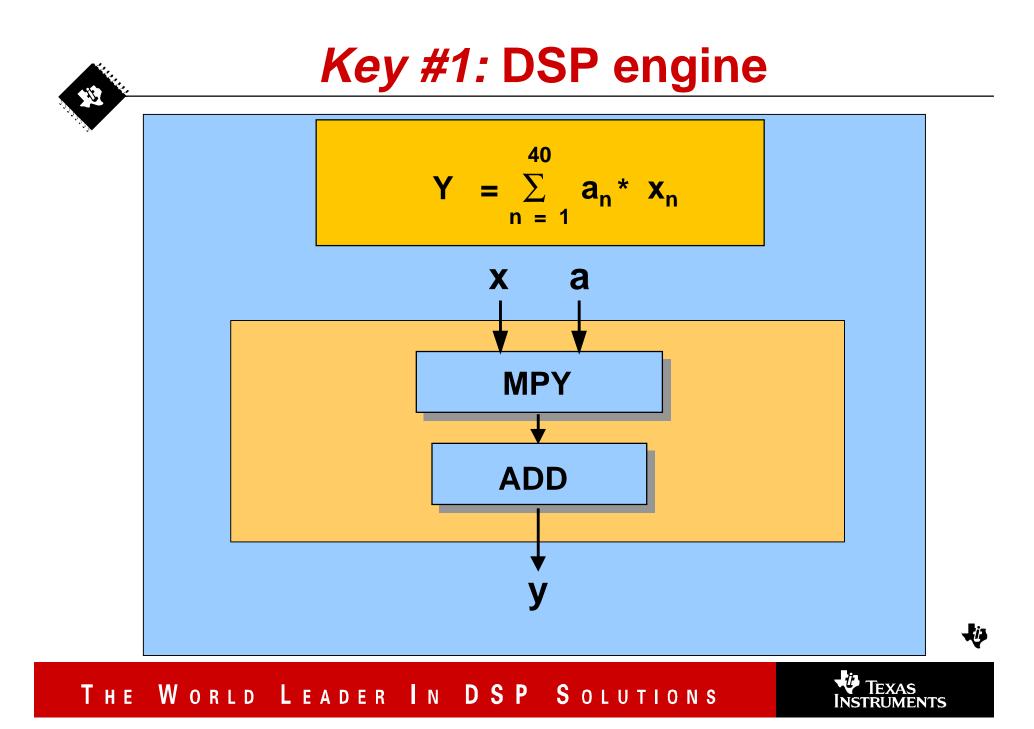

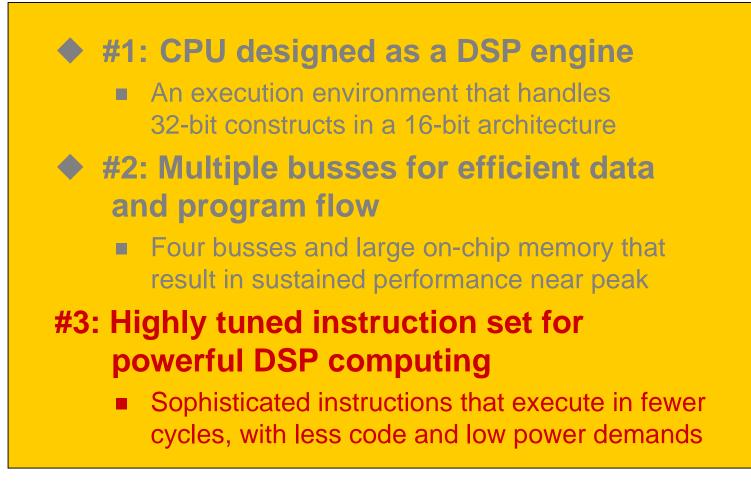

# **Architecture optimized for DSP**

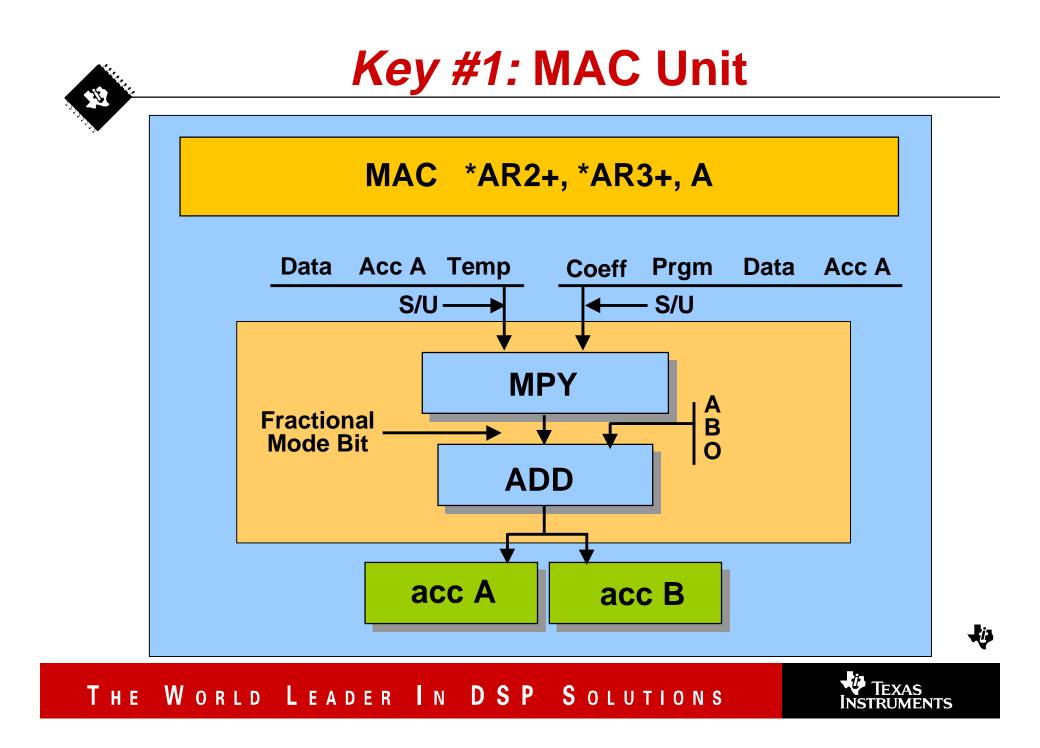

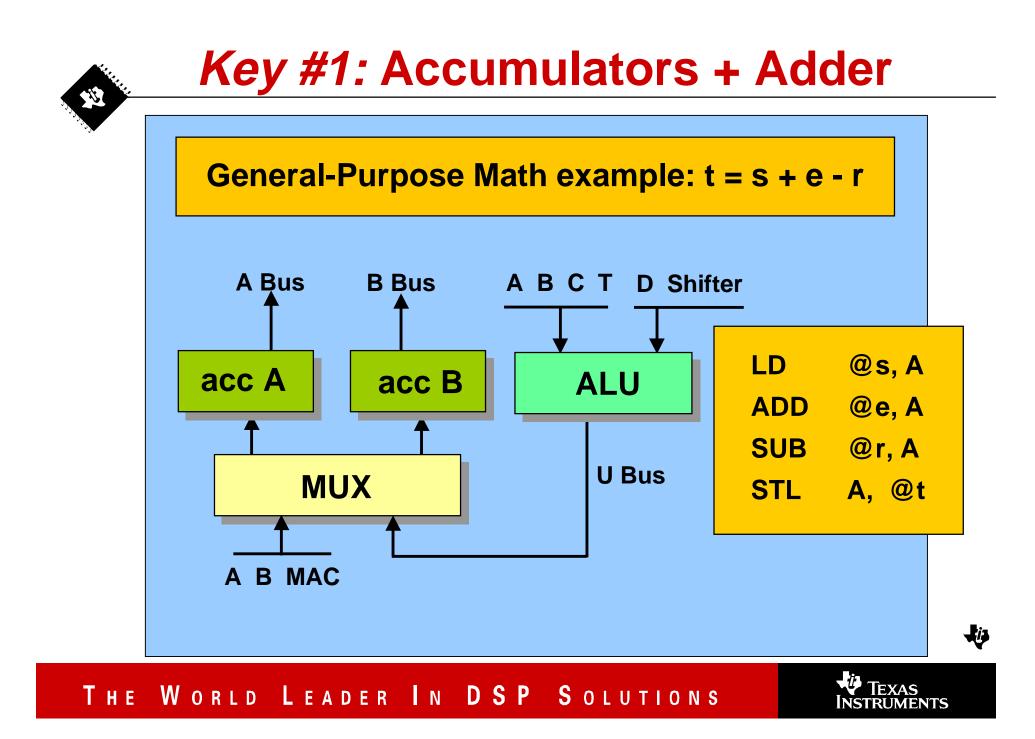

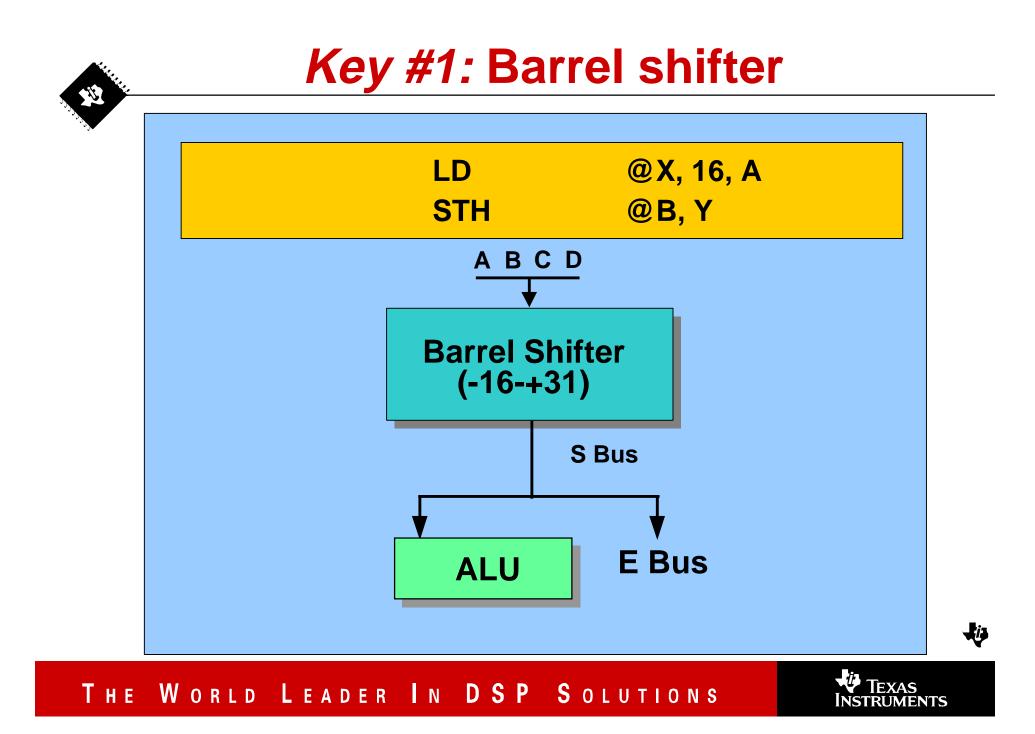

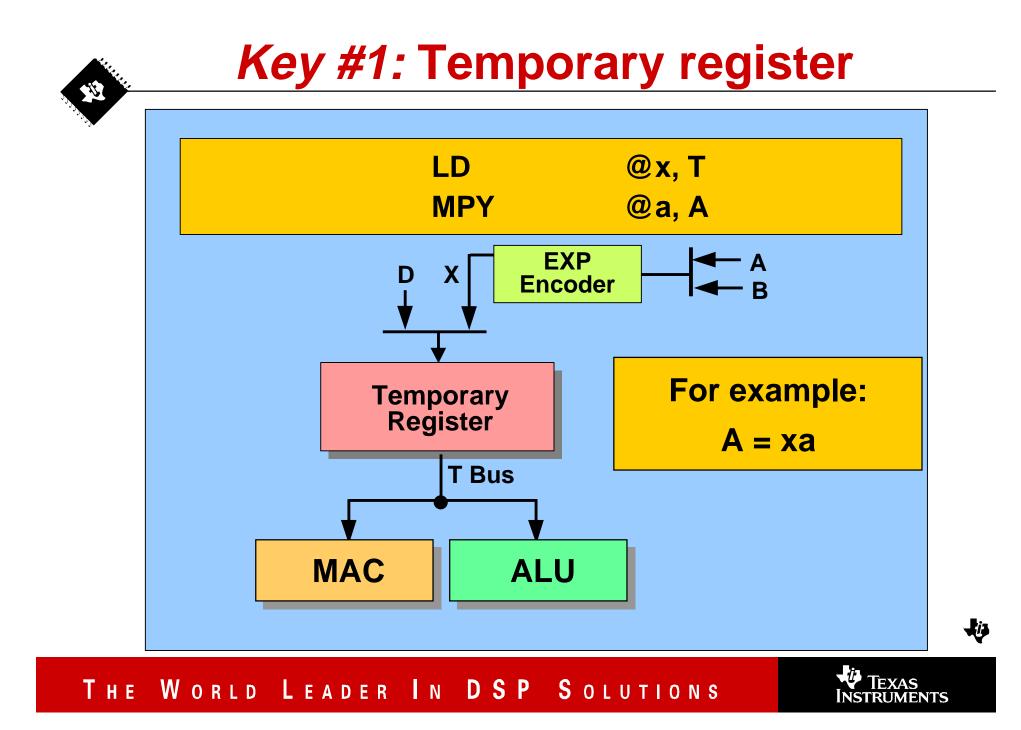

#### **#1: CPU designed as a DSP engine**

- An execution environment that handles

32-bit constructs in a 16-bit architecture

- **#2: Multiple busses for efficient data**

#### and program flow

Four busses and large on-chip memory that result in sustained performance near peak

#### #3: Highly tuned instruction set for powerful DSP computing

Sophisticated instructions that execute in fewer cycles, with less code and low power demands

#### THE WORLD LEADER IN DSP SOLUTIONS

# Key #2: Efficient data/program flow

#### #1: CPU designed as a DSP engine

An execution environment that handles

32-bit constructs in a 16-bit architecture

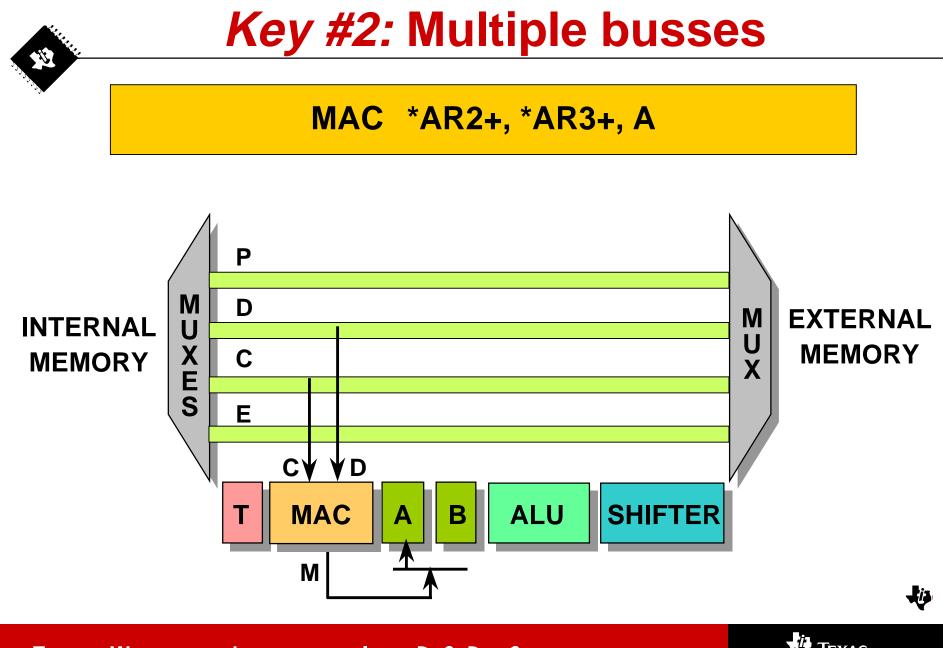

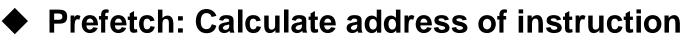

# #2: Multiple busses for efficient data and program flow

Four busses and large on-chip memory that result in sustained performance near peak

#### #3: Highly tuned instruction set for powerful DSP computing

Sophisticated instructions that execute in fewer cycles, with less code and low power demands

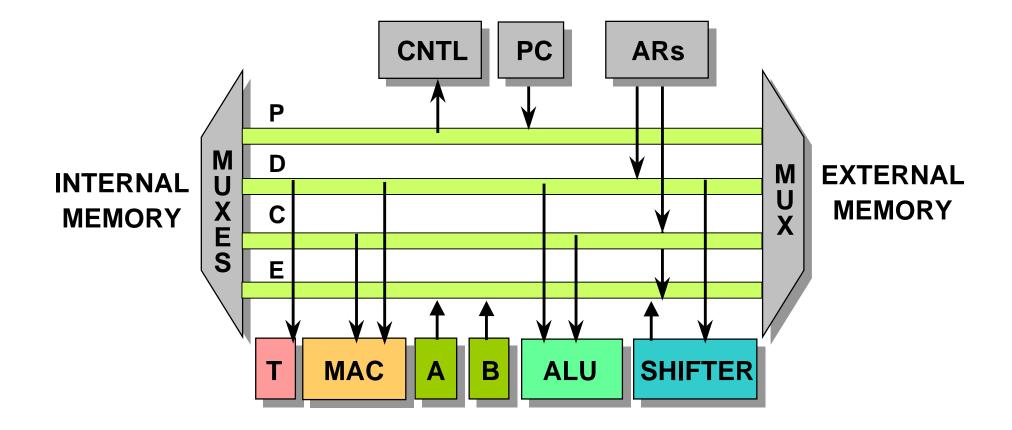

Prefetch Fetch Decode Access Read Execute

- Fetch: Collect instruction

- Decode: Interpret instruction

- Access: Collect address of operand

- Read: Collect operand

- Execute: Perform operation

Key #2: Bus usage

THE WORLD LEADER IN DSP SOLUTIONS

TEXAS INSTRUMENTS **L**ij

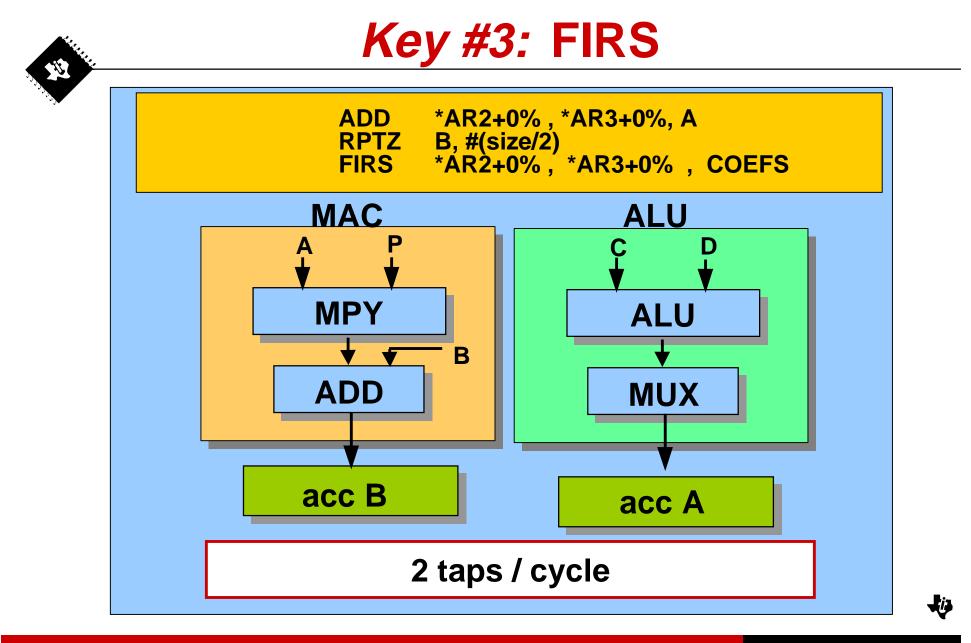

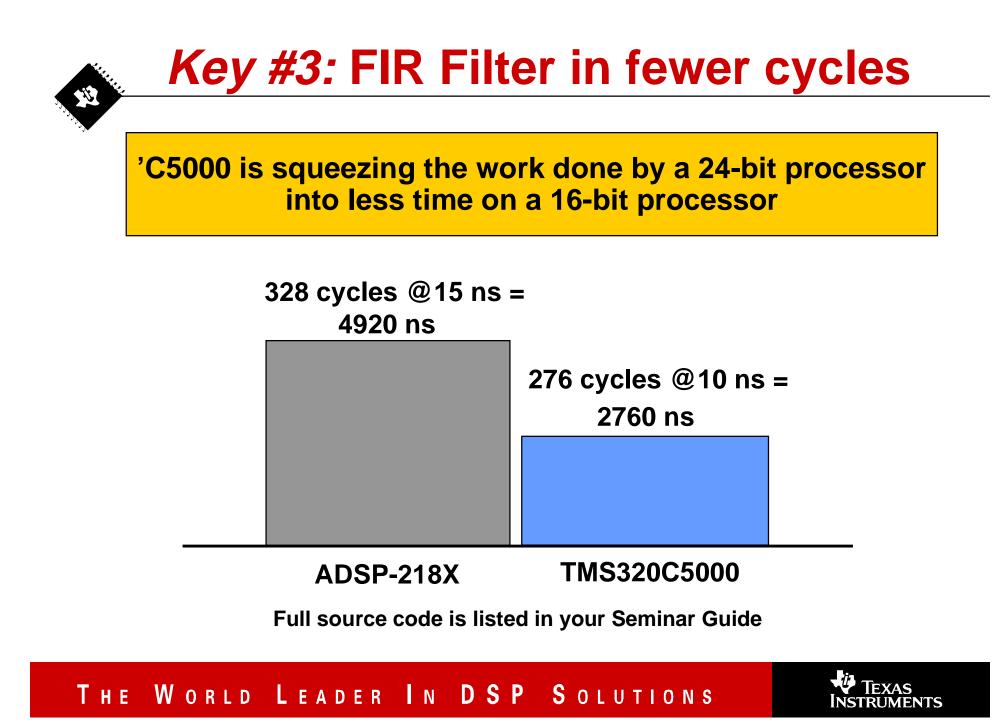

# Key #3: Powerful instructions

####

The general form of this FIR equation is written using 8 Mults, 7 Adds

Y(n) = a0x(8) + a1x(7) + a2x(6) + a3x(5) + a3x(4) + a2x(3) + a1x(2) + a0x(1)

In the specific case of a Symmetric FIR we can use 4 Mults, 7 Adds Y(n) = a0(x(8)+x(1))+a1(x(7)+x(2))+a2(x(6)+x(3))+a3(x(5)+x(4))

THE WORLD LEADER IN DSP SOLUTIONS

TEXAS INSTRUMENTS ŀ

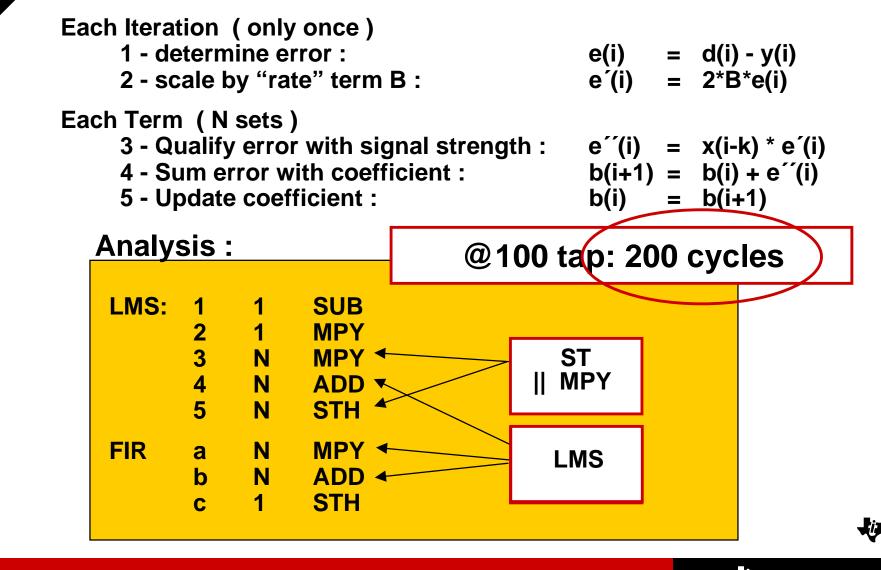

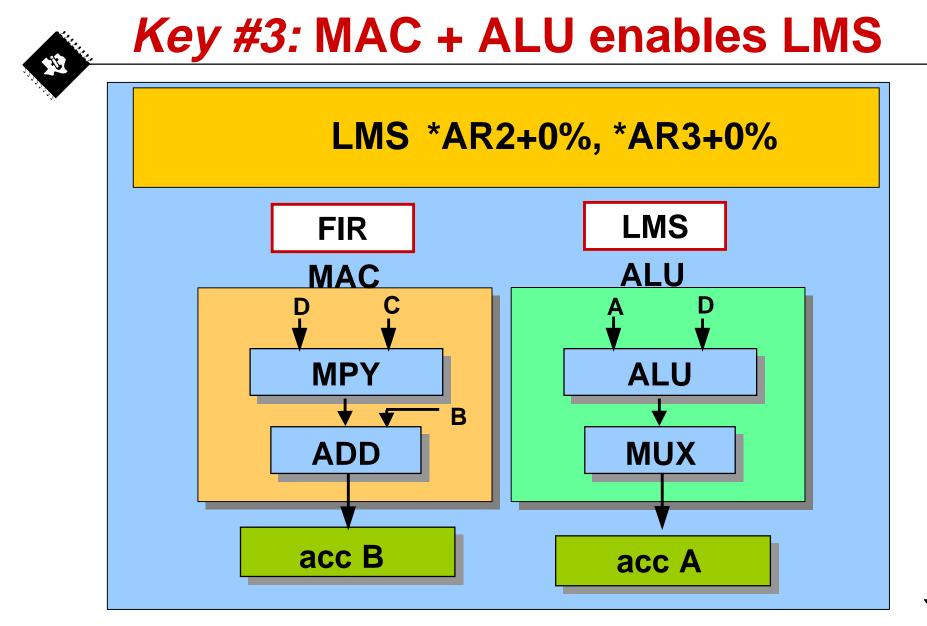

#### *Key #3:* Adaptive FIR filter using LMS ij, **Z**<sup>-1</sup> **Z**<sup>-1</sup> **Z**<sup>-1</sup> **x(n)** ..... **d(n)** b<sub>n-</sub>∕ $\mathbf{b}_1$ b<sub>0</sub> **y(n)** e(n) LMS

FIR type filters are usually used in an adaptive algorithm since they are more tolerant of non-optimal coefficients.

THE WORLD LEADER IN DSP SOLUTIONS

TEXAS INSTRUMENTS Ĭ.

# Key #3: LMS loading

THE WORLD LEADER IN DSP SOLUTIONS

TEXAS INSTRUMENTS

## Key #3: Advanced applications

| *<br>* | Symmetric FIR filter<br>Adaptive filtering | FIRS<br>LMS |

|--------|--------------------------------------------|-------------|

|        | Polynomial evaluation                      | POLY        |

|        | Code book search                           | STRCD       |

|        |                                            | SACCD       |

|        |                                            | SRCCD       |

|        | Viterbi                                    | DADST       |

|        |                                            | DSADT       |

|        |                                            | CMPS        |

THE WORLD LEADER IN DSP SOLUTIONS

# How do I work with TI's 'C5000?

How do I get my performance?

What performance can I expect?

How do I interface easily?What are the new 'C5000 devices?How do I minimize power consumption?How does TI enable power-efficient performance at lower cost?

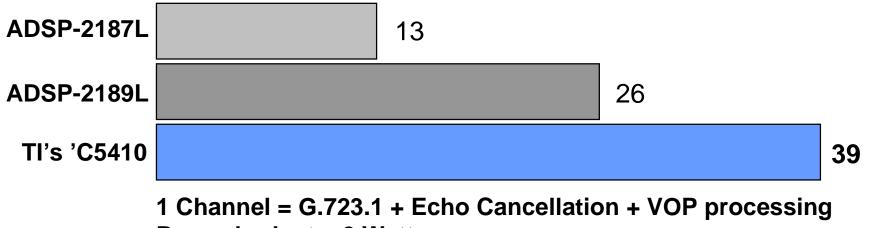

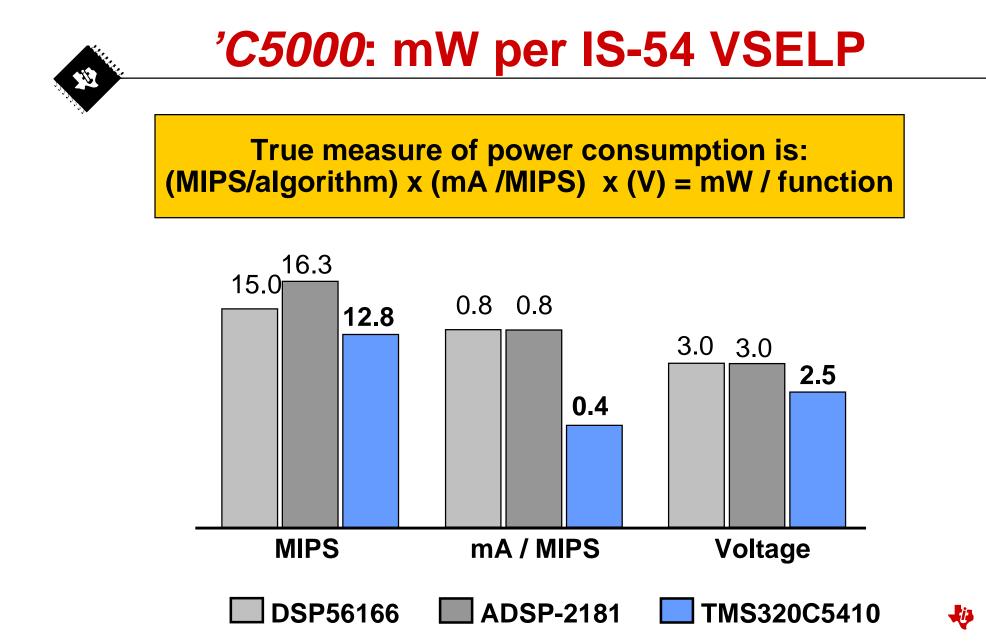

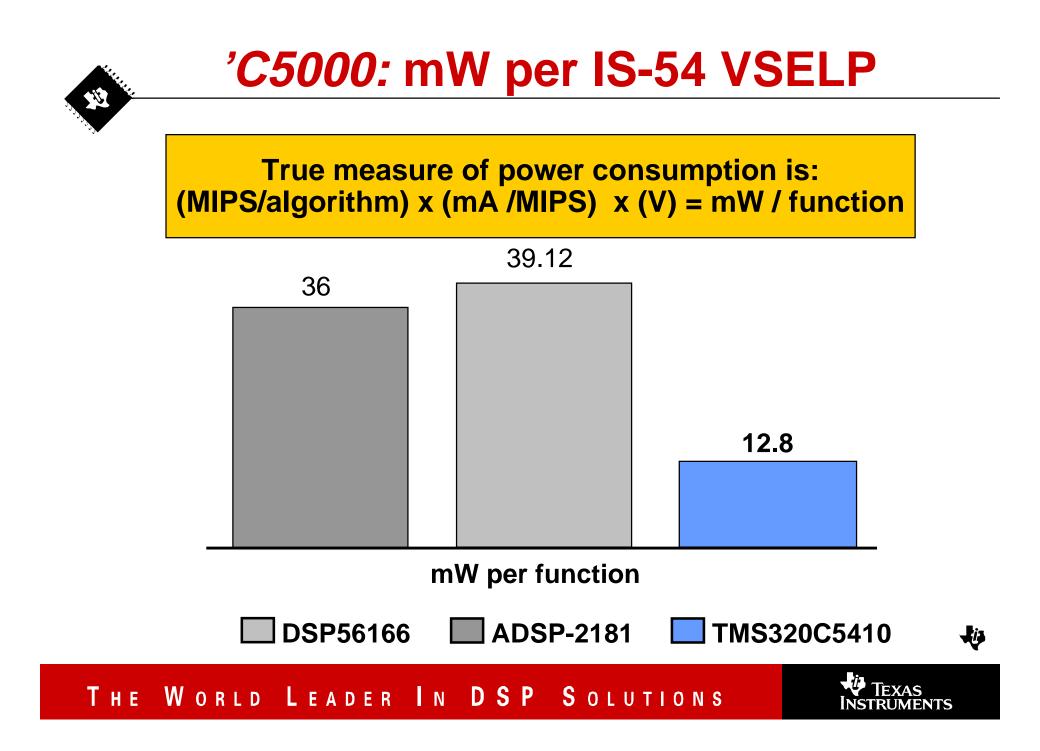

Power budget = 2 Watts

Source: Analog Devices news releases and web site

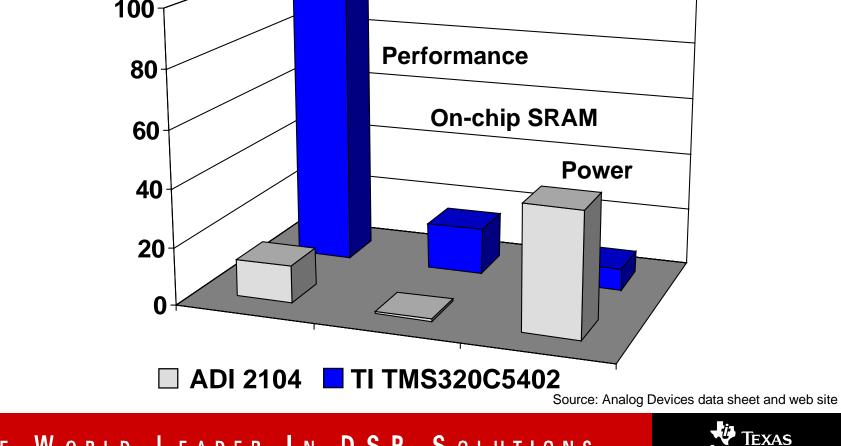

#### 'C5000: Performance per constraint **Competitors are limited by available MIPS** (1 Channel = G.723.1 + Echo Cancellation + VOP processing) 8 CONSTRAINTS 16 **Total MIPS** 18 channels 16 **On-chip** 16 Memory 18 channels 4 \$10/channel 6 **Budget** 18 channels 8 2.35"x1.35" 16 Source: **Analog Devices** Space 18 channels news releases and web site ADSP-2187L ADSP-2189L Lİ P TMS320C5000 **ADSP-2187L ADSP-2189L** THE WORLD LEADER IN DSP SOLUTIONS

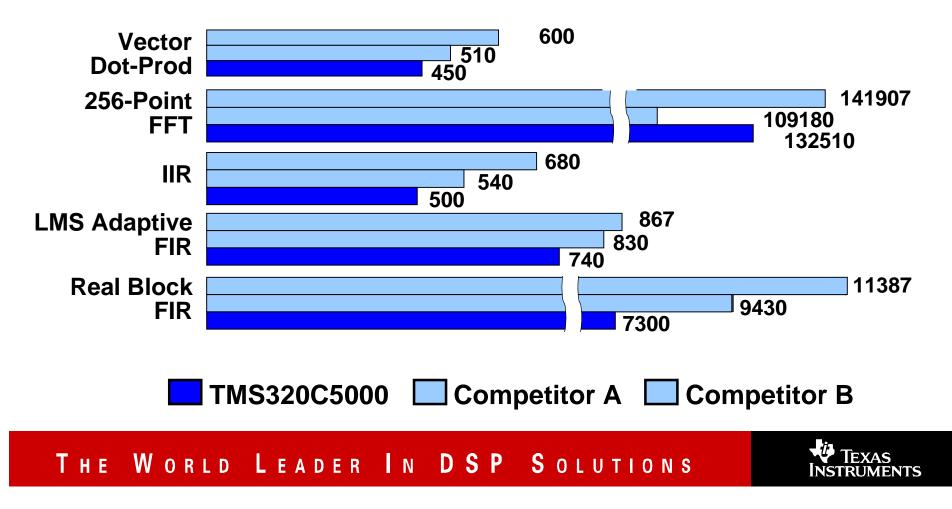

## 'C5000: DSP functions

### Execution Time vs. Major Competitors (in ns.)

Source: Buyer's Guide to DSP Processors, ©1999 BDTI

# Compiler: Lowest cycle count

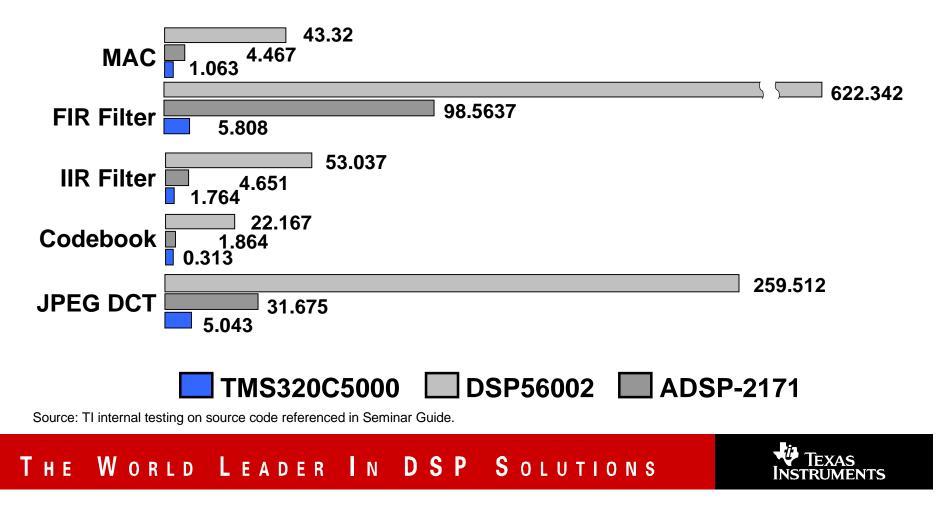

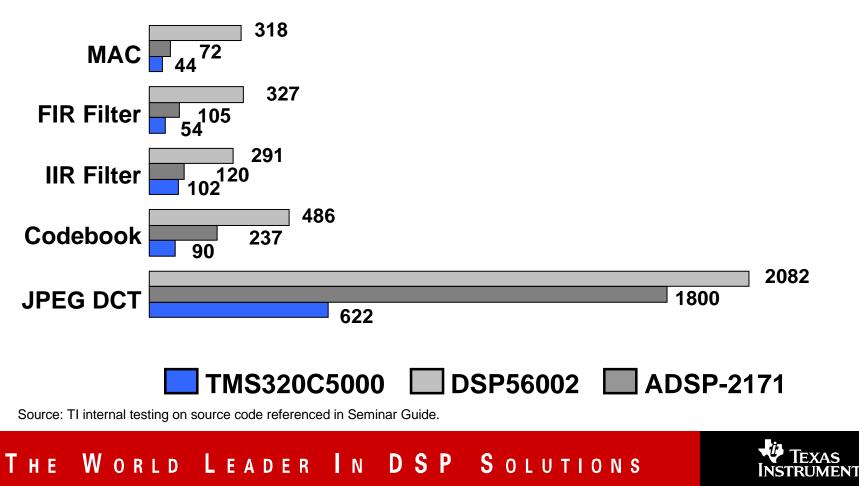

#### **Compiler Performance vs. Competition**

Cycles per task measured over 1000 cycles

### **Compiler Performance vs. Competition**

Measured in bytes

# How do I work with TI's 'C5000?

How do I get my performance? What performance can I expect?

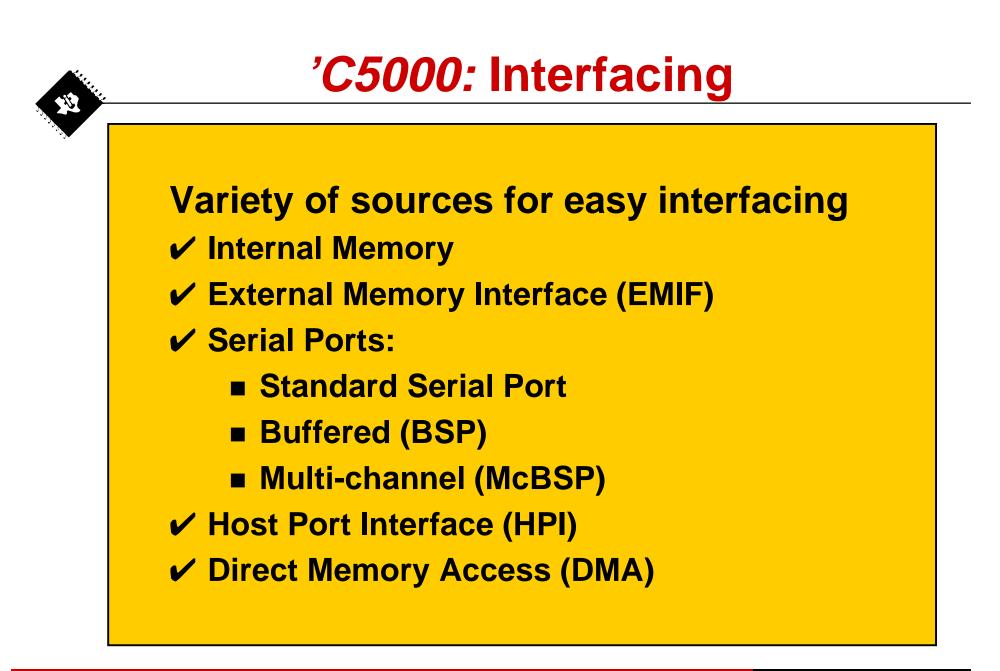

How do I interface easily?

What are the new 'C5000 devices? How do I minimize my power consumption? How does TI enable power-efficient performance at lower cost?

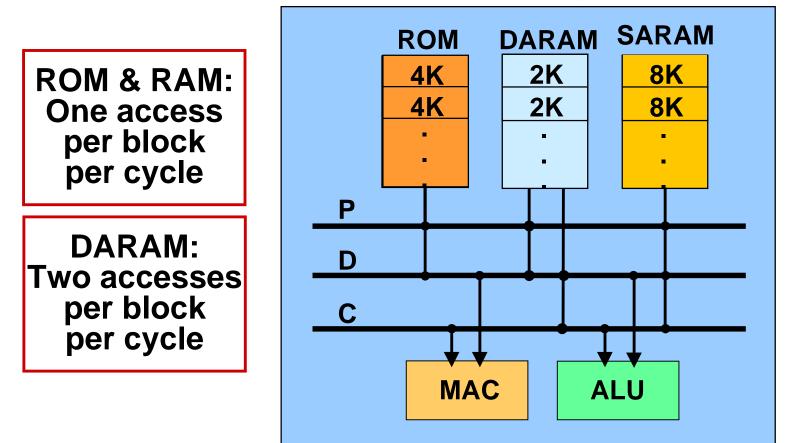

# Interfacing: Internal memory access

#### **Internal Memory Access**

THE WORLD LEADER IN DSP SOLUTIONS

TEXAS INSTRUMENTS - ji

## Interfacing: Memory

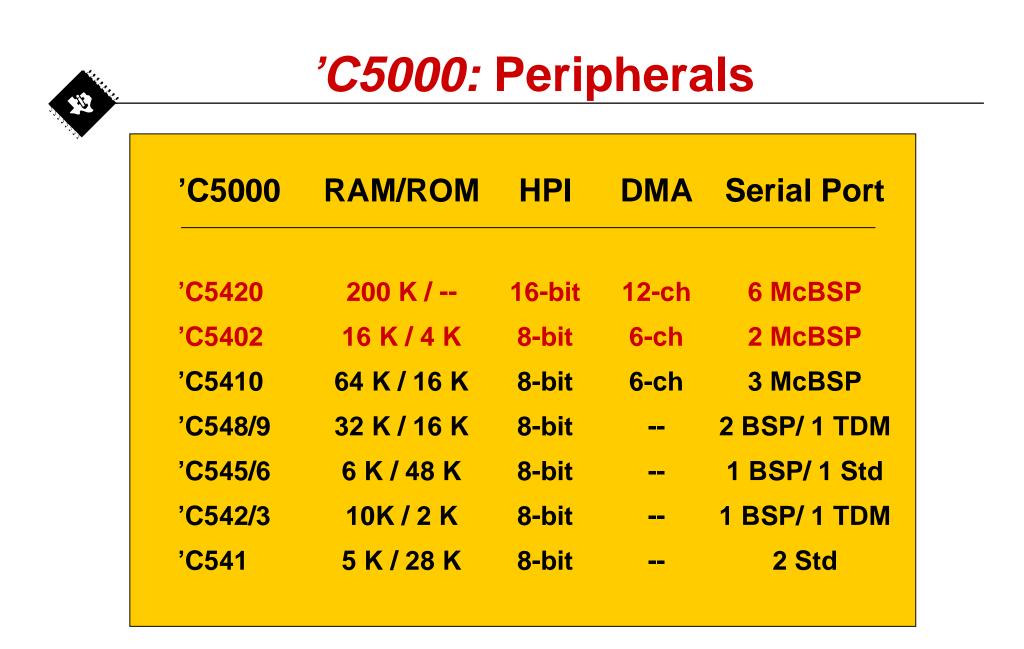

| 'C5000  | DARAM    | SARAM | ROM  |

|---------|----------|-------|------|

| 'C5420  | 32 K     | 168 K |      |

| 'C5402  | 16 K     |       | 4 K  |

| 'C5410  | 8 K      | 56 K  | 16 K |

| 'C549   | 8 K      | 24 K  | 16 K |

| 'C548   | 8 K      | 24 K  | 2 K  |

| 'C545/6 | 6 K      |       | 48 K |

| 'C542/3 | 10K      |       | 2 K  |

| 'C541   | 5 K      |       | 28 K |

|         | 16-bit w | ords  |      |

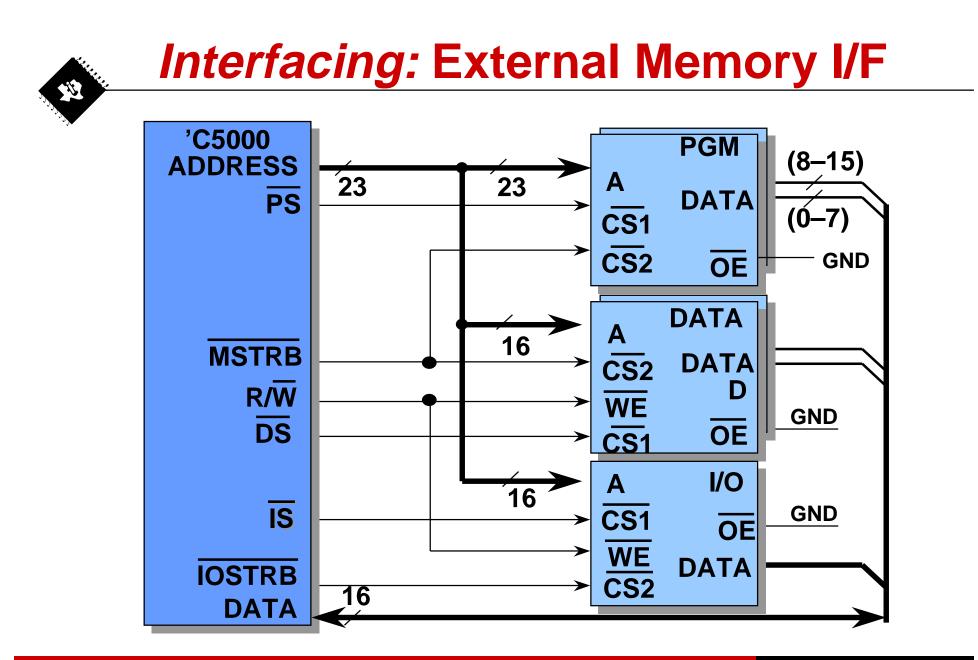

# **EMIF:** Flexible memory I/F

- Typical asynchronous parallel interface

- Separate strobes for program, data and I/O spaces

- 23-bit address range for external program space

- ♦ 0-14 software programmable wait states

- Simplified bank switching -- programmable ability to insert wait states when crossing bank boundaries

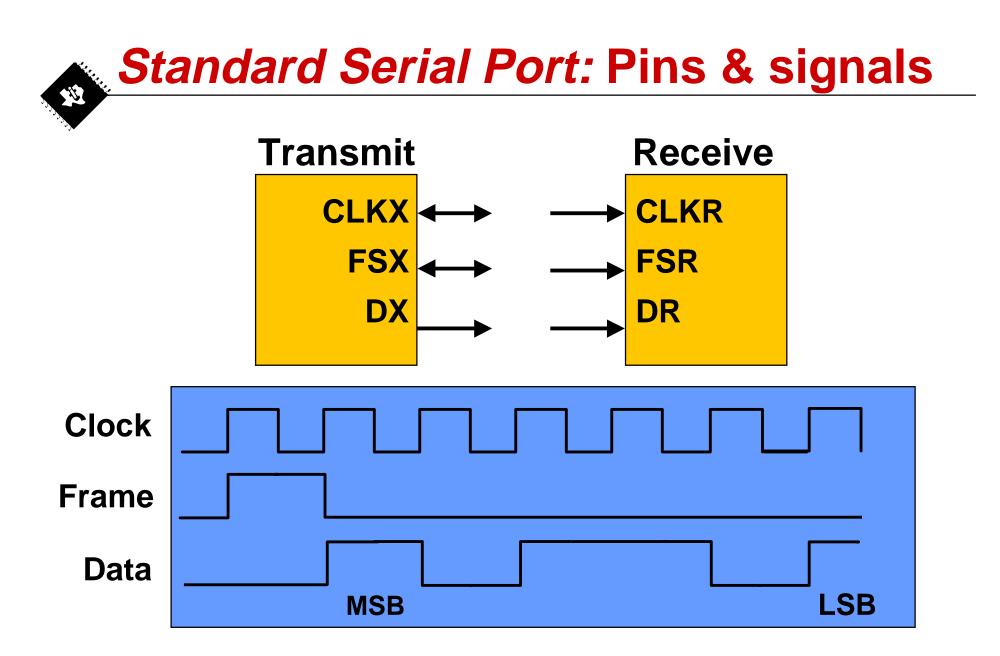

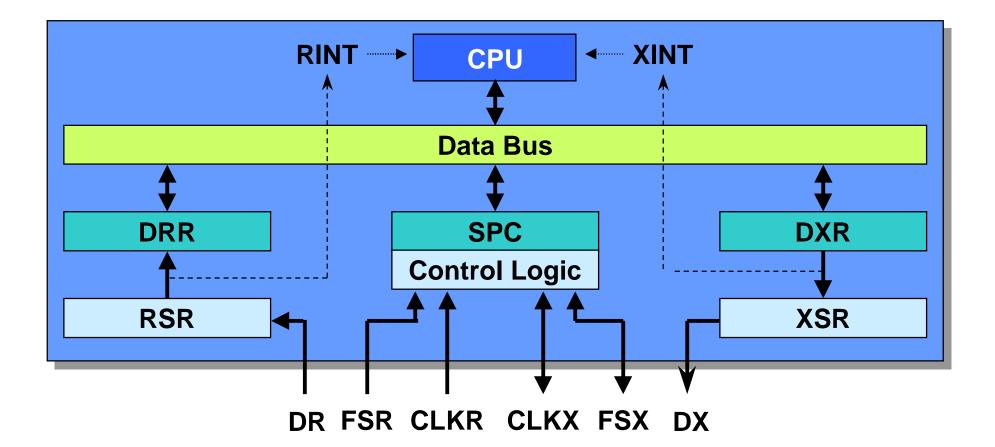

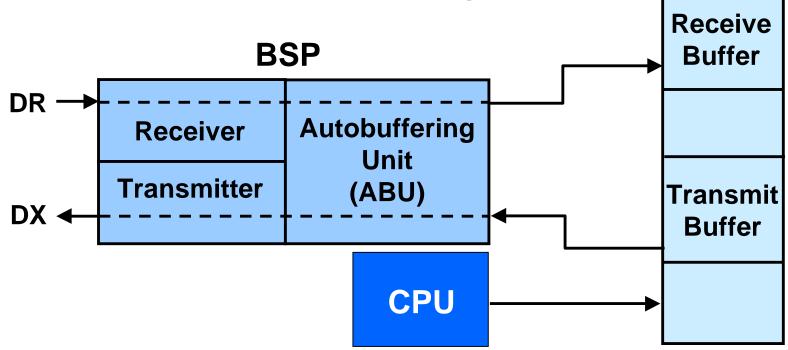

#### **Standard Serial Port:** Architecture

#### **Buffered Serial Port: Autobuffering**

Clocks at full CLKOUT rate

- XÛ

- Supports full-duplexed and doublebuffered for flexible data stream length

Data Memory

- Supports high-speed transfers

- Reduces overhead of servicing interrupts

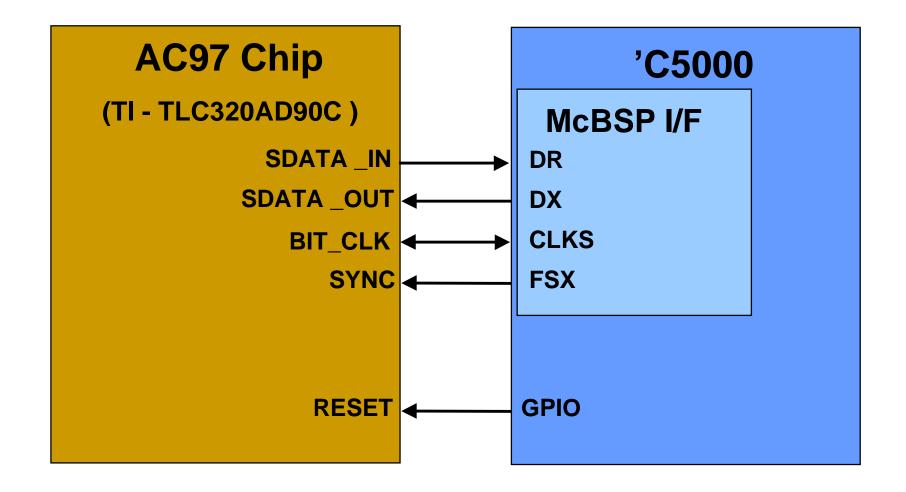

#### **McBSP:** Glueless I/F with AC97

THE WORLD LEADER IN DSP SOLUTIONS

#### Interfacing: Serial ports

| McBSP | BSP                 | TDM                        | Standard                                                                      |

|-------|---------------------|----------------------------|-------------------------------------------------------------------------------|

| 6     |                     |                            |                                                                               |

| 2     |                     |                            |                                                                               |

| 3     |                     |                            |                                                                               |

|       | 2                   | 1                          |                                                                               |

|       | 1                   |                            | 1                                                                             |

|       | 1                   | 1                          |                                                                               |

|       |                     |                            | 2                                                                             |

|       | 6<br>2<br>3<br><br> | 6<br>2<br>3<br>2<br>1<br>1 | 6           2           3            2       1          1           1       1 |

THE WORLD LEADER IN DSP SOLUTIONS

N.

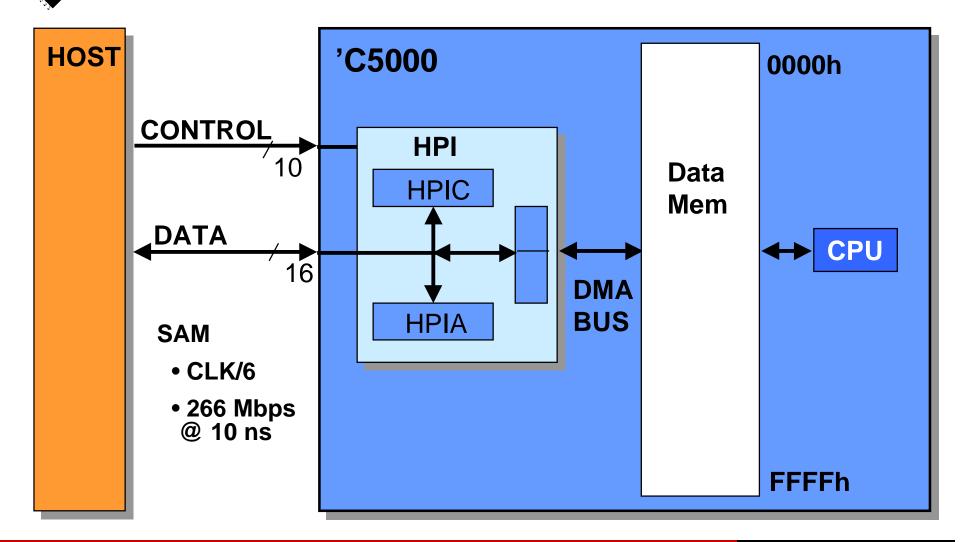

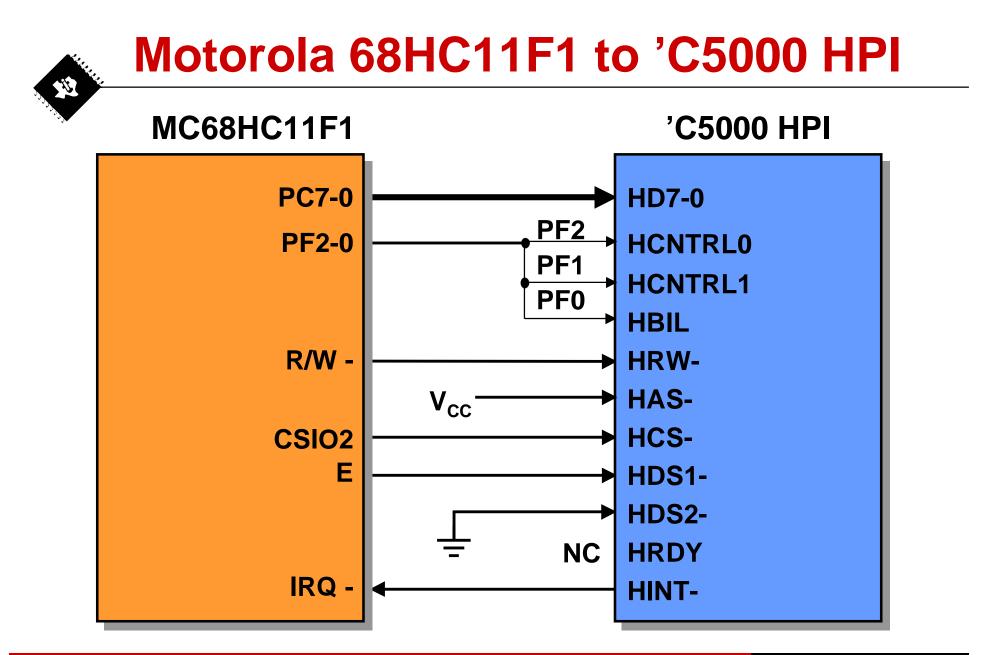

## Interfacing: The HPI concept

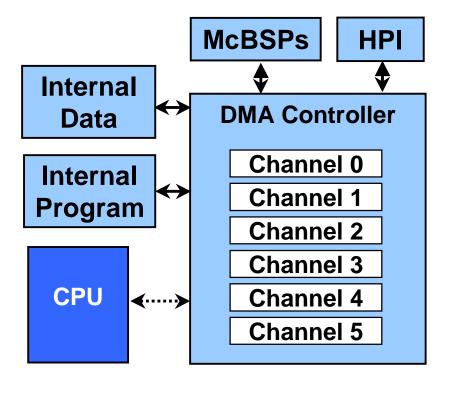

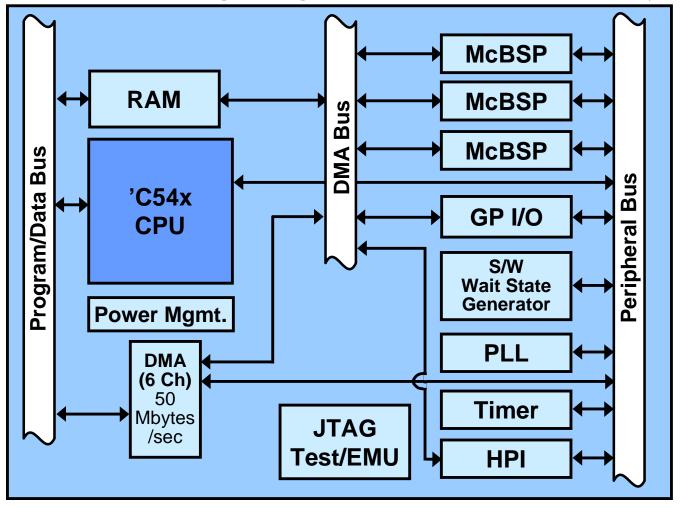

#### **DMA:** Transfers transparent to CPU

#### • High performance:

- Six DMA channels

- Data moves from / to peripherals and memory

- DMA higher priority than CPU

#### Programmable:

- Data widths

- Priorities

- Auto-initialization

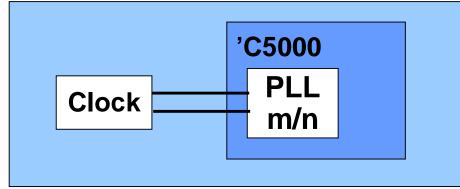

## Interfacing: PLL clock

- Instruction rate clock can be derived from slower external clock.

- 'C548 and above are programmable on the fly (32 ratios possible; no device reset required)

- PLL clock reduces EMI issues by lowering board-level clock rate.

- Lower cost/frequency oscillator (crystal) are multiplied internally.

- Device supports programmable delay for PLL lock time.

## How do I work with TI's 'C5000?

How do I get my performance? What performance can I expect? How do I interface easily?

#### What are the new 'C5000 devices?

How do I minimize power consumption? How does TI enable power-efficient performance at lower cost?

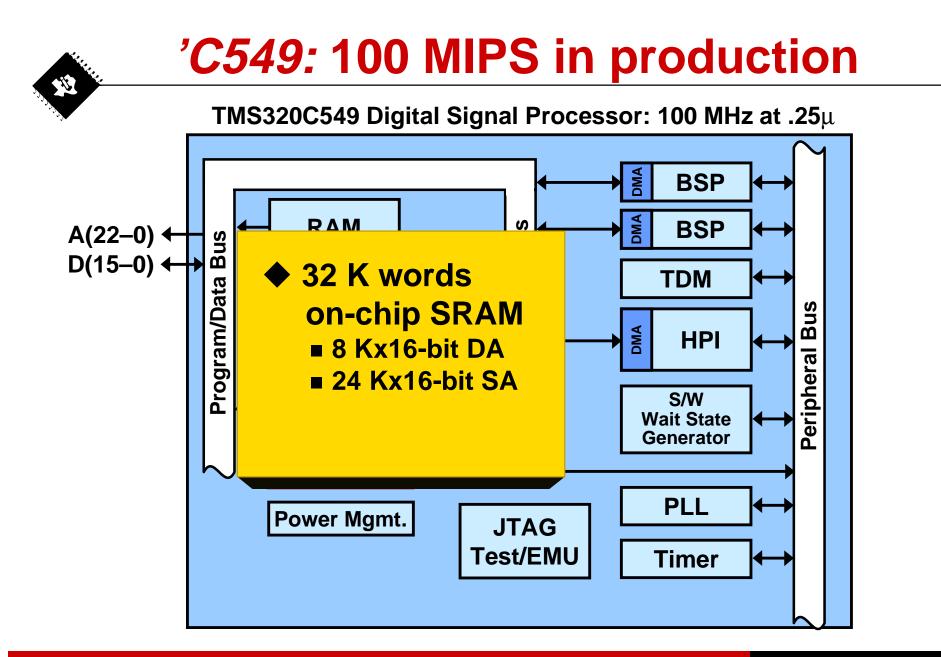

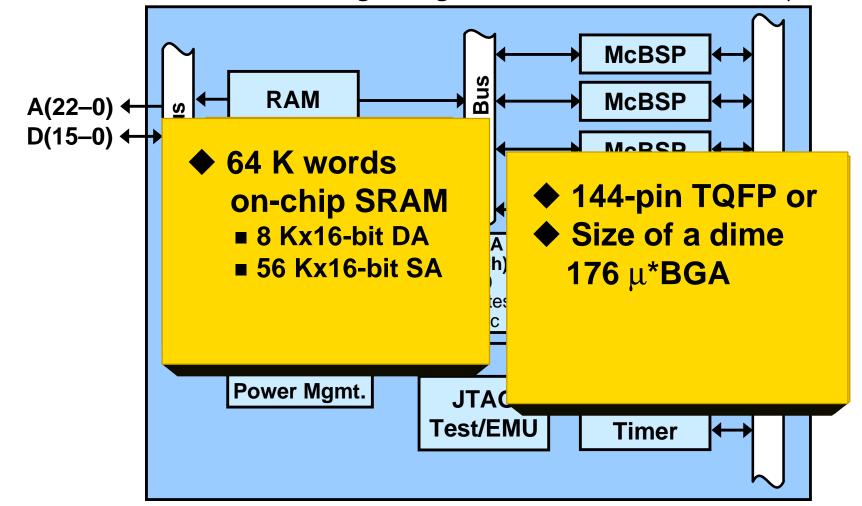

## **C5410: Increasing on-chip integration**

TMS320C5410 Digital Signal Processor: 100 MHz at .25 $\mu$

THE WORLD LEADER IN DSP SOLUTIONS

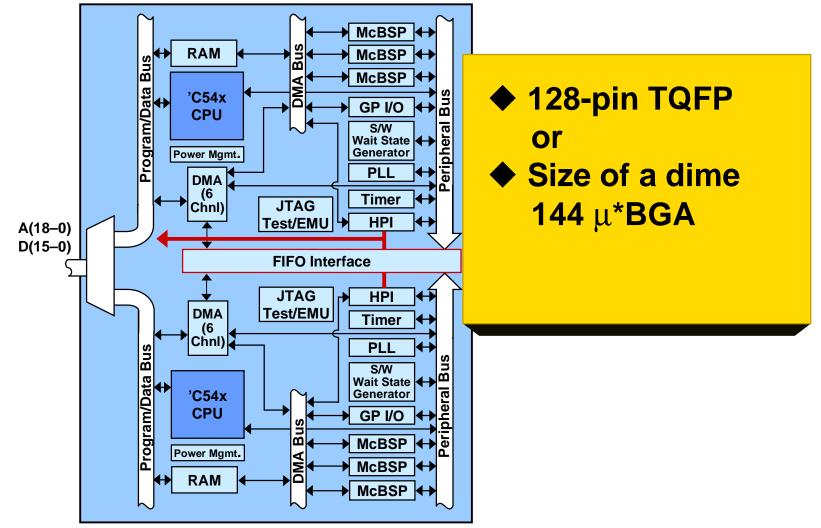

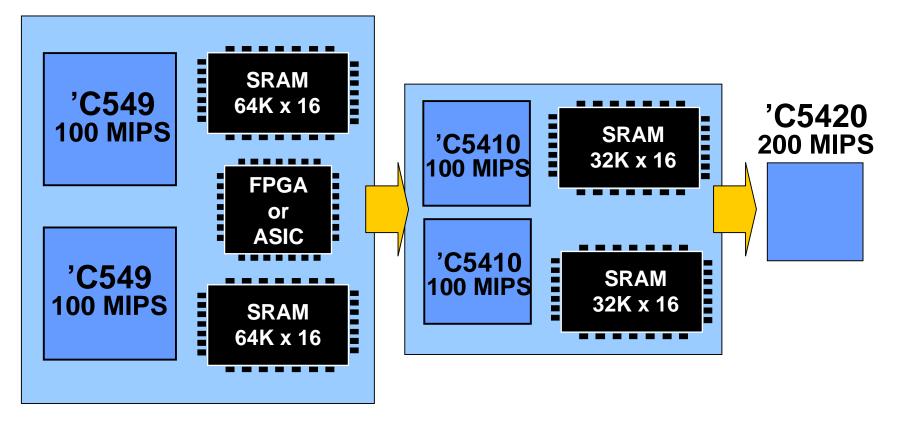

### 'C5420: Dual core 200 MIPS

TMS320C5420 Digital Signal Processor: 200 MHz at .18 $\mu$

THE WORLD LEADER IN DSP SOLUTIONS

TEXAS INSTRUMENTS ÷

#### 'C5420: Dual core 200 MIPS

THE WORLD LEADER IN DSP SOLUTIONS

TEXAS INSTRUMENTS İ

## How do I work with TI's 'C5000?

How do I get my performance?

What performance can I expect?

How do I interface easily?

What are the new 'C5000 devices?

How do I minimize power consumption?

How does TI enable power-efficient performance at lower cost?

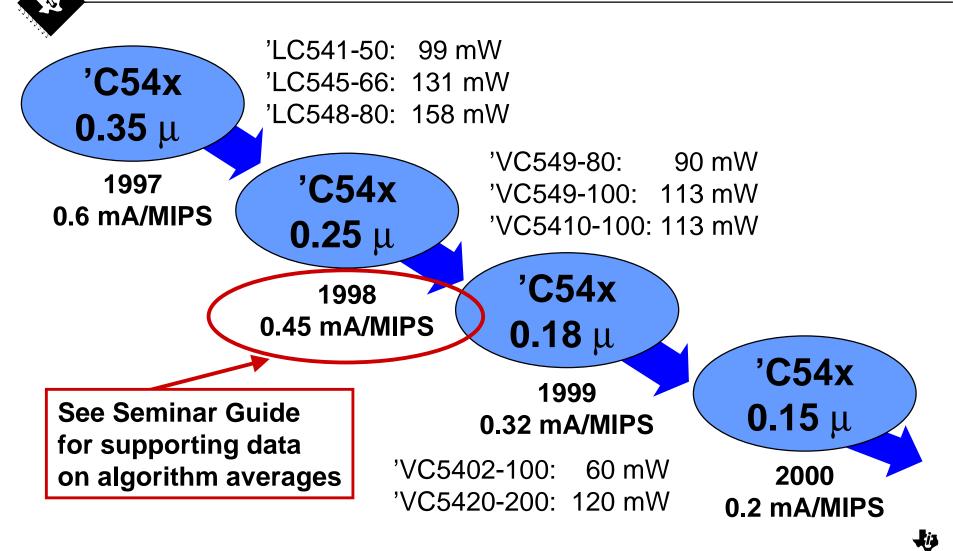

#### 'C5000: Process technology

THE WORLD LEADER IN DSP SOLUTIONS

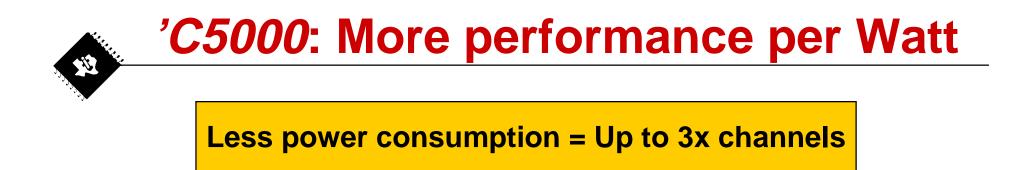

## 'C5000: Lowest power consumption

#### Mechanisms used on the 'C5000:

- Bus keepers / Holders maintain state of external bus

- External Bus off control disables the external bus

- Static design lower clock to DC

- N

- IDLE 1, 2, 3 modes drop into various power-down modes

- PLL options use lower system clock

- MIPS efficiency requiring fewer MIPS

## How do I work with TI's 'C5000?

How do I get my performance? What performance can I expect? How do I interface easily? What are the new 'C5000 devices? How do I minimize power consumption?

How does TI enable power-efficient performance at lower cost?

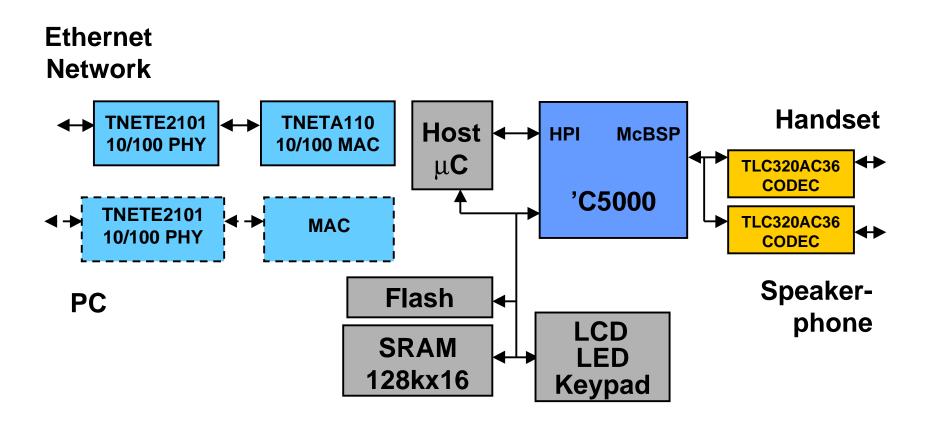

#### Value per \$: Internet phone example

THE WORLD LEADER IN DSP SOLUTIONS

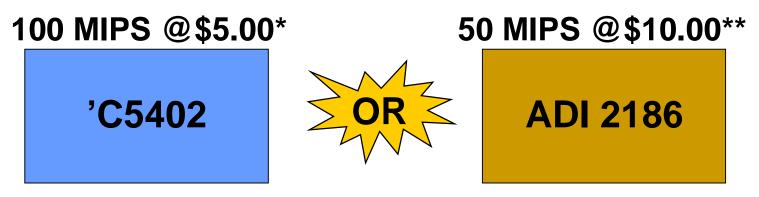

#### 'C5402: Internet phone example

G.723.1 Vocoder Echo Cancellation DTMF Voice Activity Detection Full Duplex Speakerphone Voice Packet Management

**TOTAL 40 MIPS**

Plus... at half the cost, 'C5402 delivers:

- Lower power, less space

- Glueless I/F to μC/Host, to multiple CODECs, and to fast or slow SRAM and Flash

- Expandable system for product differentiation, increased application functionality and seamless upgrades

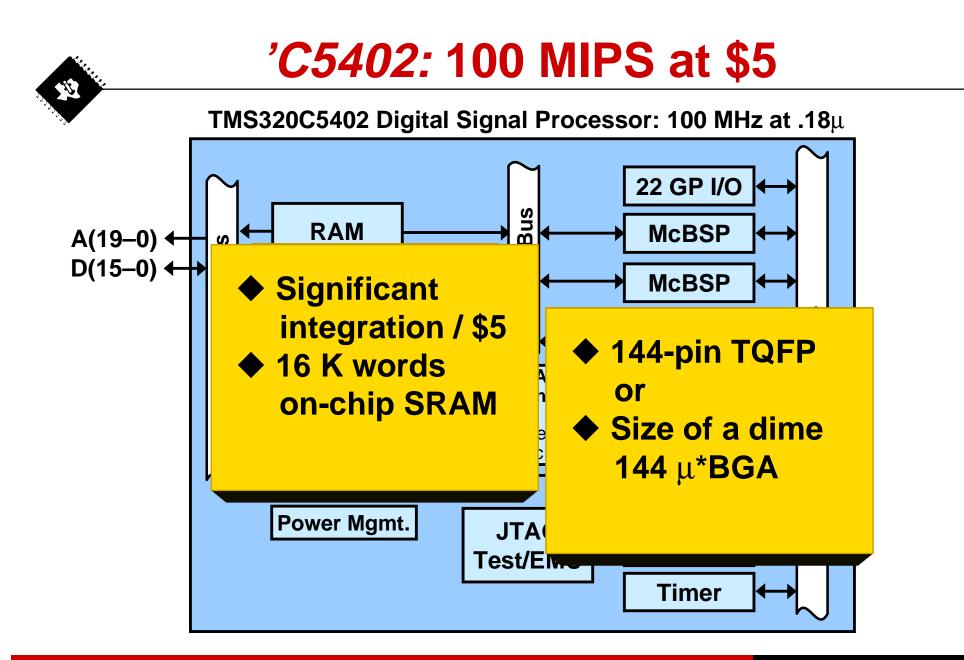

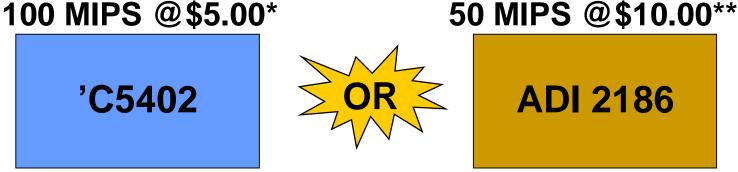

# Competitor: What do you get for \$5? 1/7<sup>th</sup> the performance, 1/20<sup>th</sup> on-chip SRAM, 6x the power consumption

ENTS

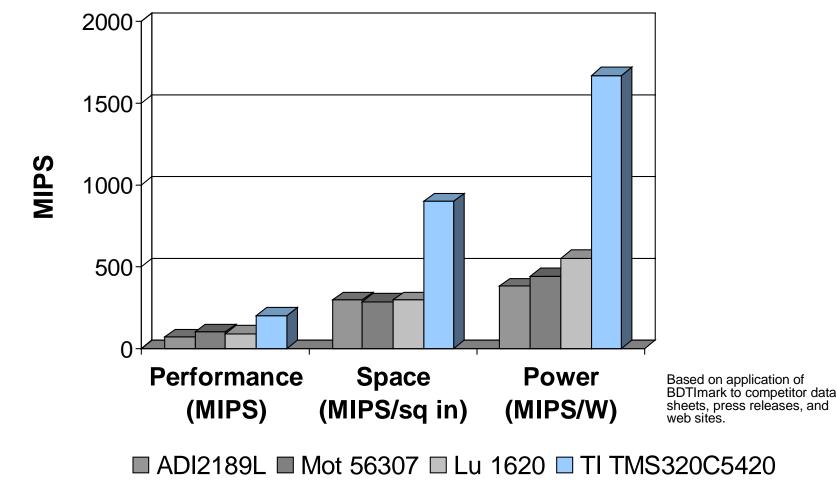

## 'C5420: More MIPS per careabout

# Up to 3x performance per Watt and 3x performance per square inch

THE WORLD LEADER IN DSP SOLUTIONS

#### ...through board space reduction

THE WORLD LEADER IN DSP SOLUTIONS

TEXAS INSTRUMENTS

**L**is