# A Motorola MC68008 Op-code compatible VHDL Microprocessor

David Lynch SN: 00019640

${\bf Supervisor}: \ {\bf Michael} \ {\bf Manzke}$

B.A (Mod) Computer Science Final Year Project

April, 2004

#### Abstract

The goal of this project is to implement a Motorola 68008 op-code compatible microprocessor capable of functioning on an FPGA. The CPU is to be specified fully in VHDL and is designed to emulate the functionality of the MC68008 in terms of instruction set decoding, operand addressing and bus operation. The ultimate target device is a custom designed FPGA-Board used in education of Computer Science and Engineering Students in TCD. As a result of this a large emphasis has been placed on structured, correct design flow and specification as well as readability of the code.

## Acknowledgments

I would like to thank Michael Manzke, my project supervisor for all the help and support given throughout the project. Appreciation is also extended to Ross Brennan for support on his FPGA board and bus-interfacing. Lastly I would like to thank John McCarthy, my Integrated Systems Design lecturer for help in mastering the use of the Xilinx platform and companion tools.<sup>1</sup>.

$<sup>^1{\</sup>rm This}$  document has been type set using LATEX

## Contents

| 1        | $\operatorname{Intr}$ | oducti            |                                            | 1         |  |  |  |

|----------|-----------------------|-------------------|--------------------------------------------|-----------|--|--|--|

|          | 1.1                   | Curre             | nt Project                                 | 1         |  |  |  |

|          |                       | 1.1.1             | Computer Architecture Coursework           | 1         |  |  |  |

|          |                       | 1.1.2             | The FPGA Design                            | 4         |  |  |  |

|          | 1.2                   | Motiv             | ation                                      | 6         |  |  |  |

|          | 1.3                   | Design            | n Approach                                 | 7         |  |  |  |

|          |                       | 1.3.1             | VHDL Programming                           | 8         |  |  |  |

|          | 1.4                   | Motor             | rola 68000 Microrocessor Overview          | 9         |  |  |  |

| <b>2</b> | Har                   | dware             | Design                                     | 13        |  |  |  |

|          | 2.1                   | Overv             | iew                                        | 13        |  |  |  |

|          | 2.2                   | Funct             | ional Unit                                 | 14        |  |  |  |

|          |                       | 2.2.1             | The Arithmetic and Logic Unit              | 15        |  |  |  |

|          |                       | 2.2.2             | The Shifter                                | 18        |  |  |  |

|          |                       | 2.2.3             | Control Registers                          | 19        |  |  |  |

|          | 2.3                   | Data S            | Storage and Movement                       | 21        |  |  |  |

|          |                       | 2.3.1             | Register File                              | 21        |  |  |  |

|          |                       | 2.3.2             | Data Bus and Address Bus Selection         | 23        |  |  |  |

|          |                       | 2.3.3             | The IPL control Module                     | 24        |  |  |  |

|          | 2.4                   | The Bus Interface |                                            |           |  |  |  |

|          |                       | 2.4.1             | Implementation                             | 25        |  |  |  |

|          |                       | 2.4.2             | Read and Write Cycles                      | 26        |  |  |  |

|          |                       | 2.4.3             | Interrupt Acknowledge and Bus Error Cycles | 27        |  |  |  |

|          |                       | 2.4.4             | Bus Interface Hardware                     | 30        |  |  |  |

|          | 2.5                   | Seque             | ncing and Control                          | 30        |  |  |  |

|          |                       | 2.5.1             | Control Path Registers                     | 31        |  |  |  |

|          |                       | 2.5.2             | Micro-sequencing                           | 32        |  |  |  |

|          |                       | 2.5.3             | Instruction Decoding                       | 36        |  |  |  |

|          |                       | 2.5.4             | The Control Word                           | 39        |  |  |  |

| 3        | Mic                   | ro-pro            | ogramming the design                       | <b>42</b> |  |  |  |

|          | 3.1                   | _                 | ol Word Generation                         | 42        |  |  |  |

|          | 3.2                   |                   | m Control Programming                      | 43        |  |  |  |

|          |                       | 3.2.1             | Memory Access                              |           |  |  |  |

|          |                       | 3.2.2             | RESET Handler                              | 44        |  |  |  |

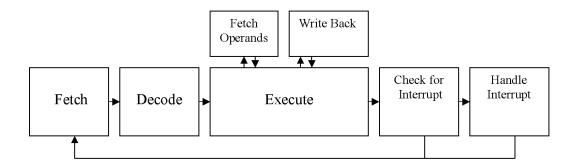

|          |                       | 3.2.3             | Fetch-Decode-Execute Sequence              | 45        |  |  |  |

|          |                       |                   | <u>*</u>                                   |           |  |  |  |

|                           | 3.3                             | The M   | OVE instruction                     | 46        |  |

|---------------------------|---------------------------------|---------|-------------------------------------|-----------|--|

|                           |                                 | 3.3.1   | Decoding                            | 46        |  |

|                           |                                 | 3.3.2   | Fetch using Addressing Modes        | 47        |  |

|                           |                                 | 3.3.3   | Write Back                          | 47        |  |

|                           | 3.4                             | The M   | TULU instruction                    | 48        |  |

|                           |                                 | 3.4.1   | The Shift-and-Add Algorithm         | 48        |  |

|                           |                                 | 3.4.2   | Other Instructions                  | 49        |  |

| 4                         | Test                            | ting an | d Conclusions                       | 50        |  |

|                           | 4.1                             | Design  | Testing and Development Progress    | 50        |  |

|                           |                                 | 4.1.1   | Synthesis                           | 51        |  |

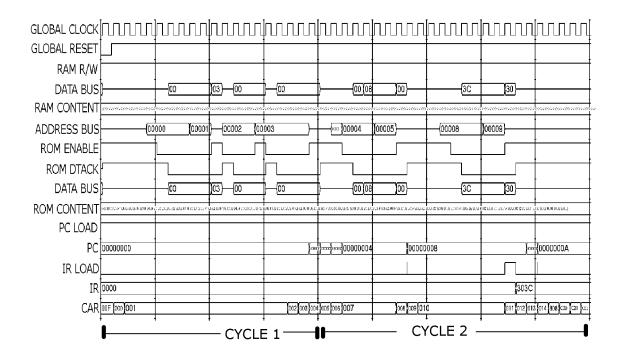

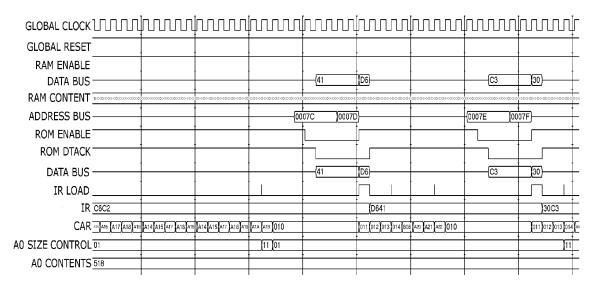

|                           |                                 | 4.1.2   | A 68008 demonstration               |           |  |

|                           | 4.2                             | Conclu  | sions                               | 55        |  |

|                           |                                 | 4.2.1   | Skills Acquired and Lessons Learned | 56        |  |

|                           |                                 | 4.2.2   | Further Work                        | 57        |  |

| Bi                        | bliog                           | graphy  |                                     | <b>57</b> |  |

| $\mathbf{A}_{\mathtt{l}}$ | ppen                            | dix A,  | CWORD Guide                         | 59        |  |

| $\mathbf{A}_{\mathtt{J}}$ | Appendix B, Design Hierarchy 62 |         |                                     |           |  |

## List of Figures

| 1.1  | The 68008 package                                         | 2          |

|------|-----------------------------------------------------------|------------|

| 1.2  | The Leon Core. Source: ESA[5]                             |            |

| 1.3  | The 68000 System Register                                 |            |

| 2.1  | 0                                                         | L4         |

| 2.2  | ALU Block Diagram                                         | 16         |

| 2.3  | BIN control CSA. BIN Feeds the Y input of the adder array | ١7         |

| 2.4  | 68000 Shifting. Source: MC68000 Programmers Reference     | 18         |

| 2.5  | VHDL Rotate Right using case for combinatorial logic      | 19         |

| 2.6  | The System Register                                       | 20         |

| 2.7  |                                                           | 22         |

| 2.8  |                                                           | 25         |

| 2.9  | Sample Read Operation State flow (Simplified)             | 26         |

| 2.10 | Setting outputs for the idle state                        | 27         |

| 2.11 |                                                           | 28         |

| 2.12 | Bus Write Cycle                                           | 28         |

| 2.13 | Auto-vector peripheral bus cycle                          | 29         |

| 2.14 | CROM and Control Address Register                         | 30         |

| 2.15 | Microsequencer Block Diagram                              | 32         |

|      |                                                           | 34         |

|      |                                                           | 37         |

| 2.18 | MOVE.B #5,(A0) Instruction                                | 37         |

| 2.19 | Instruction encoding for group 0000                       | 38         |

| 2.20 | Instruction Decoder and mapping ROM                       | 39         |

| 2.21 | CWORD Formats                                             | <b>1</b> C |

| 3.1  | 0                                                         | 13         |

| 3.2  | The Fetch-Decode-Execute Cycle                            | 15         |

| 3.3  | MOVE Instruction Form                                     | 16         |

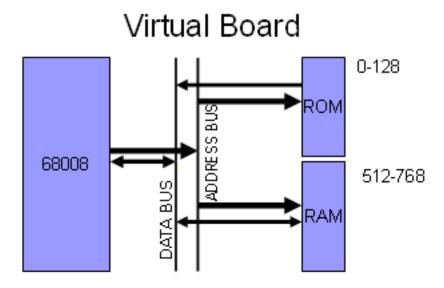

| 4.1  | The Virtual Board Simulation Setup                        |            |

| 4.2  | Multiplication of 2D Matrices                             | 52         |

| 4.3  | A timing diagram for the first 9ns of operation           | 54         |

| 4.4  | The final write back                                      | 55         |

| 4.5  | RAM contents after the program has finished               | 56         |

## List of Tables

| 1.1 | 68k Pin Description                                   | 2  |

|-----|-------------------------------------------------------|----|

| 1.2 | Addressing Modes [1]                                  |    |

| 1.3 | Data Transfer Instructions [1]                        |    |

| 1.4 | Program Flow Control Instructions                     | 11 |

| 2.1 | Functional Unit Operation Select                      | 15 |

| 2.2 | SR Load Control                                       | 21 |

| 2.3 | Internal Register Map                                 | 22 |

| 2.4 | Destination and Source Selection in the Register File | 23 |

| 2.5 | BI Select                                             | 29 |

| 2.6 | MCA Selection                                         | 33 |

| 2.7 | CCOND Possible Branching Conditions and CCR Codes     | 35 |

| 2.8 | Decoding an EA                                        | 37 |

| 2.9 | CWORD Field Function                                  | 41 |

| 3.1 | Memory Access CROM Locations                          | 43 |

## Chapter 1

### Introduction

This chapter serves as an introduction to the Motorola 68008 VHDL<sup>1</sup> CPU project. The background and motivations behind such a project are outlined. In doing so, current project-board design is introduced along with the improved board design as proposed and implemented by Ross Brennan, together with arguments for the continued use of the MC68008 in an educational context. This chapter also explores the design approach taken and reasons for such an approach.

#### 1.1 Current Project

This project branches directly from the final year project completed by Ross Brennan entitled, The Design and Evaluation of an FPGA based Microprocessor Project Board [2]. The core objective of Brennan's project was to explore the possibility and feasibility of introducing configurable hardware devices into Architecture courses taken by Computer Science students and Computer Engineering Students with a view to upgrading the project system-boards to take advantage of recent hardware advances.

#### 1.1.1 Computer Architecture Coursework

As a coursework section in the Computer Architecture I module of the B.A. (Mod) Computer Science degree at TCD. Students are required to build a functioning microprocessor system using core components. By completing such a project students become acquainted with the fundamentals of CPU-to-peripheral interaction, bus operation, asynchronous communication and board-level programming. The project is centred on the Motorola MC68008 processor with which students are required to interface two 8k static RAM chips, an 8k EEPROM and a Rockwell R6551 Asynchronous communications adapter. Wire wrap is used to connect the devices together after they have been placed on a purpose built system board.

The MC68008 processor is a 16-bit CISC<sup>2</sup> design released in late 1982 as a replica of the MC68000 except with a reduced data-bus width of 8-bits. This reduction was implemented in order to preserve compatibility with legacy 8-bit devices.

<sup>&</sup>lt;sup>1</sup>Very High Speed Integrated Circuit Hardware Description Language

<sup>&</sup>lt;sup>2</sup>Complex Instruction Set Computer

As an early CISC computer the 68000 strikes a nice balance between a powerful instruction set, advanced memory addressing capability and simplicity of interface. Largely due to the absence of legacy instruction support, floating point arithmetic, or multi-media extensions commonly found in todays processors, this balance is very desirable in an educational context, particularly when introducing junior freshmen students to low-level programming.

The MC68008 possesses a 20-bit address bus, allowing 1MB of in total addressable memory space. An 8-bit bi-directional data bus allows the MC68008 to communicate external on-board devices using asynchronous bus protocols defined by Motorola. The package is described in Fig. 1.1 and the pin functions detailed in Table 1.1.

Figure 1.1: The 68008 package

| Pins      | Description                      | Function                   |

|-----------|----------------------------------|----------------------------|

| A19 : A0  | Address Bus                      |                            |

| D7: D0    | Data Bus                         |                            |

| /DTACK    | Bus Read Acknowledge             | Asynchronous bus control   |

| /AS       | Address-on-bus                   |                            |

| /DS       | Data Strobe                      |                            |

| R/W       | Read Write                       |                            |

| /VPA      | Valid Peripheral Address         | Peripheral Control         |

| E         | Peripheral Clock Synchronisation |                            |

| /IPL[2:0] | Interrupt Level                  | External Interrupt Control |

| /BERR     | Bus Error                        | System Control             |

| /RESET    | Reset Signal                     |                            |

| /HALT     | Processor Halt                   |                            |

| /BR       | Bus Request                      | Bus Arbitration Control    |

| /BG       | Bus Grant                        |                            |

Table 1.1: 68k Pin Description

#### Components Used

- 1 x Motorola MC68008 Microprocessor

- 1 x R6551 Serial Interface

- 1 x 2764 8k EPROM

- 2 x HM6116P 2Kx8-bit Static RAM

- miscellaneous components including A 7404 Hex Inverter, 7407 Hex Buffer, 74LS73 J-K Flip Flops, Dual 4-bit binary counter and a resistor pack.

Students are given access to a pre-designed project board. This board has a 5V power supply and a parallel interface for connection with a logic state analyser. A 14.7465Mhz Crystal Oscillator is also integrated to provide clock signals for the ACIA<sup>3</sup> and the MC68008. The board acts as a basis on which to place the 5V TTL pin packages supplied. Once placed in the pin-holders students use copper wire wrap to connect the pin packages together.

#### The project stages

- Verify the board is generating a 15MHz clock signal using an oscilloscope.

- Use the 4-bit counter and the resistor pack to generate an 8Mhz clock signal for the MC68008 and a 1Mhz clock signal for the ACIAs.

- Use the hex-inverter package, and Schmitt triggers to create a debounce circuit which ensures the RESET signal is kept asserted for at least 3 clock cycles. This ensures correct reset of internal circuitry and the peripherals.

- Memory map the RAM chips, the EEPROM and the ACIA using the GAL<sup>4</sup> to generate appropriate chip-enable signals depending on the processor Address Strobe (/AS), Data Strobe (/DS) and Address Bus (A19 : A0). The students use PALASM to generate equations which are then programmed to the GAL chip.

- Program the EEPROM to provide the processor with a means of testing the bus interface. A suggested approach is through repeated JMP instruction execution.

- Establish and verify the functionality of the RAM. This can be done with a similar loop to the above, with the additional use of the MOVE instruction to test the memory space where each of the RAM chips resides.

- Use the JK Flip flop package provided to generate correct VPA and IPL signalling to enable the ACIA to operate as a peripheral component. Use these signals to provide an EEPROM program to handle interrupts generated by the ACIA and create a transparent link with a PC using a hyper-terminal session.

<sup>&</sup>lt;sup>3</sup>Asynchronous Communications Device

<sup>&</sup>lt;sup>4</sup>General Array Logic — A simple programmable device

• Upon successful completion of the above, the students are then asked to create a simple monitor program using the EEPROM and 68k Assembly language.

#### 1.1.2 The FPGA Design

FPGA devices are re-programmable and offer unparalleled flexibility for hardware specification. With recent advances in re-programmable logic devices, such as decreased FPGA device scale and increased speed as well as the evolution of synthesis software tools like Xilinx Foundation[13] it has become increasingly more feasible to develop fully-specified CPUs within a programmable hardware paradigm. The open source movement has seen a spiral in such core implementations.[4]

The advantages of using an FPGA implementation are numerous. The student is no longer only exposed to bus interfacing, but allowed to examine how such a device may be logically implemented using a hardware description language. Furthermore, the flexibility of the FPGA design allows students to compare and contrast specific technologies. For example, the student may wish to switch off the on-chip cache of a microprocessor to measure performance, or, switch between a RISC and CISC CPU to use different instruction sets, all without having to re-wire the microprocessor board set up. Lastly, an FPGA design could replace the 68008 pin-packages which are obsolete in their current form and are becoming increasingly difficult to replace.

#### Board Hardware

Ross Brennan prototyped a replacement project board that was centred on a Xilinx Virtex-II XV1000-256 FPGA. As 1 Million Gate Device, this FPGA would provide ample basis in which to situate a RISC HDL-CPU <sup>5</sup> as well as space for additional student design or a second CPU. The RAM and GAL components used in the original project are still used here, although adapted to LL3V voltage operation to suit the Xilinx FPGA voltages<sup>6</sup>. A PROM has also been added to the design. This feature allows on-board programming of the FPGA on power up. As the FPGA is based on SRAM technology the programming is lost at power down. The PROM provides a quick way to program the FPGA with a selected architecture without having to connect the system to a synthesis tool. [2, R. Brennan]

When the HDL design is synthesized, a bit file is generated by the synthesis tool. This is then downloaded onto the FPGA using an interface port. However, because the FPGA is based on SRAM, the programmed design is lost at power-down. The PROM remedies this by providing the FPGA with a bit file at power on. The PROM may also contain different designs, e.g. the bit-files for a RISC design and a MC68008 design allowing the user to change between the two without having to synthesize and download a new design from scratch.

<sup>&</sup>lt;sup>5</sup>The proposed RISC design would use 80% of these resources at full-specification

<sup>&</sup>lt;sup>6</sup>The original packages are 5V TTL

#### LEON CPU Core

The LEON[5] core is a fully featured SPARC V8[12] compatible Core specified in VHDL and developed by the European Space Agency. It has a 32-bit data bus, floating point units, on-chip caches and a memory control unit. This core was chosen because it is an OpenSource VHDL implementation that is highly configurable, thus lending itself to the ideal educational environment described above.

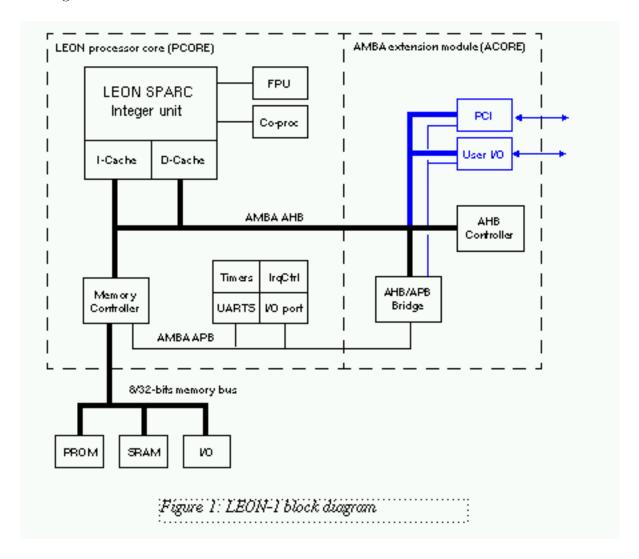

Figure 1.2: The Leon Core. Source : ESA[5]

In order for the LEON to suffice as a replacement for the MC68008 pin-package modifications were necessary. The main objective was to emulate the simplicity of MC68008 bus interaction and to ensure compatibility with the currently used RAM, ROM and GAL devices. The LEON was cut down to those components only necessary for the function of the CPU. Although the LEON is capable of a 58Mhz clock speed [2, Brennan], an 8Mhz clock has been provided. Caches were also removed from the design as caching would inhibit the ability of the student to use an oscilloscope and logic state analyser to monitor bus activity. If the executed

program, such as the JMP loop, was read from memory once, it would be cached in one bus cycle. Subsequent bus cycles would not occur, thus causing difficulty when testing for correct bus function. Likewise, The Memory Management unit was removed. The internal UARTS also needed to be removed as interfacing an asynchronous communications device to the processor is a core requirement of the Computer Architecture project therefore use of internal serial communication is not required. For the same reason, internal reset circuitry was removed. The LEON data-bus was reduced to 8-bits, to preserve component compatibility. It is calculated that an approx 95% decrease in performance would result from the changes, however it is noted here that the result is not a disadvantage for the student. A functional system is much more desirable than a fast system in and educational context. [2]

#### 1.2 Motivation

There are several purposes to this project. The main purpose is to provide a VHDL 68008 microprocessor for the above project board. As described by Brennan and Manzke [3], a 68008 HDL CPU would provide students with a CPU on-which they could learn assembly programming using a small, simple but powerful instruction set. More importantly once the processor had a bus interface capable of being used on the existing project board, it opens possibilities for expanding FPGA based microprocessor boards to allow users to configure various parts of the design to their particular needs and use different architectures within the same physical hardware paradigm. The 68008 CPU could also help preserve the use of the Motorola processor as a teaching tool. It is currently heavily used in Computer Science and Computer Engineering hardware modules due to its simplicity when compared to other processors. However, as the processor ages, it has become more and more difficult to obtain replacement 5VTLL packages when necessary. An FPGA design may eventually be a cheaper and simpler way of maintaining 68000 resources within the college.

Also, a motivation is to provide students of Computer Architecture with an understandable implementation of a micro-programmed CISC architecture as implemented using VHDL. Currently, Junior Freshmen studying for the B.A. (Mod) are exposed to digital fundamentals such as adder design and multiplexer design using primitive digital logic gates. Senior Freshmen are exposed to multiple-cycle CPU design and more complex primitives such as Arithmetic Logic Units (ALU). It would be very desirable for students of these courses to be able to break down a CPU implementation into its core components and examine the design. A VHDL design programmed in an efficient and modular manner allows a user to examine a core component, completely ignoring the surrounding implementation. Therefore students can not only see where a primitive component may be used, but also how such a primitive may be implemented using a hardware specification language.

#### 1.3 Design Approach

There were several tasks to be completed before implementation work began. The first was to master the VHDL programming language. This was done by completing a selection of second-year assignments involving simple CPU design. Several VHDL exercises using primitive components were also completed. This coupled learning VHDL with re-familiarisation of digital logic concepts.

Sources used for learning VHDL programming were http://www.vhdl-online.de[6], Xilinx[13] and VHDL, From Simulation to Synthesis [14]. These resources also provided tutorial on how the Xilinx FPGA design and simulation platform is used.

The next task was to research CPU design implementation. A large part of this research work involved the study of Computer Architecture and Digital Design. Digital Design[8] and Logic and Computer Architecture Fundamentals both by M. Morris Mano[9] provided coverage of these two topics. Once a comfortable level of VHDL proficiency had been obtained it was necessary to turn attentions to the 68008 microprocessor.

The 68000 Programmers manual[10] and the 68000 users manual[11] were invaluable resources when it came to detailing 68000 internals and operation, especially when it came to instruction decoding and bus cycles. The Motorola instruction set was examined and broken down into smaller, more visibly structured chunks from which decisions about instruction decoding and hardware support were made. Next, information about the 68000 software model was gathered. The 68000 Microprocessor: Hardware and Software Principles by James L. Aontonakos[1] was found to be a good resource that provided a useful abstraction from the meticulous detail and formality of the Motorola manuals.

Once this initial research had been completed, the hardware design process could start. The design is implemented entirely in VHDL using Xilinx v5.1 tools for programming and synthesis together with ModelSim 5.6 for simulation. The CISC CPU as described by Mano and Kime [9] in *Logic and Computer Design Fundamentals* has been extensively adapted to create a VHDL CPU capable of executing Motorola 68000 op-code. The following modifications were necessary.

- Implement the CISC CPU in VHDL.

- Add support for variable sized operands i.e. 8/16/32-bit and correct condition codes.

- Add support for 68008 Arithmetic.

- Devise and implement enhanced branching capabilities.

- 16-bit 68000 instruction decoding.

- Exception generation and handling.

- 68000 memory addressing mode support.

- Add an FPGA board compatible Bus Interface.

The CPU has been built in an incremental fashion starting with the register file. Each individual module has been programmed and tested under a behavioural simulation to verify functionality and post-synthesis simulation to verify the result could operate on an FPGA. The design approach taken is in-line with the VHDL design flow specified in VHDL From Simulation To Synthesis [14]. Firstly, the hardware was specified and programmed. Secondly, a behavioural simulation was performed to verify functionality of the design. Next, a post-synthesis simulation was carried out to verify the design still functions correctly in the target environment. This design flow was applied to every component of the project from full-adder up to CPU package.

#### 1.3.1 VHDL Programming

The design is implemented wholly in VHDL, mainly to maintain compatibility with the existing LEON design on the FPGA board. Also, second year Computer Science students are exposed to VHDL programming and it makes sense to maintain this trend in hardware education within the course. It is also argued here that VHDL is a more reader-friendly language than the alternative, Verilog.

VHDL is a hardware specification language that infers a hardware model by reducing a hardware design specified in a software model to primitive components. This automatic hardware compilation is a very powerful way, although not always resource-optimal way, of creating a functional hardware designs from a specification without having to wire primitive gates manually.

#### RTL Style

A key requirement for this project is synthesizability<sup>7</sup> of design. Not only would a synthesizable design be downloadable to the target project board but would prove that a somewhat efficient and modular design is in place. In hardware design specification for FPGA it is a necessity to keep the hardware that may be generated as a result of coding in mind. In doing this the synthesis tool is helped greatly with inferring an efficient, functional design free of undesirable side effects such as unwanted latches and multi-sources.

Although VHDL supports many language constructs and methodologies only a subset of it is synthesizable. The only VHDL language constructs (aside from declaration constructs) used in the design are process, case, if, then, else, and concurrent signal assignment. This project adheres to these constraints not only to create an efficient, synthesizable design, but a readable one capable of being modified and enhanced in the future. With this in mind a Register Transfer Level of abstraction has been kept consistent throughout the design. As a result both synchronous and combinatorial logic has been defined through use of concurrently running processes. The Xilinx synthesis tool will deduce synchronous logic for processes that rely on a global clock. Otherwise, the synthesis tool will try to infer combinatorial logic. The code listing below shows an example of using a process to infer a multiplexer.

$<sup>^7\</sup>mathrm{A}$  synthesizable design is capable of being implemented correctly on an FPGA or other target device

Care has been taken to avoid the inference of unwanted latches at every stage of the project thus ensuring the Model is always in a known state during operation. In fact, the only use of latches is in the bus interface when latching lower order bytes of a higher order operation. Wherever data needs to be stored, registers have been instantiated and wired manually using port-maps.

#### 1.4 Motorola 68000 Microrocessor Overview

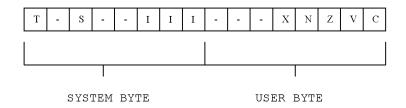

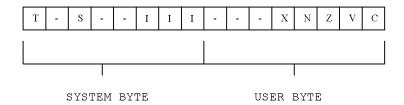

The 68000 is internally a 32-bit CPU. Eight 32 bit data registers, numbered D0-D7, are provided for data manipulation. In addition, 32-bit address registers A0-A6 are designed to hold memory addresses in order to aid data movement within the system and increase the complexity of memory addressing modes. Register A7 is a special case of such a register. It is known as the system stack pointer (SSP) when handling system control instructions (i.e. in supervisor mode), and user stack pointer (USP) in user programming mode (i.e. executing user code). A 32 bit program counter, of which the lower 24-bits are valid (20 in the 68008, due to its decreased address bus size), provides memory addressing for the currently executing instruction. A 16-bit system register holds information necessary for system functions such as branching condition codes and interrupt information. Figure 1.3 shows a graphical outline of the system register contents. The lower 8-bits, or user byte, hold condition codes such as overflow which are generated by the functional unit. The higher order byte, or the system byte, holds the current interrupt level priority mask used in peripheral control, the trace bit (whether or not to call a trace exception after each instruction) and the supervisor bit which is set when performing system control tasks.

Twelve addressing modes are available, detailed in table 1.2. Direct mode addressing transfers the data to or from any of the data or address registers. Indirect addressing is performed using an address register which contains the address in memory that that data to be manipulated resides. Post increment, pre-decrement and displacement variations of indirect addressing are implemented as modes useful during loop instructions and stack manipulation. Immediate addressing involves specifying an operand directly i.e. by encoding it in an extension to a core instruction word. Absolute addressing is similar with the exception that the immediate data specifies a location in a specific part of memory.

Figure 1.3: The 68000 System Register

| Mode                                         | Use                                      |

|----------------------------------------------|------------------------------------------|

| Data Register Direct                         | Data register holds data                 |

| Address Register Direct                      | Address register holds data              |

| Address Register Indirect                    | Using data pointed to by an Ar           |

| Address Register Direct with Post-Increment  | Increment the Ar after fetch/write       |

| Address Register Indirect with Pre-Decrement | Decrement the Ar before fetch/write      |

| Address Register Direct with Displacement    | Data at X+/-(Ar)                         |

| Address Register Direct with Index           | Data at $X+/-(Ar)+/-(Dn \text{ or } An)$ |

| Absolute Short                               | A 16-bit address specifies dest/srce     |

| Absolute Long                                | A 32-bit address specified dest/srce     |

| PC Indirect with displacement                | Data at PC +/- (Dn or An)                |

| PC Indirect with index                       | Data at PC +/- (An) +/- (Dn or An)       |

| Immediate                                    | Data encoded in instruction              |

Table 1.2: Addressing Modes [1]

The Motorola 68000 family instruction set is very much a CISC entity. The 68000 boasts powerful and numerous addressing modes and multiple-cycle instructions such as multiply and divide. Such features are not found in comparable RISC processors, such as the SPARC-II, which is a load/store architecture with a minimal instruction set. The eighty-one (counting branch as one and omitting no-op) instructions available to the 68000 programmer can be grouped loosely into four categories. Data Transfer Group, Arithmetic, Logical and Bit-manipulation group, program control group and system control group.[1] The data transfer group includes instructions to move data between memory and the processor and also between internal registers. There are also instructions, such as LINK and PEA that aid memory manipulation and the use of stack data structures. A complete list of this grouping is shown in table 1.3.

As is typical of a CISC instruction set, arithmetic instructions are plentiful. The 68000 is capable of manipulating 8, 16 or 32 bit signed operands. Instructions include ADD, SUB, MULU (Multiply Unsigned), DIVS (Divide Signed), TAS (Test and Set) and CMP(Compare). The 68000 is also capable of performing simple arithmetic on binary coded decimal. Shift operations are also available to the programmer. ASd (Arithmetic Shift) and LSd (Logical Shift) as well as ROd (Rotate) are the main shift instructions.

Program control accomplished using the instructions illustrated in table 1.4. These instructions aid the implementation of subroutines and conditional branching.

| Instruction | Description            |

|-------------|------------------------|

| EXG         | Exchange Registers     |

| LEA         | Load Effective Address |

| LINK        | Link                   |

| MOVE        | Move Data              |

| MOVEA       | Move Address           |

| MOVEM       | Move Multiple          |

| MOVEP       | Move Peripheral        |

| MOVEQ       | Move Quick             |

| PEA         | Push Effective Address |

| SWAP        | Swap Register Halves   |

| UNLK        | Unlink Stack Frame     |

Table 1.3: Data Transfer Instructions [1]

| Instruction | Description                       |

|-------------|-----------------------------------|

| Bcc         | Branch on Condition defined by cc |

| DBcc        | Decrement and Branch              |

| Scc         | Set Condition Codes defined by cc |

| BRA         | Branch Always                     |

| BSR         | Branch to Subroutine              |

| JMP         | Jump to Address                   |

| RTR         | Return and restore                |

| RTS         | Return from Subroutine            |

Table 1.4: Program Flow Control Instructions

The last group deals with system control and features instructions that reset the processor, call external subroutines, handle exceptions and manipulate stack pointers. Examples include RESET, AND to CCR, ILLEGAL and TRAP.

An instruction can have no, one or two operands which can be encoded in the instruction or specified using one of the addressing modes. Instruction.size op1,op2 is the general syntax for two operand instructions. Instruction is any two operand instruction defined by the set, size is one of B, W, L for Byte, Word and Long operation and Op1 and Op2 are effective address that specify the location of the operands and the location to place the result, which is in most cases op2. One and zero operand instructions take the same form, e.g RESET or NEG (A0). A more detailed discussion of the 68000 instruction set is considered as the design of the

VHDL CPU instruction decoder is explained in chapter 2. An exact dissection of the instruction set can be found in the Motorola 68000 Programmers Manual [10].

## Chapter 2

## Hardware Design

Although implemented in VHDL this project is essentially hardware based. This chapter explores in detail the 68008 is terms of the hardware implemented to create the functioning model. Firstly, the functionality of the design is explained followed by how such a design is implemented on the VHDL platform. Initially the design of the data-path including functional unit and register file is considered. Next, Bus Interfacing as well as sequencing and control hardware are examined. Where code listings occur, the source file is quoted and can be found on the accompanying CD in either the 68000-VHDL folder (Xilinx 5.1i) or the X\_6800-VHDL folder (Xilinx 4.1). Appendix B contains a listing of these files.

#### 2.1 Overview

The hardware design follows loosely the outline of a CISC CPU as detailed in *Logic* and Computer Design Fundamentals [9, Mano, Kime Pgs: 511 to 542]. However, extensive modifications were necessary to make an MC68008 op-code compatible CPU and to ensure a Bus Interface was implemented that could support the CPU on an FPGA board. The data-path is modified to perform arithmetic on 8-bit, 16-bit and 32-bit signed or unsigned integers. It was also necessary to add support for the correct generation of condition codes as specified by Motorola [11]. The control path is modified to cater for 16-bit Motorola instruction decoding, the addressing modes outline earlier and CPU interrupt and exception handling. Control ROM capacity is increased and the control word expanded to 64 bits. More complex sequencing has also been added, to cater for branching within micro-programs and the insertion of wait stages when interfacing the CPU with peripherals. All internal data transfer occurs through a 32 bit bus. The lower order byte of this bus is valid for a byte (8-bit) operation and the lower order word is valid for word (16-bit) operation. The remaining bits are either 0 or to be ignored. If a register is being written using a byte or word operation the lower 8 or 16 bits are the only ones affected by the operation. An overview of the hardware put in place is found in the schematic on the following page.

#### 2.2 Functional Unit

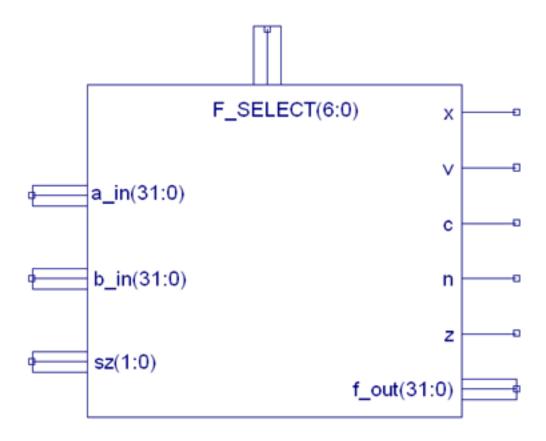

Figure 2.1: Functional Unit Block Diagram

It is necessary to be able to perform the essential arithmetic and shift operations in this module. Condition code generation must also be considered. The Functional Unit consists of two main components, an ALU and a shifter. Two inputs, A and B feed the ALU operands while The B input feeds the shifter. A size control input signal is also needed to distinguish between operation sizes. This is particularly important for the rotate instructions of the shifter and for correct condition code generation. In keeping with the Motorola instruction set 00 represents a byte operation, 01 a word operation and 10 a long-word operation. The ALU and shifter are fed simultaneously and each generates a result and appropriate condition codes. It is then the function of MUX F and MUX FC to choose the correct condition codes to send to out of the functional unit and to the condition code registers. An operation control inputs selects the desired ALU function. This is detailed in table 2.1. F Select is a 7 bit word that controls the entire operation of the unit. Bit 6 is fed to MUX F and MUX FC to distinguish between ALU and shift operations. Bits 5 and 4 respectively carry the extend bit (X) and the carry bit (C) from the

system register to the shifter. Bits 3 down to 0 choose ALU operation, and bits 2 down to 0 select a shifter operation. A 32-bit result is always generated, however the correctness of the generated result is dependant on the size of the operation. This is also true for the condition codes generated. The operations supported provide functionality identical to the Motorola instructions add, subtract, logic and shift operations and a basis on which to perform more complex operations such as multiply, divide and add binary coded decimal through the use of micro-programming.

| F Select | Function                        |

|----------|---------------------------------|

| 00000    | Transfer A                      |

| 00001    | Increment A                     |

| 00010    | A + B                           |

| 00011    | A + B + 1                       |

| 00100    | Negate B                        |

| 00101    | Decrement A                     |

| 00110    | A B $(A + (/B + 1))$            |

| 00111    | Transfer A                      |

| 0100x    | A and B                         |

| 0101x    | A or B                          |

| 0110x    | A xor B                         |

| 0111x    | Negate A                        |

| 1x000    | Arithmetic Shift Right          |

| 1x001    | Arithmetic Shift Left           |

| 1x010    | Rotate Right                    |

| 1x011    | Rotate Left                     |

| 1x100    | Rotate Right with extend (ROXR) |

| 1x101    | Rotate Left with extend (ROXL)  |

| 1x110    | Logical Shift Right             |

| 1x111    | Logical Shift Left              |

Table 2.1: Functional Unit Operation Select

This block is also responsible for generation of the negative (N) and zero (Z) condition codes. The Z condition is generated by examining the result and setting a flag if the lower order 8, 16 or 32 bits are all zero. In two complement arithmetic, the most significant bit determines the sign. If it is 1 then the integer can be interpreted as negative.[8]

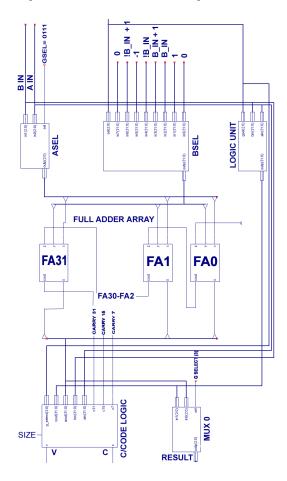

#### 2.2.1 The Arithmetic and Logic Unit

The ALU is 32-bits wide and controlled by a 4 bit select input (GSELECT) and a 2 bit size input (SZ). Bit 3 of the control signal chooses between logical and arithmetic operation within the unit. The arithmetic has been implemented using an array of full adders. Following *Digital Design* [8, Mano pgs 119-120] a HDL description has

encapsulated the functionality of a 1 bit adder, correctly generating a sum and carry out given a carry in and inputs X and Y and Z. This full adder was then instantiated 32 times using the *generate* VHDL synthesis function. This function allows multiple instantiations of the same entity using a loop counter. Other than the first carry in, which is zero, each carry out is fed into the carry in of the more significant adder.

Figure 2.2: ALU Block Diagram

#### Performing operations

Addition is performed by feeding each individual bit of A and B in to the X and Y inputs of the full adders. The carry will propagate from LSB to MSB and be set in the most significant carry out. Subtraction is performed by the twos complement method. The B operand in first negated, and then incremented to obtain its twos complement form and the fed into the Y inputs. The A input is fed as normal into the X inputs When decrementing A, a twos complement minus 1 is sent into the Y inputs of the full adders. Similarly, for single operand operations such as transfer a zero is applied to the Y inputs.

The logic is implemented by feeding each input into the gates in question. These gates are automatically generated by the synthesis tool given correct HDL

```

Source : ALU32.vhd

BIN <=LongZero

when G_SELECT="0000"

- Transfer A

else

LongOne when G_SELECT="0001"

- Increment A

BIN

when G_SELECT="0010"

- Add B to A

when G_SELECT="0011"

-A+B+1

B_{IN+1}

Not B_IN when G_SELECT="0100"

- !B

when G_SELECT="0110" else

- Decrement A

(not B_IN)+1 when G_SELECT="0101" else

— 2s Compliment of B

LongZero;

```

Figure 2.3: BIN control CSA. BIN Feeds the Y input of the adder array

specification. For example, AOUT <= AIN xor BIN is the VHDL statement that will perform exclusive-or on the inputs AIN and BIN

#### Condition Codes

The MC68008 uses 5 condition codes to perform branching functions. Overflow, or V, is set when a sign change occurs on an operand. In two complement arithmetic, which relies on a modulo numbering system, this flag can be generated by an XOR on the MSB entered to functional unit input with the MSB of the desired operation result. A 1 will indicate the sign has changed. The Carry or C flag indicates a carry out of an addition or a borrow out of a subtraction. The C flag is set when the most significant carry of an ALU operation is 1 except for subtraction. The borrow in subtraction is only set if the input operand A is greater than input operand B, otherwise carries generated by two complement subtraction are ignored and C is 0. Extend or X is set to the value of C for arithmetic functions only and is simply fed out as a replica of the C signal. It remains unassigned for logical operations. The position of the most significant bit of the result in the ALU is dependent on the size input. When generating Carry and Overflow condition codes for Word and Byte operations it is necessary to consider the 16th and the 8-th input and carry bits respectively. Any output more significant than these should be discarded as they are not guaranteed to be correct.

#### Implementation and Example

To implement the above two multiplexers decide what enters the X input and what enters the Y input of the adder array. These MUXs are controlled by G Select. 1 for increment, -1 for decrement and (not B) + 1 for subtract are three of the choices for the Y input. When only one input is required a Zero is sent through B to the adder array. A bit-vector of 32 bits is used to store the carries, which then can be operated on using concurrent assignments. A MUX decides which result to send to the ALU output.

In an example operation we feed 2 into input A and 3 into input B. Subtraction is desired so GSELECT is set to 0110. Two complement of B is fed from the MUX into the adder array while A is fed directly. The size of the operation is set to byte

(00). Since 2-3 is -1 the output is 111111111 or -1 in byte two complement form. Carry is set because a borrow has occurred, similarly a sign change has occurred on A and therefore the V flag is set.

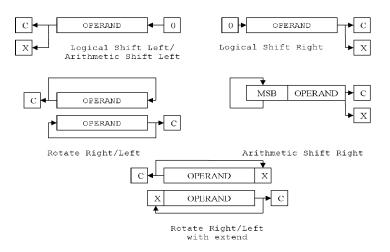

#### 2.2.2 The Shifter

The Motorola supports arithmetic shift through ASL and ASR, logical shift through LSL and LSR, bitwise rotation through ROL and ROR and rotation with the extend bit (X) acting as an expansion to the operand in question through ROXL and ROXR. Arithmetic shifting influences the C and X condition codes. When shifting left the MSB sets carry and extend. A zero is shifted in from the right. Shifting right, the LSB sets the carry and the MSB is shifted in from the left. When rotating the carry is set to be the bit that has been rotated from the MSB to the LSB or LSB to the MSB, the extend bit is not effected unless rotating with extend. In this instance X is set from C but acts as the LSB or MSB of the operation. Logical shift is exactly the same as arithmetic shift except 0 is filled in from the left when shifting right. This functionality is encapsulated in the following diagrams.

Figure 2.4: 68000 Shifting. Source: MC68000 Programmers Reference

#### Implementation and example

The VHDL CPU shifter takes carry in and extend in from the system register. Depending on the size of the operation, combinatorial logic will shift the input left or right and produce a result. A requirement of shifting is that writing to the system register is enabled. This is to ensure condition codes are set correctly and correct operation of the ROXL instruction. The shifting operations have been implemented in VHDL using combinatorial logic. An example listing is found in figure 2.4. This code piece ensures proper rotation under each operand size. The shifter code causes the Xilinx synthesis tool to infer a set of multiplexers that generates a barrel-shifter capable of shifting and left or right once per clock cycle.

```

-- Source : Shifter.vhd

- Rotate Right setting carryout to be the rotated bit

case SZ is

when "00" =>

S_OUT(6 downto 0)

\leq S_IN (7 downto 1);

S_{-}OUT(7)

\leq S_{IN}(0);

C_OUT

\leq S_{IN}(0);

X_OUT

<= '0';

V OUT

<= '0'

S_OUT(31 downto 8)

when "01" =>

\leq S<sub>-</sub>IN(15 downto 1);

S_OUT(14 downto 0)

S_OUT(15)

\leq S_{IN}(0);

C_OUT

\leq S_{IN}(0);

X_OUT

<= '0';

V_OUT

<= '0';

<= "00000000000000000";

S_out (31 downto 16)

when "10" | "11" \Rightarrow

<= S_IN (31 downto 1);

S_OUT(30 downto 0)

S_OUT(31)

\leq S_{IN}(0);

C_OUT

\leq S_{IN}(0);

<= '0';

V_OUT

X_OUT

<= '0';

when others =>

S_OUT(31 downto 0)

<= 32 X;

V_OUT

\langle = 'X':

C_OUT

\langle = 'X';

X_out

\langle = 'X';

end case;

```

Figure 2.5: VHDL Rotate Right using case for combinatorial logic

In an example using the shift-and-add method of multiplication, we are required to shift left and shift right at different stages. Given two byte operands 00001000 and 00000011 we are to obtain the result 00011000. Firstly, 00000011 is shifted right one, setting C. This is accomplished by F Select 10110. The carry flag is set and we can branch to the addition part of the algorithm given that code. Next we shift 00001000 left one to get the next partial addition. This is accomplished using F Select 10111.

#### 2.2.3 Control Registers

The microprocessor uses two registers to control the flow of micro-program and user-program execution. In order to maintain compatibility with existing 68000 code the system register has been designed to match it. As with the 68000 the user byte contains the condition codes, X,N,Z,V,C. The system byte contains support for seven levels of interrupts in IPL2,1 and 0. This holds the current interrupt level

and is used in processing external interrupts after every instruction. The S bit, or supervisor bit, is designed to inform the system whether or not it is executing in user or supervisor mode. In the 68000 programming model certain instructions, such as RESET, may only be executed in supervisor mode. This bit is set when executing system level operations such as handling exceptions. The trace bit (T) is set when the CPU is operating in trace mode. A trace exception loads in the trace vector handler which may contain code to push the system registers to a stack. This is useful in debugging software as the programmer can see exactly what is contained in all the system registers after every instruction execution.

Figure 2.6: The System Register

The second control register is the Micro-CCR. This register is 4 bits wide and is identical to the SR for bits 0 to 3. The function of the Micro-CCR is to provide a separate means of tracking conditions generated by micro-instructions. In Microcode that performs multiple cycle operations it may be necessary to consider condition codes generated without affecting the condition codes in the system register. This distinction is illustrated by taking the example above. In a micro-coded shift and add multiplication we can branch to an addition micro-subroutine if the bit in question is a 1. This could be done by shifting and using the carry as explained earlier. However, since unsigned multiplication in the 68000 will never produce a carry or overflow, it is necessary to ensure that the system register carry is not set. Thus, the Micro-CCR provides the codes necessary.

#### **Implementation**

The system register is implemented as a 16-bit positive edge triggered register. Load control of the SR is implemented using combinatorial logic in VHDL and s controlled by the CWORD field MC. Motorola instructions will set condition codes in one of 5 ways. Either the SR remains unchanged, C,V,Z,N are changed, C,V,Z,N,X are changed, Z is changed only, N is changed only or the SR is loaded from the internal data bus. Also, the trace and supervisor bits must be modifiable and the interrupt priority mask must be changeable. The Micro-CCR has simpler loading logic. TC is the CWORD field that dictates whether or not the CCR is loaded with the codes that are provided by the functional unit.

| MC   | Function             |

|------|----------------------|

| 0000 | Not Loading SR       |

| 0001 | Changing C,V,Z,N     |

| 0010 | Changing C,V,Z,N,X   |

| 0011 | Changing Z only      |

| 0100 | Changing N only      |

| 0101 | Set IPL Mask         |

| 0110 | Set Trace Bit        |

| 0111 | Clear Trace Bit      |

| 1000 | Set supervisor Bit   |

| 1001 | Clear Supervisor Bit |

| 1111 | Load SR              |

Table 2.2: SR Load Control

#### 2.3 Data Storage and Movement

The processor overview diagram shows how data is moved within the processor. There is an internal 32-bit data-bus that circulates data to the register file, through the ALU and to the control-path. MUX D is responsible for choosing between external data and data from the ALU and placing it on the internal data-bus where it feeds the rest of the processor. It is controlled by the CWORD field MD and when set to 1 reads external data from the Bus Interface.

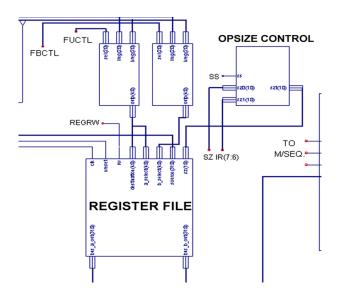

#### 2.3.1 Register File

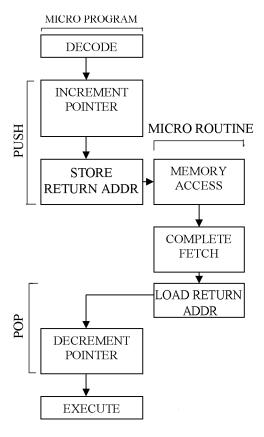

The register file contains a bank of 32 registers. Each register is 32-bits wide and is has a load control dependant on the CWORD SZ field. When the size is byte the lower order 8 bits are loaded and the rest of the register remains unchanged. This is also the case for word writes, except the lower order 16-bits are considered. The register file contains the registers D0-D7, A0-A6 the System Stack Pointer and the User Stack Pointer (A7). It also contains an internal bank of registers only addressable by micro programs. A Memory Data register and Memory Address register are provided to allow the creation of a memory read and memory write micro-routines. A micro-program can simply place the data that should be written to memory and the address to where it is to be written into these registers and branch to a micro-routine. The RRW field of the CWORD controls whether a register is written or not.

In the Motorola 68000 each instruction will contain at least one effective address (EA) which will act as a source or destination for operand fetching and write back. In the same vein as the memory registers EA Data and EA Address are provided to allow the exploitation of common operand addressing modes within instructions. The vector address register stores the base address of a to-be-executed

Figure 2.7: Register File and Control

exception handler. The remainder of the register file consists of temporary registers T0 to T8 and a Zero provider. The temporary registers are to be used in the storing of intermediate results of micro-operations and micro-programs. The Zero register simply provides a constant zero for clearing registers.

| Register                                      | Address     |

|-----------------------------------------------|-------------|

| D0-D7                                         | 00xxx       |

| A0-A7                                         | 01xxx       |

| System Stack Pointer                          | 10000       |

| EA Address                                    | 10001       |

| EA Data                                       | 10010       |

| Memory Address                                | 10011       |

| Memory Data                                   | 10100       |

| T0 T8                                         | 10100 11100 |

| Vector Address Register - 11110 Zero Provider | 11111       |

Table 2.3: Internal Register Map

#### Register Addressing and Selection

Register writing is controlled by an RW signal. A 5 bit destination control is provided to choose a register to write. There are two output ports from the register file to cater for the input of 2 operands into the ALU and to cater for simultaneous selection of an address register and a data register for placement onto the data and address busses.

Since destination and source selection is encoded in a 68000 instruction word the register file must be capable of being controlled by the CWORD and by the instruction currently being executed. The multiplexer FUCTL, FBCTL and SZCTL dictate which entity is controlling the register file and how. When SZCTL is set to 0 then the CWORD field SZ controls the size of an operation. When SZCTL is set to 1 the SZ field is controlled by the 68000 instruction word bits 7 and 8, the bits that specify the different operation sizes in the 68000 instruction set.

FUCTL feeds the register destination and port A output selection while FBCTL controls the B output selection. These multiplexers are instrumental in generating the correct register file addresses for destination and selection. When FUCTL and FUBCTL select lines are 000 the CWORD field ASEL, BSEL and DEST control register file addressing and all 32 registers are accessible. In a typical 68000 two operand instruction the instruction bits 3:0 and 11:9 control destination and source registers. When FUBCTL and FUCTL are not 000 these are the bits that control destination and source selection.

The maximum number of registers addressable with 3 bits is 7. It is therefore necessary to modify these bits in order to enable access to the Address Registers, located from register 8 to 15. When FUBCTL and FUCTL selections are 001 and 010 a 1 is concatenated onto the instruction bits 3:0 and 11:9 to allow the instruction to access a total of 16 registers. It is noted that it is still not possible for the instruction to access registers reserved for internal operation, this can only be done by the CWORD. The CWORD must be aware of the addressing mode in order to append the 1 to any instruction address and access the address registers. Table 2.3 gives a list of data registers while Table 2.4 defines FUBCTL and FUCTL operation.

| Binary | FUCTL             | FBCTL                                        |

|--------|-------------------|----------------------------------------------|

| 000    | BSEL from CWORD   | DEST/ASEL from CWORD                         |

| 001    | IR[11:9] to B Out | IR[11:9] to A Out and Data Reg. Destination  |

| 010    | IR[3:0] to B Out  | IR[3:0] to A out and Data Reg. Destination   |

| 011    | IR[11:9] to B Out | IR[11:9] to A out and Addr. Reg. Destination |

| 100    | IR[3:0] to B Out  | IR[3:0] to A out and Addr. Reg. Destination  |

Table 2.4: Destination and Source Selection in the Register File

#### 2.3.2 Data Bus and Address Bus Selection

It is necessary in any CPU to provide a means of selecting what is put on the data bus and the address bus. This function has been tied into what operands are selected for entry into the Functional Unit. MUX A controls the address bus and input A of the ALU while MUX B controls the data bus and the B input of the ALU.

#### MUX A and B assignments

Controlled by the CWORD field MA, this multiplexer has 4 inputs. Firstly, it provides a means of transferring what is selected on the A port, and the B port of

the into the ALU and the address bus. This is done through input 0, A out and 3, B out. This allows any register to be used for addressing, any register to be passed to the ALU or through the ALU to the IR or PC and back into the register file. The second input is the PC. The program counter needs to be placed on the address bus during instruction fetching and immediate operand fetching. The last input to MUX A is a vector address input. It is necessary to load the PC with a vector address when executing and exception handler routine. MUX A provides a means by which this address can be transferred from the vector decoder into the register file.

Mux B is fed the B output of the register file. The next input is the displacement register. This register is used in conjunction with the PC input of MUX A when executing instructions that adjust the PC using a 32-bit displacement. The current IPL mask is also an input to MUX B as it is necessary to compare it with the requested IPL when processing interrupts. Lastly, the entire system register has been specified as an input. This is to allow for any arithmetic manipulation of the SR that may be deemed necessary and allows the SR to be directly put on the data bus when saving the SR during interrupt processing.

MUXes A and B are implemented in code using processes to infer combinatorial logic.

#### 2.3.3 The IPL control Module

This module is a small entity that stores a pending interrupt request. If multiple interrupts are requested between interrupt handling then this module will latch the highest value request. In practical terms this is done using a comparator connected to the IPL pins and a 3 bit register. This hardware is inferred using the VHDL constructs detailed below. The signal MUXI is connected to an insanitation of a 3-bit positive edge triggered register.

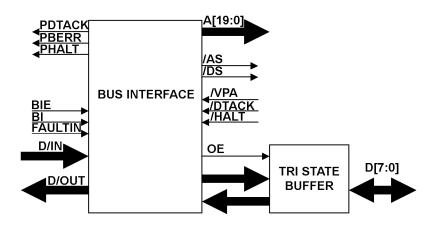

#### 2.4 The Bus Interface

It is necessary for any CPU to communicate with memory and peripheral devices. As outlined in the introduction, any CPU that is to be put on the FPGA board must use a bus interface compatible with the existing bus implementation. The bus interface protocols as defined by Motorola for 68008 8-bit operation are compatible with the ROM, RAM and ASIC and therefore are sufficient for this purpose. This design does not strictly follow the timing of the Motorola 68008 bus cycle as defined

in the *Programmers Manual*[10], as it contains certain cycles that are not applicable in this design context (such as empty clock cycles). The atomic Read-Modify-Write cycle has been omitted here as it is only deemed useful in multiprocessor situations when using the Test and Set instruction in creating locks. There is scope, however, to add this in at a later time. Similarly bus arbitration cycles have been omitted. However, the strobe generation, insertion of wait states and data bus operation are identical.

Figure 2.8: Bus Interface Block Diagram

#### 2.4.1 Implementation

To provide abstraction from the CROM, the bus interface has been designed as a separate entity capable of performing independent bus cycles. Control signals /DS (Data Strobe), /AS (Address Strobe) are generated as necessary. It receives address data and operand data from MUXes A and B. The bus interface is connected directly to the address bus, and through a tri-state buffer to the data bus. A separate tri-state buffer module is used for the data-bus as its abstraction makes it easier to handle bi-directional communication. The address bus is simply placed in Hi-Z when it is not being used and would not benefit from such an abstraction. When data is read from the data bus it is passed to MUX D and enters the data and control paths. Due to the fact that data bus is only 8-bits wide the bus interface needs extended functionality to handle reads and writes of words and long words. This essentially entails the BI being capable of multiple read and write cycles in a single operating mode.

The bus cycles generate signals in a finite sequence and it was decided that a VHDL finite state machine would be the simplest and most readable way of designing such an interface. The bus interface is implemented in VHDL using a two-process state machine. The first process handles clocking. On the positive edge of each clock cycle it updates a CurrentState register with a NextState register. The second process generates the combinatorial logic to handle state changes. The bus interface advances states depending on assigned inputs and outputs.

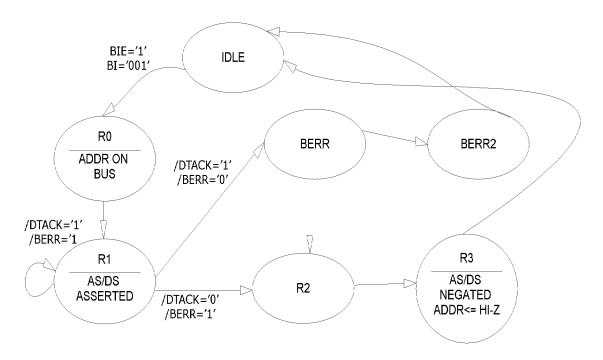

Figure 2.9: Sample Read Operation State flow (Simplified)

When BIE is high the module is either performing a write cycle, a read cycle or an interrupt acknowledge cycle depending on the input field BI. While these operations are being performed the CAR address remains constant and the microsequencer only advances the CAR when the bus interface generates a finished signal (PDTACK). The reason for this implementation is to allow for the insertion of wait stages in bus cycles. Since it can not be certain how many wait states will be inserted, simple micro-program NOPs will not suffice and the progression of the micro-program must be blocked until the bus cycle has completed. Any form of read or write cycle must use the third form of the CWORD, as outline later in this document.

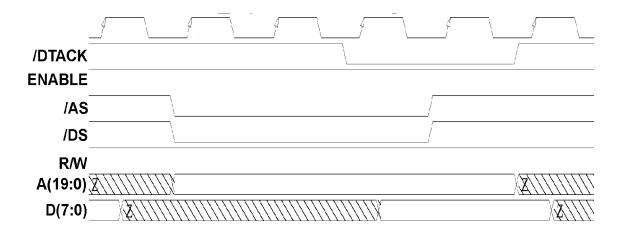

#### 2.4.2 Read and Write Cycles

In order to perform a read cycle BIE is set to enable. It is necessary to choose an operation using the BI input and provide the bus interface with a pointer to the location of the base byte i.e. an address. According to the operation size the bus interface will start at state RO and generate the bus signals as indicated in figure 2.11. The BI stays in the state R1 until DTACK is pulled low by the peripheral device, indicating data is on the bus. The lower byte is then latched in R2 by ensuring the tri-state buffer output enable is pulled low in order to read the data driven by the peripheral device. If the operation is a read-byte operation then PDTACK is pulled low, causing the CAR to be incremented and the data to read to the CPU registers. In order for PDTACK to effect the CAR in such a way it is necessary for the wait-for-DTACK condition to be set in the CCOND field and the address of the next micro-instruction to be specified using the 3rd form of the

```

if ENABLE='0' then— Wait Till We're Asked.

<= "ZZZZZZZZZZZZZZZZZZZZZZ"; — Not using A_Bus

ADDR_OUT

DATA_BUS_OUT

<= "000000000"; --- Or data bus

D_OE

<= '0'; — disable tristate output

<= '0'; — not latching interrupt level</pre>

LatchInt

P_nBERR

<= '1'; — no bus error exception

P_nHALT_w

\langle = '1'; -- no halt

<= '1': — no dtack to the microsequencer

p_nDTACK

<= "00000000"; — not latching any bytes

L_LByte

L_{-}HByte

<= "00000000";

H_LByte

<= "00000000":

H_HByte

<= "00000000";

OpSize

<= Byte; -- default opsize

<= '1'; — not writing

RnW

<= '1'; — no address on bus

nAS

<= '1'; — no data from us

nDS

<= idle; -- wait for enable</pre>

NextState

```

Source: BusInterface.vhd

Figure 2.10: Setting outputs for the idle state

CWORD. If the operation is word or long-word then this cycle is repeated 2 or 4 times each time incrementing the address pointer and latching the higher order bytes. PDTACK is not pulled low until the full operation is complete. This way a read-byte or read-longword operation does not have to enable the bus interface 2 or 4 times, it is done independently.

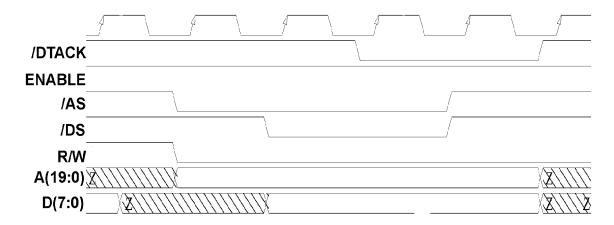

In performing a write cycle the CPU sends the address and data to be written into the bus interface and selects a write operation and again waits on PDTACK. The strobes are set in as illustrated in figure 2.12 and the write cycle begins. Like the read cycle the data is written in one-byte increments. When writing to the data bus, the tri-state buffer is set to output enable causing the data bus to be driven out of the high-impedance state.

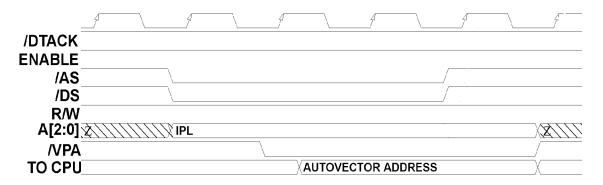

#### 2.4.3 Interrupt Acknowledge and Bus Error Cycles

68008 supports 3 levels of interrupts, however in keeping with the 68000 7 levels are supported by the project hardware. Interrupts are processed at the end of every instruction, and those generated during an instruction execution are labelled as pending by the IPL control module and processed after the execution. When handling interrupts the bus interface must perform an interrupt acknowledge cycle. When instructed to do so by the control word the Bus Interface module will start an interrupt acknowledge cycle as illustrated with figure 2.13. /AS and /DS are pulled low, R/W high and the requested interrupt level is fed into the bus interface and on to the address bus lines A0 to A2. If the peripheral wishes to request its own vector number /DTACK is pulled low and the vector number is placed on the data bus. It

Figure 2.11: Bus Read Cycle

Figure 2.12: Bus Write Cycle

is now up to the micro-program to load and execute the appropriate vector.

When opting for auto-vectoring, i.e. when the interrupting device requests a pre-defined vector address, the peripheral pulls /VPA low instead of /DTACK. The bus interface will generate one of seven vector address and send it to the CPU to be loaded into the Vector Register. The vector handler can now be loaded and executed.

The last function performed by the bus interface is Bus Error control. If the bus error flag is pulled low by an external device during a bus cycle then PBERR is pulled low and a bus error exception is generated. During this error handling FAULTIN is pushed high. If a second bus error occurs during bus fault exception processing then a double bus fault has occurred and the processor enters the halt state only to be restarted by reset. This in done by pulling PHALT low.

Figure 2.13: Auto-vector peripheral bus cycle

| BI Input | Function                       |

|----------|--------------------------------|

| 000      | Read Byte                      |

| 001      | Read Word                      |

| 010      | Read Long-Word                 |

| 011      | Write Byte                     |

| 100      | Write Word                     |

| 101      | Write Long-word                |

| 110      | Interrupt Acknowledge          |

| 111      | Reserved for Read-Modify write |

Table 2.5: BI Select

#### 2.4.4 Bus Interface Hardware

All Bus Interface hardware is inferred automatically with the exception of an 8-bit register which is a temporary storage register designed to hold the interrupt vector. Latches are used to store intermediate read cycle values, such as the first three bytes of a long-word memory read.

## 2.5 Sequencing and Control

The most complex section of the CPU hardware design is the control path. The control path contains logic to generate control signals for the data path and is responsible for program sequencing and specifying how operands are manipulated in the design.

There are two common design approaches when considering control unit design. Hardwiring is physically implementing control using a state machine designed with often complex logic. Hardwired design involves considering the states necessary to provide functionality in the data-path and subsequently deducing a state machine capable of providing this functionality. This approach is the fastest and most hardware-economical approach to the design. However, this approach is also a very inflexible way of creating a design. Specifying hardware control for a CISC instruction set, which by definition has complexity built in at processor level, is a difficult task. Moreover, once the design has been implemented it is difficult to expand control without re-wiring the control design in order to add in new states.

Figure 2.14: CROM and Control Address Register

Micro-programming is a less hardware-economical but more flexible approach. An on chip control ROM is used to provide control signals to the data-path. The control words are provided by an address kept in a Control Rom Address Register. This register is combined with program flow logic to provide Micro-program flow functionality. The CROM can be programmed to provide the functionality necessary an can be easily modified and expanded without modification of the surrounding architecture [9, Mano, Kime] This is the methodology that has been used in the CPU design. It is felt that a micro-programmed design would be easier to understand for

anybody wishing to examine the design as it is based on a simple hardware specification. Also, and more importantly, a CROM design would be reprogrammable and expandable in future giving the design an increased adaptability. Since the FPGA is based on SRAM look-up tables for interconnection of primitive components there is no performance advantage in opting for a hardwired approach. A motivation of this project is to show how a CISC design may be implemented. The fact that Micro-coding is used in CISC designs such as the Pentium IV and the 68008 was another deciding factor in choosing micro-coding over hardwired control[7]

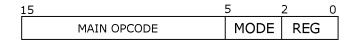

#### 2.5.1 Control Path Registers

A Motorola instruction consists of a single 16-bit word plus an optional set of extension words that are used to specify addressing mode information and displacement information in branching. As a result a 16-bit instruction register is provided and is loaded with the information on the internal data bus when the CWORD field IL is high. This register is the outputted to the instruction decoder which is responsible for CAR address generation.

The program counter is a 32-bit register, 20 bits of which generates a valid memory address for instruction and immediate operand fetching. It is implemented using a register and combinatorial logic that generates a load signal depending on the PL CWORD field. The PL can be incremented in one clock cycle by setting PL to be 01. When PL is 00 the register holds its value. If a 11 is set the PC is loaded with whatever data is on the internal data-bus. This is necessary to facilitate use of jumping and branch instructions that apply a displacement to the PC.

```

-- Source : Control.vhd

PCControl: process (PL-w, PCout_w, PCInc_out, Data_In)

begin

case PL_w is

when "00" =>

<= PCout_w;

-- Hold PC

MUX.P

when "01" =>

MUX.P <= PCInc_out;

-- Increment PC

when "10" =>

MUX.P <= Data_In;

-- Load PC

when "11" \Rightarrow

MUX_P

-- Load PC

\leq Data_In;

when others =>

end case;

end process;

```

When processing branching instructions such as BRA or BCC a signed extension word of 32-bits is used to specify a displacement to be added to, or subtracted from the PC. In order to facilitate this addition or subtraction in a quick manner, without having to use a temporary register in the file, a displacement register has been provided. Fed into MUX B, it is possible to select the displacement register as a B input to the functional unit, together with the PC into the A input from MUX

A and perform the subtraction or addition and subsequent write back to the PC in a single clock cycle.

#### 2.5.2 Micro-sequencing

A micro-sequencer is the lynchpin of any micro-programmed architecture. It is responsible for the generation of the next CAR address thus defining the next set of control signals to be applied to the data-path.

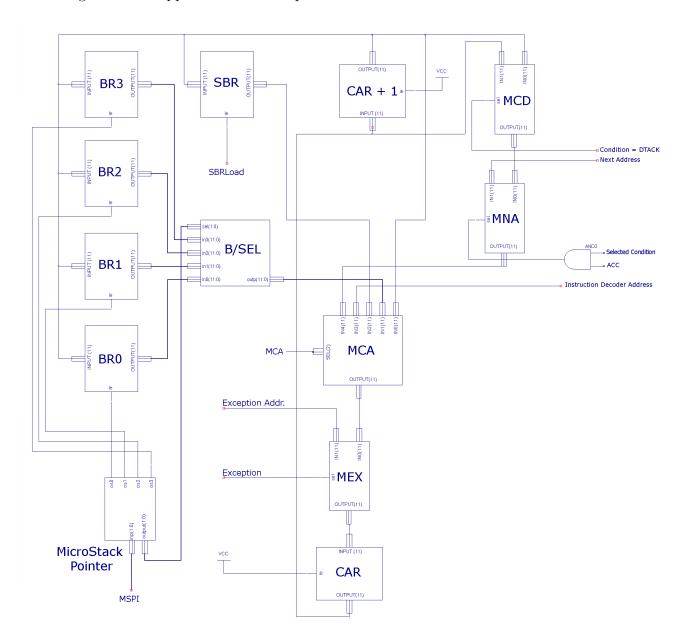

Figure 2.15: Microsequencer Block Diagram

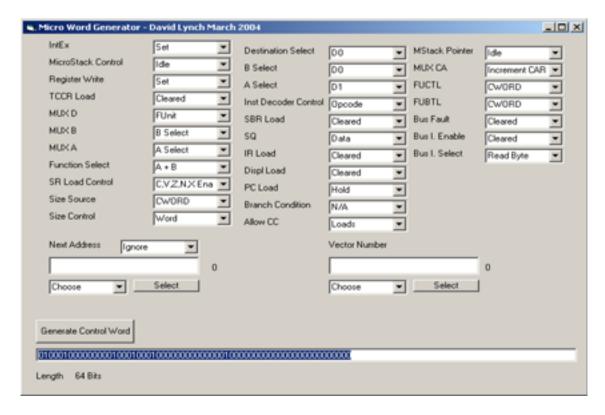

The CROM has been designed as 4096 words deep, meaning a 12-bit address is required. This gives ample space for micro-coding the 68008 instruction set provided the micro-programs are written in a modular fashion and take advantage of common