## **Hardware Details of the 68000**

- CPU Pin Descriptions

- System Timing Diagrams

## **CPU Pin Descriptions**

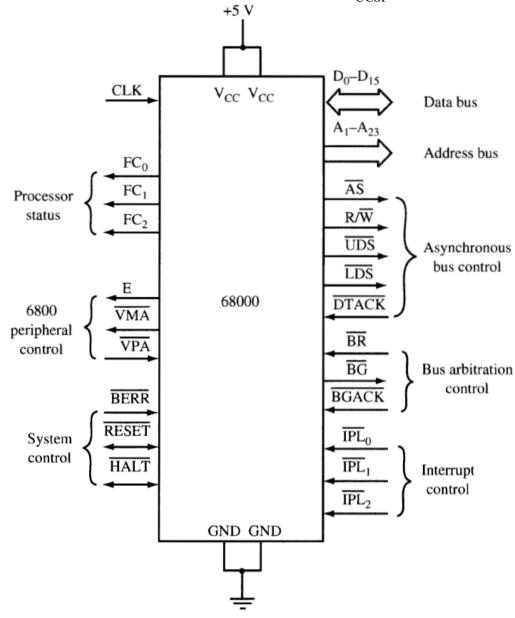

Figure 7.1: 68000 CPU input and output signals (pg 240) [1]

- 1. Antonakos J.L., The 68000 Microprocessor, Hardware and Software Principles and Applications, 1993, Prentice Hall, New Jersey.

- 2. Clements A., Microprocessor Systems Design, 68000 Hardware, Software, and Interfacing, 1992 PWS-KENT Publishing, Massachusetts.

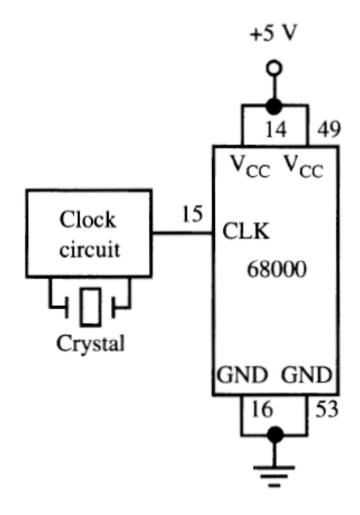

### V<sub>CC</sub>, GND, CLK

- Processor power and clock inputs.

- 2 pins each for VCC and GND

- Both must be connected

#### VCC:

- 8MHz,  $5V \pm 5\%$ , 1.5 watts

#### CLK:

- Max  $t_{rise}$  and  $t_{fall}$  are 10ns (all versions except 5ns for 12.5MHz and 16MHz)

- TTL-compatible with 50 percent duty cycle.

Antonakos J.L., The 68000 Microprocessor, Hardware and Software Principles and Applications, 1993, Prentice Hall, New Jersey.

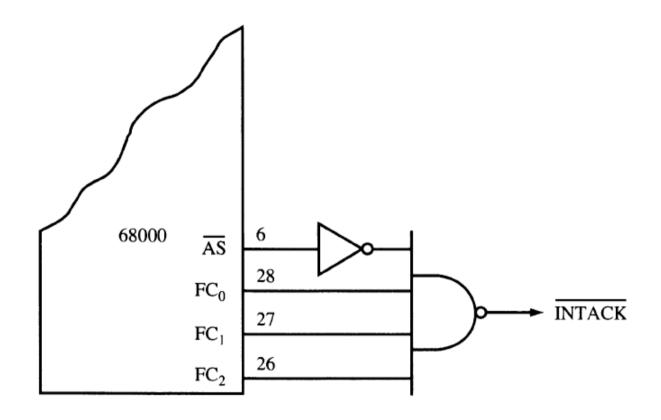

### FC<sub>0</sub>, FC<sub>1</sub>, and FC<sub>2</sub>

- FC<sub>0</sub>, FC<sub>1</sub>, and FC<sub>2</sub> are function code outputs

- Informs external circuitry of current internal processing state of the 68000.

- Only valid when AS is active.

| FC <sub>2</sub> | FC <sub>1</sub> | FC <sub>0</sub> | Cycle type            |

|-----------------|-----------------|-----------------|-----------------------|

| 0               | 0               | 0               | Reserved*             |

| 0               | 0               | 1               | User data             |

| 0               | 1               | 0               | User program          |

| 0               | 1               | 1               | Reserved*             |

| 1               | 0               | 0               | Reserved*             |

| 1               | 0               | 1               | Supervisor data       |

| 1               | 1               | 0               | Supervisor program    |

| 1               | 1               | 1               | Interrupt acknowledge |

Table 7.1: Function code outputs (pg 241) [1]

\*By Motorola, for future use.

- Frequently used to restrict memory accesses by connecting the FC pins to the memory address decoding circuitry.

<sup>1.</sup> Antonakos J.L., The 68000 Microprocessor, Hardware and Software Principles and Applications, 1993, Prentice Hall, New Jersey.

<sup>2.</sup> Clements A., Microprocessor Systems Design, 68000 Hardware, Software, and Interfacing, 1992 PWS-KENT Publishing, Massachusetts.

Figure 7.3: Interrupt acknowledge cycle decoder (pg 242) [1]

<sup>1.</sup> Antonakos J.L., The 68000 Microprocessor, Hardware and Software Principles and Applications, 1993, Prentice Hall, New Jersey.

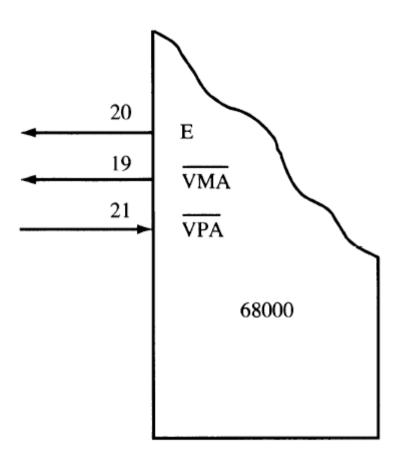

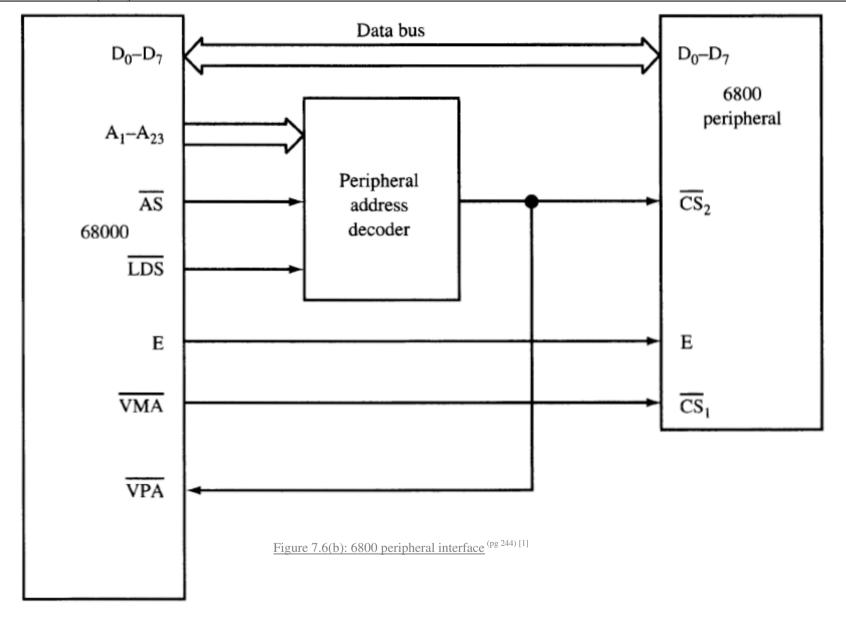

# $\underline{\mathrm{E}}, \overline{\mathit{VMA}}, \underline{\mathrm{and}} \overline{\mathit{VPA}}$

- Provides the capability to control older 6800 peripherals.

- E clock,  $\overline{VMA}$  (valid memory address), and  $\overline{VPA}$  (valid peripheral address)

#### E clock:

- Generates proper timing signals for 6800 peripherals.

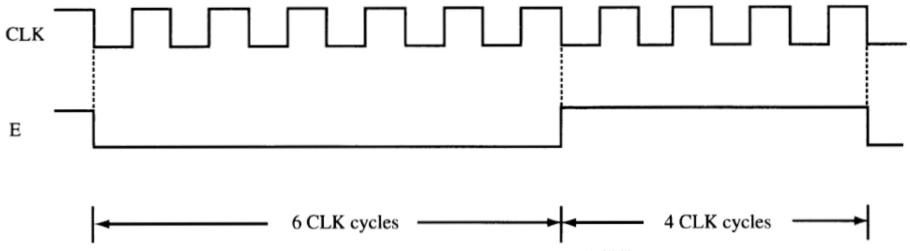

- 1/10<sup>th</sup> of 68000's clock frequency, with 40% duty cycle (high for 4 CLK cycles, low for 6 CLK cycles)

Figure 7.5: Timing relationship between CLK and E (pg 243) [1]

Sequence of events during 6800 peripheral access:

- The 68000 places address of 6800 peripheral on  $A_1$  through  $A_{23}$ .

- VPA input is activated (low) to request synchronization of 68000

- 68000 synchronizes with the E clock, then activates VMA (outputs a low).

- Data transfer takes place.

Antonakos J.L., The 68000 Microprocessor, Hardware and Software Principles and Applications, 1993, Prentice Hall, New Jersey.

<sup>1.</sup> Antonakos J.L., The 68000 Microprocessor, Hardware and Software Principles and Applications, 1993, Prentice Hall, New Jersey.

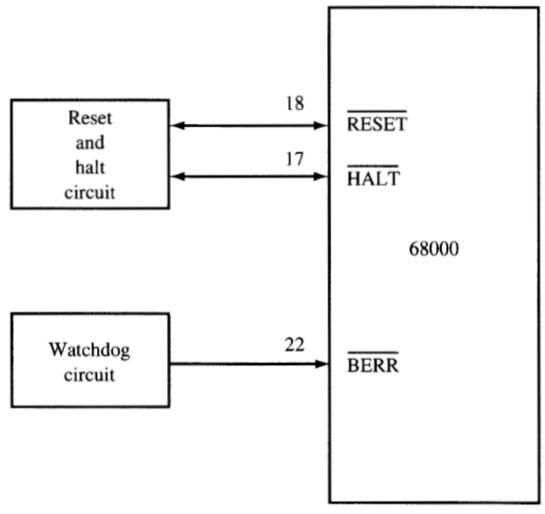

# $\overline{RESET}$ , $\overline{HALT}$ , and $\overline{BERR}$

- Provides system control.

- RESET,  $\overline{HALT}$ , and  $\overline{BERR}$  (buss error) are panic buttons of the 68000

- External circuitry pulls *BERR* low to indicate to the 68000 that an error has occurred during execution of current bus cycle.

- RESET and HALT lines are bi-directional

Sequence of events when bus error occurs:

- If *HALT* is not asserted when bus error occurs:

- The 68000 will terminate the current failed cycle and start bus error exception processing.

If  $\overline{HALT}$  was asserted before or at the same time as  $\overline{BERR}$ :

- o The 68000 will terminate the current failed cycle, and enter a "do nothing" state

- o Once the *HALT* line is deactivated, the processor will rerun the previous cycle

- o Note that  $\overline{BERR}$  must be deactivated at least one clock cycle before  $\overline{HALT}$  is deactivated.

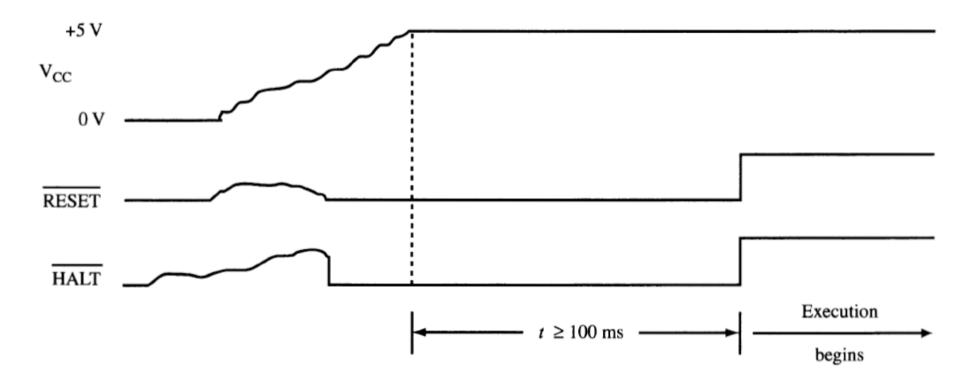

### Example (Power On Hardware Reset):

- RESET and  $\overline{HALT}$  both act as inputs

- After power on, *RESET* and  $\overline{HALT}$  are taken low for at least 100ms

- This stabilizes  $V_{CC}$  and results in total processor reset

### Example (Normal Execution Hardware Reset):

- RESET and  $\overline{HALT}$  both act as inputs

- Asserting RESET and HALT at least 10 clock cycles resets the 68000

Figure 7.9: Power-on RESET and HALT timing (pg 246) [1]

### Example (Normal Execution Peripheral Soft Reset):

- RESET acts as an output

- The RESET instruction causes the 68000 to output a low level on *RESET* for 124 clock cycles.

- This resets all external circuitry connected to *RESET* without affecting the state of the processor.

Figure 7.7: Power-on RESET and HALT timing (pg 245) [1]

<sup>1.</sup> Antonakos J.L., The 68000 Microprocessor, Hardware and Software Principles and Applications, 1993, Prentice Hall, New Jersey.

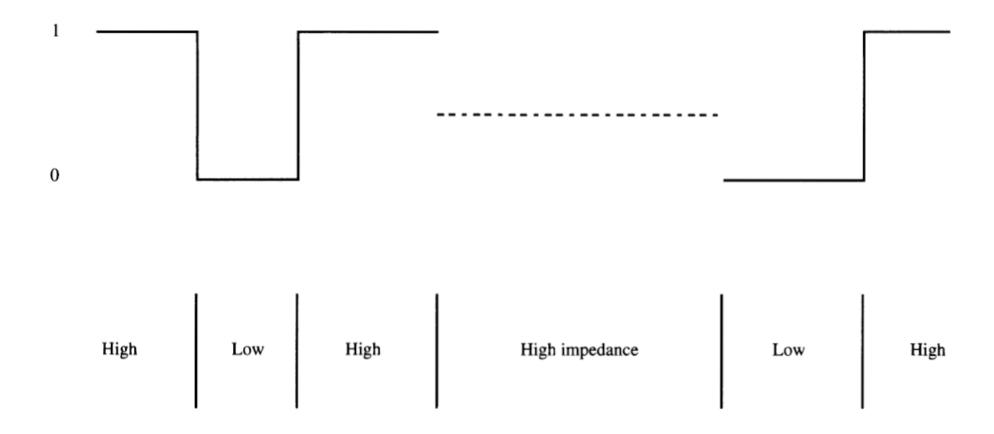

### Example (External Peripheral Halt):

- HALT acts as an input

- HALT may be driven low at any time by an external device.

- The processor then completes the current bus cycle and halts:

- All tristate signals are set to high-impedance

- All control signals are inactive.

- Execution returns to normal when *HALT* is deactivated

Figure 7.8: Tristate signal levels (pg 246) [1]

<sup>1.</sup> Antonakos J.L., The 68000 Microprocessor, Hardware and Software Principles and Applications, 1993, Prentice Hall, New Jersey.

MPS Hardware 004: 16/35

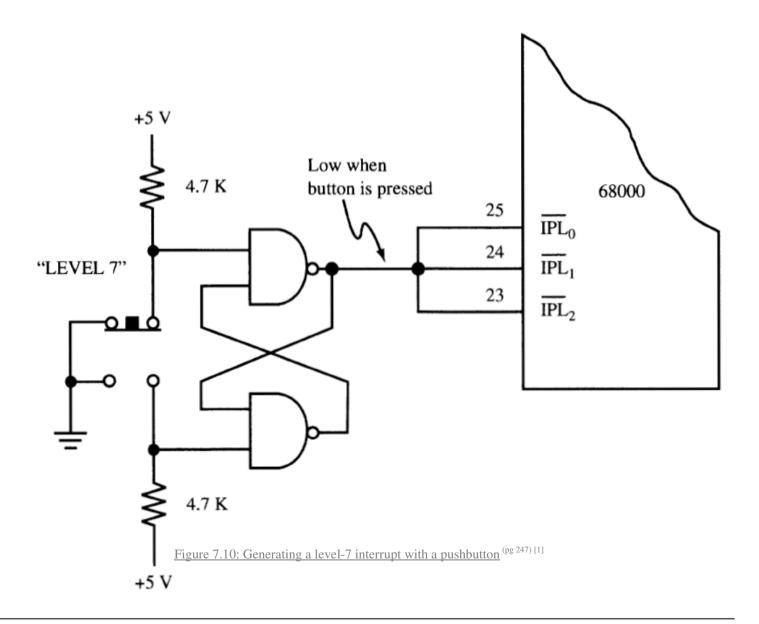

$$\overline{\mathit{IPL}_0}$$

,  $\overline{\mathit{IPL}_1}$  and  $\overline{\mathit{IPL}_2}$

- Provides interrupt control/request

- $\overline{IPL_0}$ ,  $\overline{IPL_1}$  and  $\overline{IPL_2}$  are used by external circuitry to send an interrupt request to the 68000.

- Vectored and auto-vectored interrupts may be requested.

|                  | Interrupt | •                |                          |

|------------------|-----------|------------------|--------------------------|

| IPL <sub>2</sub> | ĪPL₁      | ĪPL <sub>0</sub> | Interrupt level*         |

| 1                | 1         | 1                | 0 (Lowest, none)         |

| 1                | 1         | 0                | 1                        |

| 1                | 0         | 1                | 2                        |

| 1                | 0         | 0                | 3                        |

| 0                | 1         | 1                | 4                        |

| 0                | 1         | 0                | 5                        |

| 0                | 0         | 1                | 6                        |

| 0                | 0         | 0                | 7 (Highest, nonmaskable) |

<sup>\*</sup>Note the inversion of the binary bits needed on  $\overline{IPL}_2 - \overline{IPL}_0$ .

Figure 7.2: Interrupt level encoding (pg 246) [1]

- 1. Antonakos J.L., The 68000 Microprocessor, Hardware and Software Principles and Applications, 1993, Prentice Hall, New Jersey.

- 2. Clements A., Microprocessor Systems Design, 68000 Hardware, Software, and Interfacing, 1992 PWS-KENT Publishing, Massachusetts.

## $\overline{BR}$ , $\overline{BG}$ and $\overline{BGACK}$

- Provides bus arbitration control (use to place 68k in a wait state while hardware connected to the bus)

- *BR* (bus request), *BG* (bus grant), and *BGACK* (bus grant acknowledge) are used when a device (DMA controller or another processor) is taking over control of the bus

### Sequence of events for bus arbitration control:

- Requesting device (bus master) activate BR low to request the 68k system bus

- 68k will respond to bus master by asserting BG low to indicate its willingness to release control of the bus at the end of the current cycle.

- To take control, the new bus master asserts *BGACK*

- When the new bus master wishes to relinquish control of the bus, it does so by negating  $\overline{BGACK}$

There are 4 conditions that must be met before the new bus master may activate  $\overline{BGACK}$ :

- $\overline{BG}$  is active

- AS is inactive

- DTACK is inactive

- BGACK is inactive

Provides asynchronous bus control (for proper operation of external hardware)

- All lines are outputs except  $\overline{DTACK}$  (input)

- AS (address strobe) : to indicate that a valid memory address exists on the address bus.

<sup>1.</sup> Antonakos J.L., The 68000 Microprocessor, Hardware and Software Principles and Applications, 1993, Prentice Hall, New Jersey.

<sup>2.</sup> Clements A., Microprocessor Systems Design, 68000 Hardware, Software, and Interfacing, 1992 PWS-KENT Publishing, Massachusetts.

- R/W (read/write): determine whether the current cycle is a read or write.

- *UDS* (upper data strobe)

- *LDS* (lower data strobe)

- $\circ$  To transfer 8 bits (1 byte) of data: either  $\overline{UDS}$  or  $\overline{LDS}$  asserted

- o To transfer 16 bits: both UDS and LDS asserted low

- *DTACK* (data transfer acknowledge)

- When *DTACK* is asserted by external hardware, the 68000 recognizes that the current bus cycle can be completed