# The DP8344 BCP® Inverse Assembler

National Semiconductor Application Note 688 Laura Johnson July 1990

#### OVERVIEW

The DP8344 BCP Inverse Assembler is a software package for use in a Hewlett Packard Logic Analyzer. It was developed by National Semiconductor's Arlington Design Center to allow disassembly of the DP8344 op-code mnemonics.

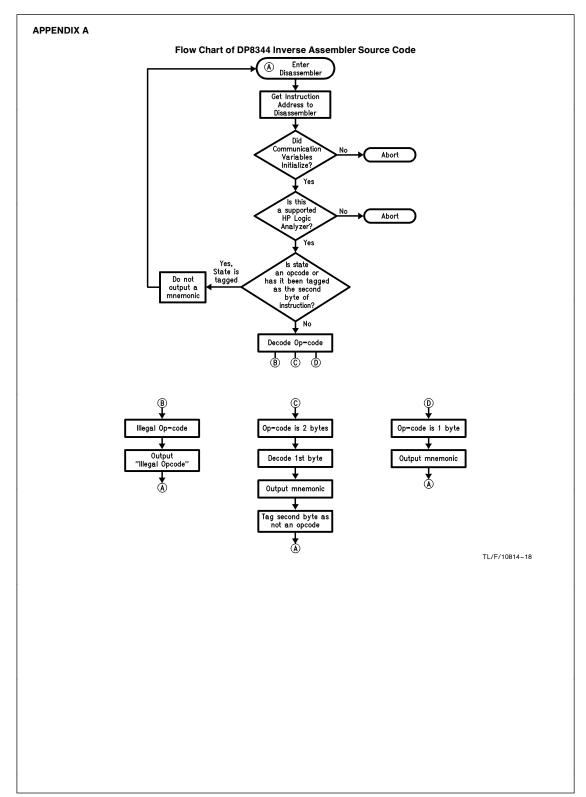

When developing systems using a RISC processor such as the DP8344, the need often arises to know the sequence of events that occurred in real time in the system. The actual execution flow that occurred in the system can be determined by monitoring the states on the Instruction memory Address bus and the Instruction memory bus of the DP8344 with a Hewlett Packard Logic Analyzer. The DP8344 BCP Inverse Assembler enhances this development tool by displaying the BCP instruction op-code mnemonics on the logic analyzer's screen. This Application Note lists the equipment needed as well as the necessary information to set up, use, and obtain the DP8344 BCP Inverse Assembler. Additionally, the source code flow chart for the DP8344 BCP Inverse Assembler is provided in Appendix A of this Application Note.

#### **EQUIPMENT REQUIRED**

The following equipment is required to use the DP8344 BCP Inverse Assembler:

- DP8344 BCP Inverse Assembler; Available from National Semiconductor.

- 2. HP1650A or HP1651A Logic Analyzer, or HP16500A Logic Analysis System with an HP16510A State/Timing Card installed

- 3. DP8344 Biphase Communications Processor in a System

It is assumed that the reader is familiar with the operation of the HP Logic Analyzer. For further information refer to the Operation Reference Manual provided with the HP1650A or 1651A Logic Analyzers, or with the HP16510A Logic Analyzer Module. Information pertaining to the operation of the logic analyzer in a state mode will be useful.

## SYSTEM SETUP

A block diagram of the setup of the system for using the DP8344 BCP Inverse Assembler is shown in *Figure 1*. The target system refers to a system containing a BCP which is running. The DP8344 BCP Inverse Assembler is software which has been loaded into the HP Logic Analyzer. The target system is interfaced to the DP8344 BCP Inverse Assembler through the HP Logic Analyzer's channels.

An example of a target system is a Multi-Protocol Adapter (MPA $^{\text{TM}}$ ) installed in a personal computer. The MPA

Design/Evaluation Kit includes both the hardware and software that allows the MPA to emulate a 3270 or 5250 display terminal and to support industry standard PC emulation software. The MPA Design/evaluation Kit is available from National Semiconductor (Part No. D88344MPA-EB). All the examples in this document were generated using an MPA board and it's associated software for the target system.

Additional equipment which one may find useful includes an extender card and an 84-pin PLCC Adapter. The extender card brings a PC board out of the PC chasis, allowing easier access to the BCP. An 84-pin PLCC Adapter allows one to directly connect the channels of the logic analyzer to the pins on the BCP. Emulation Technology, Inc., makes an 84-pin PLCC Adapter which it calls a BUG KATCHER. (It is Part No. BC-4-084-PCC5-00000).

The sample target system described above includes the following equipment:

- 1. IBM® Personal Computer or compatible

- 2. MPA Development Kit

- 3. Extender Card (optional)

- 4. 84-Pin PLCC Adapter

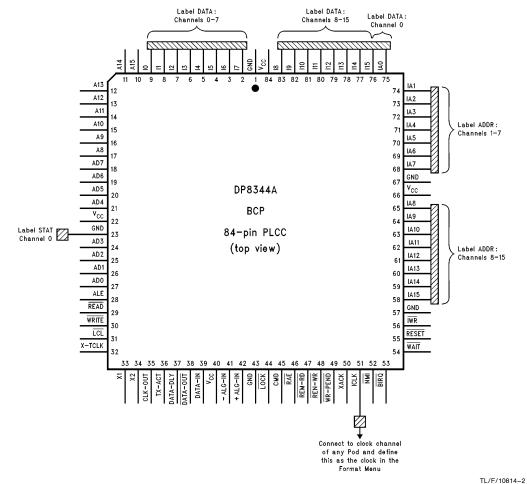

The DP8344 BCP Inverse Assembler requires information from both the Instruction memory Address bus and the Instruction memory data bus of the BCP in the target system. Thus, these pins must be connected to the logic analyzer. The 84-pin PLCC Adapter allows one to directly connect the logic analyzer channels to the BCP. Figure 2 provides a detailed view of the pin connections from the DP8344 to the logic analyzer. The pins can be connected to any of the pods as long as the channel and label definitions are defined accordingly in the FORMAT Menu as described later in this Application Note.

## STARTING THE DP8344 BCP INVERSE ASSEMBLER

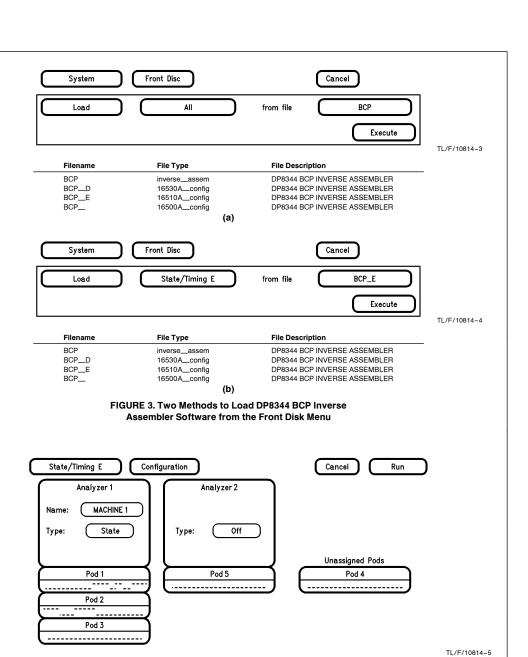

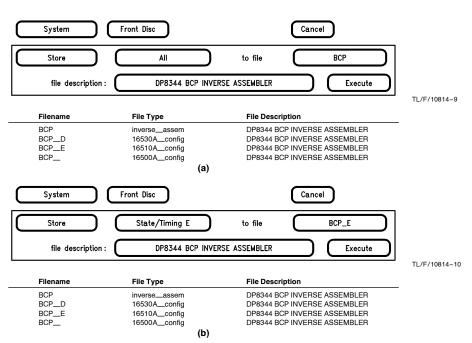

Once the system hardware has been set up, the DP8344 BCP Inverse Assembler software needs to be installed in the HP Logic Analyzer. The 3½ inch diskette provided in the DP8344 BCP Inverse Assembler Package contains the software for the HP Logic Analyzer. Load the DP8344 BCP Inverse Assembler Software into the HP Logic Analyzer by selecting either LOAD ALL from file BCP, or LOAD State/Timing E, from File BCP.E as in Figure 3. This automatically loads the DP8344 BCP Inverse Assembler as well as the stored State/Timing configuration into the HP Logic Analyzer.

FIGURE 1. Block Diagram of the System Set Up

BCP® is a registered trademark of National Semiconductor Corporation. MPA $^{TM}$  is a trademark of National Semiconductor Corporation. IBM® is a registered trademark of International Business Machines Corporation \N-688

TL/F/10814-1

## **CONFIGURING THE HP LOGIC ANALYZER**

The DP8344 Inverse Assembler software contains a State/Timing configuration which one may use without any changes. The designer can change this default configuration, or define an entirely new configuration to meet their own systems needs. However, certain parameters must exist in the configuration for the DP8344 Inverse Assembler to work. These parameters will be described using the default configuration as an example.

Internal communication variables are set as the logic analyzer collects data from the target system. Therefore, the

logic analyzer's configuration must follow the setup described here. Figures 4-6 show the configuration provided on the DP8344 BCP Inverse Assembler diskette. One may create their own configuration by adding more labels and connecting more channels to the target system than shown in the examples in this document. This will allow one to monitor the system activity according to their needs. However, the logic analyzers system configuration must include the following:

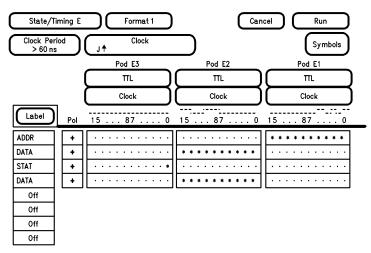

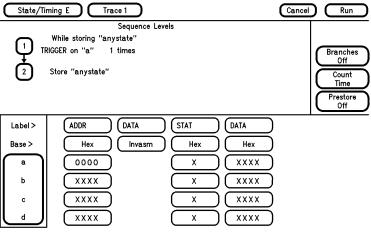

In the Configuration Menu, as in Figure 4, one must:

- 1. Define the Analyzer Type to be a State Analyzer.

- 2. Assign at least two pods to the State Analyzer.

FIGURE 2. Pins Connected to Logic Analyzer Pods

2

FIGURE 4. Configuration Menu on Logic Analyzer

In the Format Menu, see Figure 5, define the labels and assign the channels in the following manner:

- 1. Create labels ADDR, DATA, and STAT.

- 2. Assign the channels connected to the labels as follows:

- i. Label ADDR refers the channels connected to the Instruction memory Address Bus on the DP8344. From Figure 2, these are pins 75 through 68, and pins 65 through 58. To use the default configuration the pins from the Instruction memory Address bus must be connected to channel 0 through 15 of Pod E1.

- ii. The DATA label refers to the channels connected to the Instruction memory data bus on the DP8344. From Figure 2, these are pins 9–2, and pins 83–76. To use the default configuration the pins from the Instruction memory Data bus must be connected to channels 0 through 15 of Pod E2.

- iii. For the label STAT it is not necessary to actually connect any of the defined channels to the BCP. However, it is recommended that one does connect all defined channels to a pin such as ground. This is because the BCP does not use a STATUS bus. The STAT label must be defined in the Format Menu. In the example shown in Figure 5, the channel assigned to the STAT label corresponds to a ground pin on the BCP connected to channel 0 of Pod E3.

- 3. Define the Clock to be the channel which corresponds to the connection from the pod clock connection to pin 51, ICLK, on the DP8344. In the example shown in *Figure 5*, the J clock means that ICLK is connected to the clock channel of pod E1. Set the clock to trigger on the rising edge of ICLK.

FIGURE 5. Format Menu on Logic Analyzer

TL/F/10814-6

FIGURE 6. Trace Menu on Logic Analyzer

TL/F/10814-7

The trigger may be defined in the Trace Menu according to the information desired. For example, in *Figure 6*, the trace is set to trigger when the BCP executes the program, i.e., the Instruction memory Address bus is 0 hex.

Once the system configuration has been developed, it must be linked with the inverse assembler software. First, load the DP8344 BCP Inverse Assembler Software by either method shown in *Figure 3*. Second, create a configuration by either:

- i. modifying the configuration file which was loaded into the HP Logic Analyzer with the DP8344 BCP Inverse Assembler or

- ii. by loading another State/Timing Configuration which has been stored on diskette.

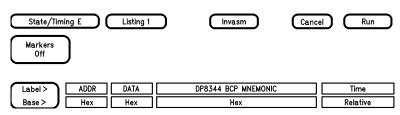

Third, verify that the three labels: ADDR, DATA and STAT exist in the Format Menu. Fourth, in the State Listing Display, shown in *Figure 7*, select the base field below the label DATA. This will generate seven pop-outs. Select the "Invasm" pop-out to allow the mnemonics to be displayed. Finally, store the new configuration to the DP8344 BCP Inverse Assembler using one of the two methods shown in *Figure 8*. Whenever this configuration file is loaded, the inverse assembler will automatically load. Note that storing the configuration to the Inverse Assembler will write over any previously stored configurations. Therefore, it is recommended that one back up all of the stored configurations by copying them to a backup diskette.

The system is now set to capture the BCP op-codes from your system and display them as mnemonics.

TL/F/10814-8

FIGURE 7. State Listing Display

The Data Label with base Hex will display the op-codes in Hex Format. The DP8344 BCP MNEMONIC Label is generated by selecting the base type for the Label DATA to be "Invasm".

FIGURE 8. Two Methods to Store Configurations to the DP8344 BCP Inverse Assembler Software

## **DP8344 BCP INVERSE ASSEMBLER OPERATION**

An inverse assembler converts instructions captured by the logic analyzer in binary form into mnemonics. Thus it makes it much easier to follow the program's execution flow. Furthermore, one can still use the logic analyzer to view other useful information by specifying the trace conditions, labels and channel connections in the logic analyzer's configuration file.

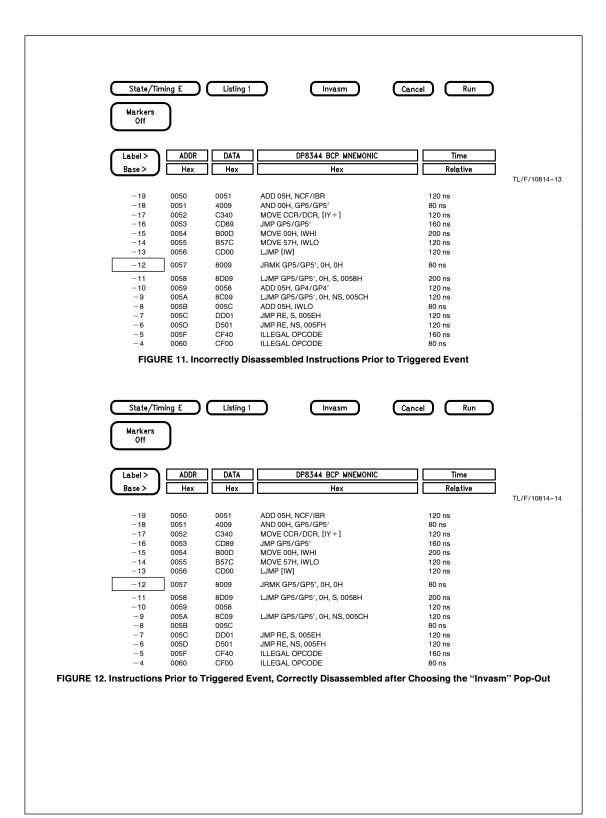

One needs to be aware of how the captured information is actually diassembled. The inverse assembler begins disassembling at the event which was triggered upon. Hence, any information captured prior to the trigger may not be correctly disassembled. To ensure valid disassembly of states captured prior to the trigger, one must scroll the display so the first instruction one wants disassembled is the first line on

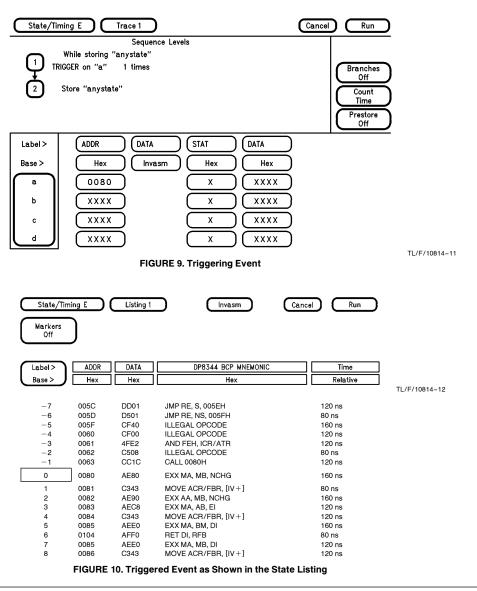

the display. Then select the "Invasm" pop-up on the top line of the State Listing Display. This causes the inverse assembler to disassemble the code from the first line on the display. For an example, refer to Figures 9 through 12. The inverse assembler was set to trigger when the Instruction Address Bus was 80 hex, as in Figures 9 and 10. The two byte instructions captured prior to the trigger were not correctly disassembled. Referring to Figure 11, one observes that line -10 is disassembled as an ADD Instruction rather than as the second byte of the LJMP instruction from line -11. To correct this, one must select "Invasm" from the top line of the State Listing Menu. The inverse assembler immediately disassembles the code from the first line on the screen. The correctly disassembled code is shown in Figure 12.

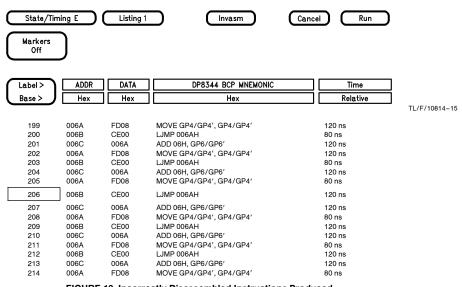

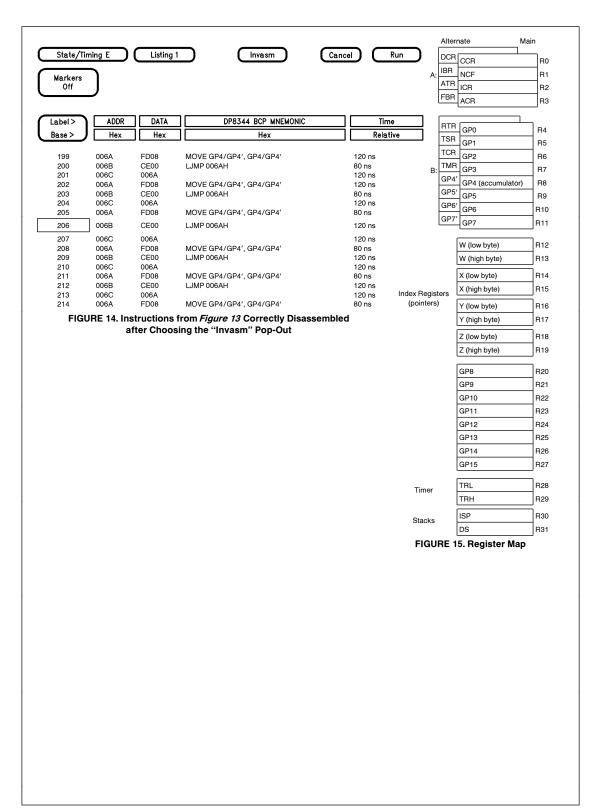

This same technique must be applied if one jumps ahead in the display and then scrolls backwards to view a certain state; in other words, you do not scroll forward through every line to reach the desired state. For example, if one manually selected the line number -12 in Figure 12 and entered line 226, the screen would display lines 219 through 234. Now if one rolls the screen backwards to display lines 199 through 214 as in Figure 13, the two byte instruction, LJMP, is once again not correctly disassembled. Therefore, select the "Invasm" pop-out and the display is correctly disassembled as shown in Figure 14.

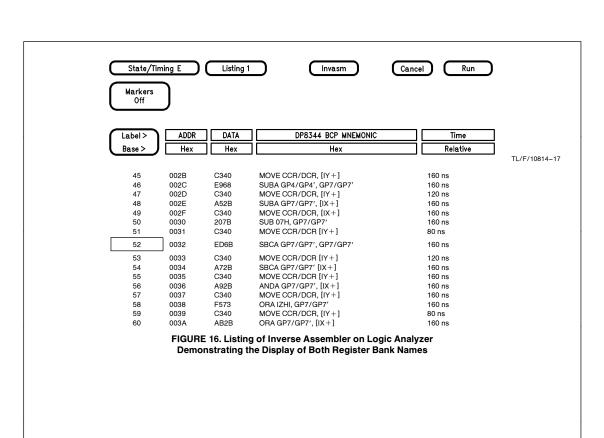

One of the features of the BCP is that it uses register banks. However, there is no external indication of the bank's state. The name of a register therefore depends upon which bank one is in, as in  $Figure\ 15$ . Due to the manner in which the inverse assembler disassembles the captured data, keeping track of the correct register name meant that one would constantly have to scroll the screen back to the last EXX statement and hit the "Invasm" pop-out to ensure that the displayed register names are correct. Hence, to avoid this inconvenience, the register names for both banks are displayed at all times. Refer to line 45 of  $Figure\ 16$  for an example. The op-code decodes to MOVE where the source register is R0. Therefore, the register names for R0 in both banks: Main Bank A — CCR, and Alternate Bank A — DCR, are displayed.

To view the op-code in both mnemonic form and hex form, as in *Figure 16*, define the DATA label twice in the Format Menu, as in *Figure 4*. Then, select the base label to be "Hex" for one and "Invasm" for the other in the State Listing.

## **OBTAINING THE DP8344 BCP INVERSE ASSEMBLER**

The DP8344 BCP Inverse Assembler package for use in a Hewlett Packard Logic Analyzer can be obtained from National Semiconductor. Included in the Inverse Assembler Package is the DP8344 BCP Inverse Assembler software, including configuration files as described in this application note. These will be on a 3½" diskette formatted for use in the HP Logic Analyzer. Additionally, a 5½" diskette formatted for use on an IBM personal computer or compatible, containing the DP8344 Inverse Assembler source code can be obtained upon a request from National Semiconductor.

If one owns the HP 10391A Inverse Assembler Development Package, the source code can be modified to make any improvements one wishes to make to the DP8344 BCP Inverse Assembler. Note that it is not necessary to have the HP 10391A Inverse Assembler Development Package to use the DP8344 BCP Inverse Assembler.

FIGURE 13. Incorrectly Disassembled Instructions Produced by Jumping Ahead in Display

## LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

**AN-688**

National Semiconductor National Semiconductor Corporation 2900 Semiconductor Drive P.O. Box 58090 Santa Clara, CA 95052-8090 Tel: 1(800) 272-9959 TWX: (910) 339-9240

National Semiconductor GmbH GmbH Livry-Gargan-Str. 10 D-82256 Fürstenfeldbruck Germany Tel: (81-41) 35-0 Telex: 527649 Fax: (81-41) 35-1

National Semiconductor Japan Ltd. Sumitomo Chemical Engineering Center Bldg. 7F 1-7-1, Nakase, Mihama-Ku Chiba-City, Ciba Prefecture 261 Tel: (043) 299-2300 Fax: (043) 299-2500

National Semiconductor Hong Kong Ltd. 13th Floor, Straight Block, Ocean Centre, 5 Canton Rd. Tsimshatsui, Kowloon Hong Kong Tei: (852) 2737-1600 Fax: (852) 2736-9960

National Semiconductores Do Brazil Ltda. Rue Deputado Lacorda Franco 120-3A Sao Paulo-SP Brazil 05418-000 Teli: (55-11) 212-5066 Telex: 391-1131931 NSBR BR Fax: (55-11) 212-1181

National Semiconductor (Australia) Pty, Ltd. Building 16 Business Park Drive Monash Business Park Nottinghill, Melbourne Victoria 3168 Australia Tel: (3) 558-9999 Fax: (3) 558-9998