## Futurebus + Chip Set **Pin Connections**

This applications brief describes pin connections of NSC transceivers and controllers to the Futurebus+ connector as specified in Profiles B, A and F.

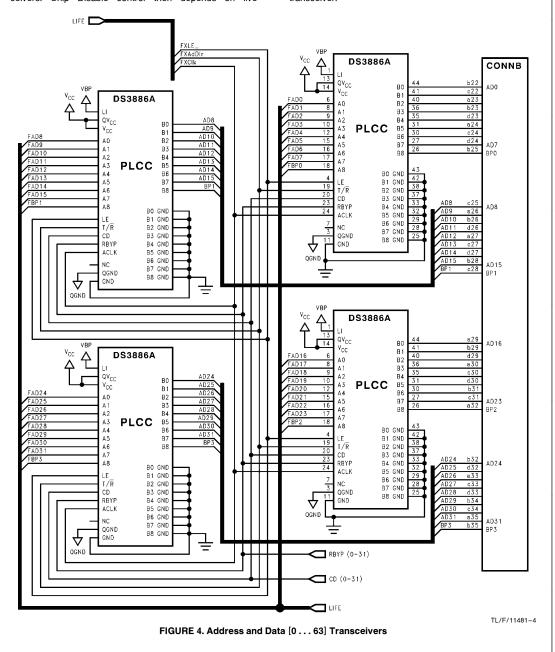

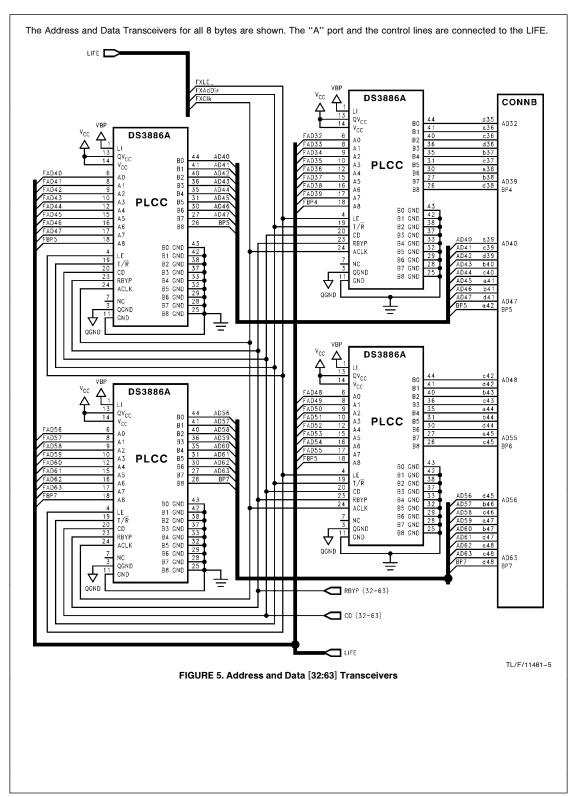

The pin connections assume that a board compliant to the Futurebus+, Profile B, will be implemented. The data path is 64 bits wide and the address width is 32 bits. Both central (required) and distributed (optional) arbitration schemes will be shown. The Profile B optional features for serial bus, tag byte, and full arbitration bus message system will also be shown. The packet mode data transfer option uses the transceiver devices in the same way shown, however, the Protocol Controller can not be used for packet mode trans-

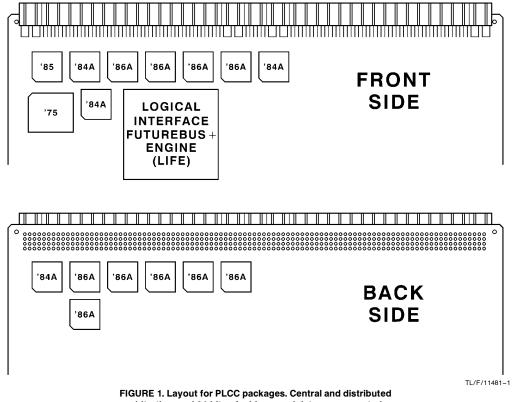

The components shown here are all pin numbered for the PLCC package. Using the PLCC package, it is difficult to meet the Profile B specification for maximum stub length when devices are mounted on a single side. The specification is 25 mm maximum, measured from the connector via to the center of the transceiver pin surface mount pad. Components can be mounted on both sides of the board and need to be for compliance to max stub length using National Semiconductor **Application Note 833** Stephen Kempainen October 1991

9-bit wide data transceivers. A recommended topographical layout is not included in this article. An experienced, talented layout person can experiment with component positioning to attain the shortest stub length with the tools and technology available for board manufacture. The solution to the stub length problem for the PLCC package is much more difficult than the PQFP package. The smaller PQFP package can easily meet the stub length specification by mounting the components on both sides of the board.

The interface has 15 transceiver devices, and 2 controllers.

- 1-DS3885 Arbitration Transceiver,

- 4—DS3884A Handshake Transceivers,

10—DS3883A or DS3886A Data Transceivers.

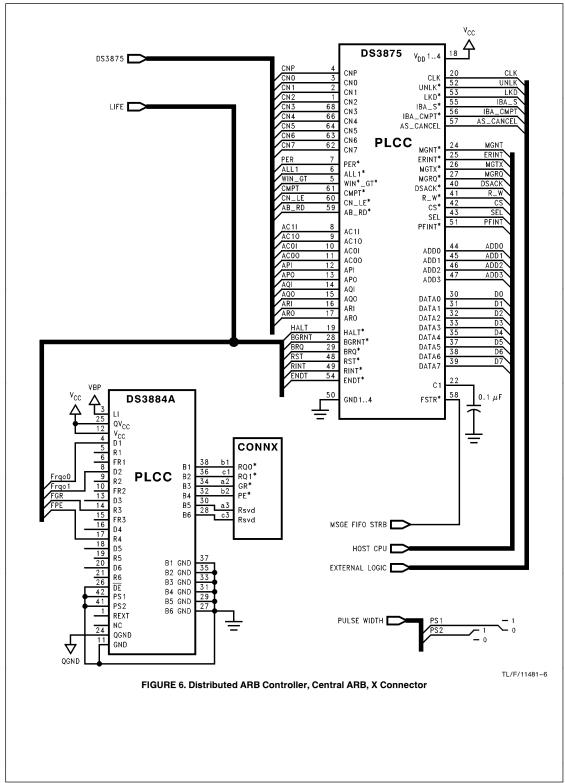

LOGICAL INTERFACE FUTUREBUS+ ENGINE Protocol Controller (not included in this drawing), DS3875 Arbitration

A 0.1  $\mu\text{F}$  capacitor is recommended for each package. The capacitor should be located as close to the package as possible. Additional protection against high frequency noise can be provided by a 0.001  $\mu F$  capacitor in parallel with the recommended capacitor.

arbitration, and 64-bits of address and data are supported. The LIFE is in a PQFP package.

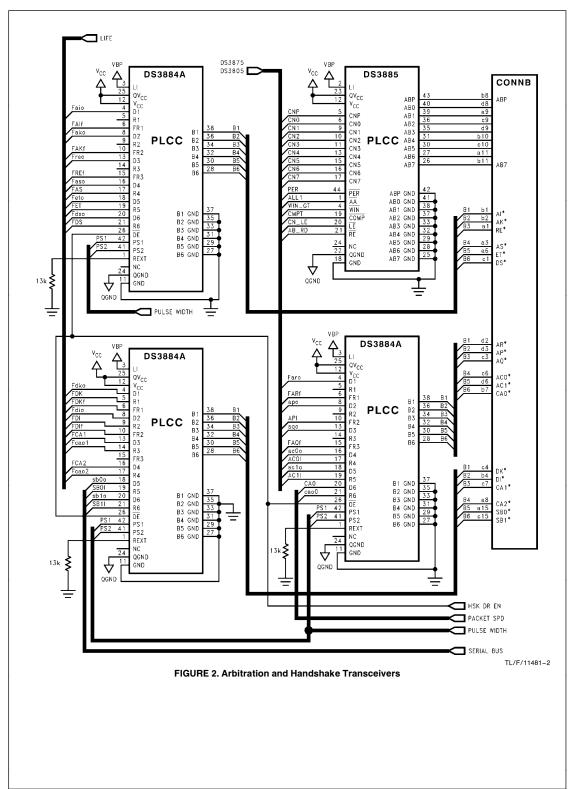

The DS3885 Arbitration Transceiver is used for message passing in the central arbitration scheme and for arbitration competition and message passing in distributed arbitration. In both arbitration schemes, it is connected to the bus exactly the same. In central arbitration, the DS3875 can be used to facilitate message transfers. It should be explained that the DS3885 preliminary data sheet pin names have been modified to match the pin names on the DS3875. This is reflected in the drawing by the preliminary names remaining on the device, while the new names (without the \*) are on the signal lines at the device.

Three DS3884A Handshake transceivers are used for the data synchronization, address synchronization and arbitration synchronization strobe signals. The additional channels on the handshake transceivers are used for control signals. The signals are divided between the 3 transceivers

so the required signals will have the filtered receiver outputs. The DI\* and DK\* signals do not require filtering in Profile B, but are shown here on filtered channels to reflect the necessity of filtering these signals in a profile that does use Broadcast/Broadcall transactions. The remaining transceiver channels are distributed with consideration for the shortest possible stub length. The synchronization signals should be given primary consideration for shortest stubs due to the low skew required between strobe and address/data signals.

If the filtered receiver outputs of the DS3884A are not used, the REXT pin should be unconnected. For the same reason, the pulse width selection pins should be tied low. All unused driver inputs should be tied low to prevent oscillation. Unused receiver outputs need not be connected.

3

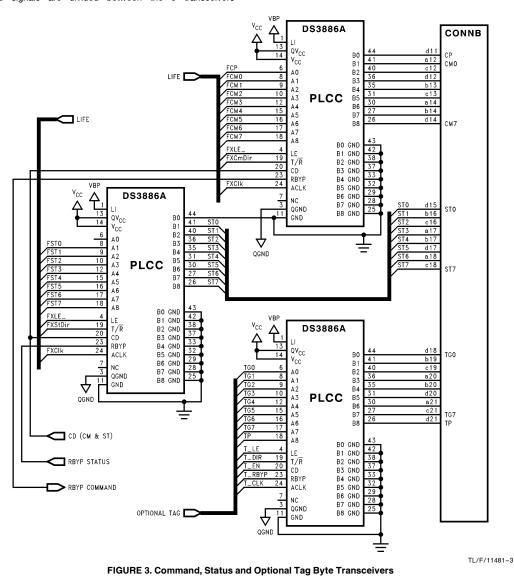

The DS3886A Latched Data transceiver is used for the Command byte and the Status byte. The command and status signals are linked to the LIFE. The control lines for the transceivers are generated by the Protocol Controller. The Chip Disable pins are connected together for all transceivers. Chip Disable control then depends on live

insertion level supported and user preference (a separate article will cover this topic). Register bypass control lines can be used as the system designer feels necessary. The optional tag byte transceiver is shown but it is completely system dependent as to the further implementation of this transceiver.

One DS3875 Arbitration controller is included as an option for a distributed arbitration board. It will also be possible to use the Arbitration controller as the message handler in the central Arbitration board. The signals on the controller are broken into groups for ease of identification.

The fourth Handshake transceiver is used for the central arbitration signals at the X connector. A handshake transceiver is chosen because there are 2 input lines and 2 output lines on each board. The receivers of the DS3884A are always on and the driver enable pin is tied low. The

other two channels can be connected to the reserved bus connectors since these signals are required to be bused by Profile B. Unused driver inputs should be tied low to prevent oscillation. Since the filtered receiver outputs are not used, the REXT pin should be unconnected to minimize power consumption. PS1 and PS2 should be tied low to prevent internal oscillations. These precautions should be followed whenever the filtered receiver outputs will not be used on a board (i.e., no support for broadcast/broadcall transactions).

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

**AN-833**

National Semiconductor Corporation 1111 West Bardin Road Arlington, TX 76017 Tel: 1(800) 272-9959 Fax: 1(800) 737-7018

http://www.national.com

**National Semiconductor** Europe

Europe Fax: +49 (0) 180-530 85 86 Email: europe.support@nsc.com

Deutsch Tel: +49 (0) 180-530 85 85 English Tel: +49 (0) 180-532 78 32 Français Tel: +49 (0) 180-532 93 88 Italiano Tel: +49 (0) 180-534 16 80

**National Semiconductor**

National Semiconductor Hong Kong Ltd. 13th Floor, Straight Block, Ocean Centre, 5 Canton Rd. Tsimshatsui, Kowloon Hong Kong Tel: (852) 2737-1600 Fax: (852) 2736-9960

**National Semiconductor** Japan Ltd.

Tel: 81-043-299-2308

Fax: 81-043-299-2408