Embedded Microprocessor

Back...

| FR Embedded Microprocessor |

Back... |

FR Series - 32 bit RISC Architecture

The Fujitsu RISC (FR) architecture is a new generation 32 bit microprocessor core which

is dedicated to resolving the twin demands of high performance coupled with low cost,

which are needed by today's high end Automotive, Consumer and Telecoms applications.

Designed from the outset to be optimised for embedded applications, the CPU has a

16 bit instruction Op Code, enabling maximum performance from low cost, half word

external memory and instruction cache widths, or else allowing double instruction

fetches for each bus cycle.

The CPU employs the same five stage pipeline and 32 x 32 Multiplier as the successful

SPARClite family but adds a new barrel shifter and a bit search unit which finds the

first 1, 0 or change in a data word. The concept of the instruction cache architecture

with its flexible locking mechanism is also replicated.

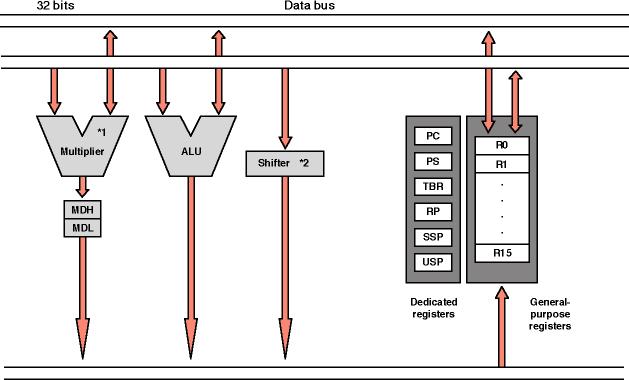

The CPU has eight dedicated 32 bit registers: Program Counter, Processor Status, Interrupt Table Base Register, Return Pointer, Supervisor and User Stack Pointers and two for multiply/divide result.

There are sixteen 32 bit, general purpose registers arranged as a single bank.

The functions of R13 to R15 are reserved as Virtual Accumulator, Frame Pointer and Stack Pointer respectively. The instruction set contains many bit manipulation instructions and data moving instructions, which are very helpful in supporting the on-chip peripheral blocks.

Although the FR is a RISC, it contains a number of extended instructions, which help assembly level programming, often unavoidable in embedded applications. An example is the store of half of the register bank to memory.

Blocks that require fast access are connected to the FR-core within a 32-Bit Harvard bus system.

Blocks that require fast access are connected to the FR-core within a 32-Bit Harvard bus system.These units are the Instruction Cache, internal RAM, the DMA-Controller and the Bit-Search unit. Resources that require simple control or status access, such as UARTs, Timers etc., are hooked up on a 16-bit peripheral bus known as the R-Bus. The R-Bus gateway to the FR-core is a bus-converter module like the one for the external bus interface. This general purpose bus, also called the "User logic bus" is used for accessing the on chip Flash ROM as well as the CAN-Interfaces, which typically require a faster and more extensive data flow to and from the FR-core than most of the other on-chip resources. The external bus also gives the user the possibility to access external memory or other memory-mapped devices on the target application, supporting seven fully configurable chip-select areas with external chip-select pins which can be controlled individually in terms of memory-area, bus-width, wait-states or alignment. |