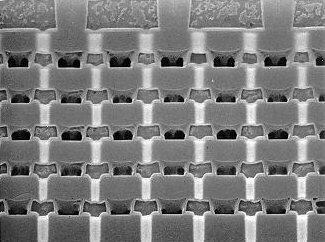

TI's 0.18-micron (leff) TImeline Technology. Cross section of 0.18-micron (leff) chip showing six levels of metal interconnect..

As digital signal processing becomes more widespread in consumer,

communications, computer and automotive applications, the need

for application-specific and customized digital signal processors

increases. TI's customizable digital signal processing cDSP

technology, coupled with the performance and density of TI's TImeline

Technology, surpasses all other technology available today in

meeting this need.

With its ability to pack 125 million transistors on a microchip and to boost performance to several times current levels, TI's TImeline Technology creates unprecedented opportunities to reach the market quickly with new, feature-rich products based on cDSP cores. The density achieved with TI's 0.18-micron technology means that dynamic random access memory (DRAM), static random access memory (SRAM), FLASH memory and read only memory (ROM) can reside on the same chip with cDSPs, communications interfaces, analog-to-digital and digital-to-analog converters, and other peripherals. The result is a true single-chip solution for many communications, computing and high-performance applications.

Equally important, the enormous integration capacity achieved with TI's TImeline Technology -- more than twice that available with current 0.25-micron technologies -- can slash development cycles by as much as half. Rather than struggle for solutions that fit within semiconductor limitations, designers can select DSPs and other modules from TI libraries or select their own logic to create a unique proprietary solution. An important part of TI's strategy of providing comprehensive DSP solutions, cDSP technology uses industry-standard application-specific integrated circuit (ASIC) design tools to combine DSP cores and peripherals with TI's gate array and standard cell ASIC libraries.

First, design support between a DSP vendor and an ASIC house can be a big problem. The design house that created the DSP core may have little experience with the ASIC vendor's software tool suite.

Similarly, the ASIC vendor often has little knowledge of DSP architecture and limited support for DSP code and debug, development tools, system modeling and in-circuit emulation. The customer is caught between two, or sometimes more vendors for support, neither of which have sufficient overall expertise to help merge the ASIC macros and a high-performance DSP core into an integrated design.

Second, as with any microprocessor, testing for DSP functional errors or bugs is paramount. When using multiple vendors, bugs can creep into components in manufacturing, since one fabrication process is different from another. Using one vendor, such as TI, can help assure that bugs are sufficiently uncovered and corrected. TI cores are used in high-volume, standard products built in harmonized wafer fabs, where processes are compatible and consistent from manufacturing facility to manufacturing facility. This not only gives the customer consistency, but flexibility as well.

Third, portability of cores from one ASIC technology to another is difficult at best and requires least-common-denominator design rules, where die sizes are large and inefficient. Also, since the characterization of the core model is unique within each ASIC vendor's technology, porting the core means starting the design over again with a new set of design rules to master. Despite claims to the contrary, there can be no completely technology-independent DSP core for ASIC design that is cost-effective and delivers high performance.

Finally, manufacturing becomes even more difficult when using multiple vendors. Each manufacturer will have different wafer fabrication processes, resulting in different characterization, electrical performance, power dissipation and so on. The results can be unpredictable, resulting in serious timing problems and even functional flaws. These problems are especially significant in devices where speed is as critical as it is in DSPs.

Customers that begin with standard DSPs may find that as their products become successful, they want to customize their processors in later generations. For these designers, cDSP offers a way to migrate their designs to greater levels of system integration and to customize their products, while shrinking time to market windows and lowering costs. The same TMS320 DSPs used in early generations of product designs can later be used as cores in cDSPs, bringing higher performance, lower cost and more robust features. The capacity available with TI's TImeline Technology permits the addition of features and peripherals without significant redesign.

TI also supplies industry-leading manufacturing processes, for which its ASIC and cDSP models are characterized. The company's design support staff is thoroughly familiar with these processes, making the prototyping and production stages of a design straightforward which improves quality and reliability. TI's multiple wafer fabs allow the company to respond to rapid production increases and long-term supply in tight markets. With 50 designs already behind them, and 30 million units shipped to date, cDSP is proven technology.

Trademark:

cDSP is a trademark of Texas Instruments Incorporated.