View your personal Web page, or receive

a weekly e-mail newsletter for what's new.

View your personal Web page, or receive

a weekly e-mail newsletter for what's new.

Access TI's on-line technical documentation.

Register today at TI&ME, and start making the most of your TI&ME.

Register today at TI&ME, and start making the most of your TI&ME.

|

September 1996, vol.13, no. 6

|

Access TI's on-line technical documentation.

|

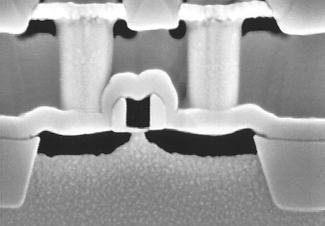

Two gate arrays Speed and power trade-offs will become virtually a thing of the past for designers who use devices from the new TGC6000 and TEC6000 families of gate array ASICs from Texas Instruments. These new devices, based on TI's recently announced 0.18 micron (L-effective) TImeline Technology, permit pre-viously unheard-of integration at ultra-high speeds while significantly reducing power consumption.

Speed and power trade-offs will become virtually a thing of the past for designers who use devices from the new TGC6000 and TEC6000 families of gate array ASICs from Texas Instruments. These new devices, based on TI's recently announced 0.18 micron (L-effective) TImeline Technology, permit pre-viously unheard-of integration at ultra-high speeds while significantly reducing power consumption.

Gate arrays and embedded arrays using TImeline Technology are compatible with core processor speeds of 500 MHz or more. In fact, TGC6000 devices, with as many as 12 million available gates, provide the foundation for next-generation, high-performance microprocessors. At the same time, devices in this family achieve optimum performance at 1.8-V, consuming up to 85 percent less power than that demanded by current 0.35-micron and 0.25-micron technologies. Extremely tight metal pitches, reduced interconnect, hierarchical floor planning and layout, advanced clocking schemes and other features allow TImeline devices to consume about 69 percent less power than competing 0.18-micron ASICs. However, devices in this family will provide full 5.5-V, 3.3-V and 2.5-V interface capabilities for mixed-voltage systems. Ultra-deep submicron technology not only increases the number of available gates that may be integrated onto a single chip, it also makes large-scale system integration possible. More important, it reduces design cycle time and time-to-market by slashing trade-off analyses, allows building from existing designs and provides enough capacity to reduce the importance of design elegance in many systems. | |

|

|

TI Home

Search

Feedback

Semiconductor Home