|

|

Inside:

Inside:

Showcase (Volume 29) is available in HTML and PDF format. - 330KB Showcase (Volume 29) is available in HTML and PDF format. - 330KB

Integrated shift register Integrated shift register

and 8-channel peripheral

driver.

Intelligent quad high-side Intelligent quad high-side

driver.

Class-D audio amplifier sets Class-D audio amplifier sets

new standards in efficiency.

Programmable D/A allows Programmable D/A allows

for speed/power optimization.

Industry's first Industry's first

programmable resolution A/D.

High-speed 10-bit A/D with High-speed 10-bit A/D with

glueless DSP interface

90-mA

loads

16-bit A/D D/A analog 16-bit A/D D/A analog

front-end.

UART provides quad-channel UART provides quad-channel

integration and 64-byte FIFO

Fully compliant 4-port Fully compliant 4-port

USB hub.

USB power distribution USB power distribution

features independant switches.

Dual low dropout regulator Dual low dropout regulator

with integrated processor

resets.

Programmable-sychronous buck Programmable-sychronous buck

regulator addresses advanced

microprocessor power needs.

High performance DSP High performance DSP

power controller

Low-voltage audio power amps Low-voltage audio power amps

designed for stero headphone

applications.

SOT-23 50mA low-dropout SOT-23 50mA low-dropout

regulator.

3-channel power supply 3-channel power supply

supervisors.

|

|

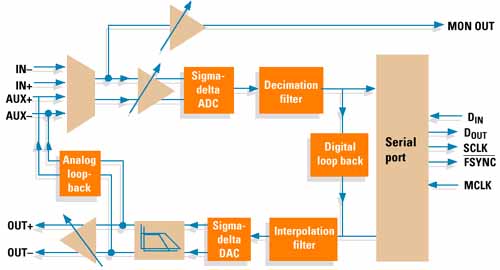

Options for analog interface applications

Product features

- Master/slave mode

- Differential output drives 600-

load load

- Single 5-V supply or 5-V analog and 3-V digital

- Power-down mode

- Input and output gain control

- Glueless DSP interface

- Characterized for operation from –40° C to 85° C (AD50I)

The TLC320AD50C/I and TLC320AD52 analog interface circuits (AICs) provide high-resolution A/D and D/A signal conversion using oversampling sigma-delta techniques. These 16-bit AICs can be used as an analog front end in modem applications, and also provide an ideal solution for business audio or motherboard audio applications. Additional applications include reduced-function modems for PDAs, point-of-sale terminals, and general DSP or MCU interface applications.

|

These 16-bit AICs can be used as an analog front end in modem applications, and also provide an ideal solution for

business audio or motherboard audio applications.

|

One of the main features of the ’AD50C/I is its master/slave capability with support for up to three slaves. The TLC320AD52 provides identical functionality to the ’AD50C, but supports only one slave in master/slave mode.

Other features of the ’AD50/52 AICs include internal 64X oversampling on the ADC and 256X oversampling on the DAC, as well as differential outputs that can drive a 600- differential load. Options for all the devices include selectable conversion rate, reset, power down, communications protocol, serial clock rate, gain control and system test mode. differential load. Options for all the devices include selectable conversion rate, reset, power down, communications protocol, serial clock rate, gain control and system test mode.

The ’AD50I is available in 28-pin SOIC (DW) package and the ’AD50C/52 is available in 28-pin SOIC (DW) and 48-pin TQFP (PT) packages.

Vol 29 November, 1998

|