|

In This Issue Special Focus on Logic

DSP Solutions

Wireless

Memory

Mixed-Signal and Analog

Business News

|

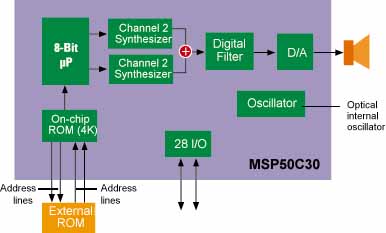

Long-duration speech processor

With a 4K internal ROM, 1024 RAM locations and 28 software- The 28 I/O pins are configurable under software control to be either inputs or outputs. A number of low bit-rate speech synthesis algorithms such as LPC, Mixed Excitation Linear Prediction (MELP) and Code Excited Linear Prediction (CELP) are available for use with the MSP50C30. These options provide great flexibility in data space use and speech quality. FM Synthesis and ADPCM are other options available for use with this device, which is suitable for learning aids, talking books, games and toys, navigation systems, fitness equipment, warning systems and voice mailboxes. Mask options also are available on the MSP50C30. These include DAC output options (two-pin digital or one-pin analog), a choice of an internal or external clock and package type (die or 100-pin QFP). Development tools supporting the MSP50C30 include an emulator and an assembler, which are used in the code development process. These tools allow users to compile, set breakpoints, single step through code and examine/modify registers and memory in order to debug their code.

For complete information, order: Product Literature. See Related Product Information

|

|

MSP50C3X family of synthesizers

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||